Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 36864                                                                    |

| Number of I/O                  | 71                                                                       |

| Number of Gates                | 125000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                 |

| Supplier Device Package        | 100-VQFP (14x14)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p125-1vqg100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ProASIC3 Device Family Overview ProASIC3 DC and Switching Characteristics Pin Descriptions Package Pin Assignments QN68 – Bottom View ......4-3 **Datasheet Information**

Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3 device provides the best available security for programmable logic designs.

### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based ProASIC3 FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

#### Instant On

Flash-based ProASIC3 devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based ProASIC3 devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs that are used for these purposes in a system. In addition, glitches and brownouts in system power will not corrupt the ProASIC3 device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASIC3 devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

#### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of ProASIC3 flash-based FPGAs. Once it is programmed, the flash cell configuration element of ProASIC3 FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### Low Power

Flash-based ProASIC3 devices exhibit power characteristics similar to an ASIC, making them an ideal choice for power-sensitive applications. ProASIC3 devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

ProASIC3 devices also have low dynamic power consumption to further maximize power savings.

Table 2-15 • Different Components Contributing to the Static Power Consumption in ProASIC3 Devices

|           | Definition                                       | Device Specific Static Power (mW)                           |                                                              |  |  |  |        |        |

|-----------|--------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--------|--------|

| Parameter |                                                  | A3P1000 A3P600 A3P400 A3P250 A3P125 A3P060                  |                                                              |  |  |  | A3P030 | A3P015 |

| PDC1      | Array static power in Active mode                | See Table 2-7 on page 2-7.                                  |                                                              |  |  |  |        |        |

| PDC2      | I/O input pin static power (standard-dependent)  |                                                             | See Table 2-8 on page 2-7 through<br>Table 2-10 on page 2-8. |  |  |  |        |        |

| PDC3      | I/O output pin static power (standard-dependent) | See Table 2-11 on page 2-9 through Table 2-13 on page 2-10. |                                                              |  |  |  |        |        |

| PDC4      | Static PLL contribution                          | 2.55 mW                                                     |                                                              |  |  |  |        |        |

| PDC5      | Bank quiescent power (VCCI-dependent)            | See Table 2-7 on page 2-7.                                  |                                                              |  |  |  |        |        |

Note: \*For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi Power spreadsheet calculator or SmartPower tool in Libero SoC software.

## **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in Libero SoC software.

The power calculation methodology described below uses the following variables:

- · The number of PLLs as well as the number and the frequency of each output clock generated

- · The number of combinatorial and sequential cells used in the design

- · The internal clock frequencies

- · The number and the standard of I/O pins used in the design

- · The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-16 on page 2-14.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-17 on page 2-14.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-17 on page 2-14. The calculation should be repeated for each clock domain defined in the design.

## Methodology

#### Total Power Consumption—PTOTAL

$P_{TOTAL} = P_{STAT} + P_{DYN}$

$P_{\mbox{\scriptsize STAT}}$  is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

P<sub>STAT</sub> = P<sub>DC1</sub> + N<sub>INPUTS</sub>\* P<sub>DC2</sub> + N<sub>OUTPUTS</sub>\* P<sub>DC3</sub>

N<sub>INPLITS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

#### Total Dynamic Power Consumption—P<sub>DYN</sub>

PDYN = PCLOCK + PS-CELL + PC-CELL + PNET + PINPUTS + POUTPUTS + PMEMORY + PPLL

## Global Clock Contribution—P<sub>CLOCK</sub>

P<sub>CLOCK</sub> = (P<sub>AC1</sub> + N<sub>SPINE</sub>\*P<sub>AC2</sub> + N<sub>ROW</sub>\*P<sub>AC3</sub> + N<sub>S-CELL</sub>\* P<sub>AC4</sub>) \* F<sub>CLK</sub>

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3 FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3 FPGA Fabric User's Guide*.

Table 2-33 • I/O Short Currents IOSH/IOSL

Applicable to Standard Plus I/O Banks

|                                      | Drive Strength              | IOSL (mA) <sup>1</sup>          | IOSH (mA) <sup>1</sup>          |

|--------------------------------------|-----------------------------|---------------------------------|---------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA                        | 27                              | 25                              |

|                                      | 4 mA                        | 27                              | 25                              |

|                                      | 6 mA                        | 54                              | 51                              |

|                                      | 8 mA                        | 54                              | 51                              |

|                                      | 12 mA                       | 109                             | 103                             |

|                                      | 16 mA                       | 109                             | 103                             |

| 3.3 V LVCMOS Wide Range <sup>2</sup> | 100 μΑ                      | Same as regular<br>3.3 V LVCMOS | Same as regular 3.3 V<br>LVCMOS |

| 2.5 V LVCMOS                         | 2 mA                        | 18                              | 16                              |

|                                      | 4 mA                        | 18                              | 16                              |

|                                      | 6 mA                        | 37                              | 32                              |

|                                      | 8 mA                        | 37                              | 32                              |

|                                      | 12 mA                       | 74                              | 65                              |

| 1.8 V LVCMOS                         | 2 mA                        | 11                              | 9                               |

|                                      | 4 mA                        | 22                              | 17                              |

|                                      | 6 mA                        | 44                              | 35                              |

|                                      | 8 mA                        | 44                              | 35                              |

| 1.5 V LVCMOS                         | 2 mA                        | 16                              | 13                              |

|                                      | 4 mA                        | 33                              | 25                              |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X specification | 109                             | 103                             |

#### Notes:

<sup>1.</sup>  $T_J = 100^{\circ}C$

<sup>2.</sup> Applicable to 3.3 V LVCMOS Wide Range. IOSL/IOSH dependent on the I/O buffer drive strength selected for wide range applications. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

Table 2-90 • LVDS Minimum and Maximum DC Input and Output Levels

| DC Parameter       | Description                 | Min.  | Тур.  | Max.  | Units |

|--------------------|-----------------------------|-------|-------|-------|-------|

| VCCI               | Supply Voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                | Output Low Voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                | Output High Voltage         | 1.25  | 1.425 | 1.6   | V     |

| IOL <sup>1</sup>   | Output Lower Current        | 0.65  | 0.91  | 1.16  | mA    |

| IOH <sup>1</sup>   | Output High Current         | 0.65  | 0.91  | 1.16  | mA    |

| VI                 | Input Voltage               | 0     |       | 2.925 | V     |

| IIH <sup>2,3</sup> | Input High Leakage Current  |       |       | 10    | μΑ    |

| IIL <sup>2,4</sup> | Input Low Leakage Current   |       |       | 10    | μΑ    |

| VODIFF             | Differential Output Voltage | 250   | 350   | 450   | mV    |

| VOCM               | Output Common Mode Voltage  | 1.125 | 1.25  | 1.375 | V     |

| VICM               | Input Common Mode Voltage   | 0.05  | 1.25  | 2.35  | V     |

| VIDIFF             | Input Differential Voltage  | 100   | 350   |       | mV    |

#### Notes:

- 1. IOL/IOH defined by VODIFF/(Resistor Network)

- 2. Currents are measured at 85°C junction temperature.

- 3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN <VCCI. Input current is larger when operating outside recommended ranges.

- 4. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN <VIL.

Table 2-91 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) |

|---------------|----------------|----------------------|

| 1.075         | 1.325          | Cross point          |

Note: \*Measuring point = V<sub>trip.</sub> See Table 2-22 on page 2-22 for a complete table of trip points.

### **Timing Characteristics**

Table 2-92 • LVDS

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 1.83            | 0.04             | 1.60            | ns    |

| <b>-1</b>   | 0.56              | 1.56            | 0.04             | 1.36            | ns    |

| -2          | 0.49              | 1.37            | 0.03             | 1.20            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

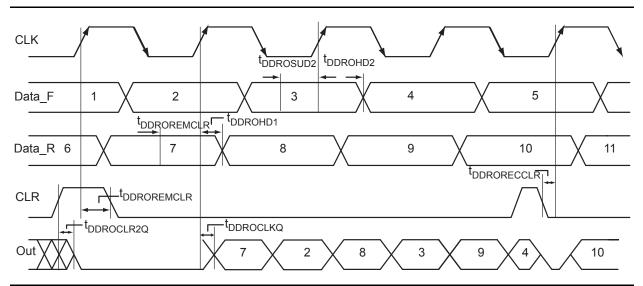

Figure 2-23 • Output DDR Timing Diagram

## **Timing Characteristics**

Table 2-104 • Output DDR Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                           | -2   | -1   | Std. | Units |

|-------------------------|-------------------------------------------------------|------|------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.70 | 0.80 | 0.94 | ns    |

| t <sub>DDROSUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.38 | 0.43 | 0.51 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.38 | 0.43 | 0.51 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width High for the Output DDR     | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output DDR      | 0.32 | 0.37 | 0.43 | ns    |

| F <sub>DDOMAX</sub>     | Maximum Frequency for the Output DDR                  | 350  | 309  | 263  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

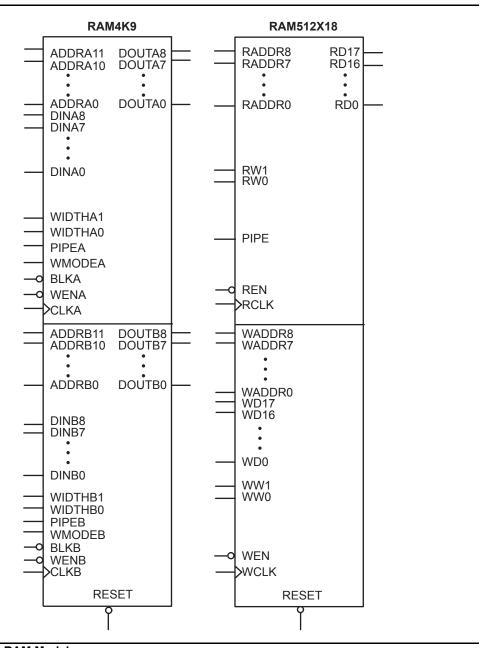

# **Embedded SRAM and FIFO Characteristics**

## **SRAM**

Figure 2-30 • RAM Models

# **Timing Characteristics**

Table 2-116 • RAM4K9

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                        | Description                                                                                                         | -2   | -1   | Std. | Units |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>                  | Address setup time                                                                                                  | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>                  | Address hold time                                                                                                   | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>                 | REN, WEN setup time                                                                                                 | 0.14 | 0.16 | 0.19 | ns    |

| t <sub>ENH</sub>                 | REN, WEN hold time                                                                                                  | 0.10 | 0.11 | 0.13 | ns    |

| t <sub>BKS</sub>                 | BLK setup time                                                                                                      | 0.23 | 0.27 | 0.31 | ns    |

| t <sub>BKH</sub>                 | BLK hold time                                                                                                       | 0.02 | 0.02 | 0.02 | ns    |

| t <sub>DS</sub>                  | Input data (DIN) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>                  | Input data (DIN) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>                | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                   | 2.36 | 2.68 | 3.15 | ns    |

|                                  | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 1.79 | 2.03 | 2.39 | ns    |

| t <sub>CKQ2</sub>                | Clock High to new data valid on DOUT (pipelined)                                                                    | 0.89 | 1.02 | 1.20 | ns    |

| t <sub>C2CWWL</sub> 1            | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Closing Edge        | 0.33 | 0.28 | 0.25 | ns    |

| t <sub>C2CWWH</sub> <sup>1</sup> | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Rising Edge         | 0.30 | 0.26 | 0.23 | ns    |

| t <sub>C2CRWH</sub> 1            | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge  | 0.45 | 0.38 | 0.34 | ns    |

| t <sub>C2CWRH</sub> 1            | Address collision clk-to-clk delay for reliable write access after read on same address— Applicable to Opening Edge | 0.49 | 0.42 | 0.37 | ns    |

| t <sub>RSTBQ</sub>               | RESET Low to data out Low on DOUT (flow-through)                                                                    | 0.92 | 1.05 | 1.23 | ns    |

|                                  | RESET Low to Data Out Low on DOUT (pipelined)                                                                       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>             | RESET removal                                                                                                       | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>             | RESET recovery                                                                                                      | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>             | RESET minimum pulse width                                                                                           | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>                 | Clock cycle time                                                                                                    | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>                 | Maximum frequency                                                                                                   | 310  | 272  | 231  | MHz   |

#### Notes:

For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

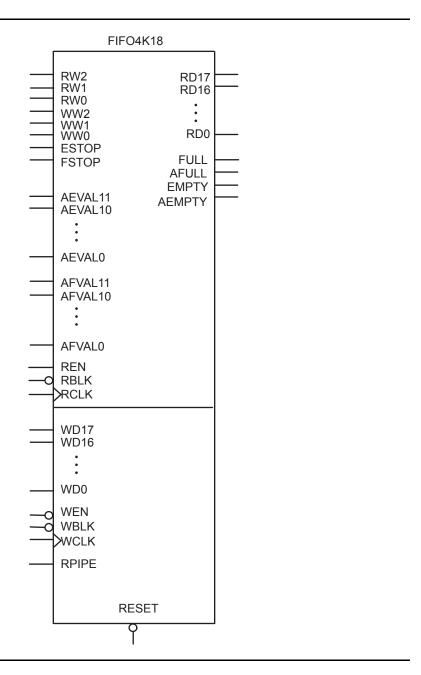

## **FIFO**

Figure 2-36 • FIFO Model

Table 2-119 • FIFO (for A3P250 only, aspect-ratio-dependent) Worst Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | <b>–1</b> | Std. | Units |

|----------------------|---------------------------------------------------|------|-----------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.26 | 3.71      | 4.36 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22      | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21      | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47      | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07      | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96      | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86      | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05      | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93      | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98      | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05      | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05      | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33      | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71      | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24      | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68      | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272       | 231  | MHz   |

2-103 Revision 18

Table 2-120 • A3P250 FIFO 512×8 Worst Commercial-Case Conditions:  $T_J$  = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.75 | 4.27 | 5.02 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

Table 2-123 • A3P250 FIFO 4k×1 (continued)

Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter            | Description                                    | -2   | <b>-1</b> | Std. | Units |

|----------------------|------------------------------------------------|------|-----------|------|-------|

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid      | 6.13 | 6.98      | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on DO (pass-through) | 0.92 | 1.05      | 1.23 | ns    |

|                      | RESET Low to Data Out Low on DO (pipelined)    | 0.92 | 1.05      | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                  | 0.29 | 0.33      | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                 | 1.50 | 1.71      | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                      | 0.21 | 0.24      | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                               | 3.23 | 3.68      | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency                              | 310  | 272       | 231  | MHz   |

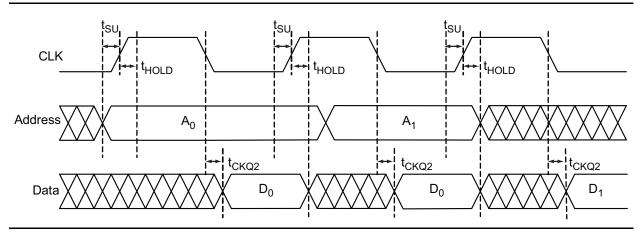

# **Embedded FlashROM Characteristics**

Figure 2-44 • Timing Diagram

# **Timing Characteristics**

Table 2-124 • Embedded FlashROM Access Time

| Parameter         | Description             | -2    | -1    | Std.  | Units |

|-------------------|-------------------------|-------|-------|-------|-------|

| t <sub>SU</sub>   | Address Setup Time      | 0.53  | 0.61  | 0.71  | ns    |

| t <sub>HOLD</sub> | Address Hold Time       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>CK2Q</sub> | Clock to Out            | 21.42 | 24.40 | 28.68 | ns    |

| F <sub>MAX</sub>  | Maximum Clock Frequency | 15    | 15    | 15    | MHz   |

2-107 Revision 18

## Package Pin Assignments

| PQ208      |                 |

|------------|-----------------|

| Pin Number | A3P600 Function |

| 109        | TRST            |

| 110        | VJTAG           |

| 111        | GDA0/IO88NDB1   |

| 112        | GDA1/IO88PDB1   |

| 113        | GDB0/IO87NDB1   |

| 114        | GDB1/IO87PDB1   |

| 115        | GDC0/IO86NDB1   |

| 116        | GDC1/IO86PDB1   |

| 117        | IO84NDB1        |

| 118        | IO84PDB1        |

| 119        | IO82NDB1        |

| 120        | IO82PDB1        |

| 121        | IO81PSB1        |

| 122        | GND             |

| 123        | VCCIB1          |

| 124        | IO77NDB1        |

| 125        | IO77PDB1        |

| 126        | NC              |

| 127        | IO74NDB1        |

| 128        | GCC2/IO74PDB1   |

| 129        | GCB2/IO73PSB1   |

| 130        | GND             |

| 131        | GCA2/IO72PSB1   |

| 132        | GCA1/IO71PDB1   |

| 133        | GCA0/IO71NDB1   |

| 134        | GCB0/IO70NDB1   |

| 135        | GCB1/IO70PDB1   |

| 136        | GCC0/IO69NDB1   |

| 137        | GCC1/IO69PDB1   |

| 138        | IO67NDB1        |

| 139        | IO67PDB1        |

| 140        | VCCIB1          |

| 141        | GND             |

| 142        | VCC             |

| 143        | IO65PSB1        |

| 144        | IO64NDB1        |

| PQ208      |                 |

|------------|-----------------|

| Pin Number | A3P600 Function |

| 145        | IO64PDB1        |

| 146        | IO63NDB1        |

| 147        | IO63PDB1        |

| 148        | IO62NDB1        |

| 149        | GBC2/IO62PDB1   |

| 150        | IO61NDB1        |

| 151        | GBB2/IO61PDB1   |

| 152        | IO60NDB1        |

| 153        | GBA2/IO60PDB1   |

| 154        | VMV1            |

| 155        | GNDQ            |

| 156        | GND             |

| 157        | VMV0            |

| 158        | GBA1/IO59RSB0   |

| 159        | GBA0/IO58RSB0   |

| 160        | GBB1/IO57RSB0   |

| 161        | GBB0/IO56RSB0   |

| 162        | GND             |

| 163        | GBC1/IO55RSB0   |

| 164        | GBC0/IO54RSB0   |

| 165        | IO52RSB0        |

| 166        | IO50RSB0        |

| 167        | IO48RSB0        |

| 168        | IO46RSB0        |

| 169        | IO44RSB0        |

| 170        | VCCIB0          |

| 171        | VCC             |

| 172        | IO36RSB0        |

| 173        | IO35RSB0        |

| 174        | IO34RSB0        |

| 175        | IO33RSB0        |

| 176        | IO32RSB0        |

| 177        | IO31RSB0        |

| 178        | GND             |

| 179        | IO29RSB0        |

| 180        | IO28RSB0        |

| PQ208      |                 |

|------------|-----------------|

| Pin Number | A3P600 Function |

| 181        | IO27RSB0        |

| 182        | IO26RSB0        |

| 183        | IO25RSB0        |

| 184        | IO24RSB0        |

| 185        | IO23RSB0        |

| 186        | VCCIB0          |

| 187        | VCC             |

| 188        | IO20RSB0        |

| 189        | IO19RSB0        |

| 190        | IO18RSB0        |

| 191        | IO17RSB0        |

| 192        | IO16RSB0        |

| 193        | IO14RSB0        |

| 194        | IO12RSB0        |

| 195        | GND             |

| 196        | IO10RSB0        |

| 197        | IO09RSB0        |

| 198        | IO08RSB0        |

| 199        | IO07RSB0        |

| 200        | VCCIB0          |

| 201        | GAC1/IO05RSB0   |

| 202        | GAC0/IO04RSB0   |

| 203        | GAB1/IO03RSB0   |

| 204        | GAB0/IO02RSB0   |

| 205        | GAA1/IO01RSB0   |

| 206        | GAA0/IO00RSB0   |

| 207        | GNDQ            |

| 208        | VMV0            |

4-36 Revision 18

## Package Pin Assignments

| FG144      |                 |

|------------|-----------------|

| Pin Number | A3P250 Function |

| A1         | GNDQ            |

| A2         | VMV0            |

| A3         | GAB0/IO02RSB0   |

| A4         | GAB1/IO03RSB0   |

| A5         | IO16RSB0        |

| A6         | GND             |

| A7         | IO29RSB0        |

| A8         | VCC             |

| A9         | IO33RSB0        |

| A10        | GBA0/IO39RSB0   |

| A11        | GBA1/IO40RSB0   |

| A12        | GNDQ            |

| B1         | GAB2/IO117UDB3  |

| B2         | GND             |

| В3         | GAA0/IO00RSB0   |

| B4         | GAA1/IO01RSB0   |

| B5         | IO14RSB0        |

| В6         | IO19RSB0        |

| В7         | IO22RSB0        |

| B8         | IO30RSB0        |

| В9         | GBB0/IO37RSB0   |

| B10        | GBB1/IO38RSB0   |

| B11        | GND             |

| B12        | VMV1            |

| C1         | IO117VDB3       |

| C2         | GFA2/IO107PPB3  |

| C3         | GAC2/IO116UDB3  |

| C4         | VCC             |

| C5         | IO12RSB0        |

| C6         | IO17RSB0        |

| C7         | IO24RSB0        |

| C8         | IO31RSB0        |

| C9         | IO34RSB0        |

| C10        | GBA2/IO41PDB1   |

| C11        | IO41NDB1        |

| C12        | GBC2/IO43PPB1   |

| FG144      |                 |

|------------|-----------------|

| Pin Number | A3P250 Function |

| D1         | IO112NDB3       |

| D2         | IO112PDB3       |

| D3         | IO116VDB3       |

| D4         | GAA2/IO118UPB3  |

| D5         | GAC0/IO04RSB0   |

| D6         | GAC1/IO05RSB0   |

| D7         | GBC0/IO35RSB0   |

| D8         | GBC1/IO36RSB0   |

| D9         | GBB2/IO42PDB1   |

| D10        | IO42NDB1        |

| D11        | IO43NPB1        |

| D12        | GCB1/IO49PPB1   |

| E1         | VCC             |

| E2         | GFC0/IO110NDB3  |

| E3         | GFC1/IO110PDB3  |

| E4         | VCCIB3          |

| E5         | IO118VPB3       |

| E6         | VCCIB0          |

| E7         | VCCIB0          |

| E8         | GCC1/IO48PDB1   |

| E9         | VCCIB1          |

| E10        | VCC             |

| E11        | GCA0/IO50NDB1   |

| E12        | IO51NDB1        |

| F1         | GFB0/IO109NPB3  |

| F2         | VCOMPLF         |

| F3         | GFB1/IO109PPB3  |

| F4         | IO107NPB3       |

| F5         | GND             |

| F6         | GND             |

| F7         | GND             |

| F8         | GCC0/IO48NDB1   |

| F9         | GCB0/IO49NPB1   |

| F10        | GND             |

| F11        | GCA1/IO50PDB1   |

| F12        | GCA2/IO51PDB1   |

| F0444      |                 |

|------------|-----------------|

| FG144      |                 |

| Pin Number | A3P250 Function |

| G1         | GFA1/IO108PPB3  |

| G2         | GND             |

| G3         | VCCPLF          |

| G4         | GFA0/IO108NPB3  |

| G5         | GND             |

| G6         | GND             |

| G7         | GND             |

| G8         | GDC1/IO58UPB1   |

| G9         | IO53NDB1        |

| G10        | GCC2/IO53PDB1   |

| G11        | IO52NDB1        |

| G12        | GCB2/IO52PDB1   |

| H1         | VCC             |

| H2         | GFB2/IO106PDB3  |

| H3         | GFC2/IO105PSB3  |

| H4         | GEC1/IO100PDB3  |

| H5         | VCC             |

| H6         | IO79RSB2        |

| H7         | IO65RSB2        |

| H8         | GDB2/IO62RSB2   |

| H9         | GDC0/IO58VPB1   |

| H10        | VCCIB1          |

| H11        | IO54PSB1        |

| H12        | VCC             |

| J1         | GEB1/IO99PDB3   |

| J2         | IO106NDB3       |

| J3         | VCCIB3          |

| J4         | GEC0/IO100NDB3  |

| J5         | IO88RSB2        |

| J6         | IO81RSB2        |

| J7         | VCC             |

| J8         | TCK             |

| J9         | GDA2/IO61RSB2   |

| J10        | TDO             |

| J11        | GDA1/IO60UDB1   |

| J12        | GDB1/IO59UDB1   |

4-44 Revision 18

| FG256      |                  |

|------------|------------------|

| Pin Number | A3P1000 Function |

| H3         | GFB1/IO208PPB3   |

| H4         | VCOMPLF          |

| H5         | GFC0/IO209NPB3   |

| H6         | VCC              |

| H7         | GND              |

| H8         | GND              |

| H9         | GND              |

| H10        | GND              |

| H11        | VCC              |

| H12        | GCC0/IO91NPB1    |

| H13        | GCB1/IO92PPB1    |

| H14        | GCA0/IO93NPB1    |

| H15        | IO96NPB1         |

| H16        | GCB0/IO92NPB1    |

| J1         | GFA2/IO206PSB3   |

| J2         | GFA1/IO207PDB3   |

| J3         | VCCPLF           |

| J4         | IO205NDB3        |

| J5         | GFB2/IO205PDB3   |

| J6         | VCC              |

| J7         | GND              |

| J8         | GND              |

| J9         | GND              |

| J10        | GND              |

| J11        | VCC              |

| J12        | GCB2/IO95PPB1    |

| J13        | GCA1/IO93PPB1    |

| J14        | GCC2/IO96PPB1    |

| J15        | IO100PPB1        |

| J16        | GCA2/IO94PSB1    |

| K1         | GFC2/IO204PDB3   |

| K2         | IO204NDB3        |

| K3         | IO203NDB3        |

| K4         | IO203PDB3        |

| K5         | VCCIB3           |

| K6         | VCC              |

| K7         | GND              |

| K8         | GND              |

|            |                  |

| FG256      |                  |

|------------|------------------|

| Pin Number | A3P1000 Function |

| K9         | GND              |

| K10        | GND              |

| K11        | VCC              |

| K12        | VCCIB1           |

| K12        | IO95NPB1         |

| K14        | IO100NPB1        |

| K15        | IO102NDB1        |

| K16        | IO102PDB1        |

| L1         | IO202NDB3        |

| L2         | IO202PDB3        |

| L2<br>L3   |                  |

|            | IO196PPB3        |

| L4         | IO193PPB3        |

| L5         | VCCIB3           |

| L6         | GND              |

| L7         | VCC              |

| L8         | VCC              |

| L9         | VCC              |

| L10        | VCC              |

| L11        | GND              |

| L12        | VCCIB1           |

| L13        | GDB0/IO112NPB1   |

| L14        | IO106NDB1        |

| L15        | IO106PDB1        |

| L16        | IO107PDB1        |

| M1         | IO197NSB3        |

| M2         | IO196NPB3        |

| M3         | IO193NPB3        |

| M4         | GEC0/IO190NPB3   |

| M5         | VMV3             |

| M6         | VCCIB2           |

| M7         | VCCIB2           |

| M8         | IO147RSB2        |

| M9         | IO136RSB2        |

| M10        | VCCIB2           |

| M11        | VCCIB2           |

| M12        | VMV2             |

| M13        | IO110NDB1        |

| M14        | GDB1/IO112PPB1   |

|            |                  |

| FG256                         |                |

|-------------------------------|----------------|

| Pin Number   A3P1000 Function |                |

| M15                           | GDC1/IO111PDB1 |

| M16                           | IO107NDB1      |

| N1                            | IO194PSB3      |

| N2                            | IO192PPB3      |

| N3                            | GEC1/IO190PPB3 |

| N4                            | IO192NPB3      |

| N5                            | GNDQ           |

| N6                            | GEA2/IO187RSB2 |

| N7                            | IO161RSB2      |

|                               |                |

| N8                            | IO155RSB2      |

| N9                            | IO141RSB2      |

| N10                           | IO129RSB2      |

| N11                           | IO124RSB2      |

| N12                           | GNDQ           |

| N13                           | IO110PDB1      |

| N14                           | VJTAG          |

| N15                           | GDC0/IO111NDB1 |

| N16                           | GDA1/IO113PDB1 |

| P1                            | GEB1/IO189PDB3 |

| P2                            | GEB0/IO189NDB3 |

| P3                            | VMV2           |

| P4                            | IO179RSB2      |

| P5                            | IO171RSB2      |

| P6                            | IO165RSB2      |

| P7                            | IO159RSB2      |

| P8                            | IO151RSB2      |

| P9                            | IO137RSB2      |

| P10                           | IO134RSB2      |

| P11                           | IO128RSB2      |

| P12                           | VMV1           |

| P13                           | TCK            |

| P14                           | VPUMP          |

| P15                           | TRST           |

| P16                           | GDA0/IO113NDB1 |

| R1                            | GEA1/IO188PDB3 |

| R2                            | GEA0/IO188NDB3 |

| R3                            | IO184RSB2      |

| R4                            | GEC2/IO185RSB2 |

| FG484      |                 |

|------------|-----------------|

| Pin Number | A3P600 Function |

| K19        | IO75NDB1        |

| K20        | NC              |

| K21        | IO76NDB1        |

| K22        | IO76PDB1        |

| L1         | NC              |

| L2         | IO155PDB3       |

| L3         | NC              |

| L4         | GFB0/IO163NPB3  |

| L5         | GFA0/IO162NDB3  |

| L6         | GFB1/IO163PPB3  |

| L7         | VCOMPLF         |

| L8         | GFC0/IO164NPB3  |

| L9         | VCC             |

| L10        | GND             |

| L11        | GND             |

| L12        | GND             |

| L13        | GND             |

| L14        | VCC             |

| L15        | GCC0/IO69NPB1   |

| L16        | GCB1/IO70PPB1   |

| L17        | GCA0/IO71NPB1   |

| L18        | IO67NPB1        |

| L19        | GCB0/IO70NPB1   |

| L20        | IO77PDB1        |

| L21        | IO77NDB1        |

| L22        | IO78NPB1        |

| M1         | NC              |

| M2         | IO155NDB3       |

| M3         | IO158NPB3       |

| M4         | GFA2/IO161PPB3  |

| M5         | GFA1/IO162PDB3  |

| M6         | VCCPLF          |

| M7         | IO160NDB3       |

| M8         | GFB2/IO160PDB3  |

| M9         | VCC             |

| M10        | GND             |

| FG484      |                 |

|------------|-----------------|

| Pin Number | A3P600 Function |

| M11        | GND             |

| M12        | GND             |

| M13        | GND             |

| M14        | VCC             |

| M15        | GCB2/IO73PPB1   |

| M16        | GCA1/IO71PPB1   |

| M17        | GCC2/IO74PPB1   |

| M18        | IO80PPB1        |

| M19        | GCA2/IO72PDB1   |

| M20        | IO79PPB1        |

| M21        | IO78PPB1        |

| M22        | NC              |

| N1         | IO154NDB3       |

| N2         | IO154PDB3       |

| N3         | NC              |

| N4         | GFC2/IO159PDB3  |

| N5         | IO161NPB3       |

| N6         | IO156PPB3       |

| N7         | IO129RSB2       |

| N8         | VCCIB3          |

| N9         | VCC             |

| N10        | GND             |

| N11        | GND             |

| N12        | GND             |

| N13        | GND             |

| N14        | VCC             |

| N15        | VCCIB1          |

| N16        | IO73NPB1        |

| N17        | IO80NPB1        |

| N18        | IO74NPB1        |

| N19        | IO72NDB1        |

| N20        | NC              |

| N21        | IO79NPB1        |

| N22        | NC              |

| P1         | NC              |

| P2         | IO153PDB3       |

| -0.01      |                 |  |

|------------|-----------------|--|

|            | FG484           |  |

| Pin Number | A3P600 Function |  |

| P3         | IO153NDB3       |  |

| P4         | IO159NDB3       |  |

| P5         | IO156NPB3       |  |

| P6         | IO151PPB3       |  |

| P7         | IO158PPB3       |  |

| P8         | VCCIB3          |  |

| P9         | GND             |  |

| P10        | VCC             |  |

| P11        | VCC             |  |

| P12        | VCC             |  |

| P13        | VCC             |  |

| P14        | GND             |  |

| P15        | VCCIB1          |  |

| P16        | GDB0/IO87NPB1   |  |

| P17        | IO85NDB1        |  |

| P18        | IO85PDB1        |  |

| P19        | IO84PDB1        |  |

| P20        | NC              |  |

| P21        | IO81PDB1        |  |

| P22        | NC              |  |

| R1         | NC              |  |

| R2         | NC              |  |

| R3         | VCC             |  |

| R4         | IO150PDB3       |  |

| R5         | IO151NPB3       |  |

| R6         | IO147NPB3       |  |

| R7         | GEC0/IO146NPB3  |  |

| R8         | VMV3            |  |

| R9         | VCCIB2          |  |

| R10        | VCCIB2          |  |

| R11        | IO117RSB2       |  |

| R12        | IO110RSB2       |  |

| R13        | VCCIB2          |  |

| R14        | VCCIB2          |  |

| R15        | VMV2            |  |

| R16        | IO94RSB2        |  |

|            | FG484           |

|------------|-----------------|

| Pin Number | A3P600 Function |

| Y15        | VCC             |

| Y16        | NC              |

| Y17        | NC              |

| Y18        | GND             |

| Y19        | NC              |

| Y20        | NC              |

| Y21        | NC              |

| Y22        | VCCIB1          |

| AA1        | GND             |

| AA2        | VCCIB3          |

| AA3        | NC              |

| AA4        | NC              |

| AA5        | NC              |

| AA6        | IO135RSB2       |

| AA7        | IO133RSB2       |

| AA8        | NC              |

| AA9        | NC              |

| AA10       | NC              |

| AA11       | NC              |

| AA12       | NC              |

| AA13       | NC              |

| AA14       | NC              |

| AA15       | NC              |

| AA16       | IO101RSB2       |

| AA17       | NC              |

| AA18       | NC              |

| AA19       | NC              |

| AA20       | NC              |

| AA21       | VCCIB1          |

| AA22       | GND             |

| AB1        | GND             |

| AB2        | GND             |

| AB3        | VCCIB2          |

| AB4        | NC              |

| AB5        | NC              |

| AB6        | IO130RSB2       |

| FG484      |                 |  |

|------------|-----------------|--|

| Pin Number | A3P600 Function |  |

| AB7        | IO128RSB2       |  |

| AB8        | IO122RSB2       |  |

| AB9        | IO116RSB2       |  |

| AB10       | NC              |  |

| AB11       | NC              |  |

| AB12       | IO113RSB2       |  |

| AB13       | IO112RSB2       |  |

| AB14       | NC              |  |

| AB15       | NC              |  |

| AB16       | IO100RSB2       |  |

| AB17       | IO95RSB2        |  |

| AB18       | NC              |  |

| AB19       | NC              |  |

| AB20       | VCCIB2          |  |

| AB21       | GND             |  |

| AB22       | GND             |  |

# 5 - Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in each version of the ProASIC3 datasheet.

| Revision                                                                                                                       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                      |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                                                                                                                                | Updated 3.3 V DC supply voltage's maximum Commercial and Industrial values from 3.3 V to 3.6 V in Table 2-2 (SAR 72693).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-2                       |

|                                                                                                                                | Added reference of Package Mechanical Drawings document in all package pin assignment notes (76833).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NA                        |

| Revision 17                                                                                                                    | Removed PQFP embedded heat spreader info. from Table 2-5 (SAR 52320).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-6                       |

| (June 2015)                                                                                                                    | Updated "VCCIBx I/O Supply Voltage" (SAR 43323).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1                       |

| Revision 16<br>(December 2014)                                                                                                 | in the second control of the second control |                           |

|                                                                                                                                | Updated Table Note (2) in Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature so that the Table Note is not applicable for Maximum Storage Temperature T <sub>STG</sub> (SAR 54297).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-3                       |

|                                                                                                                                | Added values for Drive strength 2 mA in Table 2-41 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew, Table 2-42 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew, Table 2-43 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew, and Table 2-44 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew (SAR 57184).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-34, 2-35,<br>2-36, 2-37 |

|                                                                                                                                | Added Figure 2-1 • High-Temperature Data Retention (HTR) (SAR 45466).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-3                       |

|                                                                                                                                | Updates made to maintain the style and consistency of the document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NA                        |

| (July 2014)  Ambient temperature removed in Table 2-2, table notes and Ordering Information" figure were modified (SAR 48343). | Added corner pad table note (3) to "QN132 – Bottom View" (SAR 47442).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-6                       |

|                                                                                                                                | Ambient temperature removed in Table 2-2, table notes and "ProASIC3 Ordering Information" figure were modified (SAR 48343).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-2<br>1-IV               |