Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 97                                                                        |

| Number of Gates                | 250000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 144-LBGA                                                                  |

| Supplier Device Package        | 144-FPBGA (13x13)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p250-2fgg144i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 – ProASIC3 DC and Switching Characteristics

# **General Specifications**

# **Operating Conditions**

Stresses beyond those listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-2 on page 2-2 is not implied.

| Table 2-1 • Absolute Maximum Ratings | Table 2-1 • | Absolute | Maximum | Ratings |

|--------------------------------------|-------------|----------|---------|---------|

|--------------------------------------|-------------|----------|---------|---------|

| Symbol                        | Parameter                           | Limits                                                                                                | Units |

|-------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|-------|

| VCC                           | DC core supply voltage              | –0.3 to 1.65                                                                                          | V     |

| VJTAG                         | JTAG DC voltage                     | -0.3 to 3.75                                                                                          | V     |

| VPUMP                         | Programming voltage                 | -0.3 to 3.75                                                                                          | V     |

| VCCPLL                        | Analog power supply (PLL)           | –0.3 to 1.65                                                                                          | V     |

| VCCI                          | DC I/O output buffer supply voltage | -0.3 to 3.75                                                                                          | V     |

| VMV                           | DC I/O input buffer supply voltage  | –0.3 to 3.75                                                                                          | V     |

| VI                            | I/O input voltage                   | –0.3 V to 3.6 V                                                                                       | V     |

|                               |                                     | (when I/O hot insertion mode is enabled)                                                              |       |

|                               |                                     | -0.3 V to (VCCI + 1 V) or 3.6 V, whichever voltage is lower (when I/O hot-insertion mode is disabled) |       |

| T <sub>STG</sub> <sup>2</sup> | Storage temperature                 | -65 to +150                                                                                           | °C    |

| T <sub>J</sub> <sup>2</sup>   | Junction temperature                | +125                                                                                                  | °C    |

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-4 on page 2-3.

2. VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further information.

3. For flash programming and retention maximum limits, refer to Table 2-3 on page 2-3, and for recommended operating limits, refer to Table 2-2 on page 2-2.

#### Table 2-11 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings<sup>1</sup> Applicable to Advanced I/O Banks

|                                      | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|--------------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                         |                        |          |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 35                     | 3.3      | -                                      | 468.67                                       |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 35                     | 3.3      | -                                      | 468.67                                       |

| 2.5 V LVCMOS                         | 35                     | 2.5      | -                                      | 267.48                                       |

| 1.8 V LVCMOS                         | 35                     | 1.8      | -                                      | 149.46                                       |

| 1.5 V LVCMOS<br>(JESD8-11)           | 35                     | 1.5      | -                                      | 103.12                                       |

| 3.3 V PCI                            | 10                     | 3.3      | -                                      | 201.02                                       |

| 3.3 V PCI-X                          | 10                     | 3.3      | -                                      | 201.02                                       |

| Differential                         |                        |          |                                        |                                              |

| LVDS                                 | _                      | 2.5      | 7.74                                   | 88.92                                        |

| LVPECL                               | _                      | 3.3      | 19.54                                  | 166.52                                       |

Notes:

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2. PDC3 is the static power (where applicable) measured on VCCI.

3. PAC10 is the total dynamic power measured on VCC and VCCI.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

#### Table 2-12 • Summary of I/O Output Buffer Power (Per Pin) – Default I/O Software Settings<sup>1</sup> Applicable to Standard Plus I/O Banks

|                                      | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|--------------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                         |                        |          |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 35                     | 3.3      | -                                      | 452.67                                       |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 35                     | 3.3      | -                                      | 452.67                                       |

| 2.5 V LVCMOS                         | 35                     | 2.5      | -                                      | 258.32                                       |

| 1.8 V LVCMOS                         | 35                     | 1.8      | -                                      | 133.59                                       |

| 1.5 V LVCMOS (JESD8-11)              | 35                     | 1.5      | -                                      | 92.84                                        |

| 3.3 V PCI                            | 10                     | 3.3      | -                                      | 184.92                                       |

| 3.3 V PCI-X                          | 10                     | 3.3      | -                                      | 184.92                                       |

Notes:

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2.  $P_{DC3}$  is the static power (where applicable) measured on VMV.

3. P<sub>AC10</sub> is the total dynamic power measured on VCC and VMV.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

#### Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings

-2 Speed Grade, Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst Case VCC = 1.425 V, Worst-Case VCCI (per standard)

Standard Plus I/O Banks

| I/O Standard                            | Drive Strength       | Equiv. Software Default<br>Drive Strength Option <sup>1</sup> | Slew Rate | Capacitive Load (pF) | External Resistor | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-----------------------------------------|----------------------|---------------------------------------------------------------|-----------|----------------------|-------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS           | 12 mA                | 12 mA                                                         | High      | 35                   | -                 | 0.45                   | 2.36                 | 0.03                  | 0.75                 | 0.32                   | 2.40                 | 1.93                 | 2.08                 | 2.41                 | 4.07                  | 3.60                  | ns    |

| 3.3 V LVCMOS<br>Wide Range <sup>2</sup> | 100 µA               | 12 mA                                                         | High      | 35                   | _                 | 0.45                   | 3.65                 | 0.03                  | 1.14                 | 0.32                   | 3.65                 | 2.93                 | 3.22                 | 3.72                 | 6.18                  | 5.46                  | ns    |

| 2.5 V LVCMOS                            | 12 mA                | 12 mA                                                         | High      | 35                   | _                 | 0.45                   | 2.39                 | 0.03                  | 0.97                 | 0.32                   | 2.44                 | 2.35                 | 2.11                 | 2.32                 | 4.11                  | 4.02                  | ns    |

| 1.8 V LVCMOS                            | 8 mA                 | 8 mA                                                          | High      | 35                   | -                 | 0.45                   | 3.03                 | 0.03                  | 0.90                 | 0.32                   | 2.87                 | 3.03                 | 2.19                 | 2.32                 | 4.54                  | 4.70                  | ns    |

| 1.5 V LVCMOS                            | 4 mA                 | 4 mA                                                          | High      | 35                   | -                 | 0.45                   | 3.61                 | 0.03                  | 1.06                 | 0.32                   | 3.35                 | 3.61                 | 2.26                 | 2.34                 | 5.02                  | 5.28                  | ns    |

| 3.3 V PCI                               | Per<br>PCI<br>spec   | -                                                             | High      | 10                   | 25 <sup>4</sup>   | 0.45                   | 1.72                 | 0.03                  | 0.64                 | 0.32                   | 1.76                 | 1.27                 | 2.08                 | 2.41                 | 3.42                  | 2.94                  | ns    |

| 3.3 V PCI-X                             | Per<br>PCI-X<br>spec | -                                                             | High      | 10                   | 25 <sup>4</sup>   | 0.45                   | 1.72                 | 0.03                  | 0.62                 | 0.32                   | 1.76                 | 1.27                 | 2.08                 | 2.41                 | 3.42                  | 2.94                  | ns    |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

4. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-11 on page 2-64 for connectivity. This resistor is not required during normal operation.

# Table 2-29 • I/O Output Buffer Maximum Resistances <sup>1</sup> Applicable to Standard Plus I/O Banks

| Standard                             | Drive Strength              | R <sub>PULL-DOWN</sub> (Ω) <sup>2</sup> | R <sub>PULL-UP</sub> (Ω) <sup>3</sup> |

|--------------------------------------|-----------------------------|-----------------------------------------|---------------------------------------|

| 3.3 V LVTTL / 3.3 V                  | 2 mA                        | 100                                     | 300                                   |

| LVCMOS                               | 4 mA                        | 100                                     | 300                                   |

|                                      | 6 mA                        | 50                                      | 150                                   |

|                                      | 8 mA                        | 50                                      | 150                                   |

|                                      | 12 mA                       | 25                                      | 75                                    |

|                                      | 16 mA                       | 25                                      | 75                                    |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 100 µA                      | Same as regular 3.3 V LVCMOS            | Same as regular 3.3 V LVCMOS          |

| 2.5 V LVCMOS                         | 2 mA                        | 100                                     | 200                                   |

|                                      | 4 mA                        | 100                                     | 200                                   |

|                                      | 6 mA                        | 50                                      | 100                                   |

|                                      | 8 mA                        | 50                                      | 100                                   |

|                                      | 12 mA                       | 25                                      | 50                                    |

| 1.8 V LVCMOS                         | 2 mA                        | 200                                     | 225                                   |

|                                      | 4 mA                        | 100                                     | 112                                   |

|                                      | 6 mA                        | 50                                      | 56                                    |

|                                      | 8 mA                        | 50                                      | 56                                    |

| 1.5 V LVCMOS                         | 2 mA                        | 200                                     | 224                                   |

| Γ                                    | 4 mA                        | 100                                     | 112                                   |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X specification | 25                                      | 75                                    |

Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located at http://www.microsemi.com/soc/download/ibis/default.aspx.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

<sup>2.</sup> R<sub>(PULL-DOWN-MAX)</sub> = (VOLspec) / IOLspec

<sup>3.</sup> R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

| Table 2-49 • | Minimum and Maximum DC Input and Output Levels |

|--------------|------------------------------------------------|

|              | Applicable to Standard I/O Banks               |

| 3.3 V<br>LVCMOS<br>Wide Range | Equiv.<br>Software<br>Default            |          | ΊL       | v        | ΊH       | VOL      | VOH       | IOL | юн  | IOSL                   | IOSH                   | IIL <sup>2</sup> | IIH <sup>3</sup> |

|-------------------------------|------------------------------------------|----------|----------|----------|----------|----------|-----------|-----|-----|------------------------|------------------------|------------------|------------------|

| Drive<br>Strength             | Drive<br>Strength<br>Option <sup>1</sup> | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V  | μA  | μA  | Max<br>mA <sup>4</sup> | Max<br>mA <sup>4</sup> | μA <sup>5</sup>  | μA <sup>5</sup>  |

| 100 µA                        | 2 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10               | 10               |

| 100 µA                        | 4 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10               | 10               |

| 100 µA                        | 6 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10               | 10               |

| 100 µA                        | 8 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10               | 10               |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is  $\pm 100 \ \mu$ A. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

4. Currents are measured at 85°C junction temperature.

5. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

6. Software default selection highlighted in gray.

## **Timing Characteristics**

# Table 2-100 • Output Enable Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -2   | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.59 | 0.67 | 0.79 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.31 | 0.36 | 0.42 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.50 | 0.58 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.67 | 0.76 | 0.89 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.67 | 0.76 | 0.89 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.32 | 0.37 | 0.43 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

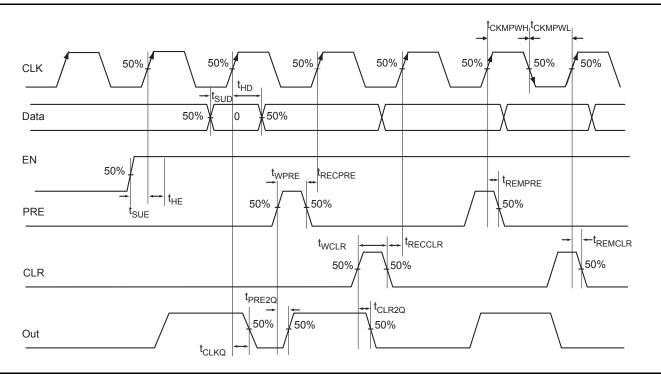

# Figure 2-27 • Timing Model and Waveforms

#### **Timing Characteristics**

### Table 2-106 • Register Delays

# Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -2   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.55 | 0.63 | 0.74 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.43 | 0.49 | 0.57 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.40 | 0.45 | 0.53 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.40 | 0.45 | 0.53 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.37 | 0.43 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.41 | 0.48 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Timing Characteristics

### Table 2-107 • A3P015 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2                | -                 | -1                | S                 |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.66              | 0.81              | 0.75              | 0.92              | 0.88              | 1.08              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.67              | 0.84              | 0.76              | 0.96              | 0.89              | 1.13              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.18              |                   | 0.21              |                   | 0.25              | ns    |

#### Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage-supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-108 • A3P030 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           |                   | -2                |                   | –1                |                   | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.67              | 0.81              | 0.76              | 0.92              | 0.89              | 1.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.68              | 0.85              | 0.77              | 0.97              | 0.91              | 1.14              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.18              |                   | 0.21              |                   | 0.24              | ns    |

#### Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-111 • A3P250 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2                | -                 | -1                | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.80              | 1.01              | 0.91              | 1.15              | 1.07              | 1.36              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.78              | 1.04              | 0.89              | 1.18              | 1.04              | 1.39              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-112 • A3P400 Global Resource

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

```

|                      |                                           | -                 | -2 -1             |                   | -1                | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.87              | 1.09              | 0.99              | 1.24              | 1.17              | 1.46              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.86              | 1.11              | 0.98              | 1.27              | 1.15              | 1.49              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# 3 – Pin Descriptions

# **Supply Pins**

#### Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

#### GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ must always be connected to GND on the board.

#### VCC

GND

#### Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is required for powering the JTAG state machine in addition to VJTAG. Even when a device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the device.

### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are up to eight I/O banks on low power flash devices plus a dedicated VJTAG bank. Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. In general, unused I/O banks should have their corresponding VCCIX pins tied to GND. If an output pad is terminated to ground through any resistor and if the corresponding VCCIX is left floating, then the leakage current to ground is ~ 0uA. However, if an output pad is terminated to ground is ~ 3 uA. For unused banks the aforementioned behavior is to be taken into account while deciding if it's better to float VCCIX of unused bank or tie it to GND.

## VMVx I/O Supply Voltage (quiet)

Quiet supply voltage to the input buffers of each I/O bank. *x* is the bank number. Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks. This minimizes the noise transfer within the package and improves input signal integrity. Each bank must have at least one VMV connection, and no VMV should be left unconnected. All I/Os in a bank run off the same VMVx supply. VMV is used to provide a quiet supply voltage to the input buffers of each I/O bank. VMVx can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VMV pins tied to GND. VMV and VCCI should be at the same voltage within a given I/O bank. Used VMV pins must be connected to the corresponding VCCI pins of the same bank (i.e., VMV0 to VCCIB0, VMV1 to VCCIB1, etc.).

## VCCPLA/B/C/D/E/F PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V.

When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Microsemi recommends tying VCCPLx to VCC and using proper filtering circuits to decouple VCC noise from the PLLs. Refer to the PLL Power Supply Decoupling section of the "Clock Conditioning Circuits in IGLOO and ProASIC3 Devices" chapter of the *ProASIC3 FPGA Fabric User's Guide* for a complete board solution for the PLL analog power supply and ground.

There is one VCCPLF pin on ProASIC3 devices.

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There is one VCOMPLF pin on ProASIC3 devices.

Package Pin Assignments

| QN132      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P060 Function |  |  |  |  |

| C17        | IO57RSB1        |  |  |  |  |

| C18        | NC              |  |  |  |  |

| C19        | ТСК             |  |  |  |  |

| C20        | VMV1            |  |  |  |  |

| C21        | VPUMP           |  |  |  |  |

| C22        | VJTAG           |  |  |  |  |

| C23        | VCCIB0          |  |  |  |  |

| C24        | NC              |  |  |  |  |

| C25        | NC              |  |  |  |  |

| C26        | GCA1/IO42RSB0   |  |  |  |  |

| C27        | GCC0/IO39RSB0   |  |  |  |  |

| C28        | VCCIB0          |  |  |  |  |

| C29        | IO29RSB0        |  |  |  |  |

| C30        | GNDQ            |  |  |  |  |

| C31        | GBA1/IO27RSB0   |  |  |  |  |

| C32        | GBB0/IO24RSB0   |  |  |  |  |

| C33        | VCC             |  |  |  |  |

| C34        | IO19RSB0        |  |  |  |  |

| C35        | IO16RSB0        |  |  |  |  |

| C36        | IO13RSB0        |  |  |  |  |

| C37        | GAC1/IO10RSB0   |  |  |  |  |

| C38        | NC              |  |  |  |  |

| C39        | GAA0/IO05RSB0   |  |  |  |  |

| C40        | VMV0            |  |  |  |  |

| D1         | GND             |  |  |  |  |

| D2         | GND             |  |  |  |  |

| D3         | GND             |  |  |  |  |

| D4         | GND             |  |  |  |  |

Package Pin Assignments

| VQ100      |                 | VQ100      |                 | VQ100      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P060 Function | Pin Number | A3P060 Function | Pin Number | A3P060 Function |  |

| 1          | GND             | 37         | VCC             | 73         | GBA2/IO25RSB0   |  |

| 2          | GAA2/IO51RSB1   | 38         | GND             | 74         | VMV0            |  |

| 3          | IO52RSB1        | 39         | VCCIB1          | 75         | GNDQ            |  |

| 4          | GAB2/IO53RSB1   | 40         | IO60RSB1        | 76         | GBA1/IO24RSB0   |  |

| 5          | IO95RSB1        | 41         | IO59RSB1        | 77         | GBA0/IO23RSB0   |  |

| 6          | GAC2/IO94RSB1   | 42         | IO58RSB1        | 78         | GBB1/IO22RSB0   |  |

| 7          | IO93RSB1        | 43         | IO57RSB1        | 79         | GBB0/IO21RSB0   |  |

| 8          | IO92RSB1        | 44         | GDC2/IO56RSB1   | 80         | GBC1/IO20RSB0   |  |

| 9          | GND             | 45         | GDB2/IO55RSB1   | 81         | GBC0/IO19RSB0   |  |

| 10         | GFB1/IO87RSB1   | 46         | GDA2/IO54RSB1   | 82         | IO18RSB0        |  |

| 11         | GFB0/IO86RSB1   | 47         | ТСК             | 83         | IO17RSB0        |  |

| 12         | VCOMPLF         | 48         | TDI             | 84         | IO15RSB0        |  |

| 13         | GFA0/IO85RSB1   | 49         | TMS             | 85         | IO13RSB0        |  |

| 14         | VCCPLF          | 50         | VMV1            | 86         | IO11RSB0        |  |

| 15         | GFA1/IO84RSB1   | 51         | GND             | 87         | VCCIB0          |  |

| 16         | GFA2/IO83RSB1   | 52         | VPUMP           | 88         | GND             |  |

| 17         | VCC             | 53         | NC              | 89         | VCC             |  |

| 18         | VCCIB1          | 54         | TDO             | 90         | IO10RSB0        |  |

| 19         | GEC1/IO77RSB1   | 55         | TRST            | 91         | IO09RSB0        |  |

| 20         | GEB1/IO75RSB1   | 56         | VJTAG           | 92         | IO08RSB0        |  |

| 21         | GEB0/IO74RSB1   | 57         | GDA1/IO49RSB0   | 93         | GAC1/IO07RSB0   |  |

| 22         | GEA1/IO73RSB1   | 58         | GDC0/IO46RSB0   | 94         | GAC0/IO06RSB0   |  |

| 23         | GEA0/IO72RSB1   | 59         | GDC1/IO45RSB0   | 95         | GAB1/IO05RSB0   |  |

| 24         | VMV1            | 60         | GCC2/IO43RSB0   | 96         | GAB0/IO04RSB0   |  |

| 25         | GNDQ            | 61         | GCB2/IO42RSB0   | 97         | GAA1/IO03RSB0   |  |

| 26         | GEA2/IO71RSB1   | 62         | GCA0/IO40RSB0   | 98         | GAA0/IO02RSB0   |  |

| 27         | GEB2/IO70RSB1   | 63         | GCA1/IO39RSB0   | 99         | IO01RSB0        |  |

| 28         | GEC2/IO69RSB1   | 64         | GCC0/IO36RSB0   | 100        | IO00RSB0        |  |

| 29         | IO68RSB1        | 65         | GCC1/IO35RSB0   |            | -               |  |

| 30         | IO67RSB1        | 66         | VCCIB0          |            |                 |  |

| 31         | IO66RSB1        | 67         | GND             |            |                 |  |

| 32         | IO65RSB1        | 68         | VCC             |            |                 |  |

| 33         | IO64RSB1        | 69         | IO31RSB0        |            |                 |  |

| 34         | IO63RSB1        | 70         | GBC2/IO29RSB0   |            |                 |  |

| 35         | IO62RSB1        | 71         | GBB2/IO27RSB0   |            |                 |  |

| 36         | IO61RSB1        | 72         | IO26RSB0        |            |                 |  |

| т          | TQ144           |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| Pin Number | A3P060 Function |  |  |  |  |  |

| 109        | NC              |  |  |  |  |  |

| 110        | NC              |  |  |  |  |  |

| 111        | GBA1/IO24RSB0   |  |  |  |  |  |

| 112        | GBA0/IO23RSB0   |  |  |  |  |  |

| 113        | GBB1/IO22RSB0   |  |  |  |  |  |

| 114        | GBB0/IO21RSB0   |  |  |  |  |  |

| 115        | GBC1/IO20RSB0   |  |  |  |  |  |

| 116        | GBC0/IO19RSB0   |  |  |  |  |  |

| 117        | VCCIB0          |  |  |  |  |  |

| 118        | GND             |  |  |  |  |  |

| 119        | VCC             |  |  |  |  |  |

| 120        | IO18RSB0        |  |  |  |  |  |

| 121        | IO17RSB0        |  |  |  |  |  |

| 122        | IO16RSB0        |  |  |  |  |  |

| 123        | IO15RSB0        |  |  |  |  |  |

| 124        | IO14RSB0        |  |  |  |  |  |

| 125        | IO13RSB0        |  |  |  |  |  |

| 126        | IO12RSB0        |  |  |  |  |  |

| 127        | IO11RSB0        |  |  |  |  |  |

| 128        | NC              |  |  |  |  |  |

| 129        | IO10RSB0        |  |  |  |  |  |

| 130        | IO09RSB0        |  |  |  |  |  |

| 131        | IO08RSB0        |  |  |  |  |  |

| 132        | GAC1/IO07RSB0   |  |  |  |  |  |

| 133        | GAC0/IO06RSB0   |  |  |  |  |  |

| 134        | NC              |  |  |  |  |  |

| 135        | GND             |  |  |  |  |  |

| 136        | NC              |  |  |  |  |  |

| 137        | GAB1/IO05RSB0   |  |  |  |  |  |

| 138        | GAB0/IO04RSB0   |  |  |  |  |  |

| 139        | GAA1/IO03RSB0   |  |  |  |  |  |

| 140        | GAA0/IO02RSB0   |  |  |  |  |  |

| 141        | IO01RSB0        |  |  |  |  |  |

| 142        | IO00RSB0        |  |  |  |  |  |

| 143        | GNDQ            |  |  |  |  |  |

| 144        | VMV0            |  |  |  |  |  |

| PQ208      |                 | F          | PQ208           | PQ208      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P600 Function | Pin Number | A3P600 Function | Pin Number | A3P600 Function |  |

| 1          | GND             | 37         | IO152PDB3       | 73         | IO120RSB2       |  |

| 2          | GAA2/IO174PDB3  | 38         | IO152NDB3       | 74         | IO119RSB2       |  |

| 3          | IO174NDB3       | 39         | IO150PSB3       | 75         | IO118RSB2       |  |

| 4          | GAB2/IO173PDB3  | 40         | VCCIB3          | 76         | IO117RSB2       |  |

| 5          | IO173NDB3       | 41         | GND             | 77         | IO116RSB2       |  |

| 6          | GAC2/IO172PDB3  | 42         | IO147PDB3       | 78         | IO115RSB2       |  |

| 7          | IO172NDB3       | 43         | IO147NDB3       | 79         | IO114RSB2       |  |

| 8          | IO171PDB3       | 44         | GEC1/IO146PDB3  | 80         | IO112RSB2       |  |

| 9          | IO171NDB3       | 45         | GEC0/IO146NDB3  | 81         | GND             |  |

| 10         | IO170PDB3       | 46         | GEB1/IO145PDB3  | 82         | IO111RSB2       |  |

| 11         | IO170NDB3       | 47         | GEB0/IO145NDB3  | 83         | IO110RSB2       |  |

| 12         | IO169PDB3       | 48         | GEA1/IO144PDB3  | 84         | IO109RSB2       |  |

| 13         | IO169NDB3       | 49         | GEA0/IO144NDB3  | 85         | IO108RSB2       |  |

| 14         | IO168PDB3       | 50         | VMV3            | 86         | IO107RSB2       |  |

| 15         | IO168NDB3       | 51         | GNDQ            | 87         | IO106RSB2       |  |

| 16         | VCC             | 52         | GND             | 88         | VCC             |  |

| 17         | GND             | 53         | VMV2            | 89         | VCCIB2          |  |

| 18         | VCCIB3          | 54         | GEA2/IO143RSB2  | 90         | IO104RSB2       |  |

| 19         | IO166PDB3       | 55         | GEB2/IO142RSB2  | 91         | IO102RSB2       |  |

| 20         | IO166NDB3       | 56         | GEC2/IO141RSB2  | 92         | IO100RSB2       |  |

| 21         | GFC1/IO164PDB3  | 57         | IO140RSB2       | 93         | IO98RSB2        |  |

| 22         | GFC0/IO164NDB3  | 58         | IO139RSB2       | 94         | IO96RSB2        |  |

| 23         | GFB1/IO163PDB3  | 59         | IO138RSB2       | 95         | IO92RSB2        |  |

| 24         | GFB0/IO163NDB3  | 60         | IO137RSB2       | 96         | GDC2/IO91RSB2   |  |

| 25         | VCOMPLF         | 61         | IO136RSB2       | 97         | GND             |  |

| 26         | GFA0/IO162NPB3  | 62         | VCCIB2          | 98         | GDB2/IO90RSB2   |  |

| 27         | VCCPLF          | 63         | IO135RSB2       | 99         | GDA2/IO89RSB2   |  |

| 28         | GFA1/IO162PPB3  | 64         | IO133RSB2       | 100        | GNDQ            |  |

| 29         | GND             | 65         | GND             | 101        | ТСК             |  |

| 30         | GFA2/IO161PDB3  | 66         | IO131RSB2       | 102        | TDI             |  |

| 31         | IO161NDB3       | 67         | IO129RSB2       | 103        | TMS             |  |

| 32         | GFB2/IO160PDB3  | 68         | IO127RSB2       | 104        | VMV2            |  |

| 33         | IO160NDB3       | 69         | IO125RSB2       | 105        | GND             |  |

| 34         | GFC2/IO159PDB3  | 70         | IO123RSB2       | 106        | VPUMP           |  |

| 35         | IO159NDB3       | 71         | VCC             | 107        | GNDQ            |  |

| 36         | VCC             | 72         | VCCIB2          | 108        | TDO             |  |

| FG144      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P125 Function |  |  |  |

| K1         | GEB0/IO109RSB1  |  |  |  |

| K2         | GEA1/IO108RSB1  |  |  |  |

| K3         | GEA0/IO107RSB1  |  |  |  |

| K4         | GEA2/IO106RSB1  |  |  |  |

| K5         | IO100RSB1       |  |  |  |

| K6         | IO98RSB1        |  |  |  |

| K7         | GND             |  |  |  |

| K8         | IO73RSB1        |  |  |  |

| K9         | GDC2/IO72RSB1   |  |  |  |

| K10        | GND             |  |  |  |

| K11        | GDA0/IO66RSB0   |  |  |  |

| K12        | GDB0/IO64RSB0   |  |  |  |

| L1         | GND             |  |  |  |

| L2         | VMV1            |  |  |  |

| L3         | GEB2/IO105RSB1  |  |  |  |

| L4         | IO102RSB1       |  |  |  |

| L5         | VCCIB1          |  |  |  |

| L6         | IO95RSB1        |  |  |  |

| L7         | IO85RSB1        |  |  |  |

| L8         | IO74RSB1        |  |  |  |

| L9         | TMS             |  |  |  |

| L10        | VJTAG           |  |  |  |

| L11        | VMV1            |  |  |  |

| L12        | TRST            |  |  |  |

| M1         | GNDQ            |  |  |  |

| M2         | GEC2/IO104RSB1  |  |  |  |

| M3         | IO103RSB1       |  |  |  |

| M4         | IO101RSB1       |  |  |  |

| M5         | IO97RSB1        |  |  |  |

| M6         | IO94RSB1        |  |  |  |

| M7         | IO86RSB1        |  |  |  |

| M8         | IO75RSB1        |  |  |  |

| M9         | TDI             |  |  |  |

| M10        | VCCIB1          |  |  |  |

| M11        | VPUMP           |  |  |  |

| M12        | GNDQ            |  |  |  |

| FG256      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P250 Function |  |  |  |  |

| P9         | IO76RSB2        |  |  |  |  |

| P10        | IO71RSB2        |  |  |  |  |

| P11        | IO66RSB2        |  |  |  |  |

| P12        | NC              |  |  |  |  |

| P13        | ТСК             |  |  |  |  |

| P14        | VPUMP           |  |  |  |  |

| P15        | TRST            |  |  |  |  |

| P16        | GDA0/IO60VDB1   |  |  |  |  |

| R1         | GEA1/IO98PDB3   |  |  |  |  |

| R2         | GEA0/IO98NDB3   |  |  |  |  |

| R3         | NC              |  |  |  |  |

| R4         | GEC2/IO95RSB2   |  |  |  |  |

| R5         | IO91RSB2        |  |  |  |  |

| R6         | IO88RSB2        |  |  |  |  |

| R7         | IO84RSB2        |  |  |  |  |

| R8         | IO80RSB2        |  |  |  |  |

| R9         | IO77RSB2        |  |  |  |  |

| R10        | IO72RSB2        |  |  |  |  |

| R11        | IO68RSB2        |  |  |  |  |

| R12        | IO65RSB2        |  |  |  |  |

| R13        | GDB2/IO62RSB2   |  |  |  |  |

| R14        | TDI             |  |  |  |  |

| R15        | NC              |  |  |  |  |

| R16        | TDO             |  |  |  |  |

| T1         | GND             |  |  |  |  |

| T2         | IO94RSB2        |  |  |  |  |

| Т3         | GEB2/IO96RSB2   |  |  |  |  |

| T4         | IO93RSB2        |  |  |  |  |

| Τ5         | IO90RSB2        |  |  |  |  |

| Т6         | IO87RSB2        |  |  |  |  |

| Τ7         | IO83RSB2        |  |  |  |  |

| Т8         | IO79RSB2        |  |  |  |  |

| Т9         | IO78RSB2        |  |  |  |  |

| T10        | IO73RSB2        |  |  |  |  |

| T11        | IO70RSB2        |  |  |  |  |

| T12        | GDC2/IO63RSB2   |  |  |  |  |

| FG256      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P250 Function |  |  |  |  |

| T13        | IO67RSB2        |  |  |  |  |

| T14        | GDA2/IO61RSB2   |  |  |  |  |

| T15        | TMS             |  |  |  |  |

| T16        | GND             |  |  |  |  |

# 🌜 Microsemi.

Package Pin Assignments

| FG256      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P400 Function |  |  |  |  |

| P9         | IO98RSB2        |  |  |  |  |

| P10        | IO95RSB2        |  |  |  |  |

| P11        | IO88RSB2        |  |  |  |  |

| P12        | IO84RSB2        |  |  |  |  |

| P13        | ТСК             |  |  |  |  |

| P14        | VPUMP           |  |  |  |  |

| P15        | TRST            |  |  |  |  |

| P16        | GDA0/IO79VDB1   |  |  |  |  |

| R1         | GEA1/IO135PDB3  |  |  |  |  |

| R2         | GEA0/IO135NDB3  |  |  |  |  |

| R3         | IO127RSB2       |  |  |  |  |

| R4         | GEC2/IO132RSB2  |  |  |  |  |

| R5         | IO123RSB2       |  |  |  |  |

| R6         | IO118RSB2       |  |  |  |  |

| R7         | IO112RSB2       |  |  |  |  |

| R8         | IO106RSB2       |  |  |  |  |

| R9         | IO100RSB2       |  |  |  |  |

| R10        | IO96RSB2        |  |  |  |  |

| R11        | IO89RSB2        |  |  |  |  |

| R12        | IO85RSB2        |  |  |  |  |

| R13        | GDB2/IO81RSB2   |  |  |  |  |

| R14        | TDI             |  |  |  |  |

| R15        | NC              |  |  |  |  |

| R16        | TDO             |  |  |  |  |

| T1         | GND             |  |  |  |  |

| T2         | IO126RSB2       |  |  |  |  |

| Т3         | GEB2/IO133RSB2  |  |  |  |  |

| T4         | IO124RSB2       |  |  |  |  |

| Т5         | IO116RSB2       |  |  |  |  |

| Т6         | IO113RSB2       |  |  |  |  |

| T7         | IO107RSB2       |  |  |  |  |

| Т8         | IO105RSB2       |  |  |  |  |

| Т9         | IO102RSB2       |  |  |  |  |

| T10        | IO97RSB2        |  |  |  |  |

| T11        | IO92RSB2        |  |  |  |  |

| T12        | GDC2/IO82RSB2   |  |  |  |  |

| FG256      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P400 Function |  |  |  |  |

| T13        | IO86RSB2        |  |  |  |  |

| T14        | GDA2/IO80RSB2   |  |  |  |  |

| T15        | TMS             |  |  |  |  |

| T16        | GND             |  |  |  |  |

| FG484      |                 | FG484      |                 |            | FG484           |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P400 Function | Pin Number | A3P400 Function | Pin Number | A3P400 Function |  |

| E21        | NC              | G13        | IO40RSB0        | J5         | IO149NPB3       |  |

| E22        | NC              | G14        | IO46RSB0        | J6         | IO09RSB0        |  |

| F1         | NC              | G15        | GNDQ            | J7         | IO152UDB3       |  |

| F2         | NC              | G16        | IO47RSB0        | J8         | VCCIB3          |  |

| F3         | NC              | G17        | GBB2/IO61PPB1   | J9         | GND             |  |

| F4         | IO154VDB3       | G18        | IO53RSB0        | J10        | VCC             |  |

| F5         | IO155VDB3       | G19        | IO63NDB1        | J11        | VCC             |  |

| F6         | IO11RSB0        | G20        | NC              | J12        | VCC             |  |

| F7         | IO07RSB0        | G21        | NC              | J13        | VCC             |  |

| F8         | GAC0/IO04RSB0   | G22        | NC              | J14        | GND             |  |

| F9         | GAC1/IO05RSB0   | H1         | NC              | J15        | VCCIB1          |  |

| F10        | IO20RSB0        | H2         | NC              | J16        | IO62NDB1        |  |

| F11        | IO24RSB0        | H3         | VCC             | J17        | IO49RSB0        |  |

| F12        | IO33RSB0        | H4         | IO150PDB3       | J18        | IO64PPB1        |  |

| F13        | IO39RSB0        | H5         | IO08RSB0        | J19        | IO66NDB1        |  |

| F14        | IO45RSB0        | H6         | IO153VDB3       | J20        | NC              |  |

| F15        | GBC0/IO54RSB0   | H7         | IO152VDB3       | J21        | NC              |  |

| F16        | IO48RSB0        | H8         | VMV0            | J22        | NC              |  |

| F17        | VMV0            | H9         | VCCIB0          | K1         | NC              |  |

| F18        | IO61NPB1        | H10        | VCCIB0          | K2         | NC              |  |

| F19        | IO63PDB1        | H11        | IO25RSB0        | K3         | NC              |  |

| F20        | NC              | H12        | IO31RSB0        | K4         | IO148NDB3       |  |

| F21        | NC              | H13        | VCCIB0          | K5         | IO148PDB3       |  |

| F22        | NC              | H14        | VCCIB0          | K6         | IO149PPB3       |  |

| G1         | NC              | H15        | VMV1            | K7         | GFC1/IO147PPB3  |  |

| G2         | NC              | H16        | GBC2/IO62PDB1   | K8         | VCCIB3          |  |

| G3         | NC              | H17        | IO65RSB1        | K9         | VCC             |  |

| G4         | IO151VDB3       | H18        | IO52RSB0        | K10        | GND             |  |

| G5         | IO151UDB3       | H19        | IO66PDB1        | K11        | GND             |  |

| G6         | GAC2/IO153UDB3  | H20        | VCC             | K12        | GND             |  |

| G7         | IO06RSB0        | H21        | NC              | K13        | GND             |  |

| G8         | GNDQ            | H22        | NC              | K14        | VCC             |  |

| G9         | IO10RSB0        | J1         | NC              | K15        | VCCIB1          |  |

| G10        | IO19RSB0        | J2         | NC              | K16        | GCC1/IO67PPB1   |  |

| G11        | IO26RSB0        | J3         | NC              | K17        | IO64NPB1        |  |

| G12        | IO30RSB0        | J4         | IO150NDB3       | K18        | IO73PDB1        |  |

| Revision                       | Changes                                                                                                                                                                                                | Page |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v2.0<br>(continued)            | Table 3-20 • Summary of I/O Timing Characteristics—Software Default Settings (Advanced) and Table 3-21 • Summary of I/O Timing Characteristics—Software Default Settings (Standard Plus) were updated. |      |

|                                | Table 3-11 • Different Components Contributing to Dynamic Power Consumptionin ProASIC3 Devices was updated.                                                                                            |      |

|                                | Table 3-24 • I/O Output Buffer Maximum Resistances1 (Advanced) and Tab25 • I/O Output Buffer Maximum Resistances1 (Standard Plus) were update                                                          |      |

|                                | Table 3-17 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions was updated.                                                                            | 3-18 |

|                                | Table 3-28 • I/O Short Currents IOSH/IOSL (Advanced) and Table 3-29 • I/O         Short Currents IOSH/IOSL (Standard Plus) were updated.                                                               |      |

|                                | The note in Table 3-32 • I/O Input Rise Time, Fall Time, and Related I/O Reliability was updated.                                                                                                      | 3-27 |

|                                | Figure 3-33 • Write Access After Write onto Same Address, Figure 3-34 • Read Access After Write onto Same Address, and Figure 3-35 • Write Access After Read onto Same Address are new.                |      |

|                                | Figure 3-43 • Timing Diagram was updated.                                                                                                                                                              | 3-96 |

|                                | Ambient was deleted from the "Speed Grade and Temperature Grade Matrix".                                                                                                                               | iv   |

|                                | Notes were added to the package diagrams identifying if they were top or bottom view.                                                                                                                  | N/A  |

|                                | The A3P030 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-2  |

|                                | The A3P060 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-4  |

|                                | The A3P125 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-6  |

|                                | The A3P250 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-8  |

|                                | The A3P030 "100-Pin VQFP" table is new.                                                                                                                                                                | 4-11 |

| Advance v0.7<br>(January 2007) | In the "I/Os Per Package" table, the I/O numbers were added for A3P060, A3P125, and A3P250. The A3P030-VQ100 I/O was changed from 79 to 77.                                                            | ii   |

| Advance v0.6<br>(April 2006)   | The term flow-through was changed to pass-through.                                                                                                                                                     | N/A  |

|                                | Table 1 was updated to include the QN132.                                                                                                                                                              | ii   |

|                                | The "I/Os Per Package" table was updated with the QN132. The footnotes were also updated. The A3P400-FG144 I/O count was updated.                                                                      | ii   |

|                                | "Automotive ProASIC3 Ordering Information" was updated with the QN132.                                                                                                                                 | iii  |

|                                | "Temperature Grade Offerings" was updated with the QN132.                                                                                                                                              | iii  |

|                                | B-LVDS and M-LDVS are new I/O standards added to the datasheet.                                                                                                                                        | N/A  |

|                                | The term flow-through was changed to pass-through.                                                                                                                                                     |      |

|                                | Figure 2-7 • Efficient Long-Line Resources was updated.                                                                                                                                                | 2-7  |

|                                | The footnotes in Figure 2-15 • Clock Input Sources Including CLKBUF, CLKBUF_LVDS/LVPECL, and CLKINT were updated.                                                                                      |      |

|                                | The Delay Increments in the Programmable Delay Blocks specification in Figure 2-24 • ProASIC3E CCC Options.                                                                                            | 2-24 |

|                                | The "SRAM and FIFO" section was updated.                                                                                                                                                               | 2-21 |

| Revision                     | Changes                                                   | Page      |

|------------------------------|-----------------------------------------------------------|-----------|

| Advance v0.2,<br>(continued) | Table 2-43 was updated.                                   | 2-64      |

|                              | Table 2-18 was updated.                                   | 2-45      |

|                              | Pin descriptions in the "JTAG Pins" section were updated. | 2-51      |

|                              | The "User I/O Naming Convention" section was updated.     | 2-48      |

|                              | Table 3-7 was updated.                                    | 3-6       |

|                              | The "Methodology" section was updated.                    | 3-10      |

|                              | Table 3-40 and Table 3-39 were updated.                   | 3-33,3-32 |

|                              | The A3P250 "100-Pin VQFP*" pin table was updated.         | 4-14      |

|                              | The A3P250 "208-Pin PQFP*" pin table was updated.         | 4-23      |

|                              | The A3P1000 "208-Pin PQFP*" pin table was updated.        | 4-29      |

|                              | The A3P250 "144-Pin FBGA*" pin table was updated.         | 4-36      |

|                              | The A3P1000 "144-Pin FBGA*" pin table was updated.        | 4-32      |

|                              | The A3P250 "256-Pin FBGA*" pin table was updated.         | 4-45      |

|                              | The A3P1000 "256-Pin FBGA*" pin table was updated.        | 4-54      |

|                              | The A3P1000 "484-Pin FBGA*" pin table was updated.        | 4-68      |