Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2012.02                        |                                                                        |

|--------------------------------|------------------------------------------------------------------------|

| Product Status                 | Active                                                                 |

| Number of LABs/CLBs            | -                                                                      |

| Number of Logic Elements/Cells | -                                                                      |

| Total RAM Bits                 | 55296                                                                  |

| Number of I/O                  | 178                                                                    |

| Number of Gates                | 400000                                                                 |

| Voltage - Supply               | 1.425V ~ 1.575V                                                        |

| Mounting Type                  | Surface Mount                                                          |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                        |

| Package / Case                 | 256-LBGA                                                               |

| Supplier Device Package        | 256-FPBGA (17x17)                                                      |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p400-fg256 |

|                                |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Advanced Flash Technology**

The ProASIC3 family offers many benefits, including nonvolatility and reprogrammability through an advanced flashbased, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

## **Advanced Architecture**

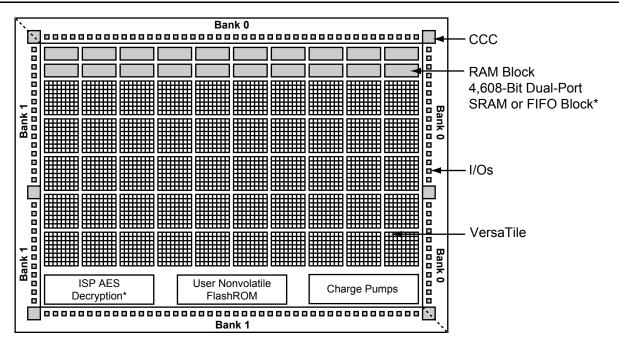

The proprietary ProASIC3 architecture provides granularity comparable to standard-cell ASICs. The ProASIC3 device consists of five distinct and programmable architectural features (Figure 1-1 and Figure 1-2 on page 1-4):

- FPGA VersaTiles

- Dedicated FlashROM

- Dedicated SRAM/FIFO memory<sup>†</sup>

- Extensive CCCs and PLLs<sup>†</sup>

- Advanced I/O structure

*Note:* \*Not supported by A3P015 and A3P030 devices

*†* The A3P015 and A3P030 do not support PLL or SRAM.

The CCC block has these key features:

- Wide input frequency range (f<sub>IN CCC</sub>) = 1.5 MHz to 350 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz to 350 MHz

- Clock delay adjustment via programmable and fixed delays from -7.56 ns to +11.12 ns

- 2 programmable delay types for clock skew minimization

- Clock frequency synthesis (for PLL only)

Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°. Output phase shift depends on the output divider configuration (for PLL only).

- Output duty cycle = 50% ± 1.5% or better (for PLL only)

- Low output jitter: worst case < 2.5% × clock period peak-to-peak period jitter when single global network used (for PLL only)

- Maximum acquisition time = 300 µs (for PLL only)

- Low power consumption of 5 mW

- Exceptional tolerance to input period jitter— allowable input jitter is up to 1.5 ns (for PLL only)

- Four precise phases; maximum misalignment between adjacent phases of 40 ps × (350 MHz / f<sub>OUT\_CCC</sub>) (for PLL only)

### **Global Clocking**

ProASIC3 devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high fanout nets.

Microsemi

Power Matters."

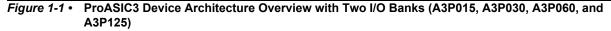

*Note: HTR time is the period during which you would not expect a verify failure due to flash cell leakage. Figure 2-1* • **High-Temperature Data Retention (HTR)**

| Tabl | e 2-3 • | Flash Program | ning Limits | <ul> <li>Retention,</li> </ul> | , Storage and | Operating | Temperature <sup>1</sup> | 1 |

|------|---------|---------------|-------------|--------------------------------|---------------|-----------|--------------------------|---|

|      |         |               |             |                                |               |           |                          |   |

| Product<br>Grade | Programming<br>Cycles | Program Retention<br>(biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) | Maximum Operating Junction Temperature $T_J (°C)^2$ |

|------------------|-----------------------|----------------------------------------|------------------------------------------------------|-----------------------------------------------------|

| Commercial       | 500                   | 20 years                               | 110                                                  | 100                                                 |

| Industrial       | 500                   | 20 years                               | 110                                                  | 100                                                 |

This is a stress rating only; functional operation at any condition other than those indicated is not implied.

These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

| VCCI and VMV  | Average VCCI–GND Overshoot or Undershoot<br>Duration as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                              | 1.4 V                                         |

|               | 5%                                                                                               | 1.49 V                                        |

| 3 V           | 10%                                                                                              | 1.1 V                                         |

| Γ Γ           | 5%                                                                                               | 1.19 V                                        |

| 3.3 V         | 10%                                                                                              | 0.79 V                                        |

| Γ             | 5%                                                                                               | 0.88 V                                        |

| 3.6 V         | 10%                                                                                              | 0.45 V                                        |

|               | 5%                                                                                               | 0.54 V                                        |

Table 2-4 • Overshoot and Undershoot Limits 1

Notes:

1. Based on reliability requirements at 85°C.

2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

3. This table does not provide PCI overshoot/undershoot limits.

#### Table 2-13 • Summary of I/O Output Buffer Power (Per Pin) – Default I/O Software Settings <sup>1</sup> Applicable to Standard I/O Banks

|                                      | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|--------------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                         |                        |          |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 35                     | 3.3      | -                                      | 431.08                                       |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 35                     | 3.3      | -                                      | 431.08                                       |

| 2.5 V LVCMOS                         | 35                     | 2.5      | -                                      | 247.36                                       |

| 1.8 V LVCMOS                         | 35                     | 1.8      | -                                      | 128.46                                       |

| 1.5 V LVCMOS (JESD8-11)              | 35                     | 1.5      | -                                      | 89.46                                        |

Notes:

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2. P<sub>DC3</sub> is the static power (where applicable) measured on VCCI.

3. P<sub>AC10</sub> is the total dynamic power measured on VCC and VCCI.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

# **Power Consumption of Various Internal Resources**

Table 2-14 • Different Components Contributing to Dynamic Power Consumption in ProASIC3 Devices

|           |                                                                | 14.50 12.80 12.80 11.00 11.00 9.30 9.30 9 |        |        |        |        |        |        |        |

|-----------|----------------------------------------------------------------|-------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Parameter | Definition                                                     | A3P1000                                   | A3P600 | A3P400 | A3P250 | A3P125 | A3P060 | A3P030 | A3P015 |

| PAC1      | Clock contribution of a Global Rib                             | 14.50                                     | 12.80  | 12.80  | 11.00  | 11.00  | 9.30   | 9.30   | 9.30   |

| PAC2      | Clock contribution of a Global Spine                           | 2.48                                      | 1.85   | 1.35   | 1.58   | 0.81   | 0.81   | 0.41   | 0.41   |

| PAC3      | Clock contribution of a VersaTile row                          |                                           | •      |        | 0.8    | 1      |        |        |        |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  |                                           |        |        | 0.1    | 2      |        |        |        |

| PAC5      | First contribution of a VersaTile used as a sequential module  | 0.07                                      |        |        |        |        |        |        |        |

| PAC6      | Second contribution of a VersaTile used as a sequential module | 0.29                                      |        |        |        |        |        |        |        |

| PAC7      | Contribution of a VersaTile used as a<br>combinatorial Module  |                                           |        |        | 0.2    | 9      |        |        |        |

| PAC8      | Average contribution of a routing net                          |                                           |        |        | 0.7    | 0      |        |        |        |

| PAC9      | Contribution of an I/O input pin (standard dependent)          |                                           | See    |        |        |        |        | gh     |        |

| PAC10     | Contribution of an I/O output pin (standard dependent)         |                                           | See    |        |        |        |        | gh     |        |

| PAC11     | Average contribution of a RAM block during a read operation    | 25.00                                     |        |        |        |        |        |        |        |

| PAC12     | Average contribution of a RAM block during a write operation   | 30.00                                     |        |        |        |        |        |        |        |

| PAC13     | Dynamic contribution for PLL                                   |                                           |        |        | 2.6    | 0      |        |        |        |

*Note:* \*For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi Power spreadsheet calculator or SmartPower tool in Libero SoC software.

|           | Definition                                       | Device Specific Static Power (mW)                              |                                                              |        |        |        |        |        |        |

|-----------|--------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Parameter |                                                  | A3P1000                                                        | A3P600                                                       | A3P400 | A3P250 | A3P125 | A3P060 | A3P030 | A3P015 |

| PDC1      | Array static power in Active mode                | See Table 2-7 on page 2-7.                                     |                                                              |        |        |        |        |        |        |

| PDC2      | I/O input pin static power (standard-dependent)  |                                                                | See Table 2-8 on page 2-7 through<br>Table 2-10 on page 2-8. |        |        |        |        |        |        |

| PDC3      | I/O output pin static power (standard-dependent) | See Table 2-11 on page 2-9 through<br>Table 2-13 on page 2-10. |                                                              |        |        |        |        |        |        |

| PDC4      | Static PLL contribution                          | 2.55 mW                                                        |                                                              |        |        |        |        |        |        |

| PDC5      | Bank quiescent power (VCCI-dependent)            | See Table 2-7 on page 2-7.                                     |                                                              |        |        |        |        |        |        |

#### Table 2-15 • Different Components Contributing to the Static Power Consumption in ProASIC3 Devices

*Note:* \*For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi Power spreadsheet calculator or SmartPower tool in Libero SoC software.

# **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs as well as the number and the frequency of each output clock generated

- · The number of combinatorial and sequential cells used in the design

- · The internal clock frequencies

- The number and the standard of I/O pins used in the design

- · The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-16 on page 2-14.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-17 on page 2-14.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-17 on page 2-14. The calculation should be repeated for each clock domain defined in the design.

#### Methodology

#### Total Power Consumption—PTOTAL

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

$P_{STAT} = P_{DC1} + N_{INPUTS} + P_{DC2} + N_{OUTPUTS} + P_{DC3}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

#### Total Dynamic Power Consumption—P<sub>DYN</sub>

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub>

#### Global Clock Contribution—P<sub>CLOCK</sub>

$P_{CLOCK} = (P_{AC1} + N_{SPINE}*P_{AC2} + N_{ROW}*P_{AC3} + N_{S-CELL}*P_{AC4})*F_{CLK}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3 FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3 FPGA Fabric User's Guide*.

#### RAM Contribution—P<sub>MEMORY</sub>

$\mathsf{P}_{\mathsf{MEMORY}} = \mathsf{P}_{\mathsf{AC11}} * \mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{F}_{\mathsf{READ-CLOCK}} * \beta_2 + \mathsf{P}_{\mathsf{AC12}} * \mathsf{N}_{\mathsf{BLOCK}} * \mathsf{F}_{\mathsf{WRITE-CLOCK}} * \beta_3$

$N_{\mbox{\scriptsize BLOCKS}}$  is the number of RAM blocks used in the design.

F<sub>READ-CLOCK</sub> is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations.

F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

$\beta_3$  is the RAM enable rate for write operations—guidelines are provided in Table 2-17 on page 2-14.

#### PLL Contribution—P<sub>PLL</sub>

$P_{PLL} = P_{DC4} + P_{AC13} * F_{CLKOUT}$

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

#### Guidelines

#### Toggle Rate Definition

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

#### Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

#### Table 2-16 • Toggle Rate Guidelines Recommended for Power Calculation

| Component      | Definition                       | Guideline |

|----------------|----------------------------------|-----------|

| $\alpha_1$     | Toggle rate of VersaTile outputs | 10%       |

| α <sub>2</sub> | I/O buffer toggle rate           | 10%       |

#### Table 2-17 • Enable Rate Guidelines Recommended for Power Calculation

| Component      | Definition                           | Guideline |

|----------------|--------------------------------------|-----------|

| β <sub>1</sub> | I/O output buffer enable rate        | 100%      |

| β <sub>2</sub> | RAM enable rate for read operations  | 12.5%     |

| β <sub>3</sub> | RAM enable rate for write operations | 12.5%     |

The PLL dynamic contribution depends on the input clock frequency, the number of output clock signals generated by the PLL, and the frequency of each output clock. If a PLL is used to generate more than one output clock, include each output clock in the formula by adding its corresponding contribution (P<sub>AC14</sub> \* F<sub>CLKOUT</sub> product) to the total PLL contribution.

|                   | Applica        | ble to St         | andard          | Plus I/          | J Bank          | S                 |                 |                 |                 |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 4 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 6 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 8 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 12 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

| 16 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

Table 2-44 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-45 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | -1             | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 4 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | –1             | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 6 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | –1             | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2             | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 8 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1             | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

#### Table 2-93 • Minimum and Maximum DC Input and Output Levels

| DC Parameter | Description                    | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

|--------------|--------------------------------|-------|------|-------|------|-------|------|-------|

| VCCI         | Supply Voltage                 | 3.    | .0   | 3     | .3   | 3     | 3.6  |       |

| VOL          | Output Low Voltage             | 0.96  | 1.27 | 1.06  | 1.43 | 1.30  | 1.57 | V     |

| VOH          | Output High Voltage            | 1.8   | 2.11 | 1.92  | 2.28 | 2.13  | 2.41 | V     |

| VIL, VIH     | Input Low, Input High Voltages | 0     | 3.6  | 0     | 3.6  | 0     | 3.6  | V     |

| VODIFF       | Differential Output Voltage    | 0.625 | 0.97 | 0.625 | 0.97 | 0.625 | 0.97 | V     |

| VOCM         | Output Common-Mode Voltage     | 1.762 | 1.98 | 1.762 | 1.98 | 1.762 | 1.98 | V     |

| VICM         | Input Common-Mode Voltage      | 1.01  | 2.57 | 1.01  | 2.57 | 1.01  | 2.57 | V     |

| VIDIFF       | Input Differential Voltage     | 300   |      | 300   |      | 300   |      | mV    |

#### Table 2-94 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) |

|---------------|----------------|----------------------|

| 1.64          | 1.94           | Cross point          |

*Note:* \**Measuring point* =  $V_{trip.}$  See Table 2-22 on page 2-22 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-95 • LVPECL

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 1.80            | 0.04             | 1.40            | ns    |

| -1          | 0.56              | 1.53            | 0.04             | 1.19            | ns    |

| -2          | 0.49              | 1.34            | 0.03             | 1.05            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# Output Enable Register

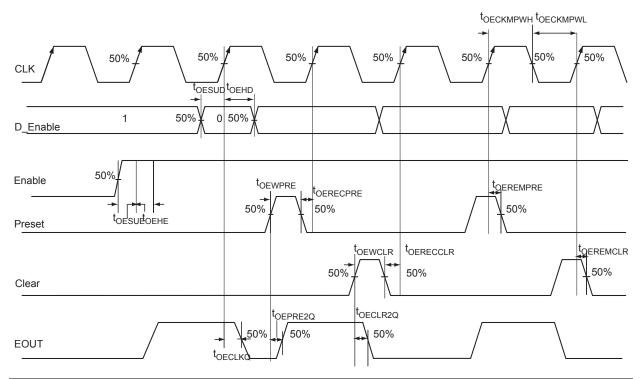

Figure 2-19 • Output Enable Register Timing Diagram

#### Timing Characteristics

#### Table 2-107 • A3P015 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2 -1             |                   | -1                | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.66              | 0.81              | 0.75              | 0.92              | 0.88              | 1.08              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.67              | 0.84              | 0.76              | 0.96              | 0.89              | 1.13              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.18              |                   | 0.21              |                   | 0.25              | ns    |

#### Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage-supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-108 • A3P030 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2                |                   | -1                |                   | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.67              | 0.81              | 0.76              | 0.92              | 0.89              | 1.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.68              | 0.85              | 0.77              | 0.97              | 0.91              | 1.14              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.18              |                   | 0.21              |                   | 0.24              | ns    |

#### Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# Table 2-119 • FIFO (for A3P250 only, aspect-ratio-dependent)Worst Commercial-Case Conditions: TJ = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.26 | 3.71 | 4.36 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

mode is not used in the design, the FF pin is available as a regular I/O. For IGLOOe, ProASIC3EL, and RT ProASIC3 only, the FF pin can be configured as a Schmitt trigger input.

When Flash\*Freeze mode is used, the FF pin must not be left floating to avoid accidentally entering Flash\*Freeze mode. While in Flash\*Freeze mode, the Flash\*Freeze pin should be constantly asserted.

The Flash\*Freeze pin can be used with any single-ended I/O standard supported by the I/O bank in which the pin is located, and input signal levels compatible with the I/O standard selected. The FF pin should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

# JTAG Pins

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the part must be supplied to allow JTAG signals to transition the device. Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND.

#### TCK Test Clock

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pull-up/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements. Refer to Table 1 for more information.

| VJTAG | Tie-Off Resistance |

|-------|--------------------|

| 3.3 V | 200 Ω –1 kΩ        |

| 2.5 V | 200 Ω –1 kΩ        |

| 1.8 V | 500 Ω –1 kΩ        |

| 1.5 V | 500 Ω –1 kΩ        |

#### Table 1 • Recommended Tie-Off Values for the TCK and TRST Pins

#### Notes:

- 1. Equivalent parallel resistance if more than one device is on the JTAG chain

- 2. The TCK pin can be pulled up/down.

- 3. The TRST pin is pulled down.

#### TDI Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

#### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE 1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the test access port (TAP) is held in reset mode. The resistor values must be chosen from Table 1 and must satisfy the parallel resistance value requirement. The values in Table 1 correspond to the resistor recommended when a single device is used, and the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

| TQ144      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P060 Function |  |  |  |

| 109        | NC              |  |  |  |

| 110        | NC              |  |  |  |

| 111        | GBA1/IO24RSB0   |  |  |  |

| 112        | GBA0/IO23RSB0   |  |  |  |

| 113        | GBB1/IO22RSB0   |  |  |  |

| 114        | GBB0/IO21RSB0   |  |  |  |

| 115        | GBC1/IO20RSB0   |  |  |  |

| 116        | GBC0/IO19RSB0   |  |  |  |

| 117        | VCCIB0          |  |  |  |

| 118        | GND             |  |  |  |

| 119        | VCC             |  |  |  |

| 120        | IO18RSB0        |  |  |  |

| 121        | IO17RSB0        |  |  |  |

| 122        | IO16RSB0        |  |  |  |

| 123        | IO15RSB0        |  |  |  |

| 124        | IO14RSB0        |  |  |  |

| 125        | IO13RSB0        |  |  |  |

| 126        | IO12RSB0        |  |  |  |

| 127        | IO11RSB0        |  |  |  |

| 128        | NC              |  |  |  |

| 129        | IO10RSB0        |  |  |  |

| 130        | IO09RSB0        |  |  |  |

| 131        | IO08RSB0        |  |  |  |

| 132        | GAC1/IO07RSB0   |  |  |  |

| 133        | GAC0/IO06RSB0   |  |  |  |

| 134        | NC              |  |  |  |

| 135        | GND             |  |  |  |

| 136        | NC              |  |  |  |

| 137        | GAB1/IO05RSB0   |  |  |  |

| 138        | GAB0/IO04RSB0   |  |  |  |

| 139        | GAA1/IO03RSB0   |  |  |  |

| 140        | GAA0/IO02RSB0   |  |  |  |

| 141        | IO01RSB0        |  |  |  |

| 142        | IO00RSB0        |  |  |  |

| 143        | GNDQ            |  |  |  |

| 144        | VMV0            |  |  |  |

Package Pin Assignments

# PQ208 – Top View

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

|            | PQ208           |            | PQ208           | PQ208      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P125 Function | Pin Number | A3P125 Function | Pin Number | A3P125 Function |

| 1          | GND             | 37         | IO116RSB1       | 73         | IO92RSB1        |

| 2          | GAA2/IO67RSB1   | 38         | IO115RSB1       | 74         | IO91RSB1        |

| 3          | IO68RSB1        | 39         | NC              | 75         | IO90RSB1        |

| 4          | GAB2/IO69RSB1   | 40         | VCCIB1          | 76         | IO89RSB1        |

| 5          | IO132RSB1       | 41         | GND             | 77         | IO88RSB1        |

| 6          | GAC2/IO131RSB1  | 42         | IO114RSB1       | 78         | IO87RSB1        |

| 7          | NC              | 43         | IO113RSB1       | 79         | IO86RSB1        |

| 8          | NC              | 44         | GEC1/IO112RSB1  | 80         | IO85RSB1        |

| 9          | IO130RSB1       | 45         | GEC0/IO111RSB1  | 81         | GND             |

| 10         | IO129RSB1       | 46         | GEB1/IO110RSB1  | 82         | IO84RSB1        |

| 11         | NC              | 47         | GEB0/IO109RSB1  | 83         | IO83RSB1        |

| 12         | IO128RSB1       | 48         | GEA1/IO108RSB1  | 84         | IO82RSB1        |

| 13         | NC              | 49         | GEA0/IO107RSB1  | 85         | IO81RSB1        |

| 14         | NC              | 50         | VMV1            | 86         | IO80RSB1        |

| 15         | NC              | 51         | GNDQ            | 87         | IO79RSB1        |

| 16         | VCC             | 52         | GND             | 88         | VCC             |

| 17         | GND             | 53         | NC              | 89         | VCCIB1          |

| 18         | VCCIB1          | 54         | NC              | 90         | IO78RSB1        |

| 19         | IO127RSB1       | 55         | GEA2/IO106RSB1  | 91         | IO77RSB1        |

| 20         | NC              | 56         | GEB2/IO105RSB1  | 92         | IO76RSB1        |

| 21         | GFC1/IO126RSB1  | 57         | GEC2/IO104RSB1  | 93         | IO75RSB1        |

| 22         | GFC0/IO125RSB1  | 58         | IO103RSB1       | 94         | IO74RSB1        |

| 23         | GFB1/IO124RSB1  | 59         | IO102RSB1       | 95         | IO73RSB1        |

| 24         | GFB0/IO123RSB1  | 60         | IO101RSB1       | 96         | GDC2/IO72RSB1   |

| 25         | VCOMPLF         | 61         | IO100RSB1       | 97         | GND             |

| 26         | GFA0/IO122RSB1  | 62         | VCCIB1          | 98         | GDB2/IO71RSB1   |

| 27         | VCCPLF          | 63         | IO99RSB1        | 99         | GDA2/IO70RSB1   |

| 28         | GFA1/IO121RSB1  | 64         | IO98RSB1        | 100        | GNDQ            |

| 29         | GND             | 65         | GND             | 101        | ТСК             |

| 30         | GFA2/IO120RSB1  | 66         | IO97RSB1        | 102        | TDI             |

| 31         | NC              | 67         | IO96RSB1        | 103        | TMS             |

| 32         | GFB2/IO119RSB1  | 68         | IO95RSB1        | 104        | VMV1            |

| 33         | NC              | 69         | IO94RSB1        | 105        | GND             |

| 34         | GFC2/IO118RSB1  | 70         | IO93RSB1        | 106        | VPUMP           |

| 35         | IO117RSB1       | 71         | VCC             | 107        | NC              |

| 36         | NC              | 72         | VCCIB1          | 108        | TDO             |

| FG144      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P600 Function |  |  |  |  |

| K1         | GEB0/IO145NDB3  |  |  |  |  |

| K2         | GEA1/IO144PDB3  |  |  |  |  |

| K3         | GEA0/IO144NDB3  |  |  |  |  |

| K4         | GEA2/IO143RSB2  |  |  |  |  |

| K5         | IO119RSB2       |  |  |  |  |

| K6         | IO111RSB2       |  |  |  |  |

| K7         | GND             |  |  |  |  |

| K8         | IO94RSB2        |  |  |  |  |

| K9         | GDC2/IO91RSB2   |  |  |  |  |

| K10        | GND             |  |  |  |  |

| K11        | GDA0/IO88NDB1   |  |  |  |  |

| K12        | GDB0/IO87NDB1   |  |  |  |  |

| L1         | GND             |  |  |  |  |

| L2         | VMV3            |  |  |  |  |

| L3         | GEB2/IO142RSB2  |  |  |  |  |

| L4         | IO136RSB2       |  |  |  |  |

| L5         | VCCIB2          |  |  |  |  |

| L6         | IO115RSB2       |  |  |  |  |

| L7         | IO103RSB2       |  |  |  |  |

| L8         | IO97RSB2        |  |  |  |  |

| L9         | TMS             |  |  |  |  |

| L10        | VJTAG           |  |  |  |  |

| L11        | VMV2            |  |  |  |  |

| L12        | TRST            |  |  |  |  |

| M1         | GNDQ            |  |  |  |  |

| M2         | GEC2/IO141RSB2  |  |  |  |  |

| M3         | IO138RSB2       |  |  |  |  |

| M4         | IO123RSB2       |  |  |  |  |

| M5         | IO126RSB2       |  |  |  |  |

| M6         | IO134RSB2       |  |  |  |  |

| M7         | IO108RSB2       |  |  |  |  |

| M8         | IO99RSB2        |  |  |  |  |

| M9         | TDI             |  |  |  |  |

| M10        | VCCIB2          |  |  |  |  |

| M11        | VPUMP           |  |  |  |  |

| M12        | GNDQ            |  |  |  |  |

| Revision                                    | Changes                                                                                                                                                                                                                                      | Page   |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Revision 9 (Oct 2009)<br>Product Brief v1.3 | The CS121 package was added to table under "Features and Benefits" section, the "I/Os Per Package 1" table, Table 1 • ProASIC3 FPGAs Package Sizes Dimensions, "ProASIC3 Ordering Information", and the "Temperature Grade Offerings" table. | I – IV |

|                                             | "ProASIC3 Ordering Information" was revised to include the fact that some RoHS compliant packages are halogen-free.                                                                                                                          | IV     |

| Packaging v1.5                              | The "CS121 – Bottom View" figure and pin table for A3P060 are new.                                                                                                                                                                           | 4-15   |

| Revision 8 (Aug 2009)<br>Product Brief v1.2 | All references to M7 devices (CoreMP7) and speed grade –F were removed from this document.                                                                                                                                                   | N/A    |

|                                             | Table 1-1 I/O Standards supported is new.                                                                                                                                                                                                    | 1-7    |

|                                             | The I/Os with Advanced I/O Standards section was revised to add definitions of hot-swap and cold-sparing.                                                                                                                                    | 1-7    |

| DC and Switching<br>Characteristics v1.4    | $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS Wide Range support was added to the datasheet. This affects all tables that contained $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS data.                                                              | N/A    |

|                                             | $\rm I_{\rm IL}$ and $\rm I_{\rm IH}$ input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                            | N/A    |

|                                             | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                   | N/A    |

|                                             | The notes in Table 2-2 • Recommended Operating Conditions 1 were updated.                                                                                                                                                                    | 2-2    |

|                                             | Table 2-4 • Overshoot and Undershoot Limits 1 was updated.                                                                                                                                                                                   | 2-3    |

|                                             | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays was updated.                                                                                                                                                          | 2-6    |

|                                             | In Table 2-116 • RAM4K9, the following specifications were removed:<br>t <sub>WRO</sub><br>t <sub>CCKH</sub>                                                                                                                                 | 2-96   |

|                                             | In Table 2-117 • RAM512X18, the following specifications were removed:<br>t <sub>WRO</sub><br>t <sub>CCKH</sub>                                                                                                                              | 2-97   |

|                                             | In the title of Table 2-74 • 1.8 V LVCMOS High Slew, VCCI had a typo. It was changed from 3.0 V to 1.7 V.                                                                                                                                    | 2-58   |

| Revision 7 (Feb 2009)<br>Product Brief v1.1 | The "Advanced I/O" section was revised to add a bullet regarding wide range power supply voltage support.                                                                                                                                    | I      |

|                                             | The table under "Features and Benefits" section, was updated to include a value for typical equivalent macrocells for A3P250.                                                                                                                | I      |

|                                             | The QN48 package was added to the following tables: the table under "Features<br>and Benefits" section, "I/Os Per Package 1" "ProASIC3 FPGAs Package Sizes<br>Dimensions", and "Temperature Grade Offerings".                                | N/A    |

|                                             | The number of singled-ended I/Os for QN68 was added to the "I/Os Per Package 1" table.                                                                                                                                                       |        |

|                                             | The Wide Range I/O Support section is new.                                                                                                                                                                                                   | 1-7    |

| Revision 6 (Dec 2008)                       | The "QN48 – Bottom View" section is new.                                                                                                                                                                                                     | 4-1    |

| Packaging v1.4                              | The "QN68" pin table for A3P030 is new.                                                                                                                                                                                                      | 4-5    |

Datasheet Information

| Revision     | Changes                                                                                                                       | Page             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|

| Advance v0.3 | The "PLL Macro" section was updated. EXTFB information was removed from this section.                                         | 2-15             |

|              | The CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> was updated in Table 2-<br>11 • ProASIC3 CCC/PLL Specification | 2-29             |

|              | EXTFB was removed from Figure 2-27 • CCC/PLL Macro.                                                                           | 2-28             |

|              | Table 2-13 • ProASIC3 I/O Features was updated.                                                                               | 2-30             |

|              | The "Hot-Swap Support" section was updated.                                                                                   | 2-33             |

|              | The "Cold-Sparing Support" section was updated.                                                                               | 2-34             |

|              | "Electrostatic Discharge (ESD) Protection" section was updated.                                                               | 2-35             |

|              | The LVPECL specification in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices was updated.   | 2-64             |

|              | In the Bank 1 area of Figure 2-72, VMV2 was changed to VMV1 and VCCIB2 was changed to VCC_IB1.                                | 2-97             |

|              | The VJTAG and I/O pin descriptions were updated in the "Pin Descriptions" section.                                            | 2-50             |

|              | The "JTAG Pins" section was updated.                                                                                          | 2-51             |

|              | "128-Bit AES Decryption" section was updated to include M7 device information.                                                | 2-53             |

|              | Table 3-6 was updated.                                                                                                        | 3-6              |

|              | Table 3-7 was updated.                                                                                                        | 3-6              |

|              | In Table 3-11, PAC4 was updated.                                                                                              | 3-93-8           |

|              | Table 3-20 was updated.                                                                                                       | 3-20             |

|              | The note in Table 3-32 was updated.                                                                                           | 3-27             |

|              | All Timing Characteristics tables were updated from LVTTL to Register Delays                                                  | 3-31 to 3-<br>73 |

|              | The Timing Characteristics for RAM4K9, RAM512X18, and FIFO were updated.                                                      | 3-85 to<br>3-90  |

|              | F <sub>TCKMAX</sub> was updated in Table 3-110.                                                                               | 3-97             |

| Advance v0.2 | Figure 2-11 was updated.                                                                                                      | 2-9              |

|              | The "Clock Resources (VersaNets)" section was updated.                                                                        | 2-9              |

|              | The "VersaNet Global Networks and Spine Access" section was updated.                                                          | 2-9              |

|              | The "PLL Macro" section was updated.                                                                                          | 2-15             |

|              | Figure 2-27 was updated.                                                                                                      | 2-28             |

|              | Figure 2-20 was updated.                                                                                                      | 2-19             |

|              | Table 2-5 was updated.                                                                                                        | 2-25             |

|              | Table 2-6 was updated.                                                                                                        | 2-25             |

|              | The "FIFO Flag Usage Considerations" section was updated.                                                                     | 2-27             |

|              | Table 2-13 was updated.                                                                                                       | 2-30             |

|              | Figure 2-24 was updated.                                                                                                      | 2-31             |

|              | The "Cold-Sparing Support" section is new.                                                                                    | 2-34             |

# **Datasheet Categories**

#### Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "ProASIC3 Device Status" table on page IV, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

#### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

#### Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

### Unmarked (production)

This version contains information that is considered to be final.

### **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.