Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 110592                                                                   |

| Number of I/O                  | 177                                                                      |

| Number of Gates                | 600000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                       |

| Package / Case                 | 256-LBGA                                                                 |

| Supplier Device Package        | 256-FPBGA (17x17)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p600-1fg256i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

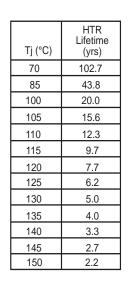

Note: HTR time is the period during which you would not expect a verify failure due to flash cell leakage.

Figure 2-1 • High-Temperature Data Retention (HTR)

Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature<sup>1</sup>

| Product<br>Grade | Programming<br>Cycles | Program Retention (biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) | Maximum Operating<br>Junction Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|------------------|-----------------------|-------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|

| Commercial       | 500                   | 20 years                            | 110                                                  | 100                                                                        |

| Industrial       | 500                   | 20 years                            | 110                                                  | 100                                                                        |

- This is a stress rating only; functional operation at any condition other than those indicated is not implied.

These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

Table 2-4 • Overshoot and Undershoot Limits 1

| VCCI and VMV  | Average VCCI–GND Overshoot or Undershoot<br>Duration as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                              | 1.4 V                                         |

|               | 5%                                                                                               | 1.49 V                                        |

| 3 V           | 10%                                                                                              | 1.1 V                                         |

|               | 5%                                                                                               | 1.19 V                                        |

| 3.3 V         | 10%                                                                                              | 0.79 V                                        |

|               | 5%                                                                                               | 0.88 V                                        |

| 3.6 V         | 10%                                                                                              | 0.45 V                                        |

|               | 5%                                                                                               | 0.54 V                                        |

#### Notes:

- 1. Based on reliability requirements at 85°C.

- 2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

- 3. This table does not provide PCI overshoot/undershoot limits.

2-3 Revision 18

## **Calculating Power Dissipation**

## **Quiescent Supply Current**

Table 2-7 • Quiescent Supply Current Characteristics

|                   | A3P015 | A3P030 | A3P060 | A3P125 | A3P250 | A3P400 | A3P600 | A3P1000 |

|-------------------|--------|--------|--------|--------|--------|--------|--------|---------|

| Typical (25°C)    | 2 mA   | 2 mA   | 2 mA   | 2 mA   | 3 mA   | 3 mA   | 5 mA   | 8 mA    |

| Max. (Commercial) | 10 mA  | 10 mA  | 10 mA  | 10 mA  | 20 mA  | 20 mA  | 30 mA  | 50 mA   |

| Max. (Industrial) | 15 mA  | 15 mA  | 15 mA  | 15 mA  | 30 mA  | 30 mA  | 45 mA  | 75 mA   |

Note: IDD Includes VCC, VPUMP, VCCI, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-11 and Table 2-12 on page 2-9.

## Power per I/O Pin

Table 2-8 • Summary of I/O Input Buffer Power (Per Pin) – Default I/O Software Settings Applicable to Advanced I/O Banks

|                                      | VMV (V) | Static Power<br>P <sub>DC2</sub> (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (μW/MHz) <sup>2</sup> |

|--------------------------------------|---------|----------------------------------------------------|---------------------------------------------|

| Single-Ended                         |         |                                                    |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 3.3     | _                                                  | 16.22                                       |

| 3.3 V LVCMOS Wide Range <sup>3</sup> | 3.3     | -                                                  | 16.22                                       |

| 2.5 V LVCMOS                         | 2.5     | _                                                  | 5.12                                        |

| 1.8 V LVCMOS                         | 1.8     | _                                                  | 2.13                                        |

| 1.5 V LVCMOS (JESD8-11)              | 1.5     | -                                                  | 1.45                                        |

| 3.3 V PCI                            | 3.3     | -                                                  | 18.11                                       |

| 3.3 V PCI-X                          | 3.3     | _                                                  | 18.11                                       |

| Differential                         | l.      | •                                                  |                                             |

| LVDS                                 | 2.5     | 2.26                                               | 1.20                                        |

| LVPECL                               | 3.3     | 5.72                                               | 1.87                                        |

### Notes:

- 1. PDC2 is the static power (where applicable) measured on VMV.

- 2. PAC9 is the total dynamic power measured on VCC and VMV.

- All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

Table 2-9 • Summary of I/O Input Buffer Power (Per Pin) – Default I/O Software Settings Applicable to Standard Plus I/O Banks

|                                      | VMV (V) | Static Power<br>PDC2 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (μW/MHz) <sup>2</sup> |

|--------------------------------------|---------|----------------------------------------|---------------------------------------------|

| Single-Ended                         |         | •                                      |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 3.3     | _                                      | 16.23                                       |

| 3.3 V LVCMOS Wide Range <sup>3</sup> | 3.3     | _                                      | 16.23                                       |

#### Notes:

- 1. PDC2 is the static power (where applicable) measured on VMV.

- 2. PAC9 is the total dynamic power measured on VCC and VMV.

- All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

2-7 Revision 18

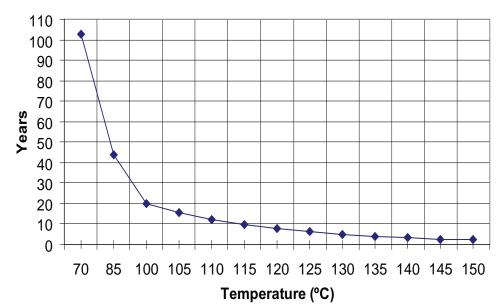

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (Example)

## Summary of I/O Timing Characteristics – Default I/O Software Settings

## Table 2-22 • Summary of AC Measuring Points

| Standard                   | Measuring Trip Point (V <sub>trip</sub> ) |

|----------------------------|-------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 1.4 V                                     |

| 3.3 V LVCMOS Wide Range    | 1.4 V                                     |

| 2.5 V LVCMOS               | 1.2 V                                     |

| 1.8 V LVCMOS               | 0.90 V                                    |

| 1.5 V LVCMOS               | 0.75 V                                    |

| 3.3 V PCI                  | 0.285 * VCCI (RR)                         |

|                            | 0.615 * VCCI (FF)                         |

| 3.3 V PCI-X                | 0.285 * VCCI (RR)                         |

|                            | 0.615 * VCCI (FF)                         |

## Table 2-23 • I/O AC Parameter Definitions

| Parameter         | Parameter Definition                                                        |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer                                  |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| $t_{LZ}$          | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

Table 2-44 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

|                   | Applica        | DIE 10 31         | aiiuaiu         | rius in          | Dank            | .3                |                 |                 |                 |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 4 mA              | Std.           | 0.66              | 9.68            | 0.04             | 1.00            | 0.43              | 9.86            | 8.42            | 2.28            | 2.21            | 12.09            | 10.66            | ns    |

|                   | -1             | 0.56              | 8.23            | 0.04             | 0.85            | 0.36              | 8.39            | 7.17            | 1.94            | 1.88            | 10.29            | 9.07             | ns    |

|                   | -2             | 0.49              | 7.23            | 0.03             | 0.75            | 0.32              | 7.36            | 6.29            | 1.70            | 1.65            | 9.03             | 7.96             | ns    |

| 6 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 8 mA              | Std.           | 0.66              | 6.70            | 0.04             | 1.00            | 0.43              | 6.82            | 5.89            | 2.58            | 2.74            | 9.06             | 8.12             | ns    |

|                   | -1             | 0.56              | 5.70            | 0.04             | 0.85            | 0.36              | 5.80            | 5.01            | 2.20            | 2.33            | 7.71             | 6.91             | ns    |

|                   | -2             | 0.49              | 5.00            | 0.03             | 0.75            | 0.32              | 5.10            | 4.40            | 1.93            | 2.05            | 6.76             | 6.06             | ns    |

| 12 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

| 16 mA             | Std.           | 0.66              | 5.05            | 0.04             | 1.00            | 0.43              | 5.14            | 4.51            | 2.79            | 3.08            | 7.38             | 6.75             | ns    |

|                   | -1             | 0.56              | 4.29            | 0.04             | 0.85            | 0.36              | 4.37            | 3.84            | 2.38            | 2.62            | 6.28             | 5.74             | ns    |

|                   | -2             | 0.49              | 3.77            | 0.03             | 0.75            | 0.32              | 3.84            | 3.37            | 2.09            | 2.30            | 5.51             | 5.04             | ns    |

|                   |                |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-45 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | -1             | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 4 mA              | Std.           | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | <b>–</b> 1     | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2             | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 6 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | <b>–</b> 1     | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2             | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 8 mA              | Std.           | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1             | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

2-37 Revision 18

Table 2-45 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

|                   | -2             | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-46 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 9.46            | 0.04             | 1.00            | 0.43              | 9.64            | 8.54            | 2.07            | 2.04            | ns    |

|                   | <b>–</b> 1     | 0.56              | 8.05            | 0.04             | 0.85            | 0.36              | 8.20            | 7.27            | 1.76            | 1.73            | ns    |

|                   | -2             | 0.49              | 7.07            | 0.03             | 0.75            | 0.32              | 7.20            | 6.38            | 1.55            | 1.52            | ns    |

| 4 mA              | Std.           | 0.66              | 9.46            | 0.04             | 1.00            | 0.43              | 9.64            | 8.54            | 2.07            | 2.04            | ns    |

|                   | <b>–</b> 1     | 0.56              | 8.05            | 0.04             | 0.85            | 0.36              | 8.20            | 7.27            | 1.76            | 1.73            | ns    |

|                   | -2             | 0.49              | 7.07            | 0.03             | 0.75            | 0.32              | 7.20            | 6.38            | 1.55            | 1.52            | ns    |

| 6 mA              | Std.           | 0.66              | 6.57            | 0.04             | 1.00            | 0.43              | 6.69            | 5.98            | 2.40            | 2.57            | ns    |

|                   | <b>–</b> 1     | 0.56              | 5.59            | 0.04             | 0.85            | 0.36              | 5.69            | 5.09            | 2.04            | 2.19            | ns    |

|                   | -2             | 0.49              | 4.91            | 0.03             | 0.75            | 0.32              | 5.00            | 4.47            | 1.79            | 1.92            | ns    |

| 8 mA              | Std.           | 0.66              | 6.57            | 0.04             | 1.00            | 0.43              | 6.69            | 5.98            | 2.40            | 2.57            | ns    |

|                   | <b>–</b> 1     | 0.56              | 5.59            | 0.04             | 0.85            | 0.36              | 5.69            | 5.09            | 2.04            | 2.19            | ns    |

|                   | -2             | 0.49              | 4.91            | 0.03             | 0.75            | 0.32              | 5.00            | 4.47            | 1.79            | 1.92            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-49 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard I/O Banks

| 3.3 V<br>LVCMOS<br>Wide Range | Equiv.<br>Software<br>Default            |          | TL.      | ٧        | ΊΗ       | VOL      | VOH       | IOL | ЮН  | IOSL                   | IOSH                   | IIL <sup>2</sup>        | IIH <sup>3</sup>        |

|-------------------------------|------------------------------------------|----------|----------|----------|----------|----------|-----------|-----|-----|------------------------|------------------------|-------------------------|-------------------------|

| Drive<br>Strength             | Drive<br>Strength<br>Option <sup>1</sup> | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V  | μΑ  | μΑ  | Max<br>mA <sup>4</sup> | Max<br>mA <sup>4</sup> | μ <b>Α</b> <sup>5</sup> | μ <b>Α</b> <sup>5</sup> |

| 100 μΑ                        | 2 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 25                     | 27                     | 10                      | 10                      |

| 100 μΑ                        | 4 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 25                     | 27                     | 10                      | 10                      |

| 100 μΑ                        | 6 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 51                     | 54                     | 10                      | 10                      |

| 100 μΑ                        | 8 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10                      | 10                      |

### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 4. Currents are measured at 85°C junction temperature.

- 5. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

- 6. Software default selection highlighted in gray.

### 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

Table 2-66 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

| 1.8 V<br>LVCMOS   |          | VIL         | VIH         |          | VOL      | VOH         | IOL | ЮН | IOSL                   | юзн                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|----------|-------------|-------------|----------|----------|-------------|-----|----|------------------------|------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V | Min<br>V    | mA  | mΑ | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 2   | 2  | 11                     | 9                      | 10                      | 10                      |

| 4 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 4   | 4  | 22                     | 17                     | 10                      | 10                      |

| 6 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 6   | 6  | 44                     | 35                     | 10                      | 10                      |

| 8 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 8   | 8  | 51                     | 45                     | 10                      | 10                      |

| 12 mA             | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 12  | 12 | 74                     | 91                     | 10                      | 10                      |

| 16 mA             | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 16  | 16 | 74                     | 91                     | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-67 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O I/O Banks

| 1.8 V<br>LVCMOS   | VIL      |             | VIH         |          | VOL      | VOH         | IOL | ЮН | IOSL                   | IOSH                   | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|----------|-------------|-------------|----------|----------|-------------|-----|----|------------------------|------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V | Min<br>V    | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI - 0.45 | 2   | 2  | 11                     | 9                      | 10                      | 10                      |

| 4 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI - 0.45 | 4   | 4  | 22                     | 17                     | 10                      | 10                      |

| 6 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI - 0.45 | 6   | 6  | 44                     | 35                     | 10                      | 10                      |

| 8 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI - 0.45 | 8   | 8  | 44                     | 35                     | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN <V CCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

2-53 Revision 18

Table 2-72 • 1.8 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

Applicable to Standard Plus I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zhs</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 11.33           | 0.04             | 1.20            | 0.43              | 8.72            | 11.33           | 2.24            | 1.52            | 10.96            | 13.57            | ns    |

|                   | <b>–</b> 1     | 0.56              | 9.64            | 0.04             | 1.02            | 0.36              | 7.42            | 9.64            | 1.91            | 1.29            | 9.32             | 11.54            | ns    |

|                   | -2             | 0.49              | 8.46            | 0.03             | 0.90            | 0.32              | 6.51            | 8.46            | 1.68            | 1.14            | 8.18             | 10.13            | ns    |

| 4 mA              | Std.           | 0.66              | 6.48            | 0.04             | 1.20            | 0.43              | 5.48            | 6.48            | 2.65            | 2.60            | 7.72             | 8.72             | ns    |

|                   | <b>–</b> 1     | 0.56              | 5.51            | 0.04             | 1.02            | 0.36              | 4.66            | 5.51            | 2.25            | 2.21            | 6.56             | 7.42             | ns    |

|                   | -2             | 0.49              | 4.84            | 0.03             | 0.90            | 0.32              | 4.09            | 4.84            | 1.98            | 1.94            | 5.76             | 6.51             | ns    |

| 6 mA              | Std.           | 0.66              | 4.06            | 0.04             | 1.20            | 0.43              | 3.84            | 4.06            | 2.93            | 3.10            | 6.07             | 6.30             | ns    |

|                   | -1             | 0.56              | 3.45            | 0.04             | 1.02            | 0.36              | 3.27            | 3.45            | 2.49            | 2.64            | 5.17             | 5.36             | ns    |

|                   | -2             | 0.49              | 3.03            | 0.03             | 0.90            | 0.32              | 2.87            | 3.03            | 2.19            | 2.32            | 4.54             | 4.70             | ns    |

| 8 mA              | Std.           | 0.66              | 4.06            | 0.04             | 1.20            | 0.43              | 3.84            | 4.06            | 2.93            | 3.10            | 6.07             | 6.30             | ns    |

|                   | -1             | 0.56              | 3.45            | 0.04             | 1.02            | 0.36              | 3.27            | 3.45            | 2.49            | 2.64            | 5.17             | 5.36             | ns    |

|                   | -2             | 0.49              | 3.03            | 0.03             | 0.90            | 0.32              | 2.87            | 3.03            | 2.19            | 2.32            | 4.54             | 4.70             | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-57 Revision 18

Table 2-81 • 1.5 V LVCMOS Low Slew Commercial-Case Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Advanced I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 12.78           | 0.04             | 1.44            | 0.43              | 12.81           | 12.78           | 3.40            | 2.64            | 15.05            | 15.02            | ns    |

|                   | <b>–</b> 1     | 0.56              | 10.87           | 0.04             | 1.22            | 0.36              | 10.90           | 10.87           | 2.89            | 2.25            | 12.80            | 12.78            | ns    |

|                   | -2             | 0.49              | 9.55            | 0.03             | 1.07            | 0.32              | 9.57            | 9.55            | 2.54            | 1.97            | 11.24            | 11.22            | ns    |

| 4 mA              | Std.           | 0.66              | 10.01           | 0.04             | 1.44            | 0.43              | 10.19           | 9.55            | 3.75            | 3.27            | 12.43            | 11.78            | ns    |

|                   | <b>–</b> 1     | 0.56              | 8.51            | 0.04             | 1.22            | 0.36              | 8.67            | 8.12            | 3.19            | 2.78            | 10.57            | 10.02            | ns    |

|                   | -2             | 0.49              | 7.47            | 0.03             | 1.07            | 0.32              | 7.61            | 7.13            | 2.80            | 2.44            | 9.28             | 8.80             | ns    |

| 6 mA              | Std.           | 0.66              | 9.33            | 0.04             | 1.44            | 0.43              | 9.51            | 8.89            | 3.83            | 3.43            | 11.74            | 11.13            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.94            | 0.04             | 1.22            | 0.36              | 8.09            | 7.56            | 3.26            | 2.92            | 9.99             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.97            | 0.03             | 1.07            | 0.32              | 7.10            | 6.64            | 2.86            | 2.56            | 8.77             | 8.31             | ns    |

| 8 mA              | Std.           | 0.66              | 8.91            | 0.04             | 1.44            | 0.43              | 9.07            | 8.89            | 3.95            | 4.05            | 11.31            | 11.13            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.58            | 0.04             | 1.22            | 0.36              | 7.72            | 7.57            | 3.36            | 3.44            | 9.62             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.65            | 0.03             | 1.07            | 0.32              | 6.78            | 6.64            | 2.95            | 3.02            | 8.45             | 8.31             | ns    |

| 12 mA             | Std.           | 0.66              | 8.91            | 0.04             | 1.44            | 0.43              | 9.07            | 8.89            | 3.95            | 4.05            | 11.31            | 11.13            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.58            | 0.04             | 1.22            | 0.36              | 7.72            | 7.57            | 3.36            | 3.44            | 9.62             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.65            | 0.03             | 1.07            | 0.32              | 6.78            | 6.64            | 2.95            | 3.02            | 8.45             | 8.31             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-82 • 1.5 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V

Applicable to Standard Plus I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 7.83            | 0.04             | 1.42            | 0.43              | 6.42            | 7.83            | 2.71            | 2.55            | 8.65             | 10.07            | ns    |

|                   | -1             | 0.56              | 6.66            | 0.04             | 1.21            | 0.36              | 5.46            | 6.66            | 2.31            | 2.17            | 7.36             | 8.56             | ns    |

|                   | -2             | 0.49              | 5.85            | 0.03             | 1.06            | 0.32              | 4.79            | 5.85            | 2.02            | 1.90            | 6.46             | 7.52             | ns    |

| 4 mA              | Std.           | 0.66              | 4.84            | 0.04             | 1.42            | 0.43              | 4.49            | 4.84            | 3.03            | 3.13            | 6.72             | 7.08             | ns    |

|                   | -1             | 0.56              | 4.12            | 0.04             | 1.21            | 0.36              | 3.82            | 4.12            | 2.58            | 2.66            | 5.72             | 6.02             | ns    |

|                   | -2             | 0.49              | 3.61            | 0.03             | 1.06            | 0.32              | 3.35            | 3.61            | 2.26            | 2.34            | 5.02             | 5.28             | ns    |

### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Package Pin Assignments

| PQ208      |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| Pin Number | A3P600 Function |  |  |  |  |  |

| 109        | TRST            |  |  |  |  |  |

| 110        | VJTAG           |  |  |  |  |  |

| 111        | GDA0/IO88NDB1   |  |  |  |  |  |

| 112        | GDA1/IO88PDB1   |  |  |  |  |  |

| 113        | GDB0/IO87NDB1   |  |  |  |  |  |

| 114        | GDB1/IO87PDB1   |  |  |  |  |  |

| 115        | GDC0/IO86NDB1   |  |  |  |  |  |

| 116        | GDC1/IO86PDB1   |  |  |  |  |  |

| 117        | IO84NDB1        |  |  |  |  |  |

| 118        | IO84PDB1        |  |  |  |  |  |

| 119        | IO82NDB1        |  |  |  |  |  |

| 120        | IO82PDB1        |  |  |  |  |  |

| 121        | IO81PSB1        |  |  |  |  |  |

| 122        | GND             |  |  |  |  |  |

| 123        | VCCIB1          |  |  |  |  |  |

| 124        | IO77NDB1        |  |  |  |  |  |

| 125        | IO77PDB1        |  |  |  |  |  |

| 126        | NC              |  |  |  |  |  |

| 127        | IO74NDB1        |  |  |  |  |  |

| 128        | GCC2/IO74PDB1   |  |  |  |  |  |

| 129        | GCB2/IO73PSB1   |  |  |  |  |  |

| 130        | GND             |  |  |  |  |  |

| 131        | GCA2/IO72PSB1   |  |  |  |  |  |

| 132        | GCA1/IO71PDB1   |  |  |  |  |  |

| 133        | GCA0/IO71NDB1   |  |  |  |  |  |

| 134        | GCB0/IO70NDB1   |  |  |  |  |  |

| 135        | GCB1/IO70PDB1   |  |  |  |  |  |

| 136        | GCC0/IO69NDB1   |  |  |  |  |  |

| 137        | GCC1/IO69PDB1   |  |  |  |  |  |

| 138        | IO67NDB1        |  |  |  |  |  |

| 139        | IO67PDB1        |  |  |  |  |  |

| 140        | VCCIB1          |  |  |  |  |  |

| 141        | GND             |  |  |  |  |  |

| 142        | VCC             |  |  |  |  |  |

| 143        | IO65PSB1        |  |  |  |  |  |

| 144        | IO64NDB1        |  |  |  |  |  |

| PQ208      |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| Pin Number | A3P600 Function |  |  |  |  |  |

| 145        | IO64PDB1        |  |  |  |  |  |

| 146        | IO63NDB1        |  |  |  |  |  |

| 147        | IO63PDB1        |  |  |  |  |  |

| 148        | IO62NDB1        |  |  |  |  |  |

| 149        | GBC2/IO62PDB1   |  |  |  |  |  |

| 150        | IO61NDB1        |  |  |  |  |  |

| 151        | GBB2/IO61PDB1   |  |  |  |  |  |

| 152        | IO60NDB1        |  |  |  |  |  |

| 153        | GBA2/IO60PDB1   |  |  |  |  |  |

| 154        | VMV1            |  |  |  |  |  |

| 155        | GNDQ            |  |  |  |  |  |

| 156        | GND             |  |  |  |  |  |

| 157        | VMV0            |  |  |  |  |  |

| 158        | GBA1/IO59RSB0   |  |  |  |  |  |

| 159        | GBA0/IO58RSB0   |  |  |  |  |  |

| 160        | GBB1/IO57RSB0   |  |  |  |  |  |

| 161        | GBB0/IO56RSB0   |  |  |  |  |  |

| 162        | GND             |  |  |  |  |  |

| 163        | GBC1/IO55RSB0   |  |  |  |  |  |

| 164        | GBC0/IO54RSB0   |  |  |  |  |  |

| 165        | IO52RSB0        |  |  |  |  |  |

| 166        | IO50RSB0        |  |  |  |  |  |

| 167        | IO48RSB0        |  |  |  |  |  |

| 168        | IO46RSB0        |  |  |  |  |  |

| 169        | IO44RSB0        |  |  |  |  |  |

| 170        | VCCIB0          |  |  |  |  |  |

| 171        | VCC             |  |  |  |  |  |

| 172        | IO36RSB0        |  |  |  |  |  |

| 173        | IO35RSB0        |  |  |  |  |  |

| 174        | IO34RSB0        |  |  |  |  |  |

| 175        | IO33RSB0        |  |  |  |  |  |

| 176        | IO32RSB0        |  |  |  |  |  |

| 177        | IO31RSB0        |  |  |  |  |  |

| 178        | GND             |  |  |  |  |  |

| 179        | IO29RSB0        |  |  |  |  |  |

| 180        | IO28RSB0        |  |  |  |  |  |

| PQ208      |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| Pin Number | A3P600 Function |  |  |  |  |  |

| 181        | IO27RSB0        |  |  |  |  |  |

| 182        | IO26RSB0        |  |  |  |  |  |

| 183        | IO25RSB0        |  |  |  |  |  |

| 184        | IO24RSB0        |  |  |  |  |  |

| 185        | IO23RSB0        |  |  |  |  |  |

| 186        | VCCIB0          |  |  |  |  |  |

| 187        | VCC             |  |  |  |  |  |

| 188        | IO20RSB0        |  |  |  |  |  |

| 189        | IO19RSB0        |  |  |  |  |  |

| 190        | IO18RSB0        |  |  |  |  |  |

| 191        | IO17RSB0        |  |  |  |  |  |

| 192        | IO16RSB0        |  |  |  |  |  |

| 193        | IO14RSB0        |  |  |  |  |  |

| 194        | IO12RSB0        |  |  |  |  |  |

| 195        | GND             |  |  |  |  |  |

| 196        | IO10RSB0        |  |  |  |  |  |

| 197        | IO09RSB0        |  |  |  |  |  |

| 198        | IO08RSB0        |  |  |  |  |  |

| 199        | IO07RSB0        |  |  |  |  |  |

| 200        | VCCIB0          |  |  |  |  |  |

| 201        | GAC1/IO05RSB0   |  |  |  |  |  |

| 202        | GAC0/IO04RSB0   |  |  |  |  |  |

| 203        | GAB1/IO03RSB0   |  |  |  |  |  |

| 204        | GAB0/IO02RSB0   |  |  |  |  |  |

| 205        | GAA1/IO01RSB0   |  |  |  |  |  |

| 206        | GAA0/IO00RSB0   |  |  |  |  |  |

| 207        | GNDQ            |  |  |  |  |  |

| 208        | VMV0            |  |  |  |  |  |

4-36 Revision 18

## Datasheet Information

| Revision                                                    | Changes                                                                                                                                                                                                                                                                                                  | Page       |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 5 (Aug 2008) DC and Switching Characteristics v1.3 | TJ, Maximum Junction Temperature, was changed to 100° from 110° in the "Thermal Characteristics" section and EQ 1. The calculated result of Maximum Power Allowed has thus changed to 1.463 W from 1.951 W.                                                                                              | 2-6        |

|                                                             | Values for the A3P015 device were added to Table 2-7 • Quiescent Supply Current Characteristics.                                                                                                                                                                                                         | 2-7        |

|                                                             | Values for the A3P015 device were added to Table 2-14 • Different Components Contributing to Dynamic Power Consumption in ProASIC3 Devices. P <sub>AC14</sub> was removed. Table 2-15 • Different Components Contributing to the Static Power Consumption in ProASIC3 Devices is new.                    | 2-11, 2-12 |

|                                                             | The "PLL Contribution—PPLL" section was updated to change the $P_{PLL}$ formula from $P_{AC13} + P_{AC14} * F_{CLKOUT}$ to $P_{DC4} + P_{AC13} * F_{CLKOUT}$ .                                                                                                                                           | 2-14       |

|                                                             | Both fall and rise values were included for $t_{\text{DDRISUD}}$ and $t_{\text{DDRIHD}}$ in Table 2-102 • Input DDR Propagation Delays.                                                                                                                                                                  | 2-78       |

|                                                             | Table 2-107 • A3P015 Global Resource is new.                                                                                                                                                                                                                                                             | 2-86       |

|                                                             | The typical value for Delay Increments in Programmable Delay Blocks was changed from 160 to 200 in Table 2-115 • ProASIC3 CCC/PLL Specification.                                                                                                                                                         | 2-90       |

| Revision 4 (Jun 2008) DC and Switching Characteristics v1.2 | Table note references were added to Table 2-2 • Recommended Operating Conditions 1, and the order of the table notes was changed.                                                                                                                                                                        | 2-2        |

|                                                             | The title for Table 2-4 • Overshoot and Undershoot Limits 1 was modified to remove "as measured on quiet I/Os." Table note 1 was revised to remove "estimated SSO density over cycles." Table note 2 was revised to remove "refers only to overshoot/undershoot limits for simultaneous switching I/Os." | 2-3        |

|                                                             | The "Power per I/O Pin" section was updated to include 3 additional tables pertaining to input buffer power and output buffer power.                                                                                                                                                                     | 2-7        |

|                                                             | Table 2-29 • I/O Output Buffer Maximum Resistances 1 was revised to include values for 3.3 V PCI/PCI-X.                                                                                                                                                                                                  | 2-27       |

|                                                             | Table 2-90 • LVDS Minimum and Maximum DC Input and Output Levels was updated.                                                                                                                                                                                                                            | 2-66       |

| Revision 3 (Jun 2008) Packaging v1.3                        | Pin numbers were added to the "QN68 – Bottom View" package diagram. Note 2 was added below the diagram.                                                                                                                                                                                                  | 4-3        |

|                                                             | The "QN132 – Bottom View" package diagram was updated to include D1 to D4. In addition, note 1 was changed from top view to bottom view, and note 2 is new.                                                                                                                                              | 4-6        |

| Revision 2 (Feb 2008)<br>Product Brief v1.0                 | This document was divided into two sections and given a version number, starting at v1.0. The first section of the document includes features, benefits, ordering information, and temperature and speed grade offerings. The second section is a device family overview.                                | N/A        |

|                                                             | This document was updated to include A3P015 device information. QN68 is a new package that was added because it is offered in the A3P015. The following sections were updated:  "Features and Benefits"                                                                                                  | N/A        |

|                                                             | "ProASIC3 Ordering Information"                                                                                                                                                                                                                                                                          |            |

|                                                             | "Temperature Grade Offerings"                                                                                                                                                                                                                                                                            |            |

|                                                             | "ProASIC3 Flash Family FPGAs"                                                                                                                                                                                                                                                                            |            |

|                                                             | "A3P015 and A3P030" note                                                                                                                                                                                                                                                                                 |            |

|                                                             | Introduction and Overview (NA)                                                                                                                                                                                                                                                                           |            |

5-7 Revision 18

| Revision                       | Changes                                                                                                                                                                                                | Page            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| v2.0<br>(continued)            | Table 3-20 • Summary of I/O Timing Characteristics—Software Default Settings (Advanced) and Table 3-21 • Summary of I/O Timing Characteristics—Software Default Settings (Standard Plus) were updated. | 3-20 to<br>3-20 |

|                                | Table 3-11 • Different Components Contributing to Dynamic Power Consumption in ProASIC3 Devices was updated.                                                                                           | 3-9             |

|                                | Table 3-24 • I/O Output Buffer Maximum Resistances1 (Advanced) and Table 3-25 • I/O Output Buffer Maximum Resistances1 (Standard Plus) were updated.                                                   | 3-22 to<br>3-22 |

|                                | Table 3-17 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions was updated.                                                                            | 3-18            |

|                                | Table 3-28 • I/O Short Currents IOSH/IOSL (Advanced) and Table 3-29 • I/O Short Currents IOSH/IOSL (Standard Plus) were updated.                                                                       | 3-24 to<br>3-26 |

|                                | The note in Table 3-32 • I/O Input Rise Time, Fall Time, and Related I/O Reliability was updated.                                                                                                      | 3-27            |

|                                | Figure 3-33 • Write Access After Write onto Same Address, Figure 3-34 • Read Access After Write onto Same Address, and Figure 3-35 • Write Access After Read onto Same Address are new.                | 3-82 to<br>3-84 |

|                                | Figure 3-43 • Timing Diagram was updated.                                                                                                                                                              | 3-96            |

|                                | Ambient was deleted from the "Speed Grade and Temperature Grade Matrix".                                                                                                                               | iv              |

|                                | Notes were added to the package diagrams identifying if they were top or bottom view.                                                                                                                  | N/A             |

|                                | The A3P030 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-2             |

|                                | The A3P060 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-4             |

|                                | The A3P125 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-6             |

|                                | The A3P250 "132-Pin QFN" table is new.                                                                                                                                                                 | 4-8             |

|                                | The A3P030 "100-Pin VQFP" table is new.                                                                                                                                                                | 4-11            |

| Advance v0.7<br>(January 2007) | In the "I/Os Per Package" table, the I/O numbers were added for A3P060, A3P125, and A3P250. The A3P030-VQ100 I/O was changed from 79 to 77.                                                            | ii              |

| Advance v0.6<br>(April 2006)   | The term flow-through was changed to pass-through.                                                                                                                                                     | N/A             |

|                                | Table 1 was updated to include the QN132.                                                                                                                                                              | ii              |

|                                | The "I/Os Per Package" table was updated with the QN132. The footnotes were also updated. The A3P400-FG144 I/O count was updated.                                                                      | ii              |

|                                | "Automotive ProASIC3 Ordering Information" was updated with the QN132.                                                                                                                                 | iii             |

|                                | "Temperature Grade Offerings" was updated with the QN132.                                                                                                                                              | iii             |

|                                | B-LVDS and M-LDVS are new I/O standards added to the datasheet.                                                                                                                                        | N/A             |

|                                | The term flow-through was changed to pass-through.                                                                                                                                                     | N/A             |

|                                | Figure 2-7 • Efficient Long-Line Resources was updated.                                                                                                                                                | 2-7             |

|                                | The footnotes in Figure 2-15 • Clock Input Sources Including CLKBUF, CLKBUF_LVDS/LVPECL, and CLKINT were updated.                                                                                      | 2-16            |

|                                | The Delay Increments in the Programmable Delay Blocks specification in Figure 2-24 • ProASIC3E CCC Options.                                                                                            | 2-24            |

|                                | The "SRAM and FIFO" section was updated.                                                                                                                                                               | 2-21            |