# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 110592                                                                   |

| Number of I/O                  | 154                                                                      |

| Number of Gates                | 600000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 208-BFQFP                                                                |

| Supplier Device Package        | 208-PQFP (28x28)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p600-1pqg208 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 – ProASIC3 Device Family Overview

## **General Description**

ProASIC3, the third-generation family of Microsemi flash FPGAs, offers performance, density, and features beyond those of the ProASIC<sup>PLUS®</sup> family. Nonvolatile flash technology gives ProASIC3 devices the advantage of being a secure, low power, single-chip solution that is Instant On. ProASIC3 is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost. These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

ProASIC3 devices offer 1 kbit of on-chip, reprogrammable, nonvolatile FlashROM storage as well as clock conditioning circuitry based on an integrated phase-locked loop (PLL). The A3P015 and A3P030 devices have no PLL or RAM support. ProASIC3 devices have up to 1 million system gates, supported with up to 144 kbits of true dual-port SRAM and up to 300 user I/Os.

ProASIC3 devices support the ARM Cortex-M1 processor. The ARM-enabled devices have Microsemi ordering numbers that begin with M1A3P (Cortex-M1) and do not support AES decryption.

## **Flash Advantages**

#### Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAMbased FPGAs, flash-based ProASIC3 devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades with confidence that valuable intellectual property (IP) cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The ProASIC3 family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the ProASIC3 family a cost-effective ASIC replacement solution, especially for applications in the consumer, networking/ communications, computing, and avionics markets.

#### Security

The nonvolatile, flash-based ProASIC3 devices do not require a boot PROM, so there is no vulnerable external bitstream that can be easily copied. ProASIC3 devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

ProASIC3 devices utilize a 128-bit flash-based lock and a separate AES key to provide the highest level of protection in the FPGA industry for intellectual property and configuration data. In addition, all FlashROM data in ProASIC3 devices can be encrypted prior to loading, using the industry-leading AES-128 (FIPS192) bit block cipher encryption standard. The AES standard was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the 1977 DES standard. ProASIC3 devices have a built-in AES decryption engine and a flash-based AES key that make them the most comprehensive programmable logic device security solution available today. ProASIC3 devices with AES-based security provide a high level of protection for remote field updates over public networks such as the Internet, and are designed to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves.

ARM-enabled ProASIC3 devices do not support user-controlled AES security mechanisms. Since the ARM core must be protected at all times, AES encryption is always on for the core logic, so bitstreams are always encrypted. There is no user access to encryption for the FlashROM programming data.

Security, built into the FPGA fabric, is an inherent component of the ProASIC3 family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. The ProASIC3 family, with FlashLock and AES security, is unique in being highly resistant to both invasive and noninvasive attacks.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

P<sub>AC1</sub>, P<sub>AC2</sub>, P<sub>AC3</sub>, and P<sub>AC4</sub> are device-dependent.

### Sequential Cells Contribution—P<sub>S-CELL</sub>

$P_{S-CELL} = N_{S-CELL} * (P_{AC5} + \alpha_1 / 2 * P_{AC6}) * F_{CLK}$

$N_{S-CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-16 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

#### Combinatorial Cells Contribution—P<sub>C-CELL</sub>

$P_{C-CELL} = N_{C-CELL} * \alpha_1 / 2 * P_{AC7} * F_{CLK}$

$N_{C\mbox{-}C\mbox{-}E\mbox{-}L\mbox{-}L}$  is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-16 on page 2-14.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

#### Routing Net Contribution—P<sub>NET</sub>

$P_{NET} = (N_{S-CELL} + N_{C-CELL}) * \alpha_1 / 2 * P_{AC8} * F_{CLK}$

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-16 on page 2-14.

$F_{CLK}$  is the global clock signal frequency.

#### I/O Input Buffer Contribution—PINPUTS

$P_{INPUTS} = N_{INPUTS} * \alpha_2 / 2 * P_{AC9} * F_{CLK}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-16 on page 2-14.

$F_{CLK}$  is the global clock signal frequency.

#### I/O Output Buffer Contribution—POUTPUTS

$P_{OUTPUTS} = N_{OUTPUTS} * \alpha_2 / 2 * \beta_1 * P_{AC10} * F_{CLK}$

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-16 on page 2-14.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-17 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

## **User I/O Characteristics**

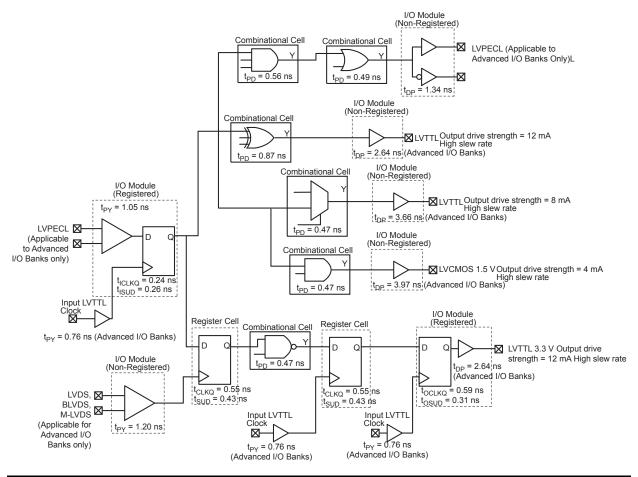

## **Timing Model**

|                                      | Drive Strength                 | IOSL (mA) <sup>1</sup>          | IOSH (mA) <sup>1</sup>          |

|--------------------------------------|--------------------------------|---------------------------------|---------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA                           | 27                              | 25                              |

|                                      | 4 mA                           | 27                              | 25                              |

|                                      | 6 mA                           | 54                              | 51                              |

|                                      | 8 mA                           | 54                              | 51                              |

|                                      | 12 mA                          | 109                             | 103                             |

|                                      | 16 mA                          | 127                             | 132                             |

|                                      | 24 mA                          | 181                             | 268                             |

| 3.3 V LVCMOS Wide Range <sup>2</sup> | 100 µA                         | Same as regular 3.3 V<br>LVCMOS | Same as regular 3.3 V<br>LVCMOS |

| 2.5 V LVCMOS                         | 2 mA                           | 18                              | 16                              |

|                                      | 4 mA                           | 18                              | 16                              |

|                                      | 6 mA                           | 37                              | 32                              |

|                                      | 8 mA                           | 37                              | 32                              |

|                                      | 12 mA                          | 74                              | 65                              |

|                                      | 16 mA                          | 87                              | 83                              |

|                                      | 24 mA                          | 124                             | 169                             |

| 1.8 V LVCMOS                         | 2 mA                           | 11                              | 9                               |

|                                      | 4 mA                           | 22                              | 17                              |

|                                      | 6 mA                           | 44                              | 35                              |

|                                      | 8 mA                           | 51                              | 45                              |

|                                      | 12 mA                          | 74                              | 91                              |

|                                      | 16 mA                          | 74                              | 91                              |

| 1.5 V LVCMOS                         | 2 mA                           | 16                              | 13                              |

|                                      | 4 mA                           | 33                              | 25                              |

|                                      | 6 mA                           | 39                              | 32                              |

|                                      | 8 mA                           | 55                              | 66                              |

|                                      | 12 mA                          | 55                              | 66                              |

| 3.3 V PCI/PCI-X                      | Per PCI/PCI-X<br>specification | 109                             | 103                             |

) Microsemi.

Power Matters."

Notes:

1.  $T_J = 100^{\circ}C$

Applicable to 3.3 V LVCMOS Wide Range. I<sub>OSL</sub>/I<sub>OSH</sub> dependent on the I/O buffer drive strength selected for wide range applications. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

### 3.3 V PCI, 3.3 V PCI-X

Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

| 3.3 V PCI/PCI-X       | V         | ΊL             | V         | IH        | VOL        | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|-----------------------|-----------|----------------|-----------|-----------|------------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive Strength        | Min.<br>V | Max.<br>V      | Min.<br>V | Max.<br>V | Max,.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| Per PCI specification |           | Per PCI curves |           |           |            | 10        | 10  |    |                         |                         |     |     |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-11.

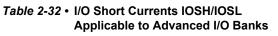

#### Figure 2-11 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the datapath; Microsemi loading for tristate is described in Table 2-87.

#### Table 2-87 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------------------|------------------------|

| 0             | 3.3            | 0.285 * VCCI for t <sub>DP(R)</sub> | 10                     |

|               |                | 0.615 * VCCI for t <sub>DP(F)</sub> |                        |

Note: \*Measuring point = V<sub>trip.</sub> See Table 2-22 on page 2-22 for a complete table of trip points.

#### **Timing Characteristics**

#### Table 2-88 • 3.3 V PCI/PCI-X

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/O Banks

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.66              | 2.68            | 0.04             | 0.86            | 0.43              | 2.73            | 1.95            | 3.21            | 3.58            | 4.97             | 4.19             | ns    |

| -1          | 0.56              | 2.28            | 0.04             | 0.73            | 0.36              | 2.32            | 1.66            | 2.73            | 3.05            | 4.22             | 3.56             | ns    |

| -2          | 0.49              | 2.00            | 0.03             | 0.65            | 0.32              | 2.04            | 1.46            | 2.40            | 2.68            | 3.71             | 3.13             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-89 • 3.3 V PCI/PCI-X

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard Plus I/O Banks

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.        | 0.66              | 2.31            | 0.04             | 0.85            | 0.43              | 2.35            | 1.70            | 2.79            | 3.22            | 4.59             | 3.94             | ns    |

| -1          | 0.56              | 1.96            | 0.04             | 0.72            | 0.36              | 2.00            | 1.45            | 2.37            | 2.74            | 3.90             | 3.35             | ns    |

| -2          | 0.49              | 1.72            | 0.03             | 0.64            | 0.32              | 1.76            | 1.27            | 2.08            | 2.41            | 3.42             | 2.94             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### **Differential I/O Characteristics**

#### Physical Implementation

Configuration of the I/O modules as a differential pair is handled by Microsemi Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

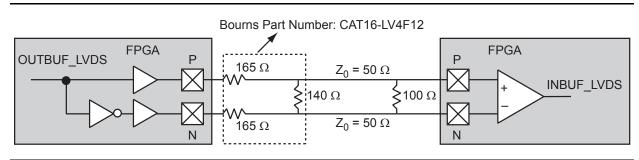

#### LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-12. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, ProASIC3 also supports Bus LVDS structure and Multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-12 • LVDS Circuit Diagram and Board-Level Implementation

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| tosue                 | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| toesud                | ESUD Data Setup Time for the Output Enable Register             |                                |

| t <sub>OEHD</sub>     |                                                                 |                                |

| tOESUE                | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   |                                                                 |                                |

| t <sub>IREMCLR</sub>  |                                                                 |                                |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

#### Table 2-97 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-16 on page 2-71 for more information.

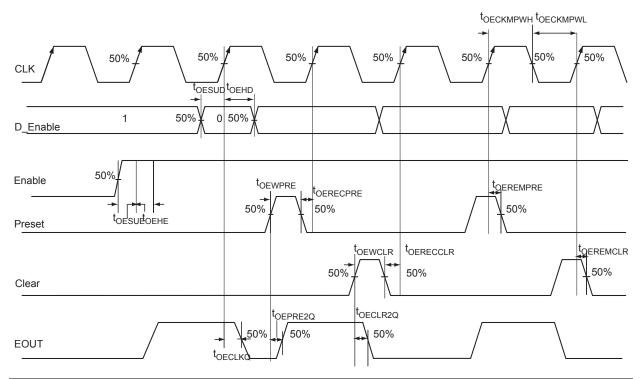

## Output Enable Register

Figure 2-19 • Output Enable Register Timing Diagram

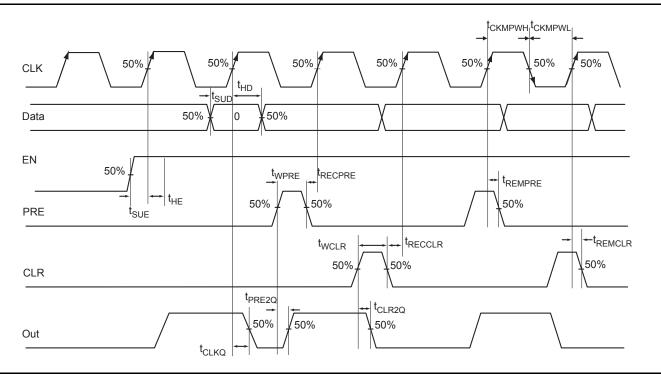

#### Figure 2-27 • Timing Model and Waveforms

#### **Timing Characteristics**

#### Table 2-106 • Register Delays

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -2   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.55 | 0.63 | 0.74 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.43 | 0.49 | 0.57 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.40 | 0.45 | 0.53 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.40 | 0.45 | 0.53 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.37 | 0.43 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.41 | 0.48 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

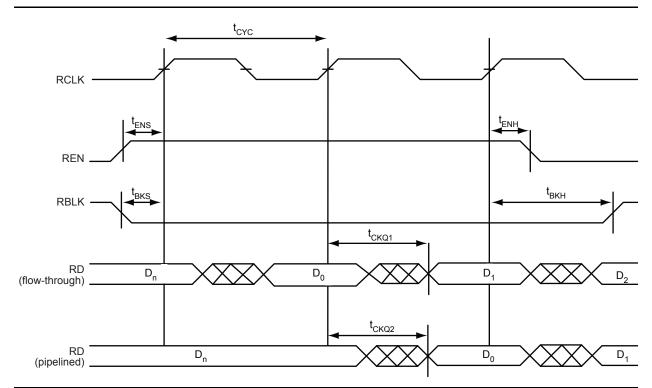

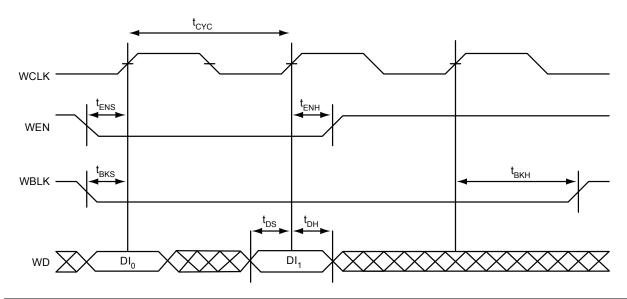

## Timing Waveforms

## **Timing Characteristics**

## Table 2-118 • FIFO (for all dies except A3P250)Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.34 | 1.52 | 1.79 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    |      | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Package Pin Assignments

|            | 2N68            |            | 2N68            |

|------------|-----------------|------------|-----------------|

| Pin Number | A3P015 Function | Pin Number | A3P015 Function |

| 1          | IO82RSB1        | 37         | TRST            |

| 2          | IO82R3B1        | 38         | VJTAG           |

| 3          |                 |            |                 |

| -          | IO78RSB1        | 39         | IO40RSB0        |

| 4          | IO76RSB1        | 40         | IO37RSB0        |

| 5          | GEC0/IO73RSB1   | 41         | GDB0/IO34RSB0   |

| 6          | GEA0/IO72RSB1   | 42         | GDA0/IO33RSB0   |

| 7          | GEB0/IO71RSB1   | 43         | GDC0/IO32RSB0   |

| 8          | VCC             | 44         | VCCIB0          |

| 9          | GND             | 45         | GND             |

| 10         | VCCIB1          | 46         | VCC             |

| 11         | IO68RSB1        | 47         | IO31RSB0        |

| 12         | IO67RSB1        | 48         | IO29RSB0        |

| 13         | IO66RSB1        | 49         | IO28RSB0        |

| 14         | IO65RSB1        | 50         | IO27RSB0        |

| 15         | IO64RSB1        | 51         | IO25RSB0        |

| 16         | IO63RSB1        | 52         | IO24RSB0        |

| 17         | IO62RSB1        | 53         | IO22RSB0        |

| 18         | IO60RSB1        | 54         | IO21RSB0        |

| 19         | IO58RSB1        | 55         | IO19RSB0        |

| 20         | IO56RSB1        | 56         | IO17RSB0        |

| 21         | IO54RSB1        | 57         | IO15RSB0        |

| 22         | IO52RSB1        | 58         | IO14RSB0        |

| 23         | IO51RSB1        | 59         | VCCIB0          |

| 24         | VCC             | 60         | GND             |

| 25         | GND             | 61         | VCC             |

| 26         | VCCIB1          | 62         | IO12RSB0        |

| 27         | IO50RSB1        | 63         | IO10RSB0        |

| 28         | IO48RSB1        | 64         | IO08RSB0        |

| 29         | IO46RSB1        | 65         | IO06RSB0        |

| 30         | IO44RSB1        | 66         | IO04RSB0        |

| 31         | IO42RSB1        | 67         | IO02RSB0        |

| 32         | ТСК             | 68         | IO00RSB0        |

| 33         | TDI             |            |                 |

| 34         | TMS             |            |                 |

| 35         | VPUMP           |            |                 |

|            |                 |            |                 |

TDO

36

|            | TQ144           |

|------------|-----------------|

| Pin Number | A3P125 Function |

| 109        | GBA1/IO40RSB0   |

| 110        | GBA0/IO39RSB0   |

| 111        | GBB1/IO38RSB0   |

| 112        | GBB0/IO37RSB0   |

| 113        | GBC1/IO36RSB0   |

| 114        | GBC0/IO35RSB0   |

| 115        | IO34RSB0        |

| 116        | IO33RSB0        |

| 117        | VCCIB0          |

| 118        | GND             |

| 119        | VCC             |

| 120        | IO29RSB0        |

| 121        | IO28RSB0        |

| 122        | IO27RSB0        |

| 123        | IO25RSB0        |

| 124        | IO23RSB0        |

| 125        | IO21RSB0        |

| 126        | IO19RSB0        |

| 127        | IO17RSB0        |

| 128        | IO16RSB0        |

| 129        | IO14RSB0        |

| 130        | IO12RSB0        |

| 131        | IO10RSB0        |

| 132        | IO08RSB0        |

| 133        | IO06RSB0        |

| 134        | VCCIB0          |

| 135        | GND             |

| 136        | VCC             |

| 137        | GAC1/IO05RSB0   |

| 138        | GAC0/IO04RSB0   |

| 139        | GAB1/IO03RSB0   |

| 140        | GAB0/IO02RSB0   |

| 141        | GAA1/IO01RSB0   |

| 142        | GAA0/IO00RSB0   |

| 143        | GNDQ            |

| 144        | VMV0            |

## 🌜 Microsemi.

Package Pin Assignments

|            | FG256           |            | FG256           |                         | FG256          |

|------------|-----------------|------------|-----------------|-------------------------|----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number A3P250 Funct |                |

| G13        | GCC1/IO48PPB1   | K1         | GFC2/IO105PDB3  | M5                      | VMV3           |

| G14        | IO47NPB1        | K2         | IO107NPB3       | M6                      | VCCIB2         |

| G15        | IO54PDB1        | K3         | IO104PPB3       | M7                      | VCCIB2         |

| G16        | IO54NDB1        | K4         | NC              | M8                      | NC             |

| H1         | GFB0/IO109NPB3  | K5         | VCCIB3          | M9                      | IO74RSB2       |

| H2         | GFA0/IO108NDB3  | K6         | VCC             | M10                     | VCCIB2         |

| H3         | GFB1/IO109PPB3  | K7         | GND             | M11                     | VCCIB2         |

| H4         | VCOMPLF         | K8         | GND             | M12                     | VMV2           |

| H5         | GFC0/IO110NPB3  | K9         | GND             | M13                     | NC             |

| H6         | VCC             | K10        | GND             | M14                     | GDB1/IO59UPB1  |

| H7         | GND             | K11        | VCC             | M15                     | GDC1/IO58UDB1  |

| H8         | GND             | K12        | VCCIB1          | M16                     | IO56NDB1       |

| H9         | GND             | K13        | IO52NPB1        | N1                      | IO103NDB3      |

| H10        | GND             | K14        | IO55RSB1        | N2                      | IO101PPB3      |

| H11        | VCC             | K15        | IO53NPB1        | N3                      | GEC1/IO100PPB3 |

| H12        | GCC0/IO48NPB1   | K16        | IO51NDB1        | N4                      | NC             |

| H13        | GCB1/IO49PPB1   | L1         | IO105NDB3       | N5                      | GNDQ           |

| H14        | GCA0/IO50NPB1   | L2         | IO104NPB3       | N6                      | GEA2/IO97RSB2  |

| H15        | NC              | L3         | NC              | N7                      | IO86RSB2       |

| H16        | GCB0/IO49NPB1   | L4         | IO102RSB3       | N8                      | IO82RSB2       |

| J1         | GFA2/IO107PPB3  | L5         | VCCIB3          | N9                      | IO75RSB2       |

| J2         | GFA1/IO108PDB3  | L6         | GND             | N10                     | IO69RSB2       |

| J3         | VCCPLF          | L7         | VCC             | N11                     | IO64RSB2       |

| J4         | IO106NDB3       | L8         | VCC             | N12                     | GNDQ           |

| J5         | GFB2/IO106PDB3  | L9         | VCC             | N13                     | NC             |

| J6         | VCC             | L10        | VCC             | N14                     | VJTAG          |

| J7         | GND             | L11        | GND             | N15                     | GDC0/IO58VDB1  |

| J8         | GND             | L12        | VCCIB1          | N16                     | GDA1/IO60UDB1  |

| J9         | GND             | L13        | GDB0/IO59VPB1   | P1                      | GEB1/IO99PDB3  |

| J10        | GND             | L14        | IO57VDB1        | P2                      | GEB0/IO99NDB3  |

| J11        | VCC             | L15        | IO57UDB1        | P3                      | NC             |

| J12        | GCB2/IO52PPB1   | L16        | IO56PDB1        | P4                      | NC             |

| J13        | GCA1/IO50PPB1   | M1         | IO103PDB3       | P5                      | IO92RSB2       |

| J14        | GCC2/IO53PPB1   | M2         | NC              | P6                      | IO89RSB2       |

| J15        | NC              | M3         | IO101NPB3       | P7                      | IO85RSB2       |

| J16        | GCA2/IO51PDB1   | M4         | GEC0/IO100NPB3  | P8                      | IO81RSB2       |

|            | FG256           |            | FG256           |                         | FG256          |

|------------|-----------------|------------|-----------------|-------------------------|----------------|

| Pin Number | A3P600 Function | Pin Number | A3P600 Function | Pin Number A3P600 Funct |                |

| A1         | GND             | C5         | GAC0/IO04RSB0   | E9                      | IO31RSB0       |

| A2         | GAA0/IO00RSB0   | C6         | GAC1/IO05RSB0   | E10                     | VCCIB0         |

| A3         | GAA1/IO01RSB0   | C7         | IO20RSB0        | E11                     | VCCIB0         |

| A4         | GAB0/IO02RSB0   | C8         | IO24RSB0        | E12                     | VMV1           |

| A5         | IO11RSB0        | C9         | IO33RSB0        | E13                     | GBC2/IO62PDB1  |

| A6         | IO16RSB0        | C10        | IO39RSB0        | E14                     | IO67PPB1       |

| A7         | IO18RSB0        | C11        | IO44RSB0        | E15                     | IO64PPB1       |

| A8         | IO28RSB0        | C12        | GBC0/IO54RSB0   | E16                     | IO66PDB1       |

| A9         | IO34RSB0        | C13        | IO51RSB0        | F1                      | IO166NDB3      |

| A10        | IO37RSB0        | C14        | VMV0            | F2                      | IO168NPB3      |

| A11        | IO41RSB0        | C15        | IO61NPB1        | F3                      | IO167PPB3      |

| A12        | IO43RSB0        | C16        | IO63PDB1        | F4                      | IO169PDB3      |

| A13        | GBB1/IO57RSB0   | D1         | IO171NDB3       | F5                      | VCCIB3         |

| A14        | GBA0/IO58RSB0   | D2         | IO171PDB3       | F6                      | GND            |

| A15        | GBA1/IO59RSB0   | D3         | GAC2/IO172PDB3  | F7                      | VCC            |

| A16        | GND             | D4         | IO06RSB0        | F8                      | VCC            |

| B1         | GAB2/IO173PDB3  | D5         | GNDQ            | F9                      | VCC            |

| B2         | GAA2/IO174PDB3  | D6         | IO10RSB0        | F10                     | VCC            |

| B3         | GNDQ            | D7         | IO19RSB0        | F11                     | GND            |

| B4         | GAB1/IO03RSB0   | D8         | IO26RSB0        | F12                     | VCCIB1         |

| B5         | IO13RSB0        | D9         | IO30RSB0        | F13                     | IO62NDB1       |

| B6         | IO14RSB0        | D10        | IO40RSB0        | F14                     | IO64NPB1       |

| B7         | IO21RSB0        | D11        | IO45RSB0        | F15                     | IO65PPB1       |

| B8         | IO27RSB0        | D12        | GNDQ            | F16                     | IO66NDB1       |

| B9         | IO32RSB0        | D13        | IO50RSB0        | G1                      | IO165NDB3      |

| B10        | IO38RSB0        | D14        | GBB2/IO61PPB1   | G2                      | IO165PDB3      |

| B11        | IO42RSB0        | D15        | IO53RSB0        | G3                      | IO168PPB3      |

| B12        | GBC1/IO55RSB0   | D16        | IO63NDB1        | G4                      | GFC1/IO164PPB3 |

| B13        | GBB0/IO56RSB0   | E1         | IO166PDB3       | G5                      | VCCIB3         |

| B14        | IO52RSB0        | E2         | IO167NPB3       | G6                      | VCC            |

| B15        | GBA2/IO60PDB1   | E3         | IO172NDB3       | G7                      | GND            |

| B16        | IO60NDB1        | E4         | IO169NDB3       | G8                      | GND            |

| C1         | IO173NDB3       | E5         | VMV0            | G9                      | GND            |

| C2         | IO174NDB3       | E6         | VCCIB0          | G10                     | GND            |

| C3         | VMV3            | E7         | VCCIB0          | G11                     | VCC            |

| C4         | IO07RSB0        | E8         | IO25RSB0        | G12                     | VCCIB1         |

## **Microsemi**

Package Pin Assignments

| FG484                      |           |  |  |  |

|----------------------------|-----------|--|--|--|

| Pin Number A3P400 Function |           |  |  |  |

| Y15                        | VCC       |  |  |  |

| Y16                        | NC        |  |  |  |

| Y17                        | NC        |  |  |  |

| Y18                        | GND       |  |  |  |

| Y19                        | NC        |  |  |  |

| Y20                        | NC        |  |  |  |

| Y21                        | NC        |  |  |  |

| Y22                        | VCCIB1    |  |  |  |

| AA1                        | GND       |  |  |  |

| AA2                        | VCCIB3    |  |  |  |

| AA3                        | NC        |  |  |  |

| AA4                        | NC        |  |  |  |

| AA5                        | NC        |  |  |  |

| AA6                        | NC        |  |  |  |

| AA7                        | NC        |  |  |  |

| AA8                        | NC        |  |  |  |

| AA9                        | NC        |  |  |  |

| AA10                       | NC        |  |  |  |

| AA11                       | NC        |  |  |  |

| AA12                       | NC        |  |  |  |

| AA13                       | NC        |  |  |  |

| AA14                       | NC        |  |  |  |

| AA15                       | NC        |  |  |  |

| AA16                       | NC        |  |  |  |

| AA17                       | NC        |  |  |  |

| AA18                       | NC        |  |  |  |

| AA19                       | NC        |  |  |  |

| AA20                       | NC        |  |  |  |

| AA21                       | VCCIB1    |  |  |  |

| AA22                       | GND       |  |  |  |

| AB1                        | GND       |  |  |  |

| AB2                        | GND       |  |  |  |

| AB3                        | VCCIB2    |  |  |  |

| AB4                        | NC        |  |  |  |

| AB5                        | NC        |  |  |  |

| AB6                        | IO121RSB2 |  |  |  |

| FG484      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A3P400 Function |  |  |

| AB7        | IO119RSB2       |  |  |

| AB8        | IO114RSB2       |  |  |

| AB9        | IO109RSB2       |  |  |

| AB10       | NC              |  |  |

| AB11       | NC              |  |  |

| AB12       | IO104RSB2       |  |  |

| AB13       | IO103RSB2       |  |  |

| AB14       | NC              |  |  |

| AB15       | NC              |  |  |

| AB16       | IO91RSB2        |  |  |

| AB17       | IO90RSB2        |  |  |

| AB18       | NC              |  |  |

| AB19       | NC              |  |  |

| AB20       | VCCIB2          |  |  |

| AB21       | GND             |  |  |

| AB22       | GND             |  |  |

## 🌜 Microsemi.

Package Pin Assignments

|            | FG484            |            | FG484            |                           | FG484          |

|------------|------------------|------------|------------------|---------------------------|----------------|

| Pin Number | A3P1000 Function | Pin Number | A3P1000 Function | Pin Number A3P1000 Functi |                |

| A1         | GND              | B15        | IO63RSB0         | D7                        | GAB0/IO02RSB0  |

| A2         | GND              | B16        | IO66RSB0         | D8                        | IO16RSB0       |

| A3         | VCCIB0           | B17        | IO68RSB0         | D9                        | IO22RSB0       |

| A4         | IO07RSB0         | B18        | IO70RSB0         | D10                       | IO28RSB0       |

| A5         | IO09RSB0         | B19        | NC               | D11                       | IO35RSB0       |

| A6         | IO13RSB0         | B20        | NC               | D12                       | IO45RSB0       |

| A7         | IO18RSB0         | B21        | VCCIB1           | D13                       | IO50RSB0       |

| A8         | IO20RSB0         | B22        | GND              | D14                       | IO55RSB0       |

| A9         | IO26RSB0         | C1         | VCCIB3           | D15                       | IO61RSB0       |

| A10        | IO32RSB0         | C2         | IO220PDB3        | D16                       | GBB1/IO75RSB0  |

| A11        | IO40RSB0         | C3         | NC               | D17                       | GBA0/IO76RSB0  |

| A12        | IO41RSB0         | C4         | NC               | D18                       | GBA1/IO77RSB0  |

| A13        | IO53RSB0         | C5         | GND              | D19                       | GND            |

| A14        | IO59RSB0         | C6         | IO10RSB0         | D20                       | NC             |

| A15        | IO64RSB0         | C7         | IO14RSB0         | D21                       | NC             |

| A16        | IO65RSB0         | C8         | VCC              | D22                       | NC             |

| A17        | IO67RSB0         | C9         | VCC              | E1                        | IO219NDB3      |

| A18        | IO69RSB0         | C10        | IO30RSB0         | E2                        | NC             |

| A19        | NC               | C11        | IO37RSB0         | E3                        | GND            |

| A20        | VCCIB0           | C12        | IO43RSB0         | E4                        | GAB2/IO224PDB3 |

| A21        | GND              | C13        | NC               | E5                        | GAA2/IO225PDB3 |

| A22        | GND              | C14        | VCC              | E6                        | GNDQ           |

| B1         | GND              | C15        | VCC              | E7                        | GAB1/IO03RSB0  |

| B2         | VCCIB3           | C16        | NC               | E8                        | IO17RSB0       |

| B3         | NC               | C17        | NC               | E9                        | IO21RSB0       |

| B4         | IO06RSB0         | C18        | GND              | E10                       | IO27RSB0       |

| B5         | IO08RSB0         | C19        | NC               | E11                       | IO34RSB0       |

| B6         | IO12RSB0         | C20        | NC               | E12                       | IO44RSB0       |

| B7         | IO15RSB0         | C21        | NC               | E13                       | IO51RSB0       |

| B8         | IO19RSB0         | C22        | VCCIB1           | E14                       | IO57RSB0       |

| B9         | IO24RSB0         | D1         | IO219PDB3        | E15                       | GBC1/IO73RSB0  |

| B10        | IO31RSB0         | D2         | IO220NDB3        | E16                       | GBB0/IO74RSB0  |

| B11        | IO39RSB0         | D3         | NC               | E17                       | IO71RSB0       |

| B12        | IO48RSB0         | D4         | GND              | E18                       | GBA2/IO78PDB1  |

| B13        | IO54RSB0         | D5         | GAA0/IO00RSB0    | E19                       | IO81PDB1       |

| B14        | IO58RSB0         | D6         | GAA1/IO01RSB0    | E20                       | GND            |

Datasheet Information

| Revision                    | Changes                                                                                                                                                                                                                                                                   | Page    |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Revision 11<br>(March 2012) | Note indicating that A3P015 is not recommended for new designs has been added. The "Devices Not Recommended For New Designs" section is new (SAR 36760).                                                                                                                  | I to IV |

|                             | The following sentence was removed from the Advanced Architecture section:<br>"In addition, extensive on-chip programming circuitry allows for rapid, single-<br>voltage (3.3 V) programming of IGLOO devices via an IEEE 1532 JTAG<br>interface" (SAR 34687).            | NA      |

|                             | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—PCLOCK" section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>ProASIC3 FPGA Fabric User's Guide</i> (SAR 34734). | 2-12    |

|                             | Figure 2-4 • Input Buffer Timing Model and Delays (Example) has been modified for the DIN waveform; the Rise and Fall time label has been changed to tDIN (35430).                                                                                                        | 2-16    |

|                             | The AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34883).                                                                 | 2-32    |

|                             | Added values for minimum pulse width and removed the FRMAX row from Table 2-107 through Table 2-114 in the "Global Tree Timing Characteristics" section. Use the software to determine the FRMAX for the device you are using (SARs 37279, 29269).                        | 2-85    |

| Revision                                                                 | Changes                                                                                                                                                                                                                                           | Page                   |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Revision 2 (cont'd)                                                      | The "ProASIC3 FPGAs Package Sizes Dimensions" table is new.                                                                                                                                                                                       | Ш                      |

|                                                                          | In the "ProASIC3 Ordering Information", the QN package measurements were updated to include both 0.4 mm and 0.5 mm.                                                                                                                               | IV                     |

|                                                                          | In the General Description section the number of I/Os was updated from 288 to 300.                                                                                                                                                                | 1-1                    |

| Packaging v1.2                                                           | The "QN68 – Bottom View" section is new.                                                                                                                                                                                                          | 4-3                    |

| <b>Revision 1 (Feb 2008)</b><br>DC and Switching<br>Characteristics v1.1 | In Table 2-2 • Recommended Operating Conditions 1, $T_J$ was listed in the symbol column and was incorrect. It was corrected and changed to $T_A$ .                                                                                               | 2-2                    |

|                                                                          | In Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature, Maximum Operating Junction Temperature was changed from 110°C to 100°C for both commercial and industrial grades.                                         | 2-3                    |

|                                                                          | The "PLL Behavior at Brownout Condition" section is new.                                                                                                                                                                                          | 2-4                    |

|                                                                          | In the "PLL Contribution—PPLL" section, the following was deleted:<br>FCLKIN is the input clock frequency.                                                                                                                                        | 2-14                   |

|                                                                          | In Table 2-21 • Summary of Maximum and Minimum DC Input Levels, the note was incorrect. It previously said $T_J$ and it was corrected and changed to $T_A$ .                                                                                      | 2-21                   |

|                                                                          | In Table 2-115 • ProASIC3 CCC/PLL Specification, the SCLK parameter and note 1 are new.                                                                                                                                                           | 2-90                   |

|                                                                          | Table 2-125 • JTAG 1532 was populated with the parameter data, which was not in the previous version of the document.                                                                                                                             | 2-108                  |

| Packaging v1.1                                                           | In the "VQ100" A3P030 pin table, the function of pin 63 was incorrect and changed from IO39RSB0 to GDB0/IO38RSB0.                                                                                                                                 | 4-19                   |

| Revision 0 (Jan 2008)                                                    | This document was previously in datasheet v2.2. As a result of moving to the handbook format, Actel has restarted the version numbers.                                                                                                            | N/A                    |

| v2.2<br>(July 2007)                                                      | The M7 and M1 device part numbers have been updated in Table 1 • ProASIC3<br>Product Family, "I/Os Per Package", "Automotive ProASIC3 Ordering<br>Information", "Temperature Grade Offerings", and "Speed Grade and<br>Temperature Grade Matrix". | i, ii, iii,<br>iii, iv |

|                                                                          | The words "ambient temperature" were added to the temperature range in the "Automotive ProASIC3 Ordering Information", "Temperature Grade Offerings", and "Speed Grade and Temperature Grade Matrix" sections.                                    | iii, iv                |

|                                                                          | The T <sub>J</sub> parameter in Table 3-2 $\cdot$ Recommended Operating Conditions was changed to T <sub>A</sub> , ambient temperature, and table notes 4–6 were added.                                                                           | 3-2                    |

| v2.1<br>(May 2007)                                                       | In the "Clock Conditioning Circuit (CCC) and PLL" section, the Wide Input Frequency Range (1.5 MHz to 200 MHz) was changed to (1.5 MHz to 350 MHz).                                                                                               | i                      |

|                                                                          | The "Clock Conditioning Circuit (CCC) and PLL" section was updated.                                                                                                                                                                               | i                      |

|                                                                          | In the "I/Os Per Package" section, the A3P030, A3P060, A3P125, ACP250, and A3P600 device I/Os were updated.                                                                                                                                       | ii                     |

|                                                                          | Table 3-5 • Package Thermal Resistivities was updated with A3P1000information. The note below the table is also new.                                                                                                                              | 3-5                    |

Datasheet Information

| Revision             | Changes                                                                                                                                                                                                                                                                                                                     | Page             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| v2.0<br>(April 2007) | In the "Packaging Tables", Ambient was deleted.                                                                                                                                                                                                                                                                             | ii               |

|                      | The timing characteristics tables were updated.                                                                                                                                                                                                                                                                             | N/A              |

|                      | The "PLL Macro" section was updated to add information on the VCO and PLL outputs during power-up.                                                                                                                                                                                                                          | 2-15             |

|                      | The "PLL Macro" section was updated to include power-up information.                                                                                                                                                                                                                                                        | 2-15             |

|                      | Table 2-11 • ProASIC3 CCC/PLL Specification was updated.                                                                                                                                                                                                                                                                    | 2-29             |

|                      | Figure 2-19 • Peak-to-Peak Jitter Definition is new.                                                                                                                                                                                                                                                                        | 2-18             |

|                      | The "SRAM and FIFO" section was updated with operation and timing requirement information.                                                                                                                                                                                                                                  | 2-21             |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                                                                                                                                            | 2-25             |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                                                                                                                                            | 2-25             |

|                      | The "Introduction" in the "Advanced I/Os" section was updated to include information on input and output buffers being disabled.                                                                                                                                                                                            | 2-28             |

|                      | PCI-X 3.3 V was added to Table 2-11 • VCCI Voltages and Compatible Standards.                                                                                                                                                                                                                                               | 2-29             |

|                      | In the Table 2-15 • Levels of Hot-Swap Support, the ProASIC3 compliance descriptions were updated for levels 3 and 4.                                                                                                                                                                                                       | 2-34             |

|                      | Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices was updated.                                                                                                                                                                                                                             | 2-64             |

|                      | Notes 3, 4, and 5 were added to Table 2-17 $\cdot$ Comparison Table for 5 V–Compliant Receiver Scheme. 5 x 52.72 was changed to 52.7 and the Maximum current was updated from 4 x 52.7 to 5 x 52.7.                                                                                                                         | 2-40             |

|                      | The "VCCPLF PLL Supply Voltage" section was updated.                                                                                                                                                                                                                                                                        | 2-50             |

|                      | The "VPUMP Programming Supply Voltage" section was updated.                                                                                                                                                                                                                                                                 | 2-50             |

|                      | The "GL Globals" section was updated to include information about direct input into quadrant clocks.                                                                                                                                                                                                                        | 2-51             |

|                      | V <sub>JTAG</sub> was deleted from the "TCK Test Clock" section.                                                                                                                                                                                                                                                            | 2-51             |

|                      | In Table 2-22 • Recommended Tie-Off Values for the TCK and TRST Pins, TSK was changed to TCK in note 2. Note 3 was also updated.                                                                                                                                                                                            | 2-51             |

|                      | Ambient was deleted from Table 3-2 • Recommended Operating Conditions. VPUMP programming mode was changed from "3.0 to 3.6" to "3.15 to 3.45".                                                                                                                                                                              | 3-2              |

|                      | Note 3 is new in Table 3-4 • Overshoot and Undershoot Limits (as measured on quiet I/Os)1.                                                                                                                                                                                                                                  | 3-2              |

|                      | In EQ 3-2, 150 was changed to 110 and the result changed from 3.9 to 1.951.                                                                                                                                                                                                                                                 | 3-5              |

|                      | Table 3-6 • Temperature and Voltage Derating Factors for Timing Delays was updated.                                                                                                                                                                                                                                         | 3-6              |

|                      | Table 3-5 • Package Thermal Resistivities was updated.                                                                                                                                                                                                                                                                      | 3-5              |

|                      | Table 3-14 • Summary of Maximum and Minimum DC Input and Output Levels<br>Applicable to Commercial and Industrial Conditions—Software Default Settings<br>(Advanced) and Table 3-17 • Summary of Maximum and Minimum DC Input<br>Levels Applicable to Commercial and Industrial Conditions (Standard Plus) were<br>updated. | 3-17 to 3-<br>17 |