# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            | -                                                                       |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 110592                                                                  |

| Number of I/O                  | 97                                                                      |

| Number of Gates                | 600000                                                                  |

| Voltage - Supply               | 1.425V ~ 1.575V                                                         |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                      |

| Package / Case                 | 144-LBGA                                                                |

| Supplier Device Package        | 144-FPBGA (13x13)                                                       |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3p600-fg144i |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2 – ProASIC3 DC and Switching Characteristics

## **General Specifications**

## **Operating Conditions**

Stresses beyond those listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-2 on page 2-2 is not implied.

| Symbol                        | Parameter                           | Limits                                                                                                | Units |

|-------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|-------|

| VCC                           | DC core supply voltage              | -0.3 to 1.65                                                                                          | V     |

| VJTAG                         | JTAG DC voltage                     | -0.3 to 3.75                                                                                          | V     |

| VPUMP                         | Programming voltage                 | -0.3 to 3.75                                                                                          | V     |

| VCCPLL                        | Analog power supply (PLL)           | -0.3 to 1.65                                                                                          | V     |

| VCCI                          | DC I/O output buffer supply voltage | -0.3 to 3.75                                                                                          | V     |

| VMV                           | DC I/O input buffer supply voltage  | -0.3 to 3.75                                                                                          | V     |

| VI                            | I/O input voltage                   | –0.3 V to 3.6 V                                                                                       | V     |

|                               |                                     | (when I/O hot insertion mode is enabled)                                                              |       |

|                               |                                     | -0.3~V to (VCCI + 1 V) or 3.6 V, whichever voltage is lower (when I/O hot-insertion mode is disabled) |       |

| T <sub>STG</sub> <sup>2</sup> | Storage temperature                 | -65 to +150                                                                                           | °C    |

| T <sub>J</sub> <sup>2</sup>   | Junction temperature                | +125                                                                                                  | °C    |

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-4 on page 2-3.

2. VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further information.

3. For flash programming and retention maximum limits, refer to Table 2-3 on page 2-3, and for recommended operating limits, refer to Table 2-2 on page 2-2.

## **Overview of I/O Performance**

### Summary of I/O DC Input and Output Levels – Default I/O Software Settings

#### Table 2-18 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Advanced I/O Banks

|                                            |                   | Equiv.                                                          |      |          | VIL         | VIH            |          | VOL         | VOH         |                        |                        |

|--------------------------------------------|-------------------|-----------------------------------------------------------------|------|----------|-------------|----------------|----------|-------------|-------------|------------------------|------------------------|

| I/O Standard                               | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> |      | Min<br>V | Max<br>V    | Min<br>V       | Max<br>V | Max<br>V    | Min<br>V    | IOL <sup>1</sup><br>mA | IOH <sup>1</sup><br>mA |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA             | 12 mA                                                           | High | -0.3     | 0.8         | 2              | 3.6      | 0.4         | 2.4         | 12                     | 12                     |

| 3.3 V<br>LVCMOS<br>Wide Range <sup>3</sup> | 100 µA            | 12 mA                                                           | High | -0.3     | 0.8         | 2              | 3.6      | 0.2         | VCCI – 0.2  | 0.1                    | 0.1                    |

| 2.5 V<br>LVCMOS                            | 12 mA             | 12 mA                                                           | High | -0.3     | 0.7         | 1.7            | 2.7      | 0.7         | 1.7         | 12                     | 12                     |

| 1.8 V<br>LVCMOS                            | 12 mA             | 12 mA                                                           | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI    | 1.9      | 0.45        | VCCI – 0.45 | 12                     | 12                     |

| 1.5 V<br>LVCMOS                            | 12 mA             | 12 mA                                                           | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI    | 1.6      | 0.25 * VCCI | 0.75 * VCCI | 12                     | 12                     |

| 3.3 V PCI                                  |                   |                                                                 |      |          | Per F       | PCI specificat | ions     |             |             |                        |                        |

| 3.3 V PCI-X                                |                   |                                                                 |      |          | Per P       | CI-X specifica | ations   |             |             |                        |                        |

Notes:

1. Currents are measured at 85°C junction temperature.

2. 3.3 V LVCMOS wide range is applicable to 100 μA drive strength only. The configuration will NOT operate at the equivalent software default drive strength. These values are for Normal Ranges ONLY.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

## Summary of I/O Timing Characteristics – Default I/O Software Settings

Table 2-22 • Summary of AC Measuring Points

| Standard              | Measuring Trip Point (V <sub>trip</sub> ) |

|-----------------------|-------------------------------------------|

| 3.3 ILTTL 13.3 ILCMOS | 1.4 🗆                                     |

| 3.3 ILCMOS ide Range  | 1.4 🗆                                     |

| 2.5 ILCMOS            | 1.2 🗆                                     |

| 1.8 ILCMOS            | 0.90 🗆                                    |

| 1.5 ILCMOS            | 0.75 🗆                                    |

| 3.3 IPC□              | 0.285 ICC [(RR)                           |

|                       | 0.615 ₪C [()]                             |

| 3.3 IPC□              | 0.285 ICCI(RR)                            |

|                       | 0.615 ₪C [()]                             |

Table 2-23 • I/O AC Parameter Definitions

| Parameter         | Parameter Definition                                             |  |  |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| t <sub>DP</sub>   | Data to Pad delay troug te Output uffer                          |  |  |  |  |  |  |  |  |

| t <sub>P□</sub>   | Pad to Data delay troug te nput uffer                            |  |  |  |  |  |  |  |  |

| t <sub>DOUT</sub> | Data to Output uffer delay trougite O interfae                   |  |  |  |  |  |  |  |  |

| t <sub>OUT</sub>  | nale to Output uffer Tristate Control delay troug te O interfae  |  |  |  |  |  |  |  |  |

| t <sub>D□</sub>   | nput uffer to Data delay troug te O interfae                     |  |  |  |  |  |  |  |  |

| t <sub>H□</sub>   | nalē to Pad delay trougītē Output ūfferHigīto 🗆                  |  |  |  |  |  |  |  |  |

| t <sub>H</sub>    | nalē to Pad delay troug te Output ūffer to Hig⊡                  |  |  |  |  |  |  |  |  |

| t∟□               | nale to Pad delay trougite Output ufferLoito                     |  |  |  |  |  |  |  |  |

| t□                | nalē to Pad delay troug te Output ūffer to Lo⊡                   |  |  |  |  |  |  |  |  |

| t <sub>HS</sub>   | nale to Pad delay trougite Outp ut uffer itidelayed enale to Hig |  |  |  |  |  |  |  |  |

| t <sub>LS</sub>   | nale to Pad delay trougite Outp ut uffer it delayed enale to Lo  |  |  |  |  |  |  |  |  |

|                |           |            |           |           |           |           |      |    |                         |                         | 1 1  | <u> </u>         |

|----------------|-----------|------------|-----------|-----------|-----------|-----------|------|----|-------------------------|-------------------------|------|------------------|

| 2.5 V LVCMOS   | V         | /IL        | V         | IH        | VOL       | VOH       | OL I | ОН | IOSL                    | IOSH I                  | '- ' | IIH <sup>2</sup> |

| Drive Strength | Min.<br>V | Max.,<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA   | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | µA 4 | µA <sup>4</sup>  |

| 2 mA           | 0.3       | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 2    | 2  | 16                      | 18                      | 10   | 10               |

| 4 mA           | 0.3       | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 4    | 4  | 16                      | 18                      | 10   | 10               |

| 6 mA           | 0.3       | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 6    | 6  | 32                      | 37                      | 10   | 10               |

| 8 mA           | 0.3       | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 8    | 8  | 32                      | 37                      | 10   | 10               |

## Table 2-58 • Minimum and Maximum DC Irput and Output Levels Applicable to Standard I/O Banks

tes

Steput eaae urret per per remmee peratits ere

Site put ease urret per per remmee peratifs DEC put urret s

arer elperatitise remmeelraes

□ Currets are measure at temperature (□

C utitemperature) a mamum tae

□ Currets are measure at C utitemperature □

🗆 tare eaut seet ite ira 🗆

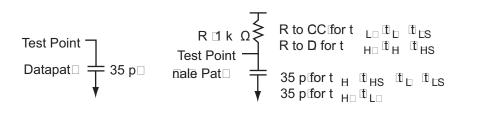

#### Figure 2-8 • AC Loading

Table 2-59 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | <sub>L</sub> G <sub>AD</sub> (pF) |

|---------------|----------------|----------------------|-----------------------------------|

| 0             | 2.5            | 1.2                  | 35                                |

|               |                | Fo mosto too tro nto |                                   |

te easur pt trp ee

Tae 🗆 pae 🗆

r⊇a mpēte taē ītrp pts⊡

#### rO C a tiCaratersts

### Timing Characteristics

Table 2-70 • 1.8 V LVCMOS High Slew

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive    | Speed |                   |                 |                  |                 |                   | _               |                 |                 |                 |                  |                  |       |

|----------|-------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Strength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

| 2 mA     | Std.  | 0.66              | 11.86           | 0.04             | 1.22            | 0.43              | 9.14            | 11.86           | 2.77            | 1.66            | 11.37            | 14.10            | ns    |

|          | 1     | 0.56              | 10.09           | 0.04             | 1.04            | 0.36              | 7.77            | 10.09           | 2.36            | 1.41            | 9.67             | 11.99            | ns    |

|          | 2     | 0.49              | 8.86            | 0.03             | 0.91            | 0.32              | 6.82            | 8.86            | 2.07            | 1.24            | 8.49             | 10.53            | ns    |

| 4 mA     | Std.  | 0.66              | 6.91            | 0.04             | 1.22            | 0.43              | 5.86            | 6.91            | 3.22            | 2.84            | 8.10             | 9.15             | ns    |

|          | 1     | 0.56              | 5.88            | 0.04             | 1.04            | 0.36              | 4.99            | 5.88            | 2.74            | 2.41            | 6.89             | 7.78             | ns    |

|          | 2     | 0.49              | 5.16            | 0.03             | 0.91            | 0.32              | 4.38            | 5.16            | 2.41            | 2.12            | 6.05             | 6.83             | ns    |

| 6 mA     | Std.  | 0.66              | 4.45            | 0.04             | 1.22            | 0.43              | 4.18            | 4.45            | 3.53            | 3.38            | 6.42             | 6.68             | ns    |

| 6 mA     | 1     | 0.56              | 3.78            | 0.04             | 1.04            | 0.36              | 3.56            | 3.78            | 3.00            | 2.88            | 5.46             | 5.69             | ns    |

|          | 2     | 0.49              | 3.32            | 0.03             | 0.91            | 0.32              | 3.12            | 3.32            | 2.64            | 2.53            | 4.79             | 4.99             | ns    |

| 8 mA     | Std.  | 0.66              | 3.92            | 0.04             | 1.22            | 0.43              | 3.93            | 3.92            | 3.60            | 3.52            | 6.16             | 6.16             | ns    |

|          | 1     | 0.56              | 3.34            | 0.04             | 1.04            | 0.36              | 3.34            | 3.34            | 3.06            | 3.00            | 5.24             | 5.24             | ns    |

|          | 2     | 0.49              | 2.93            | 0.03             | 0.91            | 0.32              | 2.93            | 2.93            | 2.69            | 2.63            | 4.60             | 4.60             | ns    |

| 12 mA    | Std.  | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|          | 1     | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|          | 2     | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

| 16 mA    | Std.  | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|          | 1     | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|          | 2     | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

|          | •     |                   |                 |                  |                 |                   |                 |                 | •               |                 |                  |                  |       |

tes 🗆

□ tare eaut seet te ra □

□ I spetutitemperature a tae supplees reer t□

Taē 🗆 paē 🗆

r erat aues

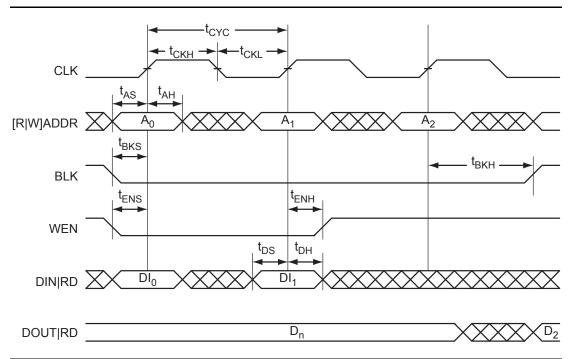

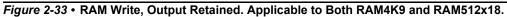

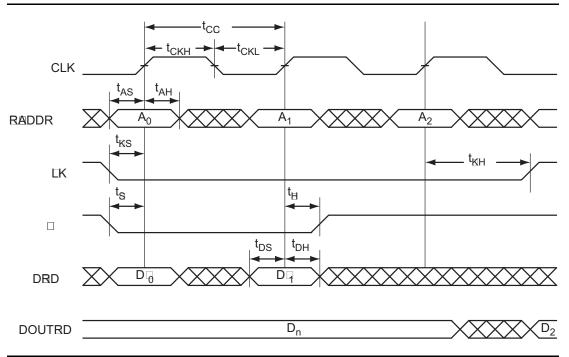

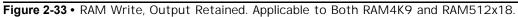

*Figure 2-34* • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 Only.

Figure 2-34 • RAM Write, Output as Write Data (WMDE = 1). Applicable to RAM4K9 Only.

## **Timing Characteristics**

#### Table 2-116 • RAM4K9

Commercial-Case Conditions: T  $_{J}$  = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                                                               | 2     | 1      | Std. | Units |

|----------------------|-----------------------------------------------------------------------------------------------------------|-------|--------|------|-------|

| t <sub>AS</sub>      | Address setup time                                                                                        | 0.25  | 0.28   | 0.33 | ns    |

| t <sub>AH</sub>      | Address old time                                                                                          | 0.00  | 0.00   | 0.00 | ns    |

| t <sub>S</sub>       | RIBetup time 0.14 0                                                                                       | 16 0  | 19     | ns   |       |

| t <sub>H</sub>       | R                                                                                                         | 1 0.1 | 3 n    | 6    |       |

| t <sub>KS</sub>      | LK setup time                                                                                             | 0.23  | 0.27 ( | 0.31 | ns    |

| t <sub>⊠H</sub>      | LK old time 0                                                                                             | .02 0 | 02 0.  | 02   | าร    |

| t <sub>DS</sub>      | nput data (D)Isetup time 0                                                                                | 18 0. | 21 0.  | 25   | าร    |

| t <sub>DH</sub>      | nput data (D)old time 0.0                                                                                 | 0.0   | 0 0.0  | 0 n: | 6     |

| t <sub>CKQ1</sub>    | Clok Hig to ne data alid on DOUT (out put retained MOD 0) 2.36                                            | 2.68  | 3.15   | ns   |       |

|                      | Clok Hig to ne data alid on DOUT (f lotroug MOD 1) 1.79 2.0                                               | 3 2.3 | 9 n:   | 6    |       |

| t <sub>CKQ2</sub>    | Clok Hig to ne data alid on DOUT (pipelined) 0.89                                                         | 1.02  | 1.20   | ns   |       |

| t <sub>C2CD</sub> 1  | Address ollision lktolk delay for reliale rite after rite on same addressAppliate to Closing dge          | 0.33  | 0.28   | 0.25 | ns    |

| t <sub>C2CH</sub> 1  | Address ollision lktolk delay for reliale rite after rite on same addressAppliate to Rising dge           | 0.30  | 0.26   | 0.23 | ns    |

| t <sub>C2CRH</sub> 1 | Address ollision lktolk delay for reliale read aess after rite on same addressAppliale to Opening dge     | 0.45  | 0.38   | 0.34 | ns    |

| t <sub>C2CRH</sub> 1 | Address ollision lktolk delay for relialē rite aēss after read on same<br>address Appliālē to Opening dge | 0.49  | 0.42   | 0.37 | ns    |

| t <sub>RSTQ</sub>    | RST Lotto data out Loton DOUT (flottoug) 0.9                                                              | 1.0   | 1.23   | s ns |       |

|                      | RST Loto Data Out Loton DO UT (pipelined)                                                                 | 0.92  | 1.05   | 1.23 | ns    |

| t <sub>RMRST□</sub>  | RSII remoal 0.2                                                                                           | 9 0.3 | 3 0.3  | 8 n: | 6     |

| t <sub>RCRST□</sub>  | RST recery 1.50                                                                                           | 1.71  | 2.01   | ns   |       |

| t <sub>MPRST□</sub>  | RSI minimum pulse idt□ 0.21                                                                               | 0.24  | 0.29   | ns   |       |

| t <sub>CC</sub>      | Cloki yle time 3.                                                                                         | 23 3. | 68 4.3 | 82 r | S     |

|                      | Maximum freueny 3                                                                                         | 10 2  | 72 2   | 31 N | 1H□   |

tes

□ Emre finatileer tite appâtite aseiΩs ais

mutaeus earte perats wart mas

Tae 🗆 pae 🗆

Ispetuttemperature attac suppteestreer t

r erat aues