# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 151                                                                       |

| Number of Gates                | 250000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 208-BFQFP                                                                 |

| Supplier Device Package        | 208-PQFP (28x28)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3p250-pqg208 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3 device provides the best available security for programmable logic designs.

## Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system powerup (unlike SRAM-based FPGAs). Therefore, flash-based ProASIC3 FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

## Instant On

Flash-based ProASIC3 devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based ProASIC3 devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs that are used for these purposes in a system. In addition, glitches and brownouts in system power will not corrupt the ProASIC3 device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASIC3 devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of ProASIC3 flash-based FPGAs. Once it is programmed, the flash cell configuration element of ProASIC3 FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

### Low Power

Flash-based ProASIC3 devices exhibit power characteristics similar to an ASIC, making them an ideal choice for power-sensitive applications. ProASIC3 devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

ProASIC3 devices also have low dynamic power consumption to further maximize power savings.

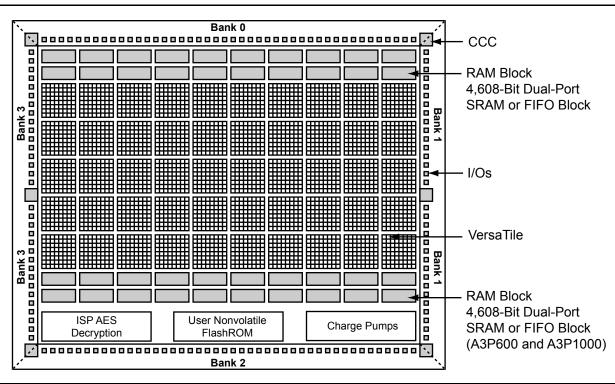

Figure 1-2 • ProASIC3 Device Architecture Overview with Four I/O Banks (A3P250, A3P600, and A3P1000)

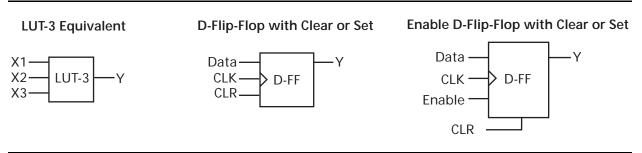

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the ProASIC3 core tile as either a three-input lookup table (LUT) equivalent or as a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the Microsemi ProASIC family of third-generation architecture flash FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

## VersaTiles

The ProASIC3 core consists of VersaTiles, which have been enhanced beyond the ProASIC<sup>PLUS®</sup> core tiles. The ProASIC3 VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-3 for VersaTile configurations.

### RAM Contribution—P<sub>MEMORY</sub>

$\mathsf{P}_{\mathsf{MEMORY}} = \mathsf{P}_{\mathsf{AC11}} * \mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{F}_{\mathsf{READ-CLOCK}} * \beta_2 + \mathsf{P}_{\mathsf{AC12}} * \mathsf{N}_{\mathsf{BLOCK}} * \mathsf{F}_{\mathsf{WRITE-CLOCK}} * \beta_3$

$N_{\mbox{\scriptsize BLOCKS}}$  is the number of RAM blocks used in the design.

F<sub>READ-CLOCK</sub> is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations.

F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

$\beta_3$  is the RAM enable rate for write operations—guidelines are provided in Table 2-17 on page 2-14.

## PLL Contribution—P<sub>PLL</sub>

$P_{PLL} = P_{DC4} + P_{AC13} * F_{CLKOUT}$

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

## Guidelines

#### Toggle Rate Definition

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

#### Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

#### Table 2-16 • Toggle Rate Guidelines Recommended for Power Calculation

| Component      | Definition                       | Guideline |

|----------------|----------------------------------|-----------|

| $\alpha_1$     | Toggle rate of VersaTile outputs | 10%       |

| α <sub>2</sub> | I/O buffer toggle rate           | 10%       |

#### Table 2-17 • Enable Rate Guidelines Recommended for Power Calculation

| Component      | Definition                           | Guideline |

|----------------|--------------------------------------|-----------|

| β <sub>1</sub> | I/O output buffer enable rate        | 100%      |

| β <sub>2</sub> | RAM enable rate for read operations  | 12.5%     |

| β <sub>3</sub> | RAM enable rate for write operations | 12.5%     |

The PLL dynamic contribution depends on the input clock frequency, the number of output clock signals generated by the PLL, and the frequency of each output clock. If a PLL is used to generate more than one output clock, include each output clock in the formula by adding its corresponding contribution (P<sub>AC14</sub> \* F<sub>CLKOUT</sub> product) to the total PLL contribution.

#### Table 2-30 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to Standard I/O Banks

| Standard                             | Drive Strength | R <sub>PULL-DOWN</sub><br>(Ω) <sup>2</sup> | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|--------------------------------------|----------------|--------------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA           | 100                                        | 300                                      |

|                                      | 4 mA           | 100                                        | 300                                      |

|                                      | 6 mA           | 50                                         | 150                                      |

|                                      | 8 mA           | 50                                         | 150                                      |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 100 µA         | Same as regular 3.3 V<br>LVCMOS            | Same as regular<br>3.3 V LVCMOS          |

| 2.5 V LVCMOS                         | 2 mA           | 100                                        | 200                                      |

|                                      | 4 mA           | 100                                        | 200                                      |

|                                      | 6 mA           | 50                                         | 100                                      |

|                                      | 8 mA           | 50                                         | 100                                      |

| 1.8 V LVCMOS                         | 2 mA           | 200                                        | 225                                      |

|                                      | 4 mA           | 100                                        | 112                                      |

| 1.5 V LVCMOS                         | 2 mA           | 200                                        | 224                                      |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located at http://www.microsemi.com/soc/download/ibis/default.aspx.

2. R<sub>(PULL-DOWN-MAX)</sub> = (VOLspec) / IOLspec

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

#### Table 2-31 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|                         | R <sub>(WEAK I</sub> | PULL-UP) <sup>1</sup><br>2) | $R_{(WEAK PULL-DOWN)}^2$ ( $\Omega$ ) |       |  |

|-------------------------|----------------------|-----------------------------|---------------------------------------|-------|--|

| VCCI                    | Min                  | Max                         | Min                                   | Мах   |  |

| 3.3 V                   | 10 k                 | 45 k                        | 10 k                                  | 45 k  |  |

| 3.3 V (wide range I/Os) | 10 k                 | 45 k                        | 10 k                                  | 45 k  |  |

| 2.5 V                   | 11 k                 | 55 k                        | 12 k                                  | 74 k  |  |

| 1.8 V                   | 18 k                 | 70 k                        | 17 k                                  | 110 k |  |

| 1.5 V                   | 19 k                 | 90 k                        | 19 k                                  | 140 k |  |

Notes:

R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCI<sub>MAX</sub> - VOH<sub>spec</sub>) / I<sub>(WEAK PULL-UP-MIN)</sub>

R<sub>(WEAK PULL-DOWN-MAX)</sub> = (VOL<sub>spec</sub>) / I<sub>(WEAK PULL-DOWN-MIN)</sub>

## Table 2-34 • I/O Short Currents IOSH/IOSL Applicable to Standard I/O Banks

|                                      | Drive Strength | IOSL (mA) <sup>1</sup>          | IOSH (mA) <sup>1</sup>          |

|--------------------------------------|----------------|---------------------------------|---------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA           | 27                              | 25                              |

|                                      | 4 mA           | 27                              | 25                              |

|                                      | 6 mA           | 54                              | 51                              |

|                                      | 8 mA           | 54                              | 51                              |

| 3.3 V LVCMOS Wide Range <sup>2</sup> | 100 µA         | Same as regular 3.3 V<br>LVCMOS | Same as regular 3.3 V<br>LVCMOS |

| 2.5 V LVCMOS                         | 2 mA           | 18                              | 16                              |

|                                      | 4 mA           | 18                              | 16                              |

|                                      | 6 mA           | 37                              | 32                              |

|                                      | 8 mA           | 37                              | 32                              |

| 1.8 V LVCMOS                         | 2 mA           | 11                              | 9                               |

|                                      | 4 mA           | 22                              | 17                              |

| 1.5 V LVCMOS                         | 2 mA           | 16                              | 13                              |

Notes:

- 1.  $T_{.1} = 100^{\circ}C$

- Applicable to 3.3 V LVCMOS Wide Range. I<sub>OSL</sub>/I<sub>OSH</sub> dependent on the I/O buffer drive strength selected for wide range applications. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

The length of time an I/O can withstand IOSH/IOSL events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than six months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

#### Table 2-35 • Duration of Short Circuit Event Before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| -40°C       | > 20 years          |

| 0°C         | > 20 years          |

| 25°C        | > 20 years          |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 0.5 years           |

#### Table 2-36 • I/O Input Rise Time, Fall Time, and Related I/O Reliability

| Input Buffer                  | It Buffer Input Rise/Fall Time (min) Input Rise/Fall Time (max) |         |                  |  |  |

|-------------------------------|-----------------------------------------------------------------|---------|------------------|--|--|

| LVTTL/LVCMOS                  | No requirement                                                  | 10 ns * | 20 years (110°C) |  |  |

| LVDS/B-LVDS/<br>M-LVDS/LVPECL | No requirement                                                  | 10 ns * | 10 years (100°C) |  |  |

Note: \*The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

| Table 2-39 • Min                     | imum an  | nd Maxim | um DC I  | nput and   | Output L | evels    |     |    |                        |                        |                  |                 |

|--------------------------------------|----------|----------|----------|------------|----------|----------|-----|----|------------------------|------------------------|------------------|-----------------|

| App<br>3.3 V LVTTL /<br>3.3 V LVCMOS |          | o Standa |          | anks<br>IH | VOL      | VOH      | IOL | ЮН | IOSL                   | IOSH                   | IIL <sup>1</sup> |                 |

| Drive Strength                       | Min<br>V | Max<br>V | Min<br>V | Max<br>V   | Max<br>V | Min<br>V | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup> |

| 2 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 2   | 2  | 25                     | 27                     | 10               | 10              |

| 4 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 4   | 4  | 25                     | 27                     | 10               | 10              |

| 6 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 6   | 6  | 51                     | 54                     | 10               | 10              |

| 8 mA                                 | -0.3     | 0.8      | 2        | 3.6        | 0.4      | 2.4      | 8   | 8  | 51                     | 54                     | 10               | 10              |

Vlicrose

Power Matters.

## T

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at 100°C junction temperature and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

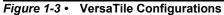

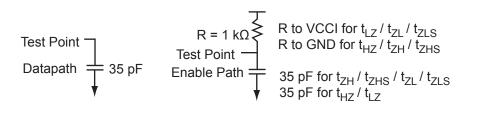

### Figure 2-7 • AC Loading

#### Table 2-40 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 3.3            | 1.4                  | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-22 on page 2-22 for a complete table of trip points.

#### Table 2-58 • Minimum and Maximum DC Input and Output Levels Applicable to Standard I/O Banks

| 2.5 V LVCMOS   | v         | ΊL         | v         | IH        | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|----------------|-----------|------------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength | Min.<br>V | Max.,<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 2   | 2   | 16                      | 18                      | 10               | 10               |

| 4 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4   | 16                      | 18                      | 10               | 10               |

| 6 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 6   | 6   | 32                      | 37                      | 10               | 10               |

| 8 mA           | -0.3      | 0.7        | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8   | 32                      | 37                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

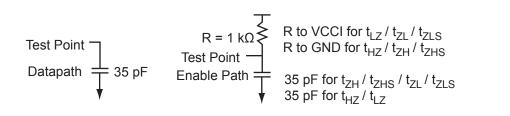

#### Figure 2-8 • AC Loading

#### Table 2-59 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 2.5            | 1.2                  | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-22 on page 2-22 for a complete table of trip points.

### **Timing Characteristics**

#### Table 2-60 • 2.5 V LVCMOS High Slew

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Advanced I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 8.66            | 0.04             | 1.31            | 0.43              | 7.83            | 8.66            | 2.68            | 2.30            | 10.07            | 10.90            | ns    |

|                   | -1             | 0.51              | 7.37            | 0.04             | 1.11            | 0.36              | 6.66            | 7.37            | 2.28            | 1.96            | 8.56             | 9.27             | ns    |

|                   | -2             | 0.45              | 6.47            | 0.03             | 0.98            | 0.32              | 5.85            | 6.47            | 2.00            | 1.72            | 7.52             | 8.14             | ns    |

| 6 mA              | Std.           | 0.60              | 5.17            | 0.04             | 1.31            | 0.43              | 5.04            | 5.17            | 3.05            | 3.00            | 7.27             | 7.40             | ns    |

|                   | -1             | 0.51              | 4.39            | 0.04             | 1.11            | 0.36              | 4.28            | 4.39            | 2.59            | 2.55            | 6.19             | 6.30             | ns    |

|                   | -2             | 0.45              | 3.86            | 0.03             | 0.98            | 0.32              | 3.76            | 3.86            | 2.28            | 2.24            | 5.43             | 5.53             | ns    |

| 8 mA              | Std.           | 0.60              | 5.17            | 0.04             | 1.31            | 0.43              | 5.04            | 5.17            | 3.05            | 3.00            | 7.27             | 7.40             | ns    |

|                   | -1             | 0.51              | 4.39            | 0.04             | 1.11            | 0.36              | 4.28            | 4.39            | 2.59            | 2.55            | 6.19             | 6.30             | ns    |

|                   | -2             | 0.45              | 3.86            | 0.03             | 0.98            | 0.32              | 3.76            | 3.86            | 2.28            | 2.24            | 5.43             | 5.53             | ns    |

| 12 mA             | Std.           | 0.60              | 3.56            | 0.04             | 1.31            | 0.43              | 3.63            | 3.43            | 3.30            | 3.44            | 5.86             | 5.67             | ns    |

|                   | -1             | 0.51              | 3.03            | 0.04             | 1.11            | 0.36              | 3.08            | 2.92            | 2.81            | 2.92            | 4.99             | 4.82             | ns    |

|                   | -2             | 0.45              | 2.66            | 0.03             | 0.98            | 0.32              | 2.71            | 2.56            | 2.47            | 2.57            | 4.38             | 4.23             | ns    |

| 16 mA             | Std.           | 0.60              | 3.35            | 0.04             | 1.31            | 0.43              | 3.41            | 3.06            | 3.36            | 3.55            | 5.65             | 5.30             | ns    |

|                   | -1             | 0.51              | 2.85            | 0.04             | 1.11            | 0.36              | 2.90            | 2.60            | 2.86            | 3.02            | 4.81             | 4.51             | ns    |

|                   | -2             | 0.45              | 2.50            | 0.03             | 0.98            | 0.32              | 2.55            | 2.29            | 2.51            | 2.65            | 4.22             | 3.96             | ns    |

| 24 mA             | Std.           | 0.60              | 3.09            | 0.04             | 1.31            | 0.43              | 3.15            | 2.44            | 3.44            | 4.00            | 5.38             | 4.68             | ns    |

|                   | -1             | 0.51              | 2.63            | 0.04             | 1.11            | 0.36              | 2.68            | 2.08            | 2.92            | 3.40            | 4.58             | 3.98             | ns    |

|                   | -2             | 0.45              | 2.31            | 0.03             | 0.98            | 0.32              | 2.35            | 1.82            | 2.57            | 2.98            | 4.02             | 3.49             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-61 • 2.5 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Advanced I/O Banks

| Applicable to Advanced no Ballis |                |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

|----------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength                | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 4 mA                             | Std.           | 0.60              | 11.40           | 0.04             | 1.31            | 0.43              | 11.22           | 11.40           | 2.68            | 2.20            | 13.45            | 13.63            | ns    |

|                                  | -1             | 0.51              | 9.69            | 0.04             | 1.11            | 0.36              | 9.54            | 9.69            | 2.28            | 1.88            | 11.44            | 11.60            | ns    |

|                                  | -2             | 0.45              | 8.51            | 0.03             | 0.98            | 0.32              | 8.38            | 8.51            | 2.00            | 1.65            | 10.05            | 10.18            | ns    |

| 6 mA                             | Std.           | 0.60              | 7.96            | 0.04             | 1.31            | 0.43              | 8.11            | 7.81            | 3.05            | 2.89            | 10.34            | 10.05            | ns    |

|                                  | -1             | 0.51              | 6.77            | 0.04             | 1.11            | 0.36              | 6.90            | 6.65            | 2.59            | 2.46            | 8.80             | 8.55             | ns    |

|                                  | -2             | 0.45              | 5.94            | 0.03             | 0.98            | 0.32              | 6.05            | 5.84            | 2.28            | 2.16            | 7.72             | 7.50             | ns    |

| 8 mA                             | Std.           | 0.60              | 7.96            | 0.04             | 1.31            | 0.43              | 8.11            | 7.81            | 3.05            | 2.89            | 10.34            | 10.05            | ns    |

|                                  | -1             | 0.51              | 6.77            | 0.04             | 1.11            | 0.36              | 6.90            | 6.65            | 2.59            | 2.46            | 8.80             | 8.55             | ns    |

|                                  | -2             | 0.45              | 5.94            | 0.03             | 0.98            | 0.32              | 6.05            | 5.84            | 2.28            | 2.16            | 7.72             | 7.50             | ns    |

| 12 mA                            | Std.           | 0.60              | 6.18            | 0.04             | 1.31            | 0.43              | 6.29            | 5.92            | 3.30            | 3.32            | 8.53             | 8.15             | ns    |

|                                  | -1             | 0.51              | 5.26            | 0.04             | 1.11            | 0.36              | 5.35            | 5.03            | 2.81            | 2.83            | 7.26             | 6.94             | ns    |

|                                  | -2             | 0.45              | 4.61            | 0.03             | 0.98            | 0.32              | 4.70            | 4.42            | 2.47            | 2.48            | 6.37             | 6.09             | ns    |

| 16 mA                            | Std.           | 0.60              | 5.76            | 0.04             | 1.31            | 0.43              | 5.87            | 5.53            | 3.36            | 3.44            | 8.11             | 7.76             | ns    |

|                                  | -1             | 0.51              | 4.90            | 0.04             | 1.11            | 0.36              | 4.99            | 4.70            | 2.86            | 2.92            | 6.90             | 6.60             | ns    |

|                                  | -2             | 0.45              | 4.30            | 0.03             | 0.98            | 0.32              | 4.38            | 4.13            | 2.51            | 2.57            | 6.05             | 5.80             | ns    |

| 24 mA                            | Std.           | 0.60              | 5.51            | 0.04             | 1.31            | 0.43              | 5.50            | 5.51            | 3.43            | 3.87            | 7.74             | 7.74             | ns    |

|                                  | -1             | 0.51              | 4.68            | 0.04             | 1.11            | 0.36              | 4.68            | 4.68            | 2.92            | 3.29            | 6.58             | 6.59             | ns    |

|                                  | -2             | 0.45              | 4.11            | 0.03             | 0.98            | 0.32              | 4.11            | 4.11            | 2.56            | 2.89            | 5.78             | 5.78             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-68 • Minimum and Maximum DC Input and Output Levels Applicable to Standard I/O Banks

| 1.8 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI – 0.45 | 2   | 2  | 9                       | 11                      | 10              | 10               |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI – 0.45 | 4   | 4  | 17                      | 22                      | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

#### Figure 2-9 • AC Loading

#### Table 2-69 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.8            | 0.9                  | 35                     |

Note: \*Measuring point = Vtrip\_See Table 2-22 on page 2-22 for a complete table of trip points.

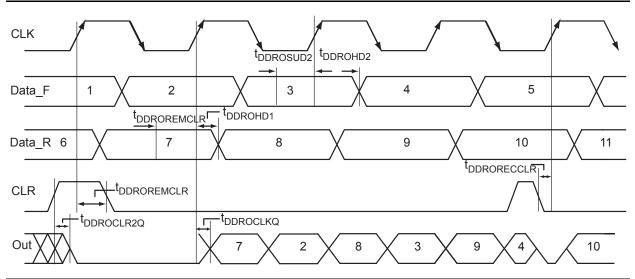

| Figure 2-23 • | Output D | DR Timing Diagram |

|---------------|----------|-------------------|

|---------------|----------|-------------------|

## **Timing Characteristics**

## Table 2-104 • Output DDR Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                           | -2   | -1   | Std. | Units |

|-------------------------|-------------------------------------------------------|------|------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.70 | 0.80 | 0.94 | ns    |

| t <sub>DDROSUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.38 | 0.43 | 0.51 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.38 | 0.43 | 0.51 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width High for the Output DDR     | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output DDR      | 0.32 | 0.37 | 0.43 | ns    |

| F <sub>DDOMAX</sub>     | Maximum Frequency for the Output DDR                  | 350  | 309  | 263  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

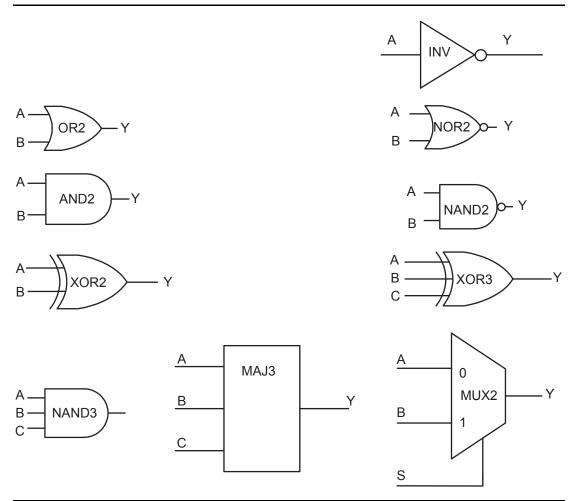

## **VersaTile Characteristics**

## VersaTile Specifications as a Combinatorial Module

The ProASIC3 library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *Fusion, IGLOO®/e, and ProASIC3/E Macro Library Guide*.

Figure 2-24 • Sample of Combinatorial Cells

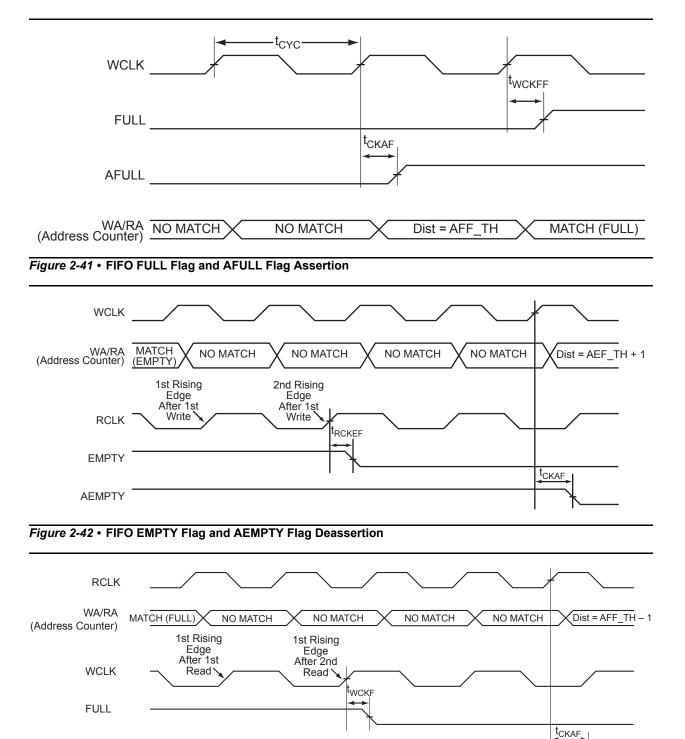

AFULL

| Table 2-123 • A3P250 FIFO 4k×1 (continued)                     |         |

|----------------------------------------------------------------|---------|

| Worst Commercial-Case Conditions: T <sub>1</sub> = 70°C, VCC = | 1.425 V |

| Parameter                                                         | Description                                 | -2   | -1   | Std. | Units |

|-------------------------------------------------------------------|---------------------------------------------|------|------|------|-------|

| t <sub>RSTAF</sub>                                                | RESET Low to Almost Empty/Full Flag Valid   |      | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub> RESET Low to Data Out Low on DO (pass-through) |                                             | 0.92 | 1.05 | 1.23 | ns    |

|                                                                   | RESET Low to Data Out Low on DO (pipelined) | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>                                              | RESET Removal                               | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>                                              | RESET Recovery                              | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>                                              | RESET Minimum Pulse Width                   | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>                                                  | Clock Cycle Time                            |      | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>                                                  | Maximum Frequency                           | 310  | 272  | 231  | MHz   |

## **Embedded FlashROM Characteristics**

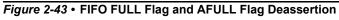

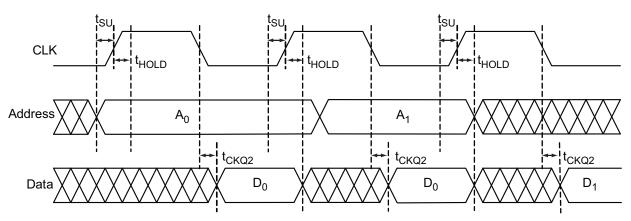

Figure 2-44 • Timing Diagram

## **Timing Characteristics**

### Table 2-124 • Embedded FlashROM Access Time

| Parameter         | Description             | -2    | -1    | Std.  | Units |

|-------------------|-------------------------|-------|-------|-------|-------|

| t <sub>SU</sub>   | Address Setup Time      | 0.53  | 0.61  | 0.71  | ns    |

| t <sub>HOLD</sub> | Address Hold Time       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>CK2Q</sub> | Clock to Out            | 21.42 | 24.40 | 28.68 | ns    |

| F <sub>MAX</sub>  | Maximum Clock Frequency | 15    | 15    | 15    | MHz   |

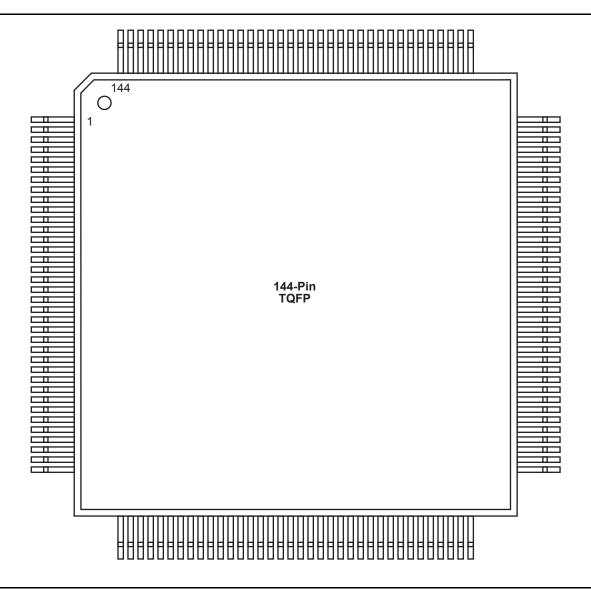

## TQ144 – Top View

## Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

Package Pin Assignments

| Т          | Q144            | Т          | Q144            | Т          | Q144            |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P060 Function | Pin Number | A3P060 Function | Pin Number | A3P060 Function |

| 1          | GAA2/IO51RSB1   | 37         | NC              | 73         | VPUMP           |

| 2          | IO52RSB1        | 38         | GEA2/IO71RSB1   | 74         | NC              |

| 3          | GAB2/IO53RSB1   | 39         | GEB2/IO70RSB1   | 75         | TDO             |

| 4          | IO95RSB1        | 40         | GEC2/IO69RSB1   | 76         | TRST            |

| 5          | GAC2/IO94RSB1   | 41         | IO68RSB1        | 77         | VJTAG           |

| 6          | IO93RSB1        | 42         | IO67RSB1        | 78         | GDA0/IO50RSB0   |

| 7          | IO92RSB1        | 43         | IO66RSB1        | 79         | GDB0/IO48RSB0   |

| 8          | IO91RSB1        | 44         | IO65RSB1        | 80         | GDB1/IO47RSB0   |

| 9          | VCC             | 45         | VCC             | 81         | VCCIB0          |

| 10         | GND             | 46         | GND             | 82         | GND             |

| 11         | VCCIB1          | 47         | VCCIB1          | 83         | IO44RSB0        |

| 12         | IO90RSB1        | 48         | NC              | 84         | GCC2/IO43RSB0   |

| 13         | GFC1/IO89RSB1   | 49         | IO64RSB1        | 85         | GCB2/IO42RSB0   |

| 14         | GFC0/IO88RSB1   | 50         | NC              | 86         | GCA2/IO41RSB0   |

| 15         | GFB1/IO87RSB1   | 51         | IO63RSB1        | 87         | GCA0/IO40RSB0   |

| 16         | GFB0/IO86RSB1   | 52         | NC              | 88         | GCA1/IO39RSB0   |

| 17         | VCOMPLF         | 53         | IO62RSB1        | 89         | GCB0/IO38RSB0   |

| 18         | GFA0/IO85RSB1   | 54         | NC              | 90         | GCB1/IO37RSB0   |

| 19         | VCCPLF          | 55         | IO61RSB1        | 91         | GCC0/IO36RSB0   |

| 20         | GFA1/IO84RSB1   | 56         | NC              | 92         | GCC1/IO35RSB0   |

| 21         | GFA2/IO83RSB1   | 57         | NC              | 93         | IO34RSB0        |

| 22         | GFB2/IO82RSB1   | 58         | IO60RSB1        | 94         | IO33RSB0        |

| 23         | GFC2/IO81RSB1   | 59         | IO59RSB1        | 95         | NC              |

| 24         | IO80RSB1        | 60         | IO58RSB1        | 96         | NC              |

| 25         | IO79RSB1        | 61         | IO57RSB1        | 97         | NC              |

| 26         | IO78RSB1        | 62         | NC              | 98         | VCCIB0          |

| 27         | GND             | 63         | GND             | 99         | GND             |

| 28         | VCCIB1          | 64         | NC              | 100        | VCC             |

| 29         | GEC1/IO77RSB1   | 65         | GDC2/IO56RSB1   | 101        | IO30RSB0        |

| 30         | GEC0/IO76RSB1   | 66         | GDB2/IO55RSB1   | 102        | GBC2/IO29RSB0   |

| 31         | GEB1/IO75RSB1   | 67         | GDA2/IO54RSB1   | 103        | IO28RSB0        |

| 32         | GEB0/IO74RSB1   | 68         | GNDQ            | 104        | GBB2/IO27RSB0   |

| 33         | GEA1/IO73RSB1   | 69         | ТСК             | 105        | IO26RSB0        |

| 34         | GEA0/IO72RSB1   | 70         | TDI             | 106        | GBA2/IO25RSB0   |

| 35         | VMV1            | 71         | TMS             | 107        | VMV0            |

| 36         | GNDQ            | 72         | VMV1            | 108        | GNDQ            |

| F          | PQ208           | F          | PQ208           | PQ208      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P600 Function | Pin Number | A3P600 Function | Pin Number | A3P600 Function |  |

| 1          | GND             | 37         | IO152PDB3       | 73         | IO120RSB2       |  |

| 2          | GAA2/IO174PDB3  | 38         | IO152NDB3       | 74         | IO119RSB2       |  |

| 3          | IO174NDB3       | 39         | IO150PSB3       | 75         | IO118RSB2       |  |

| 4          | GAB2/IO173PDB3  | 40         | VCCIB3          | 76         | IO117RSB2       |  |

| 5          | IO173NDB3       | 41         | GND             | 77         | IO116RSB2       |  |

| 6          | GAC2/IO172PDB3  | 42         | IO147PDB3       | 78         | IO115RSB2       |  |

| 7          | IO172NDB3       | 43         | IO147NDB3       | 79         | IO114RSB2       |  |

| 8          | IO171PDB3       | 44         | GEC1/IO146PDB3  | 80         | IO112RSB2       |  |

| 9          | IO171NDB3       | 45         | GEC0/IO146NDB3  | 81         | GND             |  |

| 10         | IO170PDB3       | 46         | GEB1/IO145PDB3  | 82         | IO111RSB2       |  |

| 11         | IO170NDB3       | 47         | GEB0/IO145NDB3  | 83         | IO110RSB2       |  |

| 12         | IO169PDB3       | 48         | GEA1/IO144PDB3  | 84         | IO109RSB2       |  |

| 13         | IO169NDB3       | 49         | GEA0/IO144NDB3  | 85         | IO108RSB2       |  |

| 14         | IO168PDB3       | 50         | VMV3            | 86         | IO107RSB2       |  |

| 15         | IO168NDB3       | 51         | GNDQ            | 87         | IO106RSB2       |  |

| 16         | VCC             | 52         | GND             | 88         | VCC             |  |

| 17         | GND             | 53         | VMV2            | 89         | VCCIB2          |  |

| 18         | VCCIB3          | 54         | GEA2/IO143RSB2  | 90         | IO104RSB2       |  |

| 19         | IO166PDB3       | 55         | GEB2/IO142RSB2  | 91         | IO102RSB2       |  |

| 20         | IO166NDB3       | 56         | GEC2/IO141RSB2  | 92         | IO100RSB2       |  |

| 21         | GFC1/IO164PDB3  | 57         | IO140RSB2       | 93         | IO98RSB2        |  |

| 22         | GFC0/IO164NDB3  | 58         | IO139RSB2       | 94         | IO96RSB2        |  |

| 23         | GFB1/IO163PDB3  | 59         | IO138RSB2       | 95         | IO92RSB2        |  |

| 24         | GFB0/IO163NDB3  | 60         | IO137RSB2       | 96         | GDC2/IO91RSB2   |  |

| 25         | VCOMPLF         | 61         | IO136RSB2       | 97         | GND             |  |

| 26         | GFA0/IO162NPB3  | 62         | VCCIB2          | 98         | GDB2/IO90RSB2   |  |

| 27         | VCCPLF          | 63         | IO135RSB2       | 99         | GDA2/IO89RSB2   |  |

| 28         | GFA1/IO162PPB3  | 64         | IO133RSB2       | 100        | GNDQ            |  |

| 29         | GND             | 65         | GND             | 101        | ТСК             |  |

| 30         | GFA2/IO161PDB3  | 66         | IO131RSB2       | 102        | TDI             |  |

| 31         | IO161NDB3       | 67         | IO129RSB2       | 103        | TMS             |  |

| 32         | GFB2/IO160PDB3  | 68         | IO127RSB2       | 104        | VMV2            |  |

| 33         | IO160NDB3       | 69         | IO125RSB2       | 105        | GND             |  |

| 34         | GFC2/IO159PDB3  | 70         | IO123RSB2       | 106        | VPUMP           |  |

| 35         | IO159NDB3       | 71         | VCC             | 107        | GNDQ            |  |

| 36         | VCC             | 72         | VCCIB2          | 108        | TDO             |  |

| F          | G144            |

|------------|-----------------|

| Pin Number | A3P250 Function |

| K1         | GEB0/IO99NDB3   |

| K2         | GEA1/IO98PDB3   |

| K3         | GEA0/IO98NDB3   |

| K4         | GEA2/IO97RSB2   |

| K5         | IO90RSB2        |

| K6         | IO84RSB2        |

| K7         | GND             |

| K8         | IO66RSB2        |

| K9         | GDC2/IO63RSB2   |

| K10        | GND             |

| K11        | GDA0/IO60VDB1   |

| K12        | GDB0/IO59VDB1   |

| L1         | GND             |

| L2         | VMV3            |

| L3         | GEB2/IO96RSB2   |

| L4         | IO91RSB2        |

| L5         | VCCIB2          |

| L6         | IO82RSB2        |

| L7         | IO80RSB2        |

| L8         | IO72RSB2        |

| L9         | TMS             |

| L10        | VJTAG           |

| L11        | VMV2            |

| L12        | TRST            |

| M1         | GNDQ            |

| M2         | GEC2/IO95RSB2   |

| M3         | IO92RSB2        |

| M4         | IO89RSB2        |

| M5         | IO87RSB2        |

| M6         | IO85RSB2        |

| M7         | IO78RSB2        |

| M8         | IO76RSB2        |

| M9         | TDI             |

| M10        | VCCIB2          |

| M11        | VPUMP           |

| M12        | GNDQ            |

## 🌜 Microsemi.

Package Pin Assignments

| FG256      |                 | FG256      |                 | FG256      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P400 Function | Pin Number | A3P400 Function | Pin Number | A3P400 Function |

| A1         | GND             | C5         | GAC0/IO04RSB0   | E9         | IO31RSB0        |

| A2         | GAA0/IO00RSB0   | C6         | GAC1/IO05RSB0   | E10        | VCCIB0          |

| A3         | GAA1/IO01RSB0   | C7         | IO20RSB0        | E11        | VCCIB0          |

| A4         | GAB0/IO02RSB0   | C8         | IO24RSB0        | E12        | VMV1            |

| A5         | IO16RSB0        | C9         | IO33RSB0        | E13        | GBC2/IO62PDB1   |

| A6         | IO17RSB0        | C10        | IO39RSB0        | E14        | IO65RSB1        |

| A7         | IO22RSB0        | C11        | IO45RSB0        | E15        | IO52RSB0        |

| A8         | IO28RSB0        | C12        | GBC0/IO54RSB0   | E16        | IO66PDB1        |

| A9         | IO34RSB0        | C13        | IO48RSB0        | F1         | IO150NDB3       |

| A10        | IO37RSB0        | C14        | VMV0            | F2         | IO149NPB3       |

| A11        | IO41RSB0        | C15        | IO61NPB1        | F3         | IO09RSB0        |

| A12        | IO43RSB0        | C16        | IO63PDB1        | F4         | IO152UDB3       |

| A13        | GBB1/IO57RSB0   | D1         | IO151VDB3       | F5         | VCCIB3          |

| A14        | GBA0/IO58RSB0   | D2         | IO151UDB3       | F6         | GND             |

| A15        | GBA1/IO59RSB0   | D3         | GAC2/IO153UDB3  | F7         | VCC             |

| A16        | GND             | D4         | IO06RSB0        | F8         | VCC             |

| B1         | GAB2/IO154UDB3  | D5         | GNDQ            | F9         | VCC             |

| B2         | GAA2/IO155UDB3  | D6         | IO10RSB0        | F10        | VCC             |

| B3         | IO12RSB0        | D7         | IO19RSB0        | F11        | GND             |

| B4         | GAB1/IO03RSB0   | D8         | IO26RSB0        | F12        | VCCIB1          |

| B5         | IO13RSB0        | D9         | IO30RSB0        | F13        | IO62NDB1        |

| B6         | IO14RSB0        | D10        | IO40RSB0        | F14        | IO49RSB0        |

| B7         | IO21RSB0        | D11        | IO46RSB0        | F15        | IO64PPB1        |

| B8         | IO27RSB0        | D12        | GNDQ            | F16        | IO66NDB1        |

| B9         | IO32RSB0        | D13        | IO47RSB0        | G1         | IO148NDB3       |

| B10        | IO38RSB0        | D14        | GBB2/IO61PPB1   | G2         | IO148PDB3       |

| B11        | IO42RSB0        | D15        | IO53RSB0        | G3         | IO149PPB3       |

| B12        | GBC1/IO55RSB0   | D16        | IO63NDB1        | G4         | GFC1/IO147PPB3  |

| B13        | GBB0/IO56RSB0   | E1         | IO150PDB3       | G5         | VCCIB3          |

| B14        | IO44RSB0        | E2         | IO08RSB0        | G6         | VCC             |

| B15        | GBA2/IO60PDB1   | E3         | IO153VDB3       | G7         | GND             |

| B16        | IO60NDB1        | E4         | IO152VDB3       | G8         | GND             |

| C1         | IO154VDB3       | E5         | VMV0            | G9         | GND             |

| C2         | IO155VDB3       | E6         | VCCIB0          | G10        | GND             |

| C3         | IO11RSB0        | E7         | VCCIB0          | G11        | VCC             |

| C4         | IO07RSB0        | E8         | IO25RSB0        | G12        | VCCIB1          |

Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                                                       | Page                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Revision 10<br>(continued) | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-28 • I/O Output Buffer Maximum Resistances1 through Table 2-30 • I/O Output Buffer Maximum Resistances1 was replaced by "Same as regular 3.3 V" (SAR 33852).                                                     | 2-26 to 2-28        |

|                            | The equations in the notes for Table 2-31 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 32470).                                                                                                                                                | 2-28                |

|                            | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-32 • I/O Short Currents IOSH/IOSL through Table 2-34 • I/O Short Currents IOSH/IOSL was replaced by "Same as regular 3.3 V LVCMOS" (SAR 33852).                                                                  | 2-29 to 2-31        |

|                            | In the "3.3 V LVCMOS Wide Range" section, values were added to Table 2-47 through Table 2-49 for IOSL and IOSH, replacing "TBD" (SAR 33852).                                                                                                                  | 2-39 to 2-40        |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 24916): "It uses a 5 V-tolerant input buffer and push-pull output buffer."                                                                                                            | 2-47                |

|                            | The table notes were revised for Table 2-90 • LVDS Minimum and Maximum DC Input and Output Levels (SAR 33859).                                                                                                                                                | 2-66                |

|                            | Values were added for $F_{DDRIMAX}$ and $F_{DDOMAX}$ in Table 2-102 • Input DDR Propagation Delays and Table 2-104 • Output DDR Propagation Delays (SAR 23919).                                                                                               | 2-78, 2-80          |

|                            | Table 2-115 • ProASIC3 CCC/PLL Specification was updated. A note was added to indicate that when the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available (SAR 25705).        | 2-90                |

|                            | The following figures were deleted (SAR 29991). Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 21770).                   | 2-92,               |

|                            | Figure 2-34 • Write Access after Write onto Same Address<br>Figure 2-35 • Read Access after Write onto Same Address<br>Figure 2-35 • Read Access after Write onto Same Address                                                                                | 2-94,<br>2-99 2-102 |

|                            | The port names in the SRAM "Timing Waveforms", SRAM "Timing Characteristics" tables, Figure 2-39 • FIFO Reset, and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SARs 29991, 30510).                   |                     |

|                            | The "Pin Descriptions" chapter has been added (SAR 21642).                                                                                                                                                                                                    | 3-1                 |

|                            | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                          | 4-1                 |

| July 2010                  | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "ProASIC3 Device Status" table on page IV indicates the status for each device in the device family. | N/A                 |