Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | ·                                                                          |

| Number of Logic Elements/Cells |                                                                            |

| Total RAM Bits                 | 147456                                                                     |

| Number of I/O                  | 97                                                                         |

| Number of Gates                | 1000000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 144-LBGA                                                                   |

| Supplier Device Package        | 144-FPBGA (13x13)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m7a3p1000-fg144i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# User Nonvolatile FlashROM

ProASIC3 devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- Internet protocol addressing (wireless or fixed)

- System calibration settings

- Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- · Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- Version management

The FlashROM is written using the standard ProASIC3 IEEE 1532 JTAG programming interface. The core can be individually programmed (erased and written), and on-chip AES decryption can be used selectively to securely load data over public networks (except in the A3P015 and A3P030 devices), as in security keys stored in the FlashROM for a user design.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

The ProASIC3 development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

# SRAM and FIFO

ProASIC3 devices (except the A3P015 and A3P030 devices) have embedded SRAM blocks along their north and south sides. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode) using the UJTAG macro (except in A3P015 and A3P030 devices).

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal Empty and Full flags. The embedded FIFO control unit contains the counters necessary for generation of the read and write address pointers. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

# PLL and CCC

ProASIC3 devices provide designers with very flexible clock conditioning capabilities. Each member of the ProASIC3 family contains six CCCs. One CCC (center west side) has a PLL. The A3P015 and A3P030 devices do not have a PLL.

The six CCC blocks are located at the four corners and the centers of the east and west sides.

All six CCC blocks are usable; the four corner CCCs and the east CCC allow simple clock delay operations as well as clock spine access.

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several inputs located near the CCC that have dedicated connections to the CCC block.

# **User I/O Characteristics**

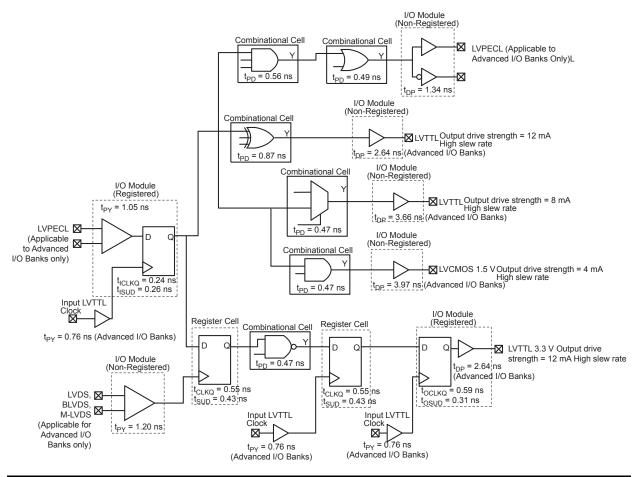

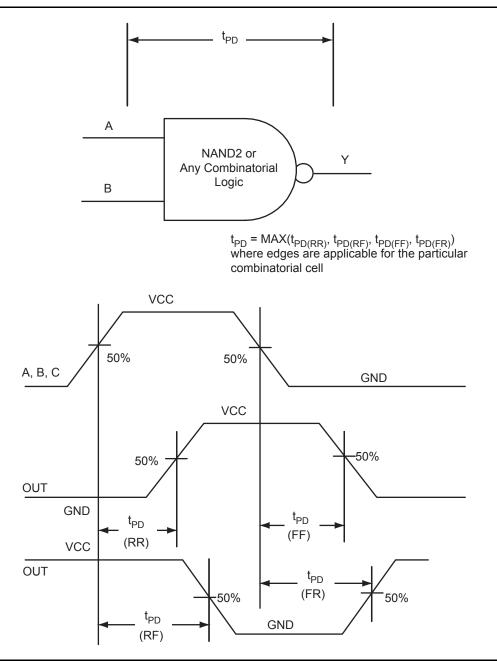

# **Timing Model**

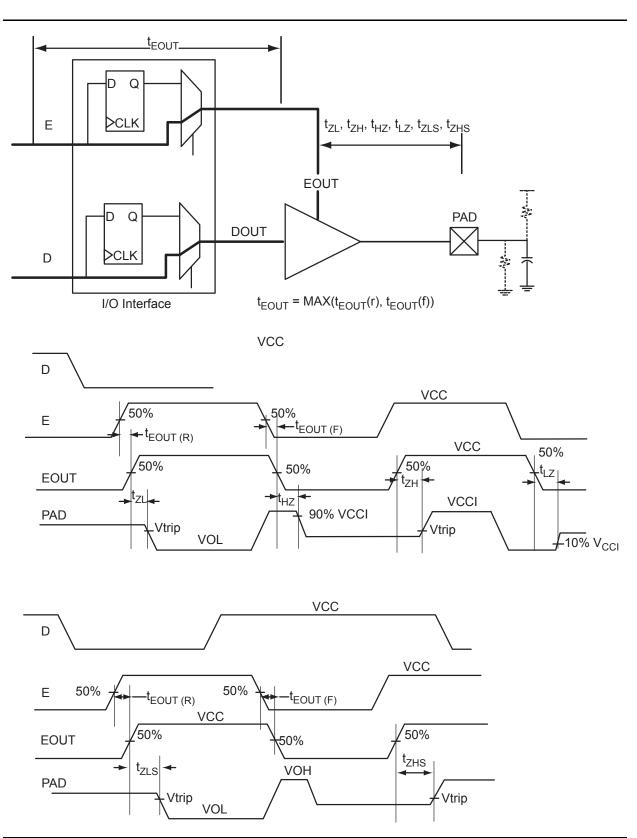

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (Example)

## 3.3 V LVCMOS Wide Range

# Table 2-47 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

| 3.3 V<br>LVCMOS<br>Wide Range | Equiv.<br>Software<br>Default            | v        | IL       | v        | ІН       | VOL      | voн       | IOL | ЮН  | IOSL                   | IOSH                   | IIL <sup>2</sup> | IIH <sup>3</sup> |

|-------------------------------|------------------------------------------|----------|----------|----------|----------|----------|-----------|-----|-----|------------------------|------------------------|------------------|------------------|

| Drive<br>Strength             | Drive<br>Strength<br>Option <sup>1</sup> | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V  | μA  | μA  | Max<br>mA <sup>4</sup> | Max<br>mA <sup>4</sup> | µA⁵              | μA <sup>5</sup>  |

| 100 µA                        | 2 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10               | 10               |

| 100 µA                        | 4 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10               | 10               |

| 100 µA                        | 6 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10               | 10               |

| 100 µA                        | 8 mA                                     | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10               | 10               |

| 100 µA                        | 12 mA                                    | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 103                    | 109                    | 10               | 10               |

| 100 µA                        | 16 mA                                    | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 132                    | 127                    | 10               | 10               |

| 100 µA                        | 24 mA                                    | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD - 0.2 | 100 | 100 | 268                    | 181                    | 10               | 10               |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

4. Currents are measured at 85°C junction temperature.

5. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

6. Software default selection highlighted in gray.

# Table 2-48 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

| 3.3 V LVCMOS<br>Wide Range | Equiv.<br>Software                                  | V        | L        | v        | ΊH       | VOL      | VOH       | IOL | ЮН  | IOSL                   | IOSH                   | IIL²            | IIH <sup>3</sup>        |

|----------------------------|-----------------------------------------------------|----------|----------|----------|----------|----------|-----------|-----|-----|------------------------|------------------------|-----------------|-------------------------|

| Drive Strength             | Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V  | μA  | μA  | Max<br>mA <sup>4</sup> | Max<br>mA <sup>4</sup> | μA <sup>5</sup> | μ <b>Α</b> <sup>5</sup> |

| 100 µA                     | 2 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10              | 10                      |

| 100 µA                     | 4 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 25                     | 27                     | 10              | 10                      |

| 100 µA                     | 6 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10              | 10                      |

| 100 µA                     | 8 mA                                                | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 51                     | 54                     | 10              | 10                      |

| 100 µA                     | 12 mA                                               | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 103                    | 109                    | 10              | 10                      |

| 100 μA                     | 16 mA                                               | -0.3     | 0.8      | 2        | 3.6      | 0.2      | VDD – 0.2 | 100 | 100 | 103                    | 109                    | 10              | 10                      |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

4. Currents are measured at 85°C junction temperature.

5. All LVMCOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

6. Software default selection highlighted in gray.

#### Table 2-83 • 1.5 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard Plus I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 12.08           | 0.04             | 1.42            | 0.43              | 12.01           | 12.08           | 2.72            | 2.43            | 14.24            | 14.31            | ns    |

|                   | -1             | 0.56              | 10.27           | 0.04             | 1.21            | 0.36              | 10.21           | 10.27           | 2.31            | 2.06            | 12.12            | 12.18            | ns    |

|                   | -2             | 0.49              | 9.02            | 0.03             | 1.06            | 0.32              | 8.97            | 9.02            | 2.03            | 1.81            | 10.64            | 10.69            | ns    |

| 4 mA              | Std.           | 0.66              | 9.28            | 0.04             | 1.42            | 0.43              | 9.45            | 8.91            | 3.04            | 3.00            | 11.69            | 11.15            | ns    |

|                   | -1             | 0.56              | 7.89            | 0.04             | 1.21            | 0.36              | 8.04            | 7.58            | 2.58            | 2.55            | 9.94             | 9.49             | ns    |

|                   | -2             | 0.49              | 6.93            | 0.03             | 1.06            | 0.32              | 7.06            | 6.66            | 2.27            | 2.24            | 8.73             | 8.33             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# Table 2-84 • 1.5 V LVCMOS High Slew Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.65            | 0.04             | 1.42            | 0.43              | 6.31            | 7.65            | 2.45            | 2.45            | ns    |

|                   | -1             | 0.56              | 6.50            | 0.04             | 1.21            | 0.36              | 5.37            | 6.50            | 2.08            | 2.08            | ns    |

|                   | -2             | 0.49              | 5.71            | 0.03             | 1.06            | 0.32              | 4.71            | 5.71            | 1.83            | 1.83            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-85 • 1.5 V LVCMOS Low Slew Commercial-Case Conditions

#### Commercial-Case Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 12.33           | 0.04             | 1.42            | 0.43              | 11.79           | 12.33           | 2.45            | 2.32            | ns    |

|                   | -1             | 0.56              | 10.49           | 0.04             | 1.21            | 0.36              | 10.03           | 10.49           | 2.08            | 1.98            | ns    |

|                   | -2             | 0.49              | 9.21            | 0.03             | 1.06            | 0.32              | 8.81            | 9.21            | 1.83            | 1.73            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

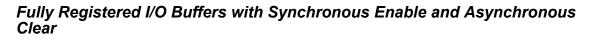

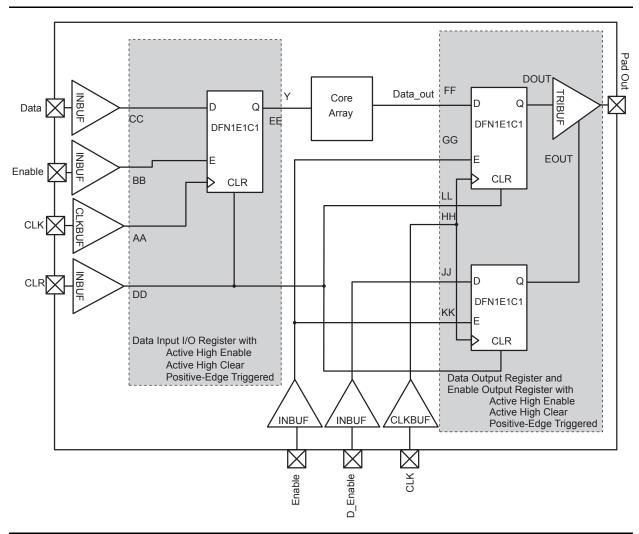

Figure 2-16 • Timing Model of the Registered I/O Buffers with Synchronous Enable and Asynchronous Clear

Figure 2-25 • Timing Model and Waveforms

### Table 2-109 • A3P060 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2                |                   | -1                | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.71              | 0.93              | 0.81              | 1.05              | 0.95              | 1.24              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.70              | 0.96              | 0.80              | 1.09              | 0.94              | 1.28              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Microse

Power Matters.

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-110 • A3P125 Global Resource

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

```

|                      |                                           | -                 | -2                |                   | -1                | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.77              | 0.99              | 0.87              | 1.12              | 1.03              | 1.32              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.76              | 1.02              | 0.87              | 1.16              | 1.02              | 1.37              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-111 • A3P250 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2                |                   | -1                | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.80              | 1.01              | 0.91              | 1.15              | 1.07              | 1.36              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.78              | 1.04              | 0.89              | 1.18              | 1.04              | 1.39              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-112 • A3P400 Global Resource

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

```

|                      |                                           | -                 | -2                |                   | -1                | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.87              | 1.09              | 0.99              | 1.24              | 1.17              | 1.46              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.86              | 1.11              | 0.98              | 1.27              | 1.15              | 1.49              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# **Timing Characteristics**

# Table 2-118 • FIFO (for all dies except A3P250)Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.34 | 1.52 | 1.79 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# 3 – Pin Descriptions

# **Supply Pins**

#### Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

#### GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ must always be connected to GND on the board.

#### VCC

GND

#### Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is required for powering the JTAG state machine in addition to VJTAG. Even when a device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the device.

#### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are up to eight I/O banks on low power flash devices plus a dedicated VJTAG bank. Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. In general, unused I/O banks should have their corresponding VCCIX pins tied to GND. If an output pad is terminated to ground through any resistor and if the corresponding VCCIX is left floating, then the leakage current to ground is ~ 0uA. However, if an output pad is terminated to ground is ~ 3 uA. For unused banks the aforementioned behavior is to be taken into account while deciding if it's better to float VCCIX of unused bank or tie it to GND.

## VMVx I/O Supply Voltage (quiet)

Quiet supply voltage to the input buffers of each I/O bank. *x* is the bank number. Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks. This minimizes the noise transfer within the package and improves input signal integrity. Each bank must have at least one VMV connection, and no VMV should be left unconnected. All I/Os in a bank run off the same VMVx supply. VMV is used to provide a quiet supply voltage to the input buffers of each I/O bank. VMVx can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VMV pins tied to GND. VMV and VCCI should be at the same voltage within a given I/O bank. Used VMV pins must be connected to the corresponding VCCI pins of the same bank (i.e., VMV0 to VCCIB0, VMV1 to VCCIB1, etc.).

## VCCPLA/B/C/D/E/F PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V.

When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Microsemi recommends tying VCCPLx to VCC and using proper filtering circuits to decouple VCC noise from the PLLs. Refer to the PLL Power Supply Decoupling section of the "Clock Conditioning Circuits in IGLOO and ProASIC3 Devices" chapter of the *ProASIC3 FPGA Fabric User's Guide* for a complete board solution for the PLL analog power supply and ground.

There is one VCCPLF pin on ProASIC3 devices.

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There is one VCOMPLF pin on ProASIC3 devices.

In critical applications, an upset in the JTAG circuit could allow entrance to an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

# **Special Function Pins**

#### NC

#### No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

# **Related Documents**

# **User's Guides**

ProASIC FPGA Fabric User's Guide http://www.microsemi.com/soc/documents/PA3\_UG.pdf

# Packaging

The following documents provide packaging information and device selection for low power flash devices.

## **Product Catalog**

http://www.microsemi.com/soc/documents/ProdCat\_PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

## Package Mechanical Drawings

http://www.microsemi.com/soc/documents/PckgMechDrwngs.pdf

This document contains the package mechanical drawings for all packages currently or previously supplied by Actel. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials are at http://www.microsemi.com/products/solutions/package/docs.aspx.

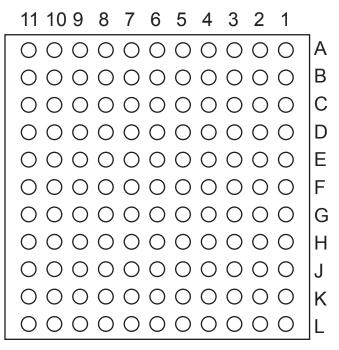

# **CS121 – Bottom View**

Note: The die attach paddle center of the package is tied to ground (GND).

## Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

Package Pin Assignments

|            | VQ100           | ,          | VQ100           | ,          | VQ100           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| 1          | GND             | 37         | VCC             | 73         | GBA2/IO41PDB1   |

| 2          | GAA2/IO118UDB3  | 38         | GND             | 74         | VMV1            |

| 3          | IO118VDB3       | 39         | VCCIB2          | 75         | GNDQ            |

| 4          | GAB2/IO117UDB3  | 40         | IO77RSB2        | 76         | GBA1/IO40RSB0   |

| 5          | IO117VDB3       | 41         | IO74RSB2        | 77         | GBA0/IO39RSB0   |

| 6          | GAC2/IO116UDB3  | 42         | IO71RSB2        | 78         | GBB1/IO38RSB0   |

| 7          | IO116VDB3       | 43         | GDC2/IO63RSB2   | 79         | GBB0/IO37RSB0   |

| 8          | IO112PSB3       | 44         | GDB2/IO62RSB2   | 80         | GBC1/IO36RSB0   |

| 9          | GND             | 45         | GDA2/IO61RSB2   | 81         | GBC0/IO35RSB0   |

| 10         | GFB1/IO109PDB3  | 46         | GNDQ            | 82         | IO29RSB0        |

| 11         | GFB0/IO109NDB3  | 47         | ТСК             | 83         | IO27RSB0        |

| 12         | VCOMPLF         | 48         | TDI             | 84         | IO25RSB0        |

| 13         | GFA0/IO108NPB3  | 49         | TMS             | 85         | IO23RSB0        |

| 14         | VCCPLF          | 50         | VMV2            | 86         | IO21RSB0        |

| 15         | GFA1/IO108PPB3  | 51         | GND             | 87         | VCCIB0          |

| 16         | GFA2/IO107PSB3  | 52         | VPUMP           | 88         | GND             |

| 17         | VCC             | 53         | NC              | 89         | VCC             |

| 18         | VCCIB3          | 54         | TDO             | 90         | IO15RSB0        |

| 19         | GFC2/IO105PSB3  | 55         | TRST            | 91         | IO13RSB0        |

| 20         | GEC1/IO100PDB3  | 56         | VJTAG           | 92         | IO11RSB0        |

| 21         | GEC0/IO100NDB3  | 57         | GDA1/IO60USB1   | 93         | GAC1/IO05RSB0   |

| 22         | GEA1/IO98PDB3   | 58         | GDC0/IO58VDB1   | 94         | GAC0/IO04RSB0   |

| 23         | GEA0/IO98NDB3   | 59         | GDC1/IO58UDB1   | 95         | GAB1/IO03RSB0   |

| 24         | VMV3            | 60         | IO52NDB1        | 96         | GAB0/IO02RSB0   |

| 25         | GNDQ            | 61         | GCB2/IO52PDB1   | 97         | GAA1/IO01RSB0   |

| 26         | GEA2/IO97RSB2   | 62         | GCA1/IO50PDB1   | 98         | GAA0/IO00RSB0   |

| 27         | GEB2/IO96RSB2   | 63         | GCA0/IO50NDB1   | 99         | GNDQ            |

| 28         | GEC2/IO95RSB2   | 64         | GCC0/IO48NDB1   | 100        | VMV0            |

| 29         | IO93RSB2        | 65         | GCC1/IO48PDB1   |            |                 |

| 30         | IO92RSB2        | 66         | VCCIB1          |            |                 |

| 31         | IO91RSB2        | 67         | GND             |            |                 |

| 32         | IO90RSB2        | 68         | VCC             |            |                 |

| 33         | IO88RSB2        | 69         | IO43NDB1        |            |                 |

| 34         | IO86RSB2        | 70         | GBC2/IO43PDB1   |            |                 |

| 35         | IO85RSB2        | 71         | GBB2/IO42PSB1   |            |                 |

| 36         | IO84RSB2        | 72         | IO41NDB1        |            |                 |

|            | PQ208           | PQ208      |                 | PQ208      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| 1          | GND             | 37         | IO104PDB3       | 73         | IO83RSB2        |

| 2          | GAA2/IO118UDB3  | 38         | IO104NDB3       | 74         | IO82RSB2        |

| 3          | IO118VDB3       | 39         | IO103PSB3       | 75         | IO81RSB2        |

| 4          | GAB2/IO117UDB3  | 40         | VCCIB3          | 76         | IO80RSB2        |

| 5          | IO117VDB3       | 41         | GND             | 77         | IO79RSB2        |

| 6          | GAC2/IO116UDB3  | 42         | IO101PDB3       | 78         | IO78RSB2        |

| 7          | IO116VDB3       | 43         | IO101NDB3       | 79         | IO77RSB2        |

| 8          | IO115UDB3       | 44         | GEC1/IO100PDB3  | 80         | IO76RSB2        |

| 9          | IO115VDB3       | 45         | GEC0/IO100NDB3  | 81         | GND             |

| 10         | IO114UDB3       | 46         | GEB1/IO99PDB3   | 82         | IO75RSB2        |

| 11         | IO114VDB3       | 47         | GEB0/IO99NDB3   | 83         | IO74RSB2        |

| 12         | IO113PDB3       | 48         | GEA1/IO98PDB3   | 84         | IO73RSB2        |

| 13         | IO113NDB3       | 49         | GEA0/IO98NDB3   | 85         | IO72RSB2        |

| 14         | IO112PDB3       | 50         | VMV3            | 86         | IO71RSB2        |

| 15         | IO112NDB3       | 51         | GNDQ            | 87         | IO70RSB2        |

| 16         | VCC             | 52         | GND             | 88         | VCC             |

| 17         | GND             | 53         | NC              | 89         | VCCIB2          |

| 18         | VCCIB3          | 54         | NC              | 90         | IO69RSB2        |

| 19         | IO111PDB3       | 55         | GEA2/IO97RSB2   | 91         | IO68RSB2        |

| 20         | IO111NDB3       | 56         | GEB2/IO96RSB2   | 92         | IO67RSB2        |

| 21         | GFC1/IO110PDB3  | 57         | GEC2/IO95RSB2   | 93         | IO66RSB2        |

| 22         | GFC0/IO110NDB3  | 58         | IO94RSB2        | 94         | IO65RSB2        |

| 23         | GFB1/IO109PDB3  | 59         | IO93RSB2        | 95         | IO64RSB2        |

| 24         | GFB0/IO109NDB3  | 60         | IO92RSB2        | 96         | GDC2/IO63RSB2   |

| 25         | VCOMPLF         | 61         | IO91RSB2        | 97         | GND             |

| 26         | GFA0/IO108NPB3  | 62         | VCCIB2          | 98         | GDB2/IO62RSB2   |

| 27         | VCCPLF          | 63         | IO90RSB2        | 99         | GDA2/IO61RSB2   |

| 28         | GFA1/IO108PPB3  | 64         | IO89RSB2        | 100        | GNDQ            |

| 29         | GND             | 65         | GND             | 101        | ТСК             |

| 30         | GFA2/IO107PDB3  | 66         | IO88RSB2        | 102        | TDI             |

| 31         | IO107NDB3       | 67         | IO87RSB2        | 103        | TMS             |

| 32         | GFB2/IO106PDB3  | 68         | IO86RSB2        | 104        | VMV2            |

| 33         | IO106NDB3       | 69         | IO85RSB2        | 105        | GND             |

| 34         | GFC2/IO105PDB3  | 70         | IO84RSB2        | 106        | VPUMP           |

| 35         | IO105NDB3       | 71         | VCC             | 107        | NC              |

| 36         | NC              | 72         | VCCIB2          | 108        | TDO             |

| P          | Q208            | PQ208      |                 | PQ208      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P400 Function | Pin Number | A3P400 Function | Pin Number | A3P400 Function |

| 1          | GND             | 37         | IO141PSB3       | 73         | IO112RSB2       |

| 2          | GAA2/IO155UDB3  | 38         | IO140PDB3       | 74         | IO111RSB2       |

| 3          | IO155VDB3       | 39         | IO140NDB3       | 75         | IO110RSB2       |

| 4          | GAB2/IO154UDB3  | 40         | VCCIB3          | 76         | IO109RSB2       |

| 5          | IO154VDB3       | 41         | GND             | 77         | IO108RSB2       |

| 6          | GAC2/IO153UDB3  | 42         | IO138PDB3       | 78         | IO107RSB2       |

| 7          | IO153VDB3       | 43         | IO138NDB3       | 79         | IO106RSB2       |

| 8          | IO152UDB3       | 44         | GEC1/IO137PDB3  | 80         | IO104RSB2       |

| 9          | IO152VDB3       | 45         | GEC0/IO137NDB3  | 81         | GND             |

| 10         | IO151UDB3       | 46         | GEB1/IO136PDB3  | 82         | IO102RSB2       |

| 11         | IO151VDB3       | 47         | GEB0/IO136NDB3  | 83         | IO101RSB2       |

| 12         | IO150PDB3       | 48         | GEA1/IO135PDB3  | 84         | IO100RSB2       |

| 13         | IO150NDB3       | 49         | GEA0/IO135NDB3  | 85         | IO99RSB2        |

| 14         | IO149PDB3       | 50         | VMV3            | 86         | IO98RSB2        |

| 15         | IO149NDB3       | 51         | GNDQ            | 87         | IO97RSB2        |

| 16         | VCC             | 52         | GND             | 88         | VCC             |

| 17         | GND             | 53         | VMV2            | 89         | VCCIB2          |

| 18         | VCCIB3          | 54         | NC              | 90         | IO94RSB2        |

| 19         | IO148PDB3       | 55         | GEA2/IO134RSB2  | 91         | IO92RSB2        |

| 20         | IO148NDB3       | 56         | GEB2/IO133RSB2  | 92         | IO90RSB2        |

| 21         | GFC1/IO147PDB3  | 57         | GEC2/IO132RSB2  | 93         | IO88RSB2        |

| 22         | GFC0/IO147NDB3  | 58         | IO131RSB2       | 94         | IO86RSB2        |

| 23         | GFB1/IO146PDB3  | 59         | IO130RSB2       | 95         | IO84RSB2        |

| 24         | GFB0/IO146NDB3  | 60         | IO129RSB2       | 96         | GDC2/IO82RSB2   |

| 25         | VCOMPLF         | 61         | IO128RSB2       | 97         | GND             |

| 26         | GFA0/IO145NPB3  | 62         | VCCIB2          | 98         | GDB2/IO81RSB2   |

| 27         | VCCPLF          | 63         | IO125RSB2       | 99         | GDA2/IO80RSB2   |

| 28         | GFA1/IO145PPB3  | 64         | IO123RSB2       | 100        | GNDQ            |

| 29         | GND             | 65         | GND             | 101        | ТСК             |

| 30         | GFA2/IO144PDB3  | 66         | IO121RSB2       | 102        | TDI             |

| 31         | IO144NDB3       | 67         | IO119RSB2       | 103        | TMS             |

| 32         | GFB2/IO143PDB3  | 68         | IO117RSB2       | 104        | VMV2            |

| 33         | IO143NDB3       | 69         | IO115RSB2       | 105        | GND             |

| 34         | GFC2/IO142PDB3  | 70         | IO113RSB2       | 106        | VPUMP           |

| 35         | IO142NDB3       | 71         | VCC             | 107        | NC              |

| 36         | NC              | 72         | VCCIB2          | 108        | TDO             |

# 🌜 Microsemi.

Package Pin Assignments

| F          | G144            | F          | G144            | FG144      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P060 Function | Pin Number | A3P060 Function | Pin Number | A3P060 Function |

| A1         | GNDQ            | D1         | IO91RSB1        | G1         | GFA1/IO84RSB1   |

| A2         | VMV0            | D2         | IO92RSB1        | G2         | GND             |

| A3         | GAB0/IO04RSB0   | D3         | IO93RSB1        | G3         | VCCPLF          |

| A4         | GAB1/IO05RSB0   | D4         | GAA2/IO51RSB1   | G4         | GFA0/IO85RSB1   |

| A5         | IO08RSB0        | D5         | GAC0/IO06RSB0   | G5         | GND             |

| A6         | GND             | D6         | GAC1/IO07RSB0   | G6         | GND             |

| A7         | IO11RSB0        | D7         | GBC0/IO19RSB0   | G7         | GND             |

| A8         | VCC             | D8         | GBC1/IO20RSB0   | G8         | GDC1/IO45RSB0   |

| A9         | IO16RSB0        | D9         | GBB2/IO27RSB0   | G9         | IO32RSB0        |

| A10        | GBA0/IO23RSB0   | D10        | IO18RSB0        | G10        | GCC2/IO43RSB0   |

| A11        | GBA1/IO24RSB0   | D11        | IO28RSB0        | G11        | IO31RSB0        |

| A12        | GNDQ            | D12        | GCB1/IO37RSB0   | G12        | GCB2/IO42RSB0   |

| B1         | GAB2/IO53RSB1   | E1         | VCC             | H1         | VCC             |

| B2         | GND             | E2         | GFC0/IO88RSB1   | H2         | GFB2/IO82RSB1   |

| B3         | GAA0/IO02RSB0   | E3         | GFC1/IO89RSB1   | H3         | GFC2/IO81RSB1   |

| B4         | GAA1/IO03RSB0   | E4         | VCCIB1          | H4         | GEC1/IO77RSB1   |

| B5         | IO00RSB0        | E5         | IO52RSB1        | H5         | VCC             |

| B6         | IO10RSB0        | E6         | VCCIB0          | H6         | IO34RSB0        |

| B7         | IO12RSB0        | E7         | VCCIB0          | H7         | IO44RSB0        |

| B8         | IO14RSB0        | E8         | GCC1/IO35RSB0   | H8         | GDB2/IO55RSB1   |

| B9         | GBB0/IO21RSB0   | E9         | VCCIB0          | H9         | GDC0/IO46RSB0   |

| B10        | GBB1/IO22RSB0   | E10        | VCC             | H10        | VCCIB0          |

| B11        | GND             | E11        | GCA0/IO40RSB0   | H11        | IO33RSB0        |

| B12        | VMV0            | E12        | IO30RSB0        | H12        | VCC             |

| C1         | IO95RSB1        | F1         | GFB0/IO86RSB1   | J1         | GEB1/IO75RSB1   |

| C2         | GFA2/IO83RSB1   | F2         | VCOMPLF         | J2         | IO78RSB1        |

| C3         | GAC2/IO94RSB1   | F3         | GFB1/IO87RSB1   | J3         | VCCIB1          |

| C4         | VCC             | F4         | IO90RSB1        | J4         | GEC0/IO76RSB1   |

| C5         | IO01RSB0        | F5         | GND             | J5         | IO79RSB1        |

| C6         | IO09RSB0        | F6         | GND             | J6         | IO80RSB1        |

| C7         | IO13RSB0        | F7         | GND             | J7         | VCC             |

| C8         | IO15RSB0        | F8         | GCC0/IO36RSB0   | J8         | ТСК             |

| C9         | IO17RSB0        | F9         | GCB0/IO38RSB0   | J9         | GDA2/IO54RSB1   |

| C10        | GBA2/IO25RSB0   | F10        | GND             | J10        | TDO             |

| C11        | IO26RSB0        | F11        | GCA1/IO39RSB0   | J11        | GDA1/IO49RSB0   |

| C12        | GBC2/IO29RSB0   | F12        | GCA2/IO41RSB0   | J12        | GDB1/IO47RSB0   |

|            | FG256           |            | FG256           | FG256      |                 |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| A1         | GND             | C5         | GAC0/IO04RSB0   | E9         | IO24RSB0        |

| A2         | GAA0/IO00RSB0   | C6         | GAC1/IO05RSB0   | E10        | VCCIB0          |

| A3         | GAA1/IO01RSB0   | C7         | IO13RSB0        | E11        | VCCIB0          |

| A4         | GAB0/IO02RSB0   | C8         | IO17RSB0        | E12        | VMV1            |

| A5         | IO07RSB0        | C9         | IO22RSB0        | E13        | GBC2/IO43PDB1   |

| A6         | IO10RSB0        | C10        | IO27RSB0        | E14        | IO46RSB1        |

| A7         | IO11RSB0        | C11        | IO31RSB0        | E15        | NC              |

| A8         | IO15RSB0        | C12        | GBC0/IO35RSB0   | E16        | IO45PDB1        |

| A9         | IO20RSB0        | C13        | IO34RSB0        | F1         | IO113NDB3       |

| A10        | IO25RSB0        | C14        | NC              | F2         | IO112PPB3       |

| A11        | IO29RSB0        | C15        | IO42NPB1        | F3         | NC              |

| A12        | IO33RSB0        | C16        | IO44PDB1        | F4         | IO115VDB3       |

| A13        | GBB1/IO38RSB0   | D1         | IO114VDB3       | F5         | VCCIB3          |

| A14        | GBA0/IO39RSB0   | D2         | IO114UDB3       | F6         | GND             |

| A15        | GBA1/IO40RSB0   | D3         | GAC2/IO116UDB3  | F7         | VCC             |

| A16        | GND             | D4         | NC              | F8         | VCC             |

| B1         | GAB2/IO117UDB3  | D5         | GNDQ            | F9         | VCC             |

| B2         | GAA2/IO118UDB3  | D6         | IO08RSB0        | F10        | VCC             |

| B3         | NC              | D7         | IO14RSB0        | F11        | GND             |

| B4         | GAB1/IO03RSB0   | D8         | IO18RSB0        | F12        | VCCIB1          |

| B5         | IO06RSB0        | D9         | IO23RSB0        | F13        | IO43NDB1        |

| B6         | IO09RSB0        | D10        | IO28RSB0        | F14        | NC              |

| B7         | IO12RSB0        | D11        | IO32RSB0        | F15        | IO47PPB1        |

| B8         | IO16RSB0        | D12        | GNDQ            | F16        | IO45NDB1        |

| B9         | IO21RSB0        | D13        | NC              | G1         | IO111NDB3       |

| B10        | IO26RSB0        | D14        | GBB2/IO42PPB1   | G2         | IO111PDB3       |

| B11        | IO30RSB0        | D15        | NC              | G3         | IO112NPB3       |

| B12        | GBC1/IO36RSB0   | D16        | IO44NDB1        | G4         | GFC1/IO110PPB3  |

| B13        | GBB0/IO37RSB0   | E1         | IO113PDB3       | G5         | VCCIB3          |

| B14        | NC              | E2         | NC              | G6         | VCC             |

| B15        | GBA2/IO41PDB1   | E3         | IO116VDB3       | G7         | GND             |

| B16        | IO41NDB1        | E4         | IO115UDB3       | G8         | GND             |

| C1         | IO117VDB3       | E5         | VMV0            | G9         | GND             |

| C2         | IO118VDB3       | E6         | VCCIB0          | G10        | GND             |

| C3         | NC              | E7         | VCCIB0          | G11        | VCC             |

| C4         | NC              | E8         | IO19RSB0        | G12        | VCCIB1          |

| Revision                                    | Changes                                                                                                                                                                                                                                      | Page   |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Revision 9 (Oct 2009)<br>Product Brief v1.3 | The CS121 package was added to table under "Features and Benefits" section, the "I/Os Per Package 1" table, Table 1 • ProASIC3 FPGAs Package Sizes Dimensions, "ProASIC3 Ordering Information", and the "Temperature Grade Offerings" table. | I – IV |

|                                             | "ProASIC3 Ordering Information" was revised to include the fact that some RoHS compliant packages are halogen-free.                                                                                                                          | IV     |

| Packaging v1.5                              | The "CS121 – Bottom View" figure and pin table for A3P060 are new.                                                                                                                                                                           | 4-15   |

| Revision 8 (Aug 2009)<br>Product Brief v1.2 | All references to M7 devices (CoreMP7) and speed grade –F were removed from this document.                                                                                                                                                   |        |

|                                             | Table 1-1 I/O Standards supported is new.                                                                                                                                                                                                    | 1-7    |

|                                             | The I/Os with Advanced I/O Standards section was revised to add definitions of hot-swap and cold-sparing.                                                                                                                                    | 1-7    |

| DC and Switching<br>Characteristics v1.4    | $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS Wide Range support was added to the datasheet. This affects all tables that contained $3.3~\rm V$ LVCMOS and $1.2~\rm V$ LVCMOS data.                                                              | N/A    |

|                                             | $\rm I_{\rm IL}$ and $\rm I_{\rm IH}$ input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                            | N/A    |

|                                             | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                   | N/A    |

|                                             | The notes in Table 2-2 • Recommended Operating Conditions 1 were updated.                                                                                                                                                                    | 2-2    |

|                                             | Table 2-4 • Overshoot and Undershoot Limits 1 was updated.                                                                                                                                                                                   | 2-3    |

|                                             | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays was updated.                                                                                                                                                          | 2-6    |

|                                             | In Table 2-116 • RAM4K9, the following specifications were removed:<br>t <sub>WRO</sub><br>t <sub>CCKH</sub>                                                                                                                                 | 2-96   |

|                                             | In Table 2-117 • RAM512X18, the following specifications were removed:<br>t <sub>WRO</sub><br>t <sub>CCKH</sub>                                                                                                                              | 2-97   |

|                                             | In the title of Table 2-74 • 1.8 V LVCMOS High Slew, VCCI had a typo. It was changed from 3.0 V to 1.7 V.                                                                                                                                    | 2-58   |

| Revision 7 (Feb 2009)<br>Product Brief v1.1 | The "Advanced I/O" section was revised to add a bullet regarding wide range power supply voltage support.                                                                                                                                    | I      |

|                                             | The table under "Features and Benefits" section, was updated to include a value for typical equivalent macrocells for A3P250.                                                                                                                | I      |

|                                             | The QN48 package was added to the following tables: the table under "Features<br>and Benefits" section, "I/Os Per Package 1" "ProASIC3 FPGAs Package Sizes<br>Dimensions", and "Temperature Grade Offerings".                                | N/A    |

|                                             | The number of singled-ended I/Os for QN68 was added to the "I/Os Per Package 1" table.                                                                                                                                                       |        |

|                                             | The Wide Range I/O Support section is new.                                                                                                                                                                                                   | 1-7    |

| Revision 6 (Dec 2008)                       | The "QN48 – Bottom View" section is new.                                                                                                                                                                                                     | 4-1    |

| Packaging v1.4                              | The "QN68" pin table for A3P030 is new.                                                                                                                                                                                                      | 4-5    |

# **Datasheet Categories**

## Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "ProASIC3 Device Status" table on page IV, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

## **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

## Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

## Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

## Unmarked (production)

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.