Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

ĿXF

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 147456                                                                     |

| Number of I/O                  | 97                                                                         |

| Number of Gates                | 1000000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 144-LBGA                                                                   |

| Supplier Device Package        | 144-FPBGA (13x13)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m7a3p1000-fgg144 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

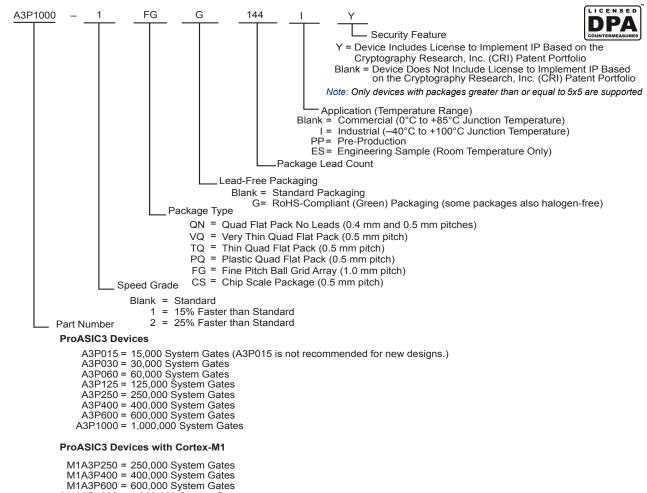

# **ProASIC3 Ordering Information**

### M1A3P1000 = 1,000,000 System Gates

# **ProASIC3** Device Status

| ProASIC3 Devices | Status                           | Cortex-M1 Devices | Status     |

|------------------|----------------------------------|-------------------|------------|

| A3P015           | Not recommended for new designs. |                   |            |

| A3P030           | Production                       |                   |            |

| A3P060           | Production                       |                   |            |

| A3P125           | Production                       |                   |            |

| A3P250           | Production                       | M1A3P250          | Production |

| A3P400           | Production                       | M1A3P400          | Production |

| A3P600           | Production                       | M1A3P600          | Production |

| A3P1000          | Production                       | M1A3P1000         | Production |

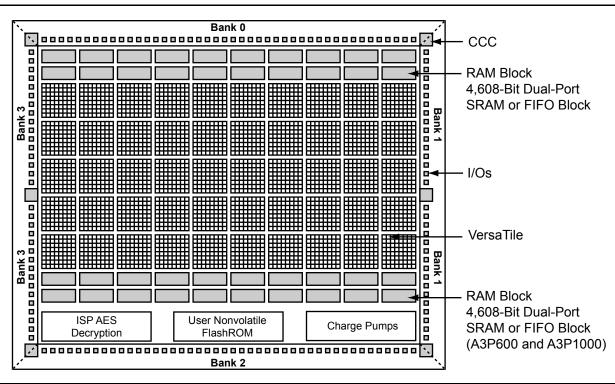

Figure 1-2 • ProASIC3 Device Architecture Overview with Four I/O Banks (A3P250, A3P600, and A3P1000)

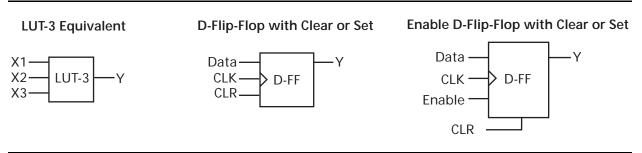

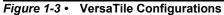

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the ProASIC3 core tile as either a three-input lookup table (LUT) equivalent or as a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the Microsemi ProASIC family of third-generation architecture flash FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

### VersaTiles

The ProASIC3 core consists of VersaTiles, which have been enhanced beyond the ProASIC<sup>PLUS®</sup> core tiles. The ProASIC3 VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-3 for VersaTile configurations.

|           | Definition                                       | Device Specific Static Powe                                    |                                                              |        |        |        |        | r (mW) |        |  |

|-----------|--------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|

| Parameter |                                                  | A3P1000                                                        | A3P600                                                       | A3P400 | A3P250 | A3P125 | A3P060 | A3P030 | A3P015 |  |

| PDC1      | Array static power in Active mode                | See Table 2-7 on page 2-7.                                     |                                                              |        |        |        |        |        |        |  |

| PDC2      | I/O input pin static power (standard-dependent)  |                                                                | See Table 2-8 on page 2-7 through<br>Table 2-10 on page 2-8. |        |        |        |        |        |        |  |

| PDC3      | I/O output pin static power (standard-dependent) | See Table 2-11 on page 2-9 through<br>Table 2-13 on page 2-10. |                                                              |        |        |        |        |        |        |  |

| PDC4      | Static PLL contribution                          | 2.55 mW                                                        |                                                              |        |        |        |        |        |        |  |

| PDC5      | Bank quiescent power (VCCI-dependent)            | See Table 2-7 on page 2-7.                                     |                                                              |        |        |        |        |        |        |  |

#### Table 2-15 • Different Components Contributing to the Static Power Consumption in ProASIC3 Devices

*Note:* \*For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi Power spreadsheet calculator or SmartPower tool in Libero SoC software.

## **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs as well as the number and the frequency of each output clock generated

- · The number of combinatorial and sequential cells used in the design

- · The internal clock frequencies

- The number and the standard of I/O pins used in the design

- · The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-16 on page 2-14.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-17 on page 2-14.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-17 on page 2-14. The calculation should be repeated for each clock domain defined in the design.

### Methodology

#### Total Power Consumption—PTOTAL

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

### Total Static Power Consumption—P<sub>STAT</sub>

$P_{STAT} = P_{DC1} + N_{INPUTS} + P_{DC2} + N_{OUTPUTS} + P_{DC3}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

#### Total Dynamic Power Consumption—P<sub>DYN</sub>

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub>

### Global Clock Contribution—P<sub>CLOCK</sub>

$P_{CLOCK} = (P_{AC1} + N_{SPINE}*P_{AC2} + N_{ROW}*P_{AC3} + N_{S-CELL}*P_{AC4})*F_{CLK}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3 FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3 FPGA Fabric User's Guide*.

Figure 2-4 • Input Buffer Timing Model and Delays (Example)

#### Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings Applicable to Standard I/O Banks

|                                            |                   | Equiv.                                                          |      |          | VIL         | VIH         |          | VOL         | VOH         |                        |                        |

|--------------------------------------------|-------------------|-----------------------------------------------------------------|------|----------|-------------|-------------|----------|-------------|-------------|------------------------|------------------------|

| I/O Standard                               | Drive<br>Strength | Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Slew | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V    | Min<br>V    | IOL <sup>1</sup><br>mA | IOH <sup>1</sup><br>mA |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS           | 8 mA              | 8 mA                                                            | High | -0.3     | 0.8         | 2           | 3.6      | 0.4         | 2.4         | 8                      | 8                      |

| 3.3 V<br>LVCMOS<br>Wide Range <sup>3</sup> | 100 µA            | 8 mA                                                            | High | -0.3     | 0.8         | 2           | 3.6      | 0.2         | VCCI – 0.2  | 0.1                    | 0.1                    |

| 2.5 V<br>LVCMOS                            | 8 mA              | 8 mA                                                            | High | -0.3     | 0.7         | 1.7         | 2.7      | 0.7         | 1.7         | 8                      | 8                      |

| 1.8 V<br>LVCMOS                            | 4 mA              | 4 mA                                                            | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45        | VCCI – 0.45 | 4                      | 4                      |

| 1.5 V<br>LVCMOS                            | 2 mA              | 2 mA                                                            | High | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.25 * VCCI | 0.75 * VCCI | 2                      | 2                      |

Notes:

1. Currents are measured at 85°C junction temperature.

2. 3.3 V LVCMOS wide range is applicable to 100 μA drive strength only. The configuration will NOT operate at the equivalent software default drive strength. These values are for Normal Ranges ONLY.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

# Table 2-21 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions

|                            | Comr             | nercial <sup>1</sup> | Indus            | strial <sup>2</sup> |

|----------------------------|------------------|----------------------|------------------|---------------------|

|                            | IIL <sup>3</sup> | IIH <sup>4</sup>     | IIL <sup>3</sup> | IIH <sup>4</sup>    |

| DC I/O Standards           | μΑ               | μA                   | μA               | μA                  |

| 3.3 V LVTTL / 3.3 V LVCMOS | 10               | 10                   | 15               | 15                  |

| 3.3 V LVCMOS Wide Range    | 10               | 10                   | 15               | 15                  |

| 2.5 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 1.8 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 1.5 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 3.3 V PCI                  | 10               | 10                   | 15               | 15                  |

| 3.3 V PCI-X                | 10               | 10                   | 15               | 15                  |

Notes:

1. Commercial range ( $0^{\circ}C < T_A < 70^{\circ}C$ )

2. Industrial range  $(-40^{\circ}C < T_A < 85^{\circ}C)$

- 3. IIL is the input leakage current per I/O pin over recommended operation conditions where  $-0.3V < V_{IN} < V_{IL}$ .

- 4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

#### Table 2-34 • I/O Short Currents IOSH/IOSL Applicable to Standard I/O Banks

|                                      | Drive Strength | IOSL (mA) <sup>1</sup>          | IOSH (mA) <sup>1</sup>          |

|--------------------------------------|----------------|---------------------------------|---------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS           | 2 mA           | 27                              | 25                              |

|                                      | 4 mA           | 27                              | 25                              |

|                                      | 6 mA           | 54                              | 51                              |

|                                      | 8 mA           | 54                              | 51                              |

| 3.3 V LVCMOS Wide Range <sup>2</sup> | 100 µA         | Same as regular 3.3 V<br>LVCMOS | Same as regular 3.3 V<br>LVCMOS |

| 2.5 V LVCMOS                         | 2 mA           | 18                              | 16                              |

|                                      | 4 mA           | 18                              | 16                              |

|                                      | 6 mA           | 37                              | 32                              |

|                                      | 8 mA           | 37                              | 32                              |

| 1.8 V LVCMOS                         | 2 mA           | 11                              | 9                               |

|                                      | 4 mA           | 22                              | 17                              |

| 1.5 V LVCMOS                         | 2 mA           | 16                              | 13                              |

Notes:

- 1.  $T_{.1} = 100^{\circ}C$

- Applicable to 3.3 V LVCMOS Wide Range. I<sub>OSL</sub>/I<sub>OSH</sub> dependent on the I/O buffer drive strength selected for wide range applications. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

The length of time an I/O can withstand IOSH/IOSL events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than six months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

#### Table 2-35 • Duration of Short Circuit Event Before Failure

| Temperature      | Time before Failure |  |  |  |  |

|------------------|---------------------|--|--|--|--|

| -40°C > 20 years |                     |  |  |  |  |

| 0°C > 20 years   |                     |  |  |  |  |

| 25°C             | > 20 years          |  |  |  |  |

| 70°C             | 5 years             |  |  |  |  |

| 85°C             | 2 years             |  |  |  |  |

| 100°C 0.5 years  |                     |  |  |  |  |

#### Table 2-36 • I/O Input Rise Time, Fall Time, and Related I/O Reliability

| Input Buffer                  | Input Rise/Fall Time (min) | Input Rise/Fall Time (max) | Reliability      |

|-------------------------------|----------------------------|----------------------------|------------------|

| LVTTL/LVCMOS                  | No requirement             | 10 ns *                    | 20 years (110°C) |

| LVDS/B-LVDS/<br>M-LVDS/LVPECL | No requirement             | 10 ns *                    | 10 years (100°C) |

Note: \*The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

# Single-Ended I/O Characteristics

## 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer.

#### Table 2-37 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v        | IL       | v        | н        | VOL      | VОН      | IOL | юн | IOSL                   | IOSH                   | IIL¹            | IIH <sup>2</sup> |

|-------------------------------|----------|----------|----------|----------|----------|----------|-----|----|------------------------|------------------------|-----------------|------------------|

| Drive Strength                | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 2   | 2  | 27                     | 25                     | 10              | 10               |

| 4 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 4   | 4  | 27                     | 25                     | 10              | 10               |

| 6 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 6   | 6  | 54                     | 51                     | 10              | 10               |

| 8 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 8   | 8  | 54                     | 51                     | 10              | 10               |

| 12 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 12  | 12 | 109                    | 103                    | 10              | 10               |

| 16 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 16  | 16 | 127                    | 132                    | 10              | 10               |

| 24 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 24  | 24 | 181                    | 268                    | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

# Table 2-38 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | V        | ΊL       | V        | ΊH       | VOL      | VOH      | IOL | ЮН | IOSL                   | IOSH                   | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|----------|----------|----------|----------|----------|----------|-----|----|------------------------|------------------------|------------------|------------------|

| Drive Strength                | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 2   | 2  | 27                     | 25                     | 10               | 10               |

| 4 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 4   | 4  | 27                     | 25                     | 10               | 10               |

| 6 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 6   | 6  | 54                     | 51                     | 10               | 10               |

| 8 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 8   | 8  | 54                     | 51                     | 10               | 10               |

| 12 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 12  | 12 | 109                    | 103                    | 10               | 10               |

| 16 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 16  | 16 | 109                    | 103                    | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

### **Timing Characteristics**

#### Table 2-70 • 1.8 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive    | Speed |                   |                 |                  |                 |                   |                 |                 |                 |                 |                  |                  |       |

|----------|-------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Strength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 2 mA     | Std.  | 0.66              | 11.86           | 0.04             | 1.22            | 0.43              | 9.14            | 11.86           | 2.77            | 1.66            | 11.37            | 14.10            | ns    |

|          | -1    | 0.56              | 10.09           | 0.04             | 1.04            | 0.36              | 7.77            | 10.09           | 2.36            | 1.41            | 9.67             | 11.99            | ns    |

|          | -2    | 0.49              | 8.86            | 0.03             | 0.91            | 0.32              | 6.82            | 8.86            | 2.07            | 1.24            | 8.49             | 10.53            | ns    |

| 4 mA     | Std.  | 0.66              | 6.91            | 0.04             | 1.22            | 0.43              | 5.86            | 6.91            | 3.22            | 2.84            | 8.10             | 9.15             | ns    |

|          | -1    | 0.56              | 5.88            | 0.04             | 1.04            | 0.36              | 4.99            | 5.88            | 2.74            | 2.41            | 6.89             | 7.78             | ns    |

|          | -2    | 0.49              | 5.16            | 0.03             | 0.91            | 0.32              | 4.38            | 5.16            | 2.41            | 2.12            | 6.05             | 6.83             | ns    |

| 6 mA     | Std.  | 0.66              | 4.45            | 0.04             | 1.22            | 0.43              | 4.18            | 4.45            | 3.53            | 3.38            | 6.42             | 6.68             | ns    |

|          | -1    | 0.56              | 3.78            | 0.04             | 1.04            | 0.36              | 3.56            | 3.78            | 3.00            | 2.88            | 5.46             | 5.69             | ns    |

|          | -2    | 0.49              | 3.32            | 0.03             | 0.91            | 0.32              | 3.12            | 3.32            | 2.64            | 2.53            | 4.79             | 4.99             | ns    |

| 8 mA     | Std.  | 0.66              | 3.92            | 0.04             | 1.22            | 0.43              | 3.93            | 3.92            | 3.60            | 3.52            | 6.16             | 6.16             | ns    |

|          | -1    | 0.56              | 3.34            | 0.04             | 1.04            | 0.36              | 3.34            | 3.34            | 3.06            | 3.00            | 5.24             | 5.24             | ns    |

|          | -2    | 0.49              | 2.93            | 0.03             | 0.91            | 0.32              | 2.93            | 2.93            | 2.69            | 2.63            | 4.60             | 4.60             | ns    |

| 12 mA    | Std.  | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|          | -1    | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|          | -2    | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

| 16 mA    | Std.  | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|          | -1    | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|          | -2    | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

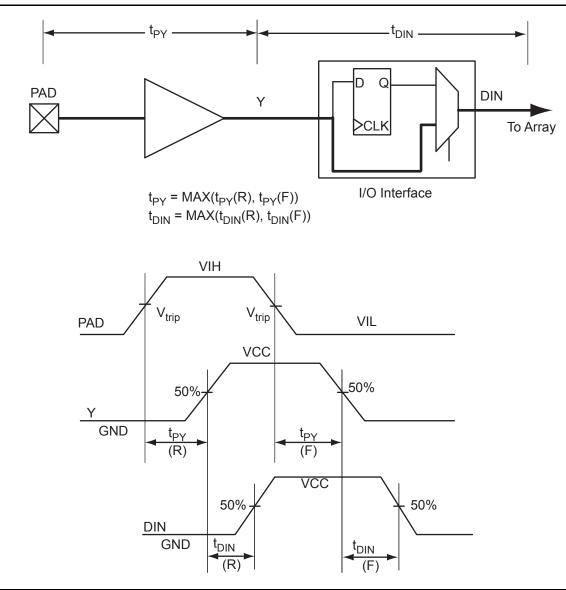

# **Output DDR Module**

### Figure 2-22 • Output DDR Timing Model

### Table 2-103 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (from, to) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | А, В                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | А, В                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

### Table 2-109 • A3P060 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2                |                   | -1                | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.71              | 0.93              | 0.81              | 1.05              | 0.95              | 1.24              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.70              | 0.96              | 0.80              | 1.09              | 0.94              | 1.28              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Microse

Power Matters.

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-110 • A3P125 Global Resource

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

```

|                      |                                           | -                 | -2                |                   | -1                |                   | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.77              | 0.99              | 0.87              | 1.12              | 1.03              | 1.32              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.76              | 1.02              | 0.87              | 1.16              | 1.02              | 1.37              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

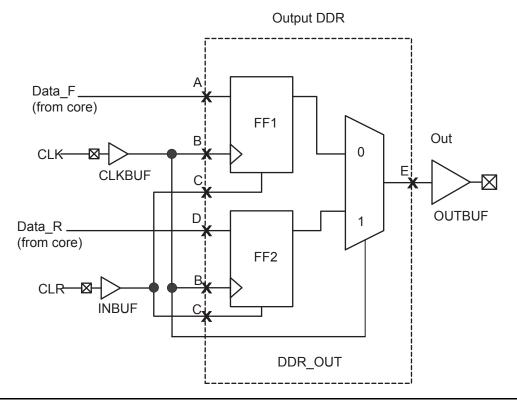

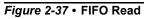

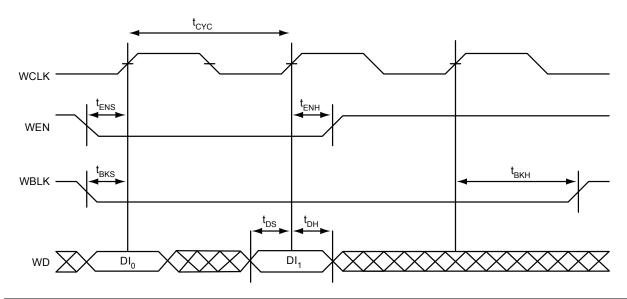

## Timing Waveforms

# Table 2-119 • FIFO (for A3P250 only, aspect-ratio-dependent)Worst Commercial-Case Conditions: TJ = 70°C, VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.26 | 3.71 | 4.36 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | MHz   |

|            | QN68            |

|------------|-----------------|

| Pin Number | A3P030 Function |

| 1          | IO82RSB1        |

| 2          | IO80RSB1        |

| 3          | IO78RSB1        |

| 4          | IO76RSB1        |

| 5          | GEC0/IO73RSB1   |

| 6          | GEA0/IO72RSB1   |

| 7          | GEB0/IO71RSB1   |

| 8          | VCC             |

| 9          | GND             |

| 10         | VCCIB1          |

| 11         | IO68RSB1        |

| 12         | IO67RSB1        |

| 13         | IO66RSB1        |

| 14         | IO65RSB1        |

| 15         | IO64RSB1        |

| 16         | IO63RSB1        |

| 17         | IO62RSB1        |

| 18         | IO60RSB1        |

| 19         | IO58RSB1        |

| 20         | IO56RSB1        |

| 21         | IO54RSB1        |

| 22         | IO52RSB1        |

| 23         | IO51RSB1        |

| 24         | VCC             |

| 25         | GND             |

| 26         | VCCIB1          |

| 27         | IO50RSB1        |

| 28         | IO48RSB1        |

| 29         | IO46RSB1        |

| 30         | IO44RSB1        |

| 31         | IO42RSB1        |

| 32         | ТСК             |

| 33         | TDI             |

| 34         | TMS             |

| 35         | VPUMP           |

| 36         | TDO             |

| QN68       |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | A3P030 Function |  |  |

| 37         | TRST            |  |  |

| 38         | VJTAG           |  |  |

| 39         | IO40RSB0        |  |  |

| 40         | IO37RSB0        |  |  |

| 41         | GDB0/IO34RSE    |  |  |

| 42         | GDA0/IO33RSE    |  |  |

| 43         | GDC0/IO32RSE    |  |  |

| 44         | VCCIB0          |  |  |

| 45         | GND             |  |  |

| 46         | VCC             |  |  |

| 47         | IO31RSB0        |  |  |

| 48         | IO29RSB0        |  |  |

| 49         | IO28RSB0        |  |  |

| 50         | IO27RSB0        |  |  |

| 51         | IO25RSB0        |  |  |

| 52         | IO24RSB0        |  |  |

| 53         | IO22RSB0        |  |  |

| 54         | IO21RSB0        |  |  |

| 55         | IO19RSB0        |  |  |

| 56         | IO17RSB0        |  |  |

| 57         | IO15RSB0        |  |  |

| 58         | IO14RSB0        |  |  |

| 59         | VCCIB0          |  |  |

| 60         | GND             |  |  |

| 61         | VCC             |  |  |

| 62         | IO12RSB0        |  |  |

| 63         | IO10RSB0        |  |  |

| 64         | IO08RSB0        |  |  |

| 65         | IO06RSB0        |  |  |

| 66         | IO04RSB0        |  |  |

| 67         | IO02RSB0        |  |  |

| 68         | IO00RSB0        |  |  |

| QN132      |                 |  |  |  |

|------------|-----------------|--|--|--|

| Pin Number | A3P250 Function |  |  |  |

| C17        | IO74RSB2        |  |  |  |

| C18        | VCCIB2          |  |  |  |

| C19        | ТСК             |  |  |  |

| C20        | VMV2            |  |  |  |

| C21        | VPUMP           |  |  |  |

| C22        | VJTAG           |  |  |  |

| C23        | VCCIB1          |  |  |  |

| C24        | IO53NSB1        |  |  |  |

| C25        | IO51NPB1        |  |  |  |

| C26        | GCA1/IO50PPB1   |  |  |  |

| C27        | GCC0/IO48NDB1   |  |  |  |

| C28        | VCCIB1          |  |  |  |

| C29        | IO42NDB1        |  |  |  |

| C30        | GNDQ            |  |  |  |

| C31        | GBA1/IO40RSB0   |  |  |  |

| C32        | GBB0/IO37RSB0   |  |  |  |

| C33        | VCC             |  |  |  |

| C34        | IO24RSB0        |  |  |  |

| C35        | IO19RSB0        |  |  |  |

| C36        | IO16RSB0        |  |  |  |

| C37        | IO10RSB0        |  |  |  |

| C38        | VCCIB0          |  |  |  |

| C39        | GAB1/IO03RSB0   |  |  |  |

| C40        | VMV0            |  |  |  |

| D1         | GND             |  |  |  |

| D2         | GND             |  |  |  |

| D3         | GND             |  |  |  |

| D4         | GND             |  |  |  |

| VQ100      |                 | VQ100      |                 | VQ100      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P060 Function | Pin Number | A3P060 Function | Pin Number | A3P060 Function |  |

| 1          | GND             | 37         | VCC             | 73         | GBA2/IO25RSB0   |  |

| 2          | GAA2/IO51RSB1   | 38         | GND             | 74         | VMV0            |  |

| 3          | IO52RSB1        | 39         | VCCIB1          | 75         | GNDQ            |  |

| 4          | GAB2/IO53RSB1   | 40         | IO60RSB1        | 76         | GBA1/IO24RSB0   |  |

| 5          | IO95RSB1        | 41         | IO59RSB1        | 77         | GBA0/IO23RSB0   |  |

| 6          | GAC2/IO94RSB1   | 42         | IO58RSB1        | 78         | GBB1/IO22RSB0   |  |

| 7          | IO93RSB1        | 43         | IO57RSB1        | 79         | GBB0/IO21RSB0   |  |

| 8          | IO92RSB1        | 44         | GDC2/IO56RSB1   | 80         | GBC1/IO20RSB0   |  |

| 9          | GND             | 45         | GDB2/IO55RSB1   | 81         | GBC0/IO19RSB0   |  |

| 10         | GFB1/IO87RSB1   | 46         | GDA2/IO54RSB1   | 82         | IO18RSB0        |  |

| 11         | GFB0/IO86RSB1   | 47         | ТСК             | 83         | IO17RSB0        |  |

| 12         | VCOMPLF         | 48         | TDI             | 84         | IO15RSB0        |  |

| 13         | GFA0/IO85RSB1   | 49         | TMS             | 85         | IO13RSB0        |  |

| 14         | VCCPLF          | 50         | VMV1            | 86         | IO11RSB0        |  |

| 15         | GFA1/IO84RSB1   | 51         | GND             | 87         | VCCIB0          |  |

| 16         | GFA2/IO83RSB1   | 52         | VPUMP           | 88         | GND             |  |

| 17         | VCC             | 53         | NC              | 89         | VCC             |  |

| 18         | VCCIB1          | 54         | TDO             | 90         | IO10RSB0        |  |

| 19         | GEC1/IO77RSB1   | 55         | TRST            | 91         | IO09RSB0        |  |

| 20         | GEB1/IO75RSB1   | 56         | VJTAG           | 92         | IO08RSB0        |  |

| 21         | GEB0/IO74RSB1   | 57         | GDA1/IO49RSB0   | 93         | GAC1/IO07RSB0   |  |

| 22         | GEA1/IO73RSB1   | 58         | GDC0/IO46RSB0   | 94         | GAC0/IO06RSB0   |  |

| 23         | GEA0/IO72RSB1   | 59         | GDC1/IO45RSB0   | 95         | GAB1/IO05RSB0   |  |

| 24         | VMV1            | 60         | GCC2/IO43RSB0   | 96         | GAB0/IO04RSB0   |  |

| 25         | GNDQ            | 61         | GCB2/IO42RSB0   | 97         | GAA1/IO03RSB0   |  |

| 26         | GEA2/IO71RSB1   | 62         | GCA0/IO40RSB0   | 98         | GAA0/IO02RSB0   |  |

| 27         | GEB2/IO70RSB1   | 63         | GCA1/IO39RSB0   | 99         | IO01RSB0        |  |

| 28         | GEC2/IO69RSB1   | 64         | GCC0/IO36RSB0   | 100        | IO00RSB0        |  |

| 29         | IO68RSB1        | 65         | GCC1/IO35RSB0   |            | -               |  |

| 30         | IO67RSB1        | 66         | VCCIB0          |            |                 |  |

| 31         | IO66RSB1        | 67         | GND             |            |                 |  |

| 32         | IO65RSB1        | 68         | VCC             |            |                 |  |

| 33         | IO64RSB1        | 69         | IO31RSB0        |            |                 |  |

| 34         | IO63RSB1        | 70         | GBC2/IO29RSB0   |            |                 |  |

| 35         | IO62RSB1        | 71         | GBB2/IO27RSB0   |            |                 |  |

| 36         | IO61RSB1        | 72         | IO26RSB0        |            |                 |  |

| TQ144      |                 | Т          | Q144            | Т          | Q144            |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P060 Function | Pin Number | A3P060 Function | Pin Number | A3P060 Function |

| 1          | GAA2/IO51RSB1   | 37         | NC              | 73         | VPUMP           |

| 2          | IO52RSB1        | 38         | GEA2/IO71RSB1   | 74         | NC              |

| 3          | GAB2/IO53RSB1   | 39         | GEB2/IO70RSB1   | 75         | TDO             |

| 4          | IO95RSB1        | 40         | GEC2/IO69RSB1   | 76         | TRST            |

| 5          | GAC2/IO94RSB1   | 41         | IO68RSB1        | 77         | VJTAG           |

| 6          | IO93RSB1        | 42         | IO67RSB1        | 78         | GDA0/IO50RSB0   |

| 7          | IO92RSB1        | 43         | IO66RSB1        | 79         | GDB0/IO48RSB0   |

| 8          | IO91RSB1        | 44         | IO65RSB1        | 80         | GDB1/IO47RSB0   |

| 9          | VCC             | 45         | VCC             | 81         | VCCIB0          |

| 10         | GND             | 46         | GND             | 82         | GND             |

| 11         | VCCIB1          | 47         | VCCIB1          | 83         | IO44RSB0        |

| 12         | IO90RSB1        | 48         | NC              | 84         | GCC2/IO43RSB0   |

| 13         | GFC1/IO89RSB1   | 49         | IO64RSB1        | 85         | GCB2/IO42RSB0   |

| 14         | GFC0/IO88RSB1   | 50         | NC              | 86         | GCA2/IO41RSB0   |

| 15         | GFB1/IO87RSB1   | 51         | IO63RSB1        | 87         | GCA0/IO40RSB0   |

| 16         | GFB0/IO86RSB1   | 52         | NC              | 88         | GCA1/IO39RSB0   |

| 17         | VCOMPLF         | 53         | IO62RSB1        | 89         | GCB0/IO38RSB0   |

| 18         | GFA0/IO85RSB1   | 54         | NC              | 90         | GCB1/IO37RSB0   |

| 19         | VCCPLF          | 55         | IO61RSB1        | 91         | GCC0/IO36RSB0   |

| 20         | GFA1/IO84RSB1   | 56         | NC              | 92         | GCC1/IO35RSB0   |

| 21         | GFA2/IO83RSB1   | 57         | NC              | 93         | IO34RSB0        |

| 22         | GFB2/IO82RSB1   | 58         | IO60RSB1        | 94         | IO33RSB0        |

| 23         | GFC2/IO81RSB1   | 59         | IO59RSB1        | 95         | NC              |

| 24         | IO80RSB1        | 60         | IO58RSB1        | 96         | NC              |

| 25         | IO79RSB1        | 61         | IO57RSB1        | 97         | NC              |

| 26         | IO78RSB1        | 62         | NC              | 98         | VCCIB0          |

| 27         | GND             | 63         | GND             | 99         | GND             |

| 28         | VCCIB1          | 64         | NC              | 100        | VCC             |

| 29         | GEC1/IO77RSB1   | 65         | GDC2/IO56RSB1   | 101        | IO30RSB0        |

| 30         | GEC0/IO76RSB1   | 66         | GDB2/IO55RSB1   | 102        | GBC2/IO29RSB0   |

| 31         | GEB1/IO75RSB1   | 67         | GDA2/IO54RSB1   | 103        | IO28RSB0        |

| 32         | GEB0/IO74RSB1   | 68         | GNDQ            | 104        | GBB2/IO27RSB0   |

| 33         | GEA1/IO73RSB1   | 69         | ТСК             | 105        | IO26RSB0        |

| 34         | GEA0/IO72RSB1   | 70         | TDI             | 106        | GBA2/IO25RSB0   |

| 35         | VMV1            | 71         | TMS             | 107        | VMV0            |

| 36         | GNDQ            | 72         | VMV1            | 108        | GNDQ            |

| PQ208      |                  |            | PQ208            | PQ208      |                  |  |

|------------|------------------|------------|------------------|------------|------------------|--|

| Pin Number | A3P1000 Function | Pin Number | A3P1000 Function | Pin Number | A3P1000 Function |  |

| 1          | GND              | 37         | IO199PDB3        | 73         | IO162RSB2        |  |

| 2          | GAA2/IO225PDB3   | 38         | IO199NDB3        | 74         | IO160RSB2        |  |

| 3          | IO225NDB3        | 39         | IO197PSB3        | 75         | IO158RSB2        |  |

| 4          | GAB2/IO224PDB3   | 40         | VCCIB3           | 76         | IO156RSB2        |  |

| 5          | IO224NDB3        | 41         | GND              | 77         | IO154RSB2        |  |

| 6          | GAC2/IO223PDB3   | 42         | IO191PDB3        | 78         | IO152RSB2        |  |

| 7          | IO223NDB3        | 43         | IO191NDB3        | 79         | IO150RSB2        |  |

| 8          | IO222PDB3        | 44         | GEC1/IO190PDB3   | 80         | IO148RSB2        |  |

| 9          | IO222NDB3        | 45         | GEC0/IO190NDB3   | 81         | GND              |  |

| 10         | IO220PDB3        | 46         | GEB1/IO189PDB3   | 82         | IO143RSB2        |  |

| 11         | IO220NDB3        | 47         | GEB0/IO189NDB3   | 83         | IO141RSB2        |  |

| 12         | IO218PDB3        | 48         | GEA1/IO188PDB3   | 84         | IO139RSB2        |  |

| 13         | IO218NDB3        | 49         | GEA0/IO188NDB3   | 85         | IO137RSB2        |  |

| 14         | IO216PDB3        | 50         | VMV3             | 86         | IO135RSB2        |  |

| 15         | IO216NDB3        | 51         | GNDQ             | 87         | IO133RSB2        |  |

| 16         | VCC              | 52         | GND              | 88         | VCC              |  |

| 17         | GND              | 53         | VMV2             | 89         | VCCIB2           |  |

| 18         | VCCIB3           | 54         | GEA2/IO187RSB2   | 90         | IO128RSB2        |  |

| 19         | IO212PDB3        | 55         | GEB2/IO186RSB2   | 91         | IO126RSB2        |  |

| 20         | IO212NDB3        | 56         | GEC2/IO185RSB2   | 92         | IO124RSB2        |  |

| 21         | GFC1/IO209PDB3   | 57         | IO184RSB2        | 93         | IO122RSB2        |  |

| 22         | GFC0/IO209NDB3   | 58         | IO183RSB2        | 94         | IO120RSB2        |  |

| 23         | GFB1/IO208PDB3   | 59         | IO182RSB2        | 95         | IO118RSB2        |  |

| 24         | GFB0/IO208NDB3   | 60         | IO181RSB2        | 96         | GDC2/IO116RSB2   |  |

| 25         | VCOMPLF          | 61         | IO180RSB2        | 97         | GND              |  |

| 26         | GFA0/IO207NPB3   | 62         | VCCIB2           | 98         | GDB2/IO115RSB2   |  |

| 27         | VCCPLF           | 63         | IO178RSB2        | 99         | GDA2/IO114RSB2   |  |

| 28         | GFA1/IO207PPB3   | 64         | IO176RSB2        | 100        | GNDQ             |  |

| 29         | GND              | 65         | GND              | 101        | ТСК              |  |

| 30         | GFA2/IO206PDB3   | 66         | IO174RSB2        | 102        | TDI              |  |

| 31         | IO206NDB3        | 67         | IO172RSB2        | 103        | TMS              |  |

| 32         | GFB2/IO205PDB3   | 68         | IO170RSB2        | 104        | VMV2             |  |

| 33         | IO205NDB3        | 69         | IO168RSB2        | 105        | GND              |  |

| 34         | GFC2/IO204PDB3   | 70         | IO166RSB2        | 106        | VPUMP            |  |

| 35         | IO204NDB3        | 71         | VCC              | 107        | GNDQ             |  |

| 36         | VCC              | 72         | VCCIB2           | 108        | TDO              |  |

# **Microsemi**

|            | FG484           |

|------------|-----------------|

| Pin Number | A3P400 Function |

| Y15        | VCC             |

| Y16        | NC              |

| Y17        | NC              |

| Y18        | GND             |

| Y19        | NC              |

| Y20        | NC              |

| Y21        | NC              |

| Y22        | VCCIB1          |

| AA1        | GND             |

| AA2        | VCCIB3          |

| AA3        | NC              |

| AA4        | NC              |

| AA5        | NC              |

| AA6        | NC              |

| AA7        | NC              |

| AA8        | NC              |

| AA9        | NC              |

| AA10       | NC              |

| AA11       | NC              |

| AA12       | NC              |

| AA13       | NC              |

| AA14       | NC              |

| AA15       | NC              |

| AA16       | NC              |

| AA17       | NC              |

| AA18       | NC              |

| AA19       | NC              |

| AA20       | NC              |

| AA21       | VCCIB1          |

| AA22       | GND             |

| AB1        | GND             |

| AB2        | GND             |

| AB3        | VCCIB2          |

| AB4        | NC              |

| AB5        | NC              |

| AB6        | IO121RSB2       |

| FG484      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P400 Function |  |  |  |  |

| AB7        | IO119RSB2       |  |  |  |  |

| AB8        | IO114RSB2       |  |  |  |  |

| AB9        | IO109RSB2       |  |  |  |  |

| AB10       | NC              |  |  |  |  |

| AB11       | NC              |  |  |  |  |

| AB12       | IO104RSB2       |  |  |  |  |

| AB13       | IO103RSB2       |  |  |  |  |

| AB14       | NC              |  |  |  |  |

| AB15       | NC              |  |  |  |  |

| AB16       | IO91RSB2        |  |  |  |  |

| AB17       | IO90RSB2        |  |  |  |  |

| AB18       | NC              |  |  |  |  |

| AB19       | NC              |  |  |  |  |

| AB20       | VCCIB2          |  |  |  |  |

| AB21       | GND             |  |  |  |  |

| AB22       | GND             |  |  |  |  |

# 🌜 Microsemi.

|            | FG484            |            | FG484            |            | FG484            |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | A3P1000 Function | Pin Number | A3P1000 Function | Pin Number | A3P1000 Function |

| A1         | GND              | B15        | IO63RSB0         | D7         | GAB0/IO02RSB0    |

| A2         | GND              | B16        | IO66RSB0         | D8         | IO16RSB0         |

| A3         | VCCIB0           | B17        | IO68RSB0         | D9         | IO22RSB0         |

| A4         | IO07RSB0         | B18        | IO70RSB0         | D10        | IO28RSB0         |

| A5         | IO09RSB0         | B19        | NC               | D11        | IO35RSB0         |

| A6         | IO13RSB0         | B20        | NC               | D12        | IO45RSB0         |

| A7         | IO18RSB0         | B21        | VCCIB1           | D13        | IO50RSB0         |

| A8         | IO20RSB0         | B22        | GND              | D14        | IO55RSB0         |

| A9         | IO26RSB0         | C1         | VCCIB3           | D15        | IO61RSB0         |

| A10        | IO32RSB0         | C2         | IO220PDB3        | D16        | GBB1/IO75RSB0    |

| A11        | IO40RSB0         | C3         | NC               | D17        | GBA0/IO76RSB0    |

| A12        | IO41RSB0         | C4         | NC               | D18        | GBA1/IO77RSB0    |

| A13        | IO53RSB0         | C5         | GND              | D19        | GND              |

| A14        | IO59RSB0         | C6         | IO10RSB0         | D20        | NC               |

| A15        | IO64RSB0         | C7         | IO14RSB0         | D21        | NC               |

| A16        | IO65RSB0         | C8         | VCC              | D22        | NC               |

| A17        | IO67RSB0         | C9         | VCC              | E1         | IO219NDB3        |

| A18        | IO69RSB0         | C10        | IO30RSB0         | E2         | NC               |

| A19        | NC               | C11        | IO37RSB0         | E3         | GND              |

| A20        | VCCIB0           | C12        | IO43RSB0         | E4         | GAB2/IO224PDB3   |

| A21        | GND              | C13        | NC               | E5         | GAA2/IO225PDB3   |

| A22        | GND              | C14        | VCC              | E6         | GNDQ             |

| B1         | GND              | C15        | VCC              | E7         | GAB1/IO03RSB0    |

| B2         | VCCIB3           | C16        | NC               | E8         | IO17RSB0         |

| B3         | NC               | C17        | NC               | E9         | IO21RSB0         |

| B4         | IO06RSB0         | C18        | GND              | E10        | IO27RSB0         |

| B5         | IO08RSB0         | C19        | NC               | E11        | IO34RSB0         |

| B6         | IO12RSB0         | C20        | NC               | E12        | IO44RSB0         |

| B7         | IO15RSB0         | C21        | NC               | E13        | IO51RSB0         |

| B8         | IO19RSB0         | C22        | VCCIB1           | E14        | IO57RSB0         |

| B9         | IO24RSB0         | D1         | IO219PDB3        | E15        | GBC1/IO73RSB0    |

| B10        | IO31RSB0         | D2         | IO220NDB3        | E16        | GBB0/IO74RSB0    |

| B11        | IO39RSB0         | D3         | NC               | E17        | IO71RSB0         |

| B12        | IO48RSB0         | D4         | GND              | E18        | GBA2/IO78PDB1    |

| B13        | IO54RSB0         | D5         | GAA0/IO00RSB0    | E19        | IO81PDB1         |

| B14        | IO58RSB0         | D6         | GAA1/IO01RSB0    | E20        | GND              |

Datasheet Information

| Revision                                                          | Changes                                                                                                                                                                                                                                                                                                  | Page       |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 5 (Aug 2008)<br>DC and Switching<br>Characteristics v1.3 | TJ, Maximum Junction Temperature, was changed to 100° from 110° in the "Thermal Characteristics" section and EQ 1. The calculated result of Maximum Power Allowed has thus changed to 1.463 W from 1.951 W.                                                                                              | 2-6        |

|                                                                   | Values for the A3P015 device were added to Table 2-7 • Quiescent Supply Current Characteristics.                                                                                                                                                                                                         | 2-7        |

|                                                                   | Values for the A3P015 device were added to Table 2-14 • Different Components Contributing to Dynamic Power Consumption in ProASIC3 Devices. $P_{AC14}$ was removed. Table 2-15 • Different Components Contributing to the Static Power Consumption in ProASIC3 Devices is new.                           | 2-11, 2-12 |

|                                                                   | The "PLL Contribution—PPLL" section was updated to change the P <sub>PLL</sub> formula from $P_{AC13} + P_{AC14} * F_{CLKOUT}$ to $P_{DC4} + P_{AC13} * F_{CLKOUT}$ .                                                                                                                                    | 2-14       |

|                                                                   | Both fall and rise values were included for $t_{\mbox{DDRISUD}}$ and $t_{\mbox{DDRIHD}}$ in Table 2-102 $\bullet$ Input DDR Propagation Delays.                                                                                                                                                          | 2-78       |

|                                                                   | Table 2-107 • A3P015 Global Resource is new.                                                                                                                                                                                                                                                             | 2-86       |

|                                                                   | The typical value for Delay Increments in Programmable Delay Blocks was changed from 160 to 200 in Table 2-115 • ProASIC3 CCC/PLL Specification.                                                                                                                                                         | 2-90       |

| Revision 4 (Jun 2008)<br>DC and Switching<br>Characteristics v1.2 | Table note references were added to Table 2-2 • Recommended Operating Conditions 1, and the order of the table notes was changed.                                                                                                                                                                        | 2-2        |

|                                                                   | The title for Table 2-4 • Overshoot and Undershoot Limits 1 was modified to remove "as measured on quiet I/Os." Table note 1 was revised to remove "estimated SSO density over cycles." Table note 2 was revised to remove "refers only to overshoot/undershoot limits for simultaneous switching I/Os." | 2-3        |

|                                                                   | The "Power per I/O Pin" section was updated to include 3 additional tables pertaining to input buffer power and output buffer power.                                                                                                                                                                     | 2-7        |

|                                                                   | Table 2-29 • I/O Output Buffer Maximum Resistances 1 was revised to include values for 3.3 V PCI/PCI-X.                                                                                                                                                                                                  | 2-27       |

|                                                                   | Table 2-90 • LVDS Minimum and Maximum DC Input and Output Levels was updated.                                                                                                                                                                                                                            | 2-66       |

| <b>Revision 3 (Jun 2008)</b><br>Packaging v1.3                    | Pin numbers were added to the "QN68 – Bottom View" package diagram. Note 2 was added below the diagram.                                                                                                                                                                                                  | 4-3        |

|                                                                   | The "QN132 – Bottom View" package diagram was updated to include D1 to D4. In addition, note 1 was changed from top view to bottom view, and note 2 is new.                                                                                                                                              | 4-6        |

| Revision 2 (Feb 2008)<br>Product Brief v1.0                       | This document was divided into two sections and given a version number, starting at v1.0. The first section of the document includes features, benefits, ordering information, and temperature and speed grade offerings. The second section is a device family overview.                                | N/A        |

|                                                                   | This document was updated to include A3P015 device information. QN68 is a new package that was added because it is offered in the A3P015. The following sections were updated:                                                                                                                           | N/A        |

|                                                                   | "Features and Benefits"                                                                                                                                                                                                                                                                                  |            |

|                                                                   | "ProASIC3 Ordering Information"                                                                                                                                                                                                                                                                          |            |

|                                                                   | "Temperature Grade Offerings"                                                                                                                                                                                                                                                                            |            |

|                                                                   | "ProASIC3 Flash Family FPGAs"                                                                                                                                                                                                                                                                            |            |

|                                                                   | "A3P015 and A3P030" note                                                                                                                                                                                                                                                                                 |            |

|                                                                   | Introduction and Overview (NA)                                                                                                                                                                                                                                                                           |            |