Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E·XFI

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells |                                                                            |

| Total RAM Bits                 | 147456                                                                     |

| Number of I/O                  | 177                                                                        |

| Number of Gates                | 100000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 256-LBGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m7a3p1000-fgg256 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

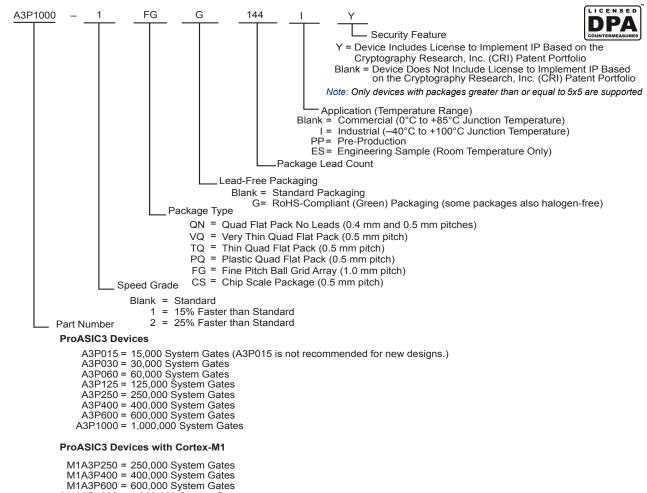

# **ProASIC3 Ordering Information**

## M1A3P1000 = 1,000,000 System Gates

## **ProASIC3** Device Status

| ProASIC3 Devices | Status                           | Cortex-M1 Devices | Status     |

|------------------|----------------------------------|-------------------|------------|

| A3P015           | Not recommended for new designs. |                   |            |

| A3P030           | Production                       |                   |            |

| A3P060           | Production                       |                   |            |

| A3P125           | Production                       |                   |            |

| A3P250           | Production                       | M1A3P250          | Production |

| A3P400           | Production                       | M1A3P400          | Production |

| A3P600           | Production                       | M1A3P600          | Production |

| A3P1000          | Production                       | M1A3P1000         | Production |

## Single-Ended I/O Characteristics

## 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer.

#### Table 2-37 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v        | IL       | v        | н        | VOL      | VОН      | IOL | юн | IOSL                   | IOSH                   | IIL¹            | IIH <sup>2</sup> |

|-------------------------------|----------|----------|----------|----------|----------|----------|-----|----|------------------------|------------------------|-----------------|------------------|

| Drive Strength                | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 2   | 2  | 27                     | 25                     | 10              | 10               |

| 4 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 4   | 4  | 27                     | 25                     | 10              | 10               |

| 6 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 6   | 6  | 54                     | 51                     | 10              | 10               |

| 8 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 8   | 8  | 54                     | 51                     | 10              | 10               |

| 12 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 12  | 12 | 109                    | 103                    | 10              | 10               |

| 16 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 16  | 16 | 127                    | 132                    | 10              | 10               |

| 24 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 24  | 24 | 181                    | 268                    | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

# Table 2-38 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | V        | ΊL       | V        | ΊH       | VOL      | VOH      | IOL | ЮН | IOSL                   | IOSH                   | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|----------|----------|----------|----------|----------|----------|-----|----|------------------------|------------------------|------------------|------------------|

| Drive Strength                | Min<br>V | Max<br>V | Min<br>V | Max<br>V | Max<br>V | Min<br>V | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 2   | 2  | 27                     | 25                     | 10               | 10               |

| 4 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 4   | 4  | 27                     | 25                     | 10               | 10               |

| 6 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 6   | 6  | 54                     | 51                     | 10               | 10               |

| 8 mA                          | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 8   | 8  | 54                     | 51                     | 10               | 10               |

| 12 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 12  | 12 | 109                    | 103                    | 10               | 10               |

| 16 mA                         | -0.3     | 0.8      | 2        | 3.6      | 0.4      | 2.4      | 16  | 16 | 109                    | 103                    | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

## 2.5 V LVCMOS

Low-Voltage CMOS for 2.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 2.5 V applications.

| 2.5 V LVCMOS   | V         | ΊL        | V         | ΊH        | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL1            | IIH <sup>2</sup> |

|----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|-----------------|------------------|

| Drive Strength | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 2   | 2   | 18                      | 16                      | 10              | 10               |

| 4 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 4   | 4   | 18                      | 16                      | 10              | 10               |

| 6 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 6   | 6   | 37                      | 32                      | 10              | 10               |

| 8 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 8   | 8   | 37                      | 32                      | 10              | 10               |

| 12 mA          | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 12  | 12  | 74                      | 65                      | 10              | 10               |

| 16 mA          | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 16  | 16  | 87                      | 83                      | 10              | 10               |

| 24 mA          | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 24  | 24  | 124                     | 169                     | 10              | 10               |

#### Table 2-56 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

# Table 2-57 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O Banks

| 2.5 V LVCMOS   | VIL       |           | VIH       |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 2   | 2  | 18                      | 16                      | 10               | 10               |

| 4 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10               | 10               |

| 6 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 6   | 6  | 37                      | 32                      | 10               | 10               |

| 8 mA           | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10               | 10               |

| 12 mA          | -0.3      | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 12  | 12 | 74                      | 65                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

## 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

| 1.8 V<br>LVCMOS   |          | VIL         | VIH         | VIH      |          | VOH         | IOL | юн | IOSL                   | IOSH                   | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|----------|-------------|-------------|----------|----------|-------------|-----|----|------------------------|------------------------|------------------|------------------|

| Drive<br>Strength | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V | Min<br>V    | mA  | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 2   | 2  | 11                     | 9                      | 10               | 10               |

| 4 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 4   | 4  | 22                     | 17                     | 10               | 10               |

| 6 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI - 0.45 | 6   | 6  | 44                     | 35                     | 10               | 10               |

| 8 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 8   | 8  | 51                     | 45                     | 10               | 10               |

| 12 mA             | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 12  | 12 | 74                     | 91                     | 10               | 10               |

| 16 mA             | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 1.9      | 0.45     | VCCI-0.45   | 16  | 16 | 74                     | 91                     | 10               | 10               |

#### Table 2-66 • Minimum and Maximum DC Input and Output Levels Applicable to Advanced I/O Banks

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

# Table 2-67 • Minimum and Maximum DC Input and Output Levels Applicable to Standard Plus I/O I/O Banks

| 1.8 V<br>LVCMOS   |          | VIL         | VIH         |          | VOL      | VOL VOH I   |    | ЮН | IOSL                   | IOSH                   | IIL¹            | IIH <sup>2</sup> |

|-------------------|----------|-------------|-------------|----------|----------|-------------|----|----|------------------------|------------------------|-----------------|------------------|

| Drive<br>Strength | Min<br>V | Max<br>V    | Min<br>V    | Max<br>V | Max<br>V | Min<br>V    | mA | mA | Max<br>mA <sup>3</sup> | Max<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI – 0.45 | 2  | 2  | 11                     | 9                      | 10              | 10               |

| 4 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI – 0.45 | 4  | 4  | 22                     | 17                     | 10              | 10               |

| 6 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI – 0.45 | 6  | 6  | 44                     | 35                     | 10              | 10               |

| 8 mA              | -0.3     | 0.35 * VCCI | 0.65 * VCCI | 3.6      | 0.45     | VCCI - 0.45 | 8  | 8  | 44                     | 35                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN <V CCI. Input current is larger when operating outside recommended ranges

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

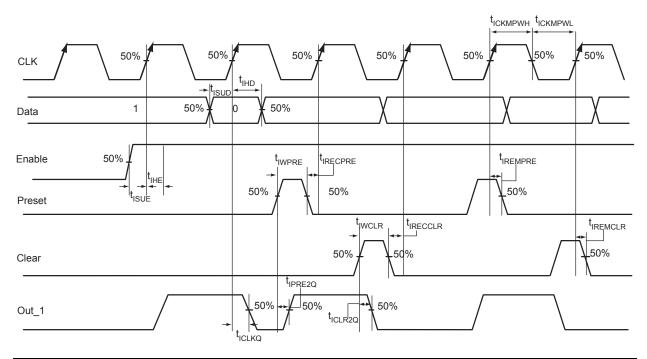

## Input Register

## Timing Characteristics

# Table 2-98 • Input Data Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.24 | 0.27 | 0.32 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.26 | 0.30 | 0.35 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.37 | 0.42 | 0.50 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.37 | 0.43 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

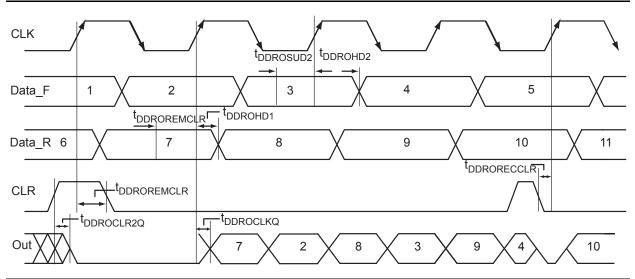

| Figure 2-23 • | Output D | DR Timing Diagram |

|---------------|----------|-------------------|

|---------------|----------|-------------------|

## **Timing Characteristics**

## Table 2-104 • Output DDR Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                           | -2   | -1   | Std. | Units |

|-------------------------|-------------------------------------------------------|------|------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.70 | 0.80 | 0.94 | ns    |

| t <sub>DDROSUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.38 | 0.43 | 0.51 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.38 | 0.43 | 0.51 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width High for the Output DDR     | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output DDR      | 0.32 | 0.37 | 0.43 | ns    |

| F <sub>DDOMAX</sub>     | Maximum Frequency for the Output DDR                  | 350  | 309  | 263  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# **VersaTile Characteristics**

## VersaTile Specifications as a Combinatorial Module

The ProASIC3 library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *Fusion, IGLOO®/e, and ProASIC3/E Macro Library Guide*.

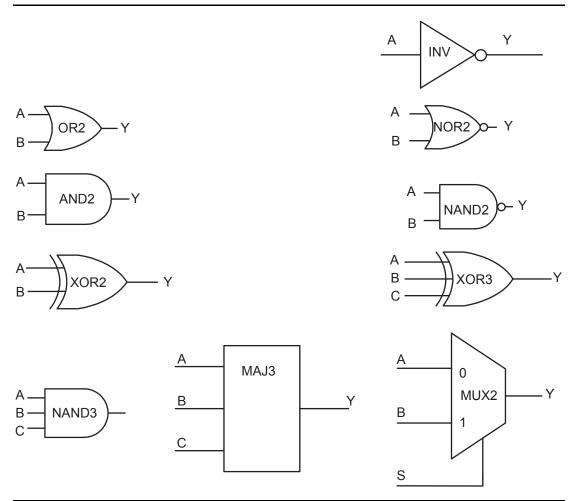

Figure 2-24 • Sample of Combinatorial Cells

# **Global Resource Characteristics**

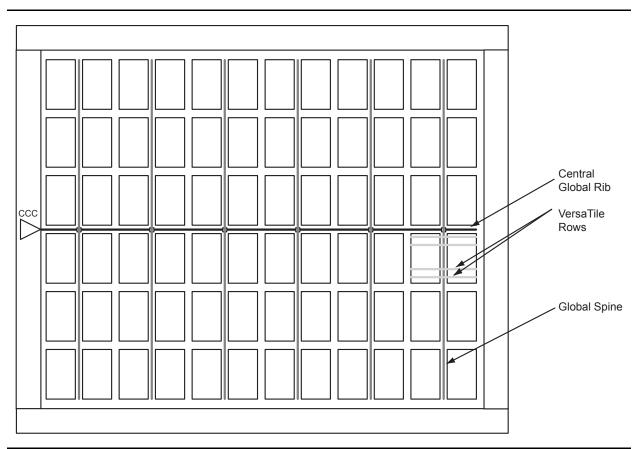

## A3P250 Clock Tree Topology

Clock delays are device-specific. Figure 2-28 is an example of a global tree used for clock routing. The global tree presented in Figure 2-28 is driven by a CCC located on the west side of the A3P250 device. It is used to drive all D-flip-flops in the device.

Figure 2-28 • Example of Global Tree Use in an A3P250 Device for Clock Routing

## **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-90. Table 2-108 to Table 2-114 on page 2-89 present minimum and maximum global clock delays within each device. Minimum and maximum delays are measured with minimum and maximum loading.

### Timing Characteristics

### Table 2-107 • A3P015 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -2                |                   | -                 | -1                | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.66              | 0.81              | 0.75              | 0.92              | 0.88              | 1.08              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.67              | 0.84              | 0.76              | 0.96              | 0.89              | 1.13              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.18              |                   | 0.21              |                   | 0.25              | ns    |

#### Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage-supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-108 • A3P030 Global Resource

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -                 | -2                |                   | -1                | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.67              | 0.81              | 0.76              | 0.92              | 0.89              | 1.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.68              | 0.85              | 0.77              | 0.97              | 0.91              | 1.14              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.18              |                   | 0.21              |                   | 0.24              | ns    |

#### Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-109 • A3P060 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | -    | -2                |                   | –1 S              |                   | td.               |       |

|----------------------|-------------------------------------------|------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               |      | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.71 | 0.93              | 0.81              | 1.05              | 0.95              | 1.24              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.70 | 0.96              | 0.80              | 1.09              | 0.94              | 1.28              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75 |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85 |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |      | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Microse

Power Matters.

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-110 • A3P125 Global Resource

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

```

|                      |                                           | -                 | -2                |                   | -1                | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.77              | 0.99              | 0.87              | 1.12              | 1.03              | 1.32              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.76              | 1.02              | 0.87              | 1.16              | 1.02              | 1.37              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 0.75              |                   | 0.85              |                   | 1.00              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 0.85              |                   | 0.96              |                   | 1.13              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.29              |                   | 0.34              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# **Clock Conditioning Circuits**

## **CCC Electrical Specifications**

### **Timing Characteristics**

### Table 2-115 • ProASIC3 CCC/PLL Specification

| Parameter                                                          | Minimum                     | Typical          | Maximum                      | Units |

|--------------------------------------------------------------------|-----------------------------|------------------|------------------------------|-------|

| Clock Conditioning Circuitry Input Frequency fIN_CCC               | 1.5                         |                  | 350                          | MHz   |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT CCC</sub> | 0.75                        |                  | 350                          | MHz   |

| Serial Clock (SCLK) for Dynamic PLL <sup>1</sup>                   |                             |                  | 125                          | MHz   |

| Delay Increments in Programmable Delay Blocks <sup>2, 3</sup>      |                             | 200 <sup>4</sup> |                              | ps    |

| Number of Programmable Values in Each Programmable<br>Delay Block  |                             |                  | 32                           |       |

| Input Period Jitter                                                |                             |                  | 1.5                          | ns    |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | N                           | lax Peak-to-F    | Peak Period Jitt             | er    |

|                                                                    | 1 Global<br>Network<br>Used |                  | 3 Global<br>Networks<br>Used |       |

| 0.75 MHz to 24 MHz                                                 | 0.50%                       |                  | 0.70%                        |       |

| 24 MHz to 100 MHz                                                  | 1.00%                       |                  | 1.20%                        |       |

| 100 MHz to 250 MHz                                                 | 1.75%                       |                  | 2.00%                        |       |

| 250 MHz to 350 MHz                                                 | 2.50%                       |                  | 5.60%                        |       |

| Acquisition Time                                                   |                             |                  |                              |       |

| (A3P250 and A3P1000 only) LockControl = 0                          |                             |                  | 300                          | μs    |

| LockControl = 1                                                    |                             |                  | 300                          | μs    |

| (all other dies) LockControl = 0                                   |                             |                  | 300                          | μs    |

| LockControl = 1                                                    |                             |                  | 6.0                          | ms    |

| Tracking Jitter <sup>5</sup>                                       |                             |                  |                              |       |

| (A3P250 and A3P1000 only) LockControl = 0                          |                             |                  | 1.6                          | ns    |

| LockControl = 1                                                    |                             |                  | 1.6                          | ns    |

| (all other dies) LockControl = 0                                   |                             |                  | 1.6                          | ns    |

| LockControl = 1                                                    |                             |                  | 0.8                          | ns    |

| Output Duty Cycle                                                  | 48.5                        |                  | 51.5                         | %     |

| Delay Range in Block: Programmable Delay 1 <sup>2, 3</sup>         | 0.6                         |                  | 5.56                         | ns    |

| Delay Range in Block: Programmable Delay 2 <sup>2, 3</sup>         | 0.225                       |                  | 5.56                         | ns    |

| Delay Range in Block: Fixed Delay <sup>2, 3</sup>                  |                             | 2.2              |                              | ns    |

Notes:

1. Maximum value obtained for a -2 speed-grade device in worst-case commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 for deratings.

3.  $T_J = 25^{\circ}C$ , VCC = 1.5 V

- 4. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help for more information.

- 5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

6. The A3P030 device does not contain a PLL.

AFULL

| QN132      |                 |            | QN132           | QN132      |                 |  |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|--|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |  |  |

| A1         | GAB2/IO117UPB3  | A37        | GBB1/IO38RSB0   | B25        | GND             |  |  |

| A2         | IO117VPB3       | A38        | GBC0/IO35RSB0   | B26        | IO54PDB1        |  |  |

| A3         | VCCIB3          | A39        | VCCIB0          | B27        | GCB2/IO52PDB1   |  |  |

| A4         | GFC1/IO110PDB3  | A40        | IO28RSB0        | B28        | GND             |  |  |

| A5         | GFB0/IO109NPB3  | A41        | IO22RSB0        | B29        | GCB0/IO49NDB1   |  |  |

| A6         | VCCPLF          | A42        | IO18RSB0        | B30        | GCC1/IO48PDB1   |  |  |

| A7         | GFA1/IO108PPB3  | A43        | IO14RSB0        | B31        | GND             |  |  |

| A8         | GFC2/IO105PPB3  | A44        | IO11RSB0        | B32        | GBB2/IO42PDB1   |  |  |

| A9         | IO103NDB3       | A45        | IO07RSB0        | B33        | VMV1            |  |  |

| A10        | VCC             | A46        | VCC             | B34        | GBA0/IO39RSB0   |  |  |

| A11        | GEA1/IO98PPB3   | A47        | GAC1/IO05RSB0   | B35        | GBC1/IO36RSB0   |  |  |

| A12        | GEA0/IO98NPB3   | A48        | GAB0/IO02RSB0   | B36        | GND             |  |  |

| A13        | GEC2/IO95RSB2   | B1         | IO118VDB3       | B37        | IO26RSB0        |  |  |

| A14        | IO91RSB2        | B2         | GAC2/IO116UDB3  | B38        | IO21RSB0        |  |  |

| A15        | VCC             | B3         | GND             | B39        | GND             |  |  |

| A16        | IO90RSB2        | B4         | GFC0/IO110NDB3  | B40        | IO13RSB0        |  |  |

| A17        | IO87RSB2        | B5         | VCOMPLF         | B41        | IO08RSB0        |  |  |

| A18        | IO85RSB2        | B6         | GND             | B42        | GND             |  |  |

| A19        | IO82RSB2        | B7         | GFB2/IO106PSB3  | B43        | GAC0/IO04RSB0   |  |  |

| A20        | IO76RSB2        | B8         | IO103PDB3       | B44        | GNDQ            |  |  |

| A21        | IO70RSB2        | B9         | GND             | C1         | GAA2/IO118UDB3  |  |  |

| A22        | VCC             | B10        | GEB0/IO99NDB3   | C2         | IO116VDB3       |  |  |

| A23        | GDB2/IO62RSB2   | B11        | VMV3            | C3         | VCC             |  |  |

| A24        | TDI             | B12        | GEB2/IO96RSB2   | C4         | GFB1/IO109PPB3  |  |  |

| A25        | TRST            | B13        | IO92RSB2        | C5         | GFA0/IO108NPB3  |  |  |

| A26        | GDC1/IO58UDB1   | B14        | GND             | C6         | GFA2/IO107PSB3  |  |  |

| A27        | VCC             | B15        | IO89RSB2        | C7         | IO105NPB3       |  |  |

| A28        | IO54NDB1        | B16        | IO86RSB2        | C8         | VCCIB3          |  |  |

| A29        | IO52NDB1        | B17        | GND             | C9         | GEB1/IO99PDB3   |  |  |

| A30        | GCA2/IO51PPB1   | B18        | IO78RSB2        | C10        | GNDQ            |  |  |

| A31        | GCA0/IO50NPB1   | B19        | IO72RSB2        | C11        | GEA2/IO97RSB2   |  |  |

| A32        | GCB1/IO49PDB1   | B20        | GND             | C12        | IO94RSB2        |  |  |

| A33        | IO47NSB1        | B21        | GNDQ            | C13        | VCCIB2          |  |  |

| A34        | VCC             | B22        | TMS             | C14        | IO88RSB2        |  |  |

| A35        | IO41NPB1        | B23        | TDO             | C15        | IO84RSB2        |  |  |

| A36        | GBA2/IO41PPB1   | B24        | GDC0/IO58VDB1   | C16        | IO80RSB2        |  |  |

| VQ100      |                 | VQ100      |                 | VQ100      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |  |

| 1          | GND             | 37         | VCC             | 73         | GBA2/IO41PDB1   |  |

| 2          | GAA2/IO118UDB3  | 38         | GND             | 74         | VMV1            |  |

| 3          | IO118VDB3       | 39         | VCCIB2          | 75         | GNDQ            |  |

| 4          | GAB2/IO117UDB3  | 40         | IO77RSB2        | 76         | GBA1/IO40RSB0   |  |

| 5          | IO117VDB3       | 41         | IO74RSB2        | 77         | GBA0/IO39RSB0   |  |

| 6          | GAC2/IO116UDB3  | 42         | IO71RSB2        | 78         | GBB1/IO38RSB0   |  |

| 7          | IO116VDB3       | 43         | GDC2/IO63RSB2   | 79         | GBB0/IO37RSB0   |  |

| 8          | IO112PSB3       | 44         | GDB2/IO62RSB2   | 80         | GBC1/IO36RSB0   |  |

| 9          | GND             | 45         | GDA2/IO61RSB2   | 81         | GBC0/IO35RSB0   |  |

| 10         | GFB1/IO109PDB3  | 46         | GNDQ            | 82         | IO29RSB0        |  |

| 11         | GFB0/IO109NDB3  | 47         | ТСК             | 83         | IO27RSB0        |  |

| 12         | VCOMPLF         | 48         | TDI             | 84         | IO25RSB0        |  |

| 13         | GFA0/IO108NPB3  | 49         | TMS             | 85         | IO23RSB0        |  |

| 14         | VCCPLF          | 50         | VMV2            | 86         | IO21RSB0        |  |

| 15         | GFA1/IO108PPB3  | 51         | GND             | 87         | VCCIB0          |  |

| 16         | GFA2/IO107PSB3  | 52         | VPUMP           | 88         | GND             |  |

| 17         | VCC             | 53         | NC              | 89         | VCC             |  |

| 18         | VCCIB3          | 54         | TDO             | 90         | IO15RSB0        |  |

| 19         | GFC2/IO105PSB3  | 55         | TRST            | 91         | IO13RSB0        |  |

| 20         | GEC1/IO100PDB3  | 56         | VJTAG           | 92         | IO11RSB0        |  |

| 21         | GEC0/IO100NDB3  | 57         | GDA1/IO60USB1   | 93         | GAC1/IO05RSB0   |  |

| 22         | GEA1/IO98PDB3   | 58         | GDC0/IO58VDB1   | 94         | GAC0/IO04RSB0   |  |

| 23         | GEA0/IO98NDB3   | 59         | GDC1/IO58UDB1   | 95         | GAB1/IO03RSB0   |  |

| 24         | VMV3            | 60         | IO52NDB1        | 96         | GAB0/IO02RSB0   |  |

| 25         | GNDQ            | 61         | GCB2/IO52PDB1   | 97         | GAA1/IO01RSB0   |  |

| 26         | GEA2/IO97RSB2   | 62         | GCA1/IO50PDB1   | 98         | GAA0/IO00RSB0   |  |

| 27         | GEB2/IO96RSB2   | 63         | GCA0/IO50NDB1   | 99         | GNDQ            |  |

| 28         | GEC2/IO95RSB2   | 64         | GCC0/IO48NDB1   | 100        | VMV0            |  |

| 29         | IO93RSB2        | 65         | GCC1/IO48PDB1   |            |                 |  |

| 30         | IO92RSB2        | 66         | VCCIB1          |            |                 |  |

| 31         | IO91RSB2        | 67         | GND             |            |                 |  |

| 32         | IO90RSB2        | 68         | VCC             |            |                 |  |

| 33         | IO88RSB2        | 69         | IO43NDB1        |            |                 |  |

| 34         | IO86RSB2        | 70         | GBC2/IO43PDB1   |            |                 |  |

| 35         | IO85RSB2        | 71         | GBB2/IO42PSB1   |            |                 |  |

| 36         | IO84RSB2        | 72         | IO41NDB1        |            |                 |  |

Package Pin Assignments

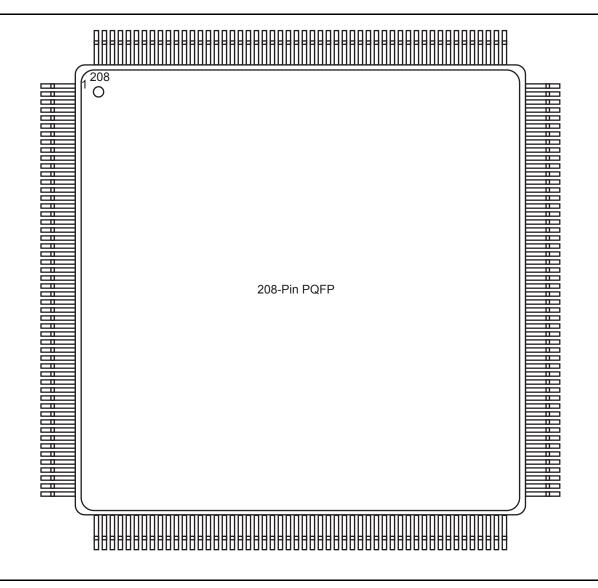

# PQ208 – Top View

## Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

## **Microsemi**

| PQ208      |                 |            | PQ208           | PQ208      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | A3P125 Function | Pin Number | A3P125 Function | Pin Number | A3P125 Function |  |

| 109        | TRST            | 145        | IO46RSB0        | 181        | IO21RSB0        |  |

| 110        | VJTAG           | 146        | NC              | 182        | IO20RSB0        |  |

| 111        | GDA0/IO66RSB0   | 147        | NC              | 183        | IO19RSB0        |  |

| 112        | GDA1/IO65RSB0   | 148        | NC              | 184        | IO18RSB0        |  |

| 113        | GDB0/IO64RSB0   | 149        | GBC2/IO45RSB0   | 185        | IO17RSB0        |  |

| 114        | GDB1/IO63RSB0   | 150        | IO44RSB0        | 186        | VCCIB0          |  |

| 115        | GDC0/IO62RSB0   | 151        | GBB2/IO43RSB0   | 187        | VCC             |  |

| 116        | GDC1/IO61RSB0   | 152        | IO42RSB0        | 188        | IO16RSB0        |  |

| 117        | NC              | 153        | GBA2/IO41RSB0   | 189        | IO15RSB0        |  |

| 118        | NC              | 154        | VMV0            | 190        | IO14RSB0        |  |

| 119        | NC              | 155        | GNDQ            | 191        | IO13RSB0        |  |

| 120        | NC              | 156        | GND             | 192        | IO12RSB0        |  |

| 121        | NC              | 157        | NC              | 193        | IO11RSB0        |  |

| 122        | GND             | 158        | GBA1/IO40RSB0   | 194        | IO10RSB0        |  |

| 123        | VCCIB0          | 159        | GBA0/IO39RSB0   | 195        | GND             |  |

| 124        | NC              | 160        | GBB1/IO38RSB0   | 196        | IO09RSB0        |  |

| 125        | NC              | 161        | GBB0/IO37RSB0   | 197        | IO08RSB0        |  |

| 126        | VCC             | 162        | GND             | 198        | IO07RSB0        |  |

| 127        | IO60RSB0        | 163        | GBC1/IO36RSB0   | 199        | IO06RSB0        |  |

| 128        | GCC2/IO59RSB0   | 164        | GBC0/IO35RSB0   | 200        | VCCIB0          |  |

| 129        | GCB2/IO58RSB0   | 165        | IO34RSB0        | 201        | GAC1/IO05RSB0   |  |

| 130        | GND             | 166        | IO33RSB0        | 202        | GAC0/IO04RSB0   |  |

| 131        | GCA2/IO57RSB0   | 167        | IO32RSB0        | 203        | GAB1/IO03RSB0   |  |

| 132        | GCA0/IO56RSB0   | 168        | IO31RSB0        | 204        | GAB0/IO02RSB0   |  |

| 133        | GCA1/IO55RSB0   | 169        | IO30RSB0        | 205        | GAA1/IO01RSB0   |  |

| 134        | GCB0/IO54RSB0   | 170        | VCCIB0          | 206        | GAA0/IO00RSB0   |  |

| 135        | GCB1/IO53RSB0   | 171        | VCC             | 207        | GNDQ            |  |

| 136        | GCC0/IO52RSB0   | 172        | IO29RSB0        | 208        | VMV0            |  |

| 137        | GCC1/IO51RSB0   | 173        | IO28RSB0        |            |                 |  |

| 138        | IO50RSB0        | 174        | IO27RSB0        |            |                 |  |

| 139        | IO49RSB0        | 175        | IO26RSB0        |            |                 |  |

| 140        | VCCIB0          | 176        | IO25RSB0        |            |                 |  |

| 141        | GND             | 177        | IO24RSB0        |            |                 |  |

| 142        | VCC             | 178        | GND             |            |                 |  |

| 143        | IO48RSB0        | 179        | IO23RSB0        |            |                 |  |

| 144        | IO47RSB0        | 180        | IO22RSB0        |            |                 |  |

## 🌜 Microsemi.

| F          | G144            | F          | G144            | F          | G144            |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | A3P250 Function | Pin Number | A3P250 Function | Pin Number | A3P250 Function |

| A1         | GNDQ            | D1         | IO112NDB3       | G1         | GFA1/IO108PPB3  |

| A2         | VMV0            | D2         | IO112PDB3       | G2         | GND             |

| A3         | GAB0/IO02RSB0   | D3         | IO116VDB3       | G3         | VCCPLF          |

| A4         | GAB1/IO03RSB0   | D4         | GAA2/IO118UPB3  | G4         | GFA0/IO108NPB3  |

| A5         | IO16RSB0        | D5         | GAC0/IO04RSB0   | G5         | GND             |

| A6         | GND             | D6         | GAC1/IO05RSB0   | G6         | GND             |

| A7         | IO29RSB0        | D7         | GBC0/IO35RSB0   | G7         | GND             |

| A8         | VCC             | D8         | GBC1/IO36RSB0   | G8         | GDC1/IO58UPB1   |

| A9         | IO33RSB0        | D9         | GBB2/IO42PDB1   | G9         | IO53NDB1        |

| A10        | GBA0/IO39RSB0   | D10        | IO42NDB1        | G10        | GCC2/IO53PDB1   |

| A11        | GBA1/IO40RSB0   | D11        | IO43NPB1        | G11        | IO52NDB1        |

| A12        | GNDQ            | D12        | GCB1/IO49PPB1   | G12        | GCB2/IO52PDB1   |

| B1         | GAB2/IO117UDB3  | E1         | VCC             | H1         | VCC             |

| B2         | GND             | E2         | GFC0/IO110NDB3  | H2         | GFB2/IO106PDB3  |

| B3         | GAA0/IO00RSB0   | E3         | GFC1/IO110PDB3  | H3         | GFC2/IO105PSB3  |

| B4         | GAA1/IO01RSB0   | E4         | VCCIB3          | H4         | GEC1/IO100PDB3  |

| B5         | IO14RSB0        | E5         | IO118VPB3       | H5         | VCC             |

| B6         | IO19RSB0        | E6         | VCCIB0          | H6         | IO79RSB2        |

| B7         | IO22RSB0        | E7         | VCCIB0          | H7         | IO65RSB2        |

| B8         | IO30RSB0        | E8         | GCC1/IO48PDB1   | H8         | GDB2/IO62RSB2   |

| B9         | GBB0/IO37RSB0   | E9         | VCCIB1          | H9         | GDC0/IO58VPB1   |

| B10        | GBB1/IO38RSB0   | E10        | VCC             | H10        | VCCIB1          |

| B11        | GND             | E11        | GCA0/IO50NDB1   | H11        | IO54PSB1        |

| B12        | VMV1            | E12        | IO51NDB1        | H12        | VCC             |

| C1         | IO117VDB3       | F1         | GFB0/IO109NPB3  | J1         | GEB1/IO99PDB3   |

| C2         | GFA2/IO107PPB3  | F2         | VCOMPLF         | J2         | IO106NDB3       |

| C3         | GAC2/IO116UDB3  | F3         | GFB1/IO109PPB3  | J3         | VCCIB3          |

| C4         | VCC             | F4         | IO107NPB3       | J4         | GEC0/IO100NDB3  |

| C5         | IO12RSB0        | F5         | GND             | J5         | IO88RSB2        |

| C6         | IO17RSB0        | F6         | GND             | J6         | IO81RSB2        |

| C7         | IO24RSB0        | F7         | GND             | J7         | VCC             |

| C8         | IO31RSB0        | F8         | GCC0/IO48NDB1   | J8         | ТСК             |

| C9         | IO34RSB0        | F9         | GCB0/IO49NPB1   | J9         | GDA2/IO61RSB2   |

| C10        | GBA2/IO41PDB1   | F10        | GND             | J10        | TDO             |

| C11        | IO41NDB1        | F11        | GCA1/IO50PDB1   | J11        | GDA1/IO60UDB1   |

| C12        | GBC2/IO43PPB1   | F12        | GCA2/IO51PDB1   | J12        | GDB1/IO59UDB1   |

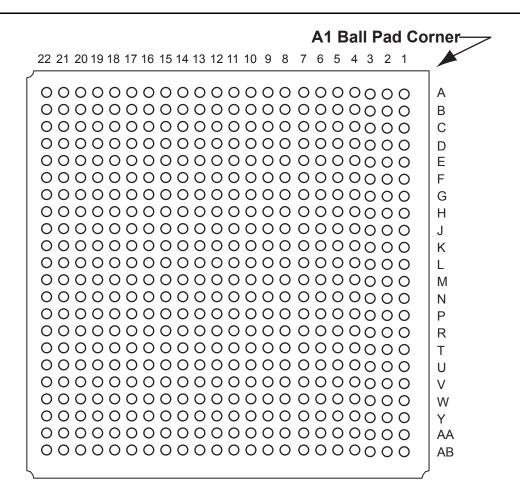

# FG484 – Bottom View

## Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

## 🌜 Microsemi.

|            | FG484            |            | FG484            |            | FG484            |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | A3P1000 Function | Pin Number | A3P1000 Function | Pin Number | A3P1000 Function |

| A1         | GND              | B15        | IO63RSB0         | D7         | GAB0/IO02RSB0    |

| A2         | GND              | B16        | IO66RSB0         | D8         | IO16RSB0         |

| A3         | VCCIB0           | B17        | IO68RSB0         | D9         | IO22RSB0         |

| A4         | IO07RSB0         | B18        | IO70RSB0         | D10        | IO28RSB0         |

| A5         | IO09RSB0         | B19        | NC               | D11        | IO35RSB0         |

| A6         | IO13RSB0         | B20        | NC               | D12        | IO45RSB0         |

| A7         | IO18RSB0         | B21        | VCCIB1           | D13        | IO50RSB0         |

| A8         | IO20RSB0         | B22        | GND              | D14        | IO55RSB0         |

| A9         | IO26RSB0         | C1         | VCCIB3           | D15        | IO61RSB0         |

| A10        | IO32RSB0         | C2         | IO220PDB3        | D16        | GBB1/IO75RSB0    |

| A11        | IO40RSB0         | C3         | NC               | D17        | GBA0/IO76RSB0    |

| A12        | IO41RSB0         | C4         | NC               | D18        | GBA1/IO77RSB0    |

| A13        | IO53RSB0         | C5         | GND              | D19        | GND              |

| A14        | IO59RSB0         | C6         | IO10RSB0         | D20        | NC               |

| A15        | IO64RSB0         | C7         | IO14RSB0         | D21        | NC               |

| A16        | IO65RSB0         | C8         | VCC              | D22        | NC               |

| A17        | IO67RSB0         | C9         | VCC              | E1         | IO219NDB3        |

| A18        | IO69RSB0         | C10        | IO30RSB0         | E2         | NC               |

| A19        | NC               | C11        | IO37RSB0         | E3         | GND              |

| A20        | VCCIB0           | C12        | IO43RSB0         | E4         | GAB2/IO224PDB3   |

| A21        | GND              | C13        | NC               | E5         | GAA2/IO225PDB3   |

| A22        | GND              | C14        | VCC              | E6         | GNDQ             |

| B1         | GND              | C15        | VCC              | E7         | GAB1/IO03RSB0    |

| B2         | VCCIB3           | C16        | NC               | E8         | IO17RSB0         |

| B3         | NC               | C17        | NC               | E9         | IO21RSB0         |

| B4         | IO06RSB0         | C18        | GND              | E10        | IO27RSB0         |

| B5         | IO08RSB0         | C19        | NC               | E11        | IO34RSB0         |

| B6         | IO12RSB0         | C20        | NC               | E12        | IO44RSB0         |

| B7         | IO15RSB0         | C21        | NC               | E13        | IO51RSB0         |

| B8         | IO19RSB0         | C22        | VCCIB1           | E14        | IO57RSB0         |

| B9         | IO24RSB0         | D1         | IO219PDB3        | E15        | GBC1/IO73RSB0    |

| B10        | IO31RSB0         | D2         | IO220NDB3        | E16        | GBB0/IO74RSB0    |

| B11        | IO39RSB0         | D3         | NC               | E17        | IO71RSB0         |

| B12        | IO48RSB0         | D4         | GND              | E18        | GBA2/IO78PDB1    |

| B13        | IO54RSB0         | D5         | GAA0/IO00RSB0    | E19        | IO81PDB1         |

| B14        | IO58RSB0         | D6         | GAA1/IO01RSB0    | E20        | GND              |

Datasheet Information

| Revision             | Changes                                                                                                                                                                                                                                                                                                                     | Page             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| v2.0<br>(April 2007) | In the "Packaging Tables", Ambient was deleted.                                                                                                                                                                                                                                                                             | ii               |

|                      | The timing characteristics tables were updated.                                                                                                                                                                                                                                                                             | N/A              |

|                      | The "PLL Macro" section was updated to add information on the VCO and PLL outputs during power-up.                                                                                                                                                                                                                          | 2-15             |

|                      | The "PLL Macro" section was updated to include power-up information.                                                                                                                                                                                                                                                        | 2-15             |

|                      | Table 2-11 • ProASIC3 CCC/PLL Specification was updated.                                                                                                                                                                                                                                                                    | 2-29             |

|                      | Figure 2-19 • Peak-to-Peak Jitter Definition is new.                                                                                                                                                                                                                                                                        | 2-18             |

|                      | The "SRAM and FIFO" section was updated with operation and timing requirement information.                                                                                                                                                                                                                                  | 2-21             |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                                                                                                                                            | 2-25             |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                                                                                                                                            | 2-25             |

|                      | The "Introduction" in the "Advanced I/Os" section was updated to include information on input and output buffers being disabled.                                                                                                                                                                                            | 2-28             |

|                      | PCI-X 3.3 V was added to Table 2-11 • VCCI Voltages and Compatible Standards.                                                                                                                                                                                                                                               | 2-29             |

|                      | In the Table 2-15 • Levels of Hot-Swap Support, the ProASIC3 compliance descriptions were updated for levels 3 and 4.                                                                                                                                                                                                       | 2-34             |

|                      | Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices was updated.                                                                                                                                                                                                                             | 2-64             |

|                      | Notes 3, 4, and 5 were added to Table 2-17 $\cdot$ Comparison Table for 5 V–Compliant Receiver Scheme. 5 x 52.72 was changed to 52.7 and the Maximum current was updated from 4 x 52.7 to 5 x 52.7.                                                                                                                         | 2-40             |

|                      | The "VCCPLF PLL Supply Voltage" section was updated.                                                                                                                                                                                                                                                                        | 2-50             |

|                      | The "VPUMP Programming Supply Voltage" section was updated.                                                                                                                                                                                                                                                                 | 2-50             |

|                      | The "GL Globals" section was updated to include information about direct input into quadrant clocks.                                                                                                                                                                                                                        | 2-51             |

|                      | V <sub>JTAG</sub> was deleted from the "TCK Test Clock" section.                                                                                                                                                                                                                                                            | 2-51             |

|                      | In Table 2-22 • Recommended Tie-Off Values for the TCK and TRST Pins, TSK was changed to TCK in note 2. Note 3 was also updated.                                                                                                                                                                                            | 2-51             |

|                      | Ambient was deleted from Table 3-2 • Recommended Operating Conditions. VPUMP programming mode was changed from "3.0 to 3.6" to "3.15 to 3.45".                                                                                                                                                                              | 3-2              |

|                      | Note 3 is new in Table 3-4 • Overshoot and Undershoot Limits (as measured on quiet I/Os)1.                                                                                                                                                                                                                                  | 3-2              |

|                      | In EQ 3-2, 150 was changed to 110 and the result changed from 3.9 to 1.951.                                                                                                                                                                                                                                                 | 3-5              |

|                      | Table 3-6 • Temperature and Voltage Derating Factors for Timing Delays was updated.                                                                                                                                                                                                                                         | 3-6              |

|                      | Table 3-5       •       Package Thermal Resistivities was updated.                                                                                                                                                                                                                                                          | 3-5              |

|                      | Table 3-14 • Summary of Maximum and Minimum DC Input and Output Levels<br>Applicable to Commercial and Industrial Conditions—Software Default Settings<br>(Advanced) and Table 3-17 • Summary of Maximum and Minimum DC Input<br>Levels Applicable to Commercial and Industrial Conditions (Standard Plus) were<br>updated. | 3-17 to 3-<br>17 |