### NXP USA Inc. - MC68HC908JK3ECDW Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | LED, LVD, POR, PWM                                                       |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                              |

| Data Converters            | A/D 12x8b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908jk3ecdw |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

List of Chapters

General Description

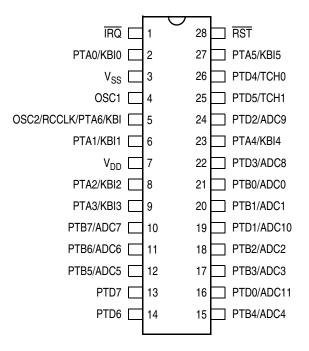

## 1.4 Pin Assignments

### MC68H(R)C908JL3E

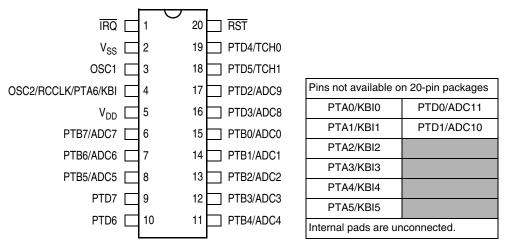

### MC68H(R)C908JK3E/JK1E

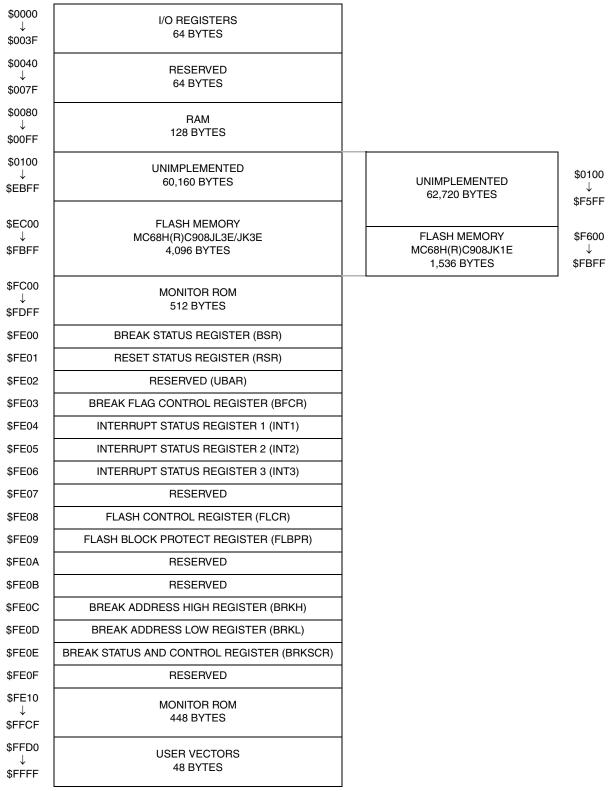

Memory

Figure 2-1. Memory Map

# NP

#### **Configuration Registers (CONFIG)**

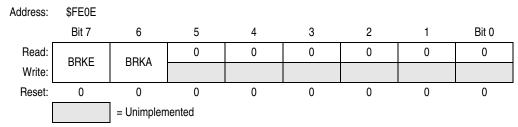

### LVID — Low Voltage Inhibit Disable Bit

- 1 = Low Voltage Inhibit disabled

- 0 = Low Voltage Inhibit enabled

### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of

$32 \times 20$ SCOUT cycles instead of a  $4096 \times 20$ SCOUT cycle delay.

1 = Stop mode recovery after 32 × 20SCOUT cycles

0 = Stop mode recovery after 4096 × 2OSCOUT cycles

#### NOTE

Exiting stop mode by pulling reset will result in the long stop recovery.

If using an external crystal, do not set the SSREC bit.

#### STOP — STOP Instruction Enable

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### COPD — COP Disable Bit

COPD disables the COP module. (See Chapter 13 Computer Operating Properly (COP).)

- 1 = COP module disabled

- 0 = COP module enabled

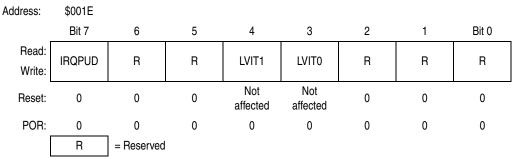

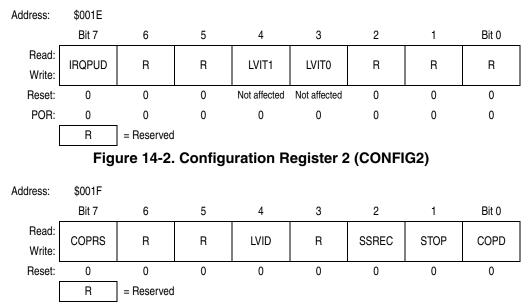

### 3.4 Configuration Register 2 (CONFIG2)

#### Figure 3-2. Configuration Register 2 (CONFIG2)

### IRQPUD — IRQ Pin Pull-up control bit

1 = Internal pull-up is disconnected

0 = Internal pull-up is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

#### LVIT1, LVIT0 — Low Voltage Inhibit trip voltage selection bits

Detail description of the LVI control signals is given in Chapter 14 Low Voltage Inhibit (LVI)

# Chapter 4 Central Processor Unit (CPU)

### 4.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

### 4.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

# 4.3 CPU Registers

Figure 4-1 shows the five CPU registers. CPU registers are not part of the memory map.

#### System Integration Module (SIM)

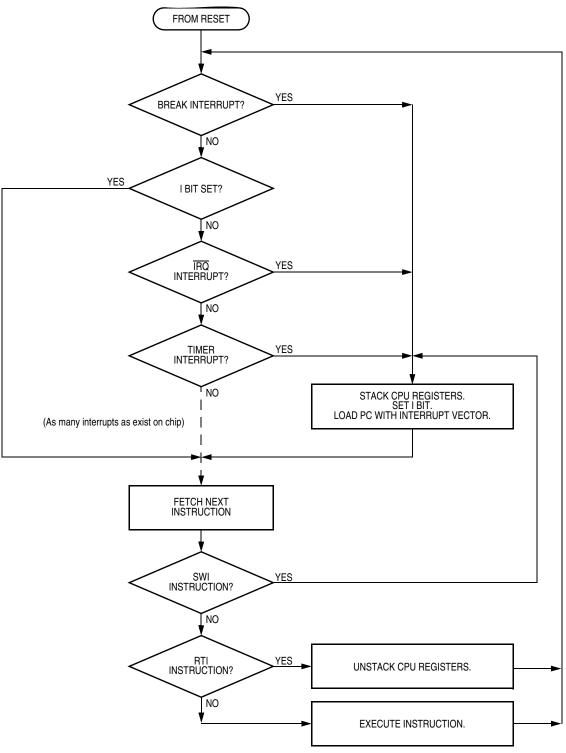

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared).

Figure 5-8. Interrupt Processing

MC68HC908JL3E Family Data Sheet, Rev. 4

**Oscillator (OSC)**

### 6.5 Low Power Modes

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

### 6.5.1 Wait Mode

The WAIT instruction has no effect on the oscillator logic. OSCOUT and 2OSCOUT continues to drive to the SIM module.

### 6.5.2 Stop Mode

The STOP instruction disables the XTALCLK or the RCCLK output, hence OSCOUT and 2OSCOUT.

### 6.6 Oscillator During Break Mode

The oscillator continues to drive OSCOUT and 2OSCOUT when the device enters the break state.

### 7.3.1 Entering Monitor Mode

Table 7-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a POR and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- 1. If  $\overline{IRQ} = V_{TST}$ :

- Clock on OSC1 is 4.9125MHz (EXT OSC or XTAL)

- PTB3 = low

- 2. If  $\overline{IRQ} = V_{TST}$ :

- Clock on OSC1 is 9.8304MHz (EXT OSC or XTAL)

- PTB3 = high

- 3. If \$FFFE & \$FFFF is blank (contains \$FF):

- Clock on OSC1 is 9.8304 MHz (EXT OSC or XTAL or RC)

- IRQ = V<sub>DD</sub>

### Table 7-1. Monitor Mode Entry Requirements and Options

| ĪRQ                             | \$FFFE<br>and<br>\$FFFF    | PTB3 <sup>(1)</sup> | PTB2 | PTB1 | PTB0 | OSC1 Frequency          | Bus<br>Frequency        | Comments                                                                                                  |

|---------------------------------|----------------------------|---------------------|------|------|------|-------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------|

| V <sub>TST</sub> <sup>(2)</sup> | х                          | 0                   | 0    | 1    | 1    | 4.9152MHz               | 2.4576MHz<br>(OSC1 ÷ 2) | High-voltage entry to monitor mode. <sup>(3)</sup>                                                        |

| V <sub>TST</sub>                | Х                          | 1                   | 0    | 1    | 1    | 9.8304MHz               | 2.4576MHz<br>(OSC1 ÷ 4) | 9600 baud communication on PTB0. COP disabled.                                                            |

| V <sub>DD</sub>                 | BLANK<br>(contain<br>\$FF) | x                   | x    | х    | 1    | 9.8304MHz               | 2.4576MHz<br>(OSC1 ÷ 4) | Low-voltage entry to monitor<br>mode. <sup>(4)</sup><br>9600 baud communication on<br>PTB0. COP disabled. |

| V <sub>DD</sub>                 | NOT<br>BLANK               | х                   | х    | х    | х    | At desired<br>frequency | OSC1 ÷ 4                | Enters User mode.                                                                                         |

1. PTB3 = 0: Bypasses the divide-by-two prescaler to SIM when using  $V_{TST}$  for monitor mode entry.

The OSC1 clock must be 50% duty cycle for this condition.

2. See Table 16-4. DC Electrical Characteristics (5V) for  $V_{TST}$  voltage level requirements.

3. For  $\overline{IRQ} = V_{TST}$ :

MC68HRC908JL3E/JK3E/JK1E — clock must be EXT OSC. MC68HC908JL3E/JK3E/JK1E — clock can be EXT OSC or XTAL.

4. For IRQ = V<sub>DD</sub>: MC68HRC908JL3E/JK3E/JK1E — clock must be RC OSC. MC68HC908JL3E/JK3E/JK1E — clock can be EXT OSC or XTAL.

If  $V_{TST}$  is applied to  $\overline{IRQ}$  and PTB3 is low upon monitor mode entry (Table 7-1 condition set 1), the bus frequency is a divide-by-two of the clock input to OSC1. If PTB3 is high with  $V_{TST}$  applied to  $\overline{IRQ}$  upon monitor mode entry (Table 7-1 condition set 2), the bus frequency is a divide-by-four of the clock input to OSC1. Holding the PTB3 pin low when entering monitor mode causes a bypass of a divide-by-two stage at the oscillator *only if*  $V_{TST}$  *is applied to*  $\overline{IRQ}$ . In this event, the OSCOUT frequency is equal to the 2OSCOUT frequency, and OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.

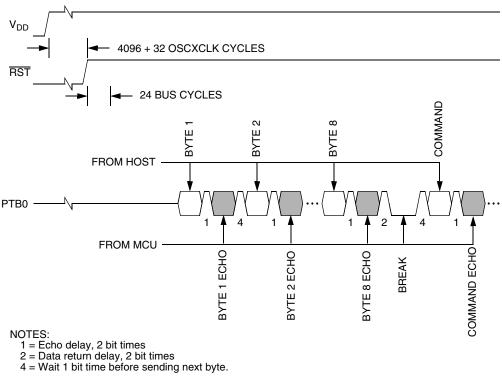

| Description        | Reads stack pointer                               |

|--------------------|---------------------------------------------------|

| Operand            | None                                              |

| Data Returned      | Returns stack pointer in high byte:low byte order |

| Opcode             | \$0C                                              |

| Command Sequence   |                                                   |

| SENT TO<br>MONITOR | READSP     SP HIGH     SP LOW       RESULT        |

#### Table 7-9. RUN (Run User Program) Command

| Description        | Executes RTI instruction |

|--------------------|--------------------------|

| Operand            | None                     |

| Data Returned      | None                     |

| Opcode             | \$28                     |

| Command Sequence   |                          |

| SENT TO<br>MONITOR |                          |

| ECHO ———           |                          |

### 7.4 Security

A security feature discourages unauthorized reading of Flash locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6–\$FFFD. Locations \$FFF6–\$FFFD contain user-defined data.

#### NOTE

Do not leave locations \$FFF6-\$FFFD blank. For security reasons, program locations \$FFF6-\$FFFD even if they are not used for vectors.

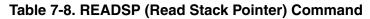

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTB0. If the received bytes match those at locations \$FFF6-\$FFFD, the host bypasses the security feature and can read all Flash locations and execute code from Flash. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. (See Figure 7-7.)

#### Monitor ROM (MON)

#### Figure 7-7. Monitor Mode Entry Timing

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6-\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a Flash location returns an invalid value and trying to execute code from Flash causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

#### NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$80 is set. If it is, then the correct security code has been entered and Flash can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the Flash module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

#### **Functional Description**

| Addr.  | Register Name                                           |                 | Bit 7 | 6       | 5        | 4           | 3              | 2     | 1    | Bit 0    |

|--------|---------------------------------------------------------|-----------------|-------|---------|----------|-------------|----------------|-------|------|----------|

|        |                                                         | Read:           | TOF   | TOIL    | TOTOD    | 0           | 0              | DCO   | DO1  | DCO      |

| \$0020 | TIM Status and Control<br>Register (TSC)                | Write:          | 0     | TOIE    | TSTOP    | TRST        |                | PS2   | PS1  | PS0      |

|        |                                                         | Reset:          | 0     | 0       | 1        | 0           | 0              | 0     | 0    | 0        |

|        | TIM Occurrent De sciete a Lliste                        | Read:           | Bit15 | Bit14   | Bit13    | Bit12       | Bit11          | Bit10 | Bit9 | Bit8     |

| \$0021 | TIM Counter Register High<br>(TCNTH)                    | Write:          |       |         |          |             |                |       |      |          |

|        |                                                         | Reset:          | 0     | 0       | 0        | 0           | 0              | 0     | 0    | 0        |

|        | TIM Counter Register Low                                | Read:           | Bit7  | Bit6    | Bit5     | Bit4        | Bit3           | Bit2  | Bit1 | Bit0     |

| \$0022 | (TCNTL)                                                 | Write:          |       |         |          |             |                |       |      |          |

|        | ( )                                                     | Reset:          | 0     | 0       | 0        | 0           | 0              | 0     | 0    | 0        |

| \$0023 | TIM Counter Modulo Register<br>High (TMODH)             | Read:<br>Write: | Bit15 | Bit14   | Bit13    | Bit12       | Bit11          | Bit10 | Bit9 | Bit8     |

|        |                                                         | Reset:          | 1     | 1       | 1        | 1           | 1              | 1     | 1    | 1        |

| \$0024 | TIM Counter Modulo Register<br>Low (TMODL)              | Read:<br>Write: | Bit7  | Bit6    | Bit5     | Bit4        | Bit3           | Bit2  | Bit1 | Bit0     |

|        |                                                         | Reset:          | 1     | 1       | 1        | 1           | 1              | 1     | 1    | 1        |

|        | TIM Channel 0 Status and                                |                 | CH0F  | CH0IE   | MS0B     | MS0A        | ELS0B          | ELS0A | TOV0 | CHOMAX   |

| \$0025 | 025 TIM Channel 0 Status and<br>Control Register (TSC0) | Write:          | 0     | ONDIE   | IVISUD   | WOOA        | ELOUD          | ELSUA | 1000 | CHUIVIAA |

|        |                                                         | Reset:          | 0     | 0       | 0        | 0           | 0              | 0     | 0    | 0        |

| \$0026 | TIM Channel 0 Register High<br>(TCH0H)                  | Read:<br>Write: | Bit15 | Bit14   | Bit13    | Bit12       | Bit11          | Bit10 | Bit9 | Bit8     |

|        |                                                         | Reset:          |       |         |          | Indetermina | te after reset |       |      |          |

| \$0027 | TIM Channel 0 Register Low<br>(TCH0L)                   | Read:<br>Write: | Bit7  | Bit6    | Bit5     | Bit4        | Bit3           | Bit2  | Bit1 | Bit0     |

|        |                                                         | Reset:          |       |         | •        | Indetermina | te after reset |       |      | •        |

|        | <b>TIIIIIIIIIIIII</b>                                   | Read:           | CH1F  | CH1IE   | 0        | MS1A        | ELS1B          | ELS1A | TOV1 | CH1MAX   |

| \$0028 | TIM Channel 1 Status and<br>Control Register (TSC1)     | Write:          | 0     | CHILE   |          | NISTA       | ELOID          | ELSTA | 1001 | CITIVIAN |

|        |                                                         | Reset:          | 0     | 0       | 0        | 0           | 0              | 0     | 0    | 0        |

| \$0029 | TIM Channel 1 Register High<br>(TCH1H)                  | Read:<br>Write: | Bit15 | Bit14   | Bit13    | Bit12       | Bit11          | Bit10 | Bit9 | Bit8     |

|        | (101111)                                                | Reset:          |       |         |          | Indetermina | te after reset | -     |      |          |

| \$002A | TIM Channel 1 Register Low<br>(TCH1L)                   | Read:<br>Write: | Bit7  | Bit6    | Bit5     | Bit4        | Bit3           | Bit2  | Bit1 | Bit0     |

|        | (10.112)                                                | Reset:          |       |         |          | Indetermina | te after reset |       |      |          |

|        |                                                         |                 |       | = Unimp | lemented |             |                |       |      |          |

|        |                                                         |                 |       |         |          | •           |                |       |      |          |

Figure 8-2. TIM I/O Register Summary

MC68HC908JL3E Family Data Sheet, Rev. 4

### 8.4.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use the following initialization procedure:

- 1. In the TIM status and control register (TSC):

- a. Stop the TIM counter by setting the TIM stop bit, TSTOP.

- b. Reset the TIM counter and prescaler by setting the TIM reset bit, TRST.

- 2. In the TIM counter modulo registers (TMODH:TMODL), write the value for the required PWM period.

- 3. In the TIM channel x registers (TCHxH:TCHxL), write the value for the required pulse width.

- 4. In TIM channel x status and control register (TSCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB:MSxA. (See Table 8-3.)

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. (See Table 8-3.)

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM status control register (TSC), clear the TIM stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSC0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. (See 8.9.4 TIM Channel Status and Control Registers (TSC0:TSC1).)

# Chapter 9 Analog-to-Digital Converter (ADC)

### 9.1 Introduction

This section describes the 12-channel, 8-bit linear successive approximation analog-to-digital converter (ADC).

### 9.2 Features

Features of the ADC module include:

- 12 channels with multiplexed input

- · Linear successive approximation with monotonicity

- 8-bit resolution

- Single or continuous conversion

- Conversion complete flag or conversion complete interrupt

- Selectable ADC clock

| Addr.  | Register Name                              |        | Bit 7                     | 6           | 5     | 4     | 3       | 2      | 1     | Bit 0 |  |  |

|--------|--------------------------------------------|--------|---------------------------|-------------|-------|-------|---------|--------|-------|-------|--|--|

|        |                                            | Read:  | 0000                      | AIEN        | ADCO  | ADCH4 | ADCH3   | ADCH2  | ADCH1 | ADCH0 |  |  |

| \$003C | ADC Status and Control<br>Register (ADSCR) | Write: |                           |             | ADOO  |       | ADOI 10 | ADOINZ | Aboin | ADOIN |  |  |

|        |                                            | Reset: | 0                         | 0           | 0     | 1     | 1       | 1      | 1     | 1     |  |  |

|        |                                            | Read:  | AD7                       | AD6         | AD5   | AD4   | AD3     | AD2    | AD1   | AD0   |  |  |

| \$003D | ADC Data Register<br>(ADR)                 | Write: |                           |             |       |       |         |        |       |       |  |  |

|        | (ADA)                                      |        | Indeterminate after reset |             |       |       |         |        |       |       |  |  |

|        |                                            | Read:  | ADIV2                     | ADIV1       | ADIV0 | 0     | 0       | 0      | 0     | 0     |  |  |

| \$003E | ADC Input Clock Register<br>(ADICLK)       | Write: | ADIV2                     | ADIVI       | ADIVU |       |         |        |       |       |  |  |

|        |                                            | Reset: | 0                         | 0           | 0     | 0     | 0       | 0      | 0     | 0     |  |  |

|        |                                            |        |                           | = Unimpleme | ented |       |         |        |       |       |  |  |

### 9.3 Functional Description

Twelve ADC channels are available for sampling external sources at pins PTB0–PTB7 and PTD0–PTD3. An analog multiplexer allows the single ADC converter to select one of the 12 ADC channels as ADC voltage input (ADCVIN). ADCVIN is converted by the successive approximation register-based counters. The ADC resolution is 8 bits. When the conversion is completed, ADC puts the result in the ADC data register and sets a flag or generates an interrupt. Figure 9-2 shows a block diagram of the ADC.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge-sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt pin stays at 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

To determine the logic level on a keyboard interrupt pin, disable the pull-up device, use the data direction register to configure the pin as an input and then read the data register.

### NOTE

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

### 12.4.1 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pull-up to reach a logic 1. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- 1. Configure the keyboard pins as outputs by setting the appropriate DDRA bits in the data direction register A.

- 2. Write 1s to the appropriate port A data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

### 12.5 Keyboard Interrupt Registers

Two registers control the operation of the keyboard interrupt module:

- Keyboard status and control register

- Keyboard interrupt enable register

#### **Computer Operating Properly (COP)**

### 13.7.1 Wait Mode

The COP continues to operate during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter in a CPU interrupt routine.

### 13.7.2 Stop Mode

Stop mode turns off the 2OSCOUT input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

### 13.8 COP Module During Break Mode

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

Low Voltage Inhibit (LVI)

# 14.4 LVI Control Register (CONFIG2/CONFIG1)

The LVI module is controlled by three bits in the configuration registers, CONFIG1 and CONFIG2.

### Figure 14-3. Configuration Register 1 (CONFIG1)

### LVID — Low Voltage Inhibit Disable Bit

1 = Low voltage inhibit disabled

0 = Low voltage inhibit enabled

### LVIT1, LVIT0 — LVI Trip Voltage Selection

These two bits determine at which level of  $V_{DD}$  the LVI module will come into action. LVIT1 and LVIT0 are cleared by a Power-On Reset only.

| LVIT1 | LVIT0 | Trip Voltage <sup>(1)</sup> | Comments                          |

|-------|-------|-----------------------------|-----------------------------------|

| 0     | 0     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 0     | 1     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 1     | 0     | V <sub>LVR5</sub> (4.0V)    | For V <sub>DD</sub> =5V operation |

| 1     | 1     | Reserved                    |                                   |

1. See Chapter 16 Electrical Specifications for full parameters.

### 14.5 Low-Power Modes

The STOP and WAIT instructions put the MCU in low-power-consumption standby modes.

### 14.5.1 Wait Mode

The LVI module, when enabled, will continue to operate in WAIT Mode.

### 14.5.2 Stop Mode

The LVI module, when enabled, will continue to operate in STOP Mode.

MC68HC908JL3E Family Data Sheet, Rev. 4

# NP

#### **Break Module (BREAK)**

| Addr.           | Register Name                  |                 | Bit 7 | 6          | 5     | 4     | 3          | 2     | 1                | Bit 0 |

|-----------------|--------------------------------|-----------------|-------|------------|-------|-------|------------|-------|------------------|-------|

| \$FE00          | Break Status Register<br>(BSR) | Read:<br>Write: | R     | R          | R     | R     | R          | R     | SBSW<br>See note | R     |

|                 | ()                             | Reset:          |       |            |       |       |            |       | 0                |       |

| \$FE03          | Break Flag Control<br>Register | Read:<br>Write: | BCFE  | R          | R     | R     | R          | R     | R                | R     |

|                 | (BFCR)                         | Reset:          | 0     |            |       |       |            |       |                  |       |

| \$FE0C          | Break Address High<br>Register | Read:<br>Write: | Bit15 | Bit14      | Bit13 | Bit12 | Bit11      | Bit10 | Bit9             | Bit8  |

|                 | (BRKH)                         | Reset:          | 0     | 0          | 0     | 0     | 0          | 0     | 0                | 0     |

| \$FE0D          | Break Address low<br>Register  | Read:<br>Write: | Bit7  | Bit6       | Bit5  | Bit4  | Bit3       | Bit2  | Bit1             | Bit0  |

|                 | (BRKL)                         |                 | 0     | 0          | 0     | 0     | 0          | 0     | 0                | 0     |

|                 | Break Status and Control       | Read:           | BRKE  | BRKA       | 0     | 0     | 0          | 0     | 0                | 0     |

| \$FE0E Register | Write:                         | DAKE            | DHKA  |            |       |       |            |       |                  |       |

|                 | (BRKSCR)                       | Reset:          | 0     | 0          | 0     | 0     | 0          | 0     | 0                | 0     |

| Note: Writir    | ng a 0 clears SBSW.            |                 |       | = Unimplem | ented | R     | = Reserved |       |                  |       |

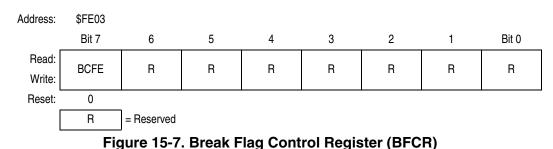

### Figure 15-2. Break I/O Register Summary

### **15.3.1 Flag Protection During Break Interrupts**

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. (See 5.7.3 Break Flag Control Register (BFCR) and see the Break Interrupts subsection for each module.)

### 15.3.2 CPU During Break Interrupts

The CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD (\$FEFC:\$FEFD in monitor mode)

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

### 15.3.3 TIM During Break Interrupts

A break interrupt stops the timer counter.

### 15.3.4 COP During Break Interrupts

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

**Break Module Registers**

### 15.4 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

- Break status register (BSR)

- Break flag control register (BFCR)

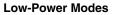

### 15.4.1 Break Status and Control Register (BRKSCR)

The break status and control register contains break module enable and status bits.

Figure 15-3. Break Status and Control Register (BRKSCR)

#### BRKE — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a zero to bit 7. Reset clears the BRKE bit.

- 1 = Breaks enabled on 16-bit address match

- 0 = Breaks disabled

### BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a one to BRKA generates a break interrupt. Clear BRKA by writing a zero to it before exiting the break routine. Reset clears the BRKA bit.

1 = Break address match

0 = No break address match

### 15.4.4 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear status bits while the MCU is in a break state.

### BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

### 15.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power-consumption standby modes.

#### 15.5.1 Wait Mode

If enabled, the break module is active in wait mode. In the break routine, the user can subtract one from the return address on the stack if SBSW is set (see 5.6 Low-Power Modes). Clear the SBSW bit by writing zero to it.

### 15.5.2 Stop Mode

A break interrupt causes exit from stop mode and sets the SBSW bit in the break status register. See 5.7 SIM Registers.

### 16.7 5V Oscillator Characteristics

| Characteristic                                       | Symbol               | Min | Тур            | Max | Unit |

|------------------------------------------------------|----------------------|-----|----------------|-----|------|

| Crystal frequency, XTALCLK                           | f <sub>oscxclk</sub> | —   | 10             | 32  | MHz  |

| RC oscillator frequency, RCCLK                       | f <sub>RCCLK</sub>   | 2   | 10             | 12  | MHz  |

| External clock<br>reference frequency <sup>(1)</sup> | foscxclk             | dc  | _              | 32  | MHz  |

| Crystal load capacitance <sup>(2)</sup>              | CL                   | —   | —              | —   |      |

| Crystal fixed capacitance <sup>(2)</sup>             | C <sub>1</sub>       | —   | $2 \times C_L$ | —   |      |

| Crystal tuning capacitance <sup>(2)</sup>            | C <sub>2</sub>       | —   | $2 \times C_L$ | —   |      |

| Feedback bias resistor                               | R <sub>B</sub>       | —   | 10 MΩ          | —   |      |

| Series resistor <sup>(2), (3)</sup>                  | R <sub>S</sub>       | —   | —              | —   |      |

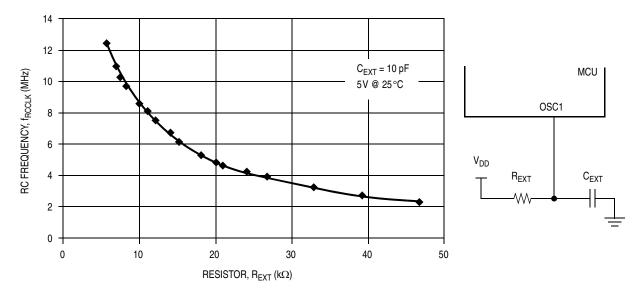

| RC oscillator external R                             | R <sub>EXT</sub>     |     | See Figure 1   | 6-1 |      |

| RC oscillator external C                             | C <sub>EXT</sub>     | —   | 10             | —   | pF   |

### Table 16-6. Oscillator Component Specifications (5V)

1. No more than 10% duty cycle deviation from 50%.

2. Consult crystal vendor data sheet.

3. Not required for high frequency crystals.

Figure 16-1. RC vs. Frequency (5V @25°C)