Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | LED, LVD, POR, PWM                                                       |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                              |

| Data Converters            | A/D 12x8b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908jl3ecdw |

## **General Description**

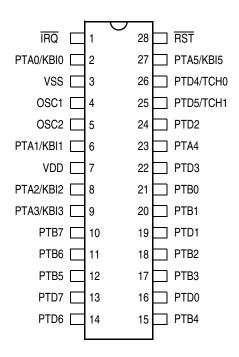

## 1.5 Pin Functions

Description of the pin functions are provided in Table 1-2.

**Table 1-2. Pin Functions**

| PIN NAME              | PIN DESCRIPTION                                                                                                                          | IN/OUT | VOLTAGE LEVEL                       |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------|

| V <sub>DDJL3JL3</sub> | Power supply.                                                                                                                            | In     | 5V or 3V                            |

| V <sub>SS</sub>       | Power supply ground                                                                                                                      | Out    | 0V                                  |

| RST                   | RESET input, active low. With Internal pull-up and Schmitt trigger input.                                                                | Input  | V <sub>DD</sub> to V <sub>TST</sub> |

| ĪRQ                   | External IRQ pin. With software programmable internal pull-up and schmitt trigger input. This pin is also used for mode entry selection. | Input  | V <sub>DD</sub> to V <sub>TST</sub> |

| OSC1                  | X-tal or RC oscillator input.                                                                                                            | In     | Analog                              |

|                       | MC68HC908JL3E/JK3E/JK1E:<br>X-tal oscillator output, this is the inverting OSC1 signal.                                                  | Out    | Analog                              |

| OSC2                  | MC68HRC908JL3E/JK3E/JK1E: Default is RC oscillator clock output, RCCLK. Shared with PTA6/KBI6, with programmable pull-up.                | In/Out | $V_{DD}$                            |

| DTAIO O               | 7-bit general purpose I/O port.                                                                                                          | In/Out | V <sub>DD</sub>                     |

|                       | Shared with 7 keyboard interrupts KBI[0:6].                                                                                              | In     | V <sub>DD</sub>                     |

| PTA[0:6]              | Each pin has programmable internal pull-up device.                                                                                       | In     | V <sub>DD</sub>                     |

|                       | PTA[0:5] have LED direct sink capability                                                                                                 | In     | V <sub>SS</sub>                     |

| PTB[0:7]              | 8-bit general purpose I/O port.                                                                                                          | In/Out | V <sub>DD</sub>                     |

| РТБ[0:7]              | Shared with 8 ADC inputs, ADC[0:7].                                                                                                      | In     | Analog                              |

|                       | 8-bit general purpose I/O port.                                                                                                          | In/Out | V <sub>DD</sub>                     |

|                       | PTD[3:0] shared with 4 ADC inputs, ADC[8:11].                                                                                            | Input  | Analog                              |

| PTD[0:7]              | PTD[4:5] shared with TIM channels, TCH0 and TCH1.                                                                                        | In/Out | V <sub>DD</sub>                     |

|                       | PTD[2:3], PTD[6:7] have LED direct sink capability                                                                                       | In     | V <sub>SS</sub>                     |

|                       | PTD[6:7] can be configured as 25mA open-drain output with pull-up.                                                                       | In/Out | V <sub>DD</sub>                     |

## **NOTE**

On the MC68H(R)C908JK3E/JK1E, the following pins are not available: PTA0, PTA1, PTA2, PTA3, PTA4, PTA5, PTD0, and PTD1.

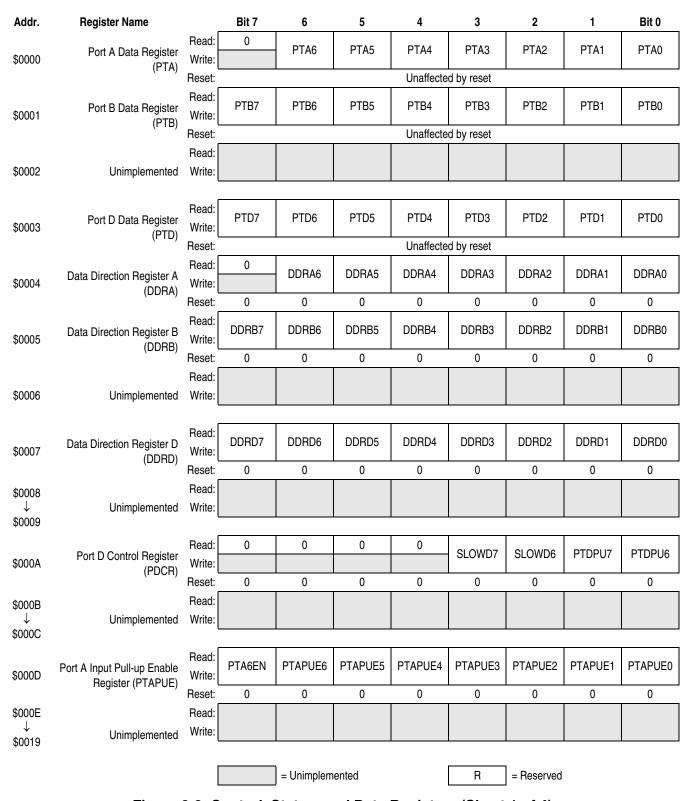

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 4)

Memory

# 2.8 Flash Page Erase Operation

Use the following procedure to erase a page of Flash memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80 or \$XXC0. The 48-byte user interrupt vectors area also forms a page. Any page within the 4K bytes user memory area (\$EC00–\$FBFF) can be erased alone. The 48-byte user interrupt vectors cannot be erased by the page erase operation because of security reasons. Mass erase is required to erase this page.

- 1. Set the ERASE bit and clear the MASS bit in the Flash Control Register.

- 2. Write any data to any Flash address within the page address range desired.

- 3. Wait for a time,  $t_{nvs}$  (10 $\mu$ s).

- 4. Set the HVEN bit.

- 5. Wait for a time t<sub>Frase</sub> (1ms).

- 6. Clear the ERASE bit.

- Wait for a time, t<sub>nvh</sub> (5μs).

- 8. Clear the HVEN bit.

- 9. After time,  $t_{rev}$  (1 $\mu$ s), the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of Flash locations cannot be performed by code being executed from the Flash memory. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

## 2.9 Flash Mass Erase Operation

Use the following procedure to erase the entire Flash memory:

- 1. Set both the ERASE bit and the MASS bit in the Flash Control Register.

- 2. Write any data to any Flash location within the Flash memory address range.

- 3. Wait for a time,  $t_{nvs}$  (10 $\mu$ s).

- Set the HVEN bit.

- 5. Wait for a time t<sub>MErase</sub> (4ms).

- 6. Clear the ERASE bit.

- 7. Wait for a time,  $t_{nvh1}$  (100 $\mu$ s).

- 8. Clear the HVEN bit.

- 9. After time,  $t_{rcv}$  (1 $\mu$ s), the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of Flash locations cannot be performed by code being executed from the Flash memory. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

# Chapter 4 Central Processor Unit (CPU)

#### 4.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

#### 4.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

# 4.3 CPU Registers

Figure 4-1 shows the five CPU registers. CPU registers are not part of the memory map.

# Table 4-1. Instruction Set Summary (Sheet 2 of 6)

| Source                                                                                                | Operation                                         | Description                                                                                                                                                                                                                                                                                                                                                                          |   |   | Effect on CCR |   |   |   |                                                                                              |                                              | Operand                                                              | es                              |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---------------|---|---|---|----------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|---------------------------------|

| Form                                                                                                  | Operation                                         | Bescription                                                                                                                                                                                                                                                                                                                                                                          | ٧ | Н | I             | N | Z | С | Add                                                                                          | Opcode                                       | Ope                                                                  | Cycles                          |

| BHS rel                                                                                               | Branch if Higher or Same (Same as BCC)            | $PC \leftarrow (PC) + 2 + rel? (C) = 0$                                                                                                                                                                                                                                                                                                                                              | - | - | -             | - | ı | - | REL                                                                                          | 24                                           | rr                                                                   | 3                               |

| BIH rel                                                                                               | Branch if IRQ Pin High                            | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 1$                                                                                                                                                                                                                                                                                                                                  |   |   | -             | - | - | - | REL                                                                                          | 2F                                           | rr                                                                   | 3                               |

| BIL rel                                                                                               | Branch if IRQ Pin Low                             | PC ← (PC) + 2 + rel? <del>IRQ</del> = 0 -                                                                                                                                                                                                                                                                                                                                            |   |   | _             | - | - | _ | REL                                                                                          | 2E                                           | rr                                                                   | 3                               |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT,X<br>BIT opr,SP<br>BIT opr,SP         | Bit Test                                          | (A) & (M)                                                                                                                                                                                                                                                                                                                                                                            | 0 | _ | ı             | 1 | ‡ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9ED5     |                                                                      | 2 3 4 4 3 2 4 5                 |

| BLE opr                                                                                               | Branch if Less Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (Z) \mid (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                            | _ | - | ı             | _ | ı | _ | REL                                                                                          | 93                                           | rr                                                                   | 3                               |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                     | $PC \leftarrow (PC) + 2 + rel? (C) = 1$                                                                                                                                                                                                                                                                                                                                              | _ | - | _             | - | - | _ | REL                                                                                          | 25                                           | rr                                                                   | 3                               |

| BLS rel                                                                                               | Branch if Lower or Same                           | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                                                                     | L | - | L             | - | - | - | REL                                                                                          | 23                                           | rr                                                                   | 3                               |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                                     | - | - | -             | - | - | _ | REL                                                                                          | 91                                           | rr                                                                   | 3                               |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                    | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                                                              | _ | - | _             | - | _ | _ | REL                                                                                          | 2C                                           | rr                                                                   | 3                               |

| BMI rel                                                                                               | Branch if Minus                                   | PC ← (PC) + 2 + rel? (N) = 1                                                                                                                                                                                                                                                                                                                                                         | - | - | -             | - | - | - | REL                                                                                          | 2B                                           | rr                                                                   | 3                               |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                      | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                                                                                                                                                                                                                                                                                                                                 | - | - | -             | - | - | - | REL                                                                                          | 2D                                           | rr                                                                   | 3                               |

| BNE rel                                                                                               | Branch if Not Equal                               | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                                                              | - | - | -             | - | - | - | REL                                                                                          | 26                                           | rr                                                                   | 3                               |

| BPL rel                                                                                               | Branch if Plus                                    | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                                                              | _ | _ | _             | - | - | _ | REL                                                                                          | 2A                                           | rr                                                                   | 3                               |

| BRA rel                                                                                               | Branch Always                                     | PC ← (PC) + 2 + <i>rel</i>                                                                                                                                                                                                                                                                                                                                                           | - | - | -             | - | - | - | REL                                                                                          | 20                                           | rr                                                                   | 3                               |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                 | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                                                                | _ | _ | _             | _ | - | ‡ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                        |

| BRN rel                                                                                               | Branch Never                                      | PC ← (PC) + 2                                                                                                                                                                                                                                                                                                                                                                        | _ | - | _             | _ | _ | _ | REL                                                                                          | 21                                           | rr                                                                   | 3                               |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                                                                | _ | _ | -             | _ | - | ‡ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5 5 5 5 5 5 5 5                 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                             | Mn ← 1                                                                                                                                                                                                                                                                                                                                                                               | _ | _ |               | _ | - | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C       | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                         | 4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BSR rel                                                                                               | Branch to Subroutine                              | $ \begin{array}{c} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array} $                                                                                                                                                                                                         | _ | _ | _             | _ | _ | _ | REL                                                                                          | AD                                           | rr                                                                   | 4                               |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                       | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel \; ? \; (A) - (M) = \$00 \\ \end{array}$ | _ | _ | -             | - | - | - | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 71                                           | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6      |

| CLC                                                                                                   | Clear Carry Bit                                   | C ← 0                                                                                                                                                                                                                                                                                                                                                                                | Ŀ | - | Ŀ             | Ŀ |   | 0 | INH                                                                                          | 98                                           |                                                                      | 1                               |

| CLI                                                                                                   | Clear Interrupt Mask                              | I ← 0                                                                                                                                                                                                                                                                                                                                                                                | - | - | 0             | _ | - | - | INH                                                                                          | 9A                                           |                                                                      | 2                               |

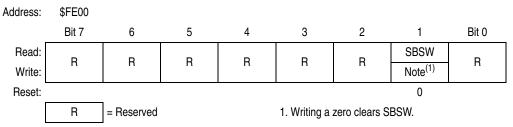

## 5.7.3 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 5-22. Break Flag Control Register (BFCR)

## **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

# Chapter 7 Monitor ROM (MON)

#### 7.1 Introduction

This section describes the monitor ROM (MON) and the monitor mode entry methods. The monitor ROM allows complete testing of the MCU through a single-wire interface with a host computer. This mode is also used for programming and erasing of Flash memory in the MCU. Monitor mode entry can be achieved without use of the higher test voltage, V<sub>TST</sub>, as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

#### 7.2 Features

Features of the monitor ROM include the following:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between monitor ROM and host computer

- Standard mark/space non-return-to-zero (NRZ) communication with host computer

- Execution of code in RAM or Flash

- Flash memory security feature<sup>(1)</sup>

- Flash memory programming interface

- 960 bytes monitor ROM code size

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage, V<sub>TST</sub>, is applied to IRQ

# 7.3 Functional Description

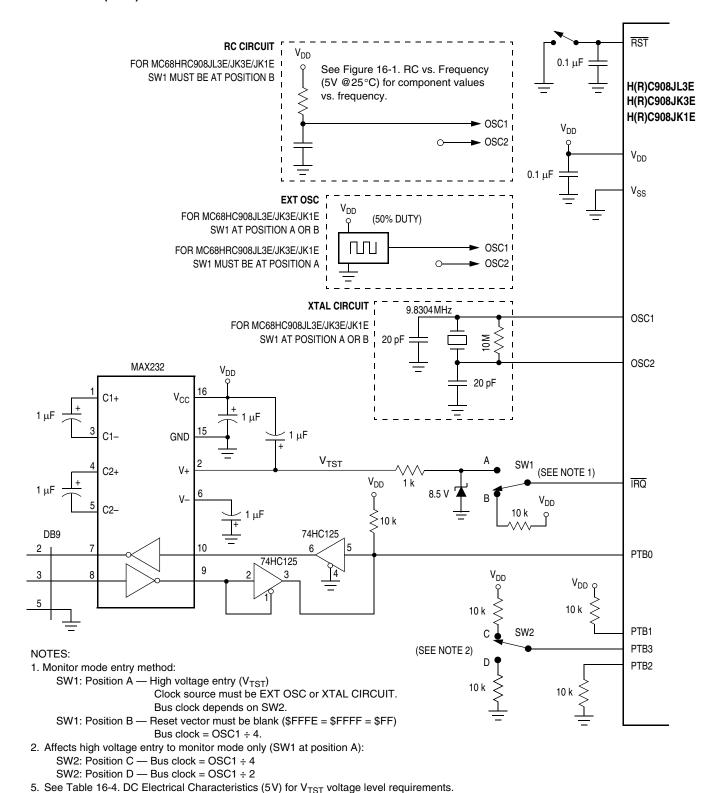

The monitor ROM receives and executes commands from a host computer. Figure 7-1 shows a example circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute host-computer code in RAM while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTB0 pin. A level-shifting and multiplexing interface is required between PTB0 and the host computer. PTB0 is used in a wired-OR configuration and requires a pull-up resistor.

MC68HC908JL3E Family Data Sheet, Rev. 4

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the Flash difficult for unauthorized users.

#### Monitor ROM (MON)

Figure 7-1. Monitor Mode Circuit

MC68HC908JL3E Family Data Sheet, Rev. 4

**Timer Interface Module (TIM)**

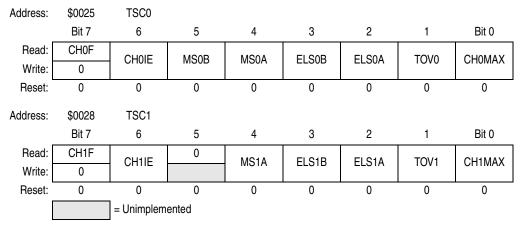

## 8.9.4 TIM Channel Status and Control Registers (TSC0:TSC1)

Each of the TIM channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- · Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 8-7. TIM Channel Status and Control Registers (TSC0:TSC1)

#### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

When TIM CPU interrupt requests are enabled (CHxIE=1), clear CHxF by reading the TIM channel x status and control register with CHxF set and then writing a zero to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing zero to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a one to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

#### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

**Keyboard Interrupt Module (KBI)**

## 12.4 Functional Description

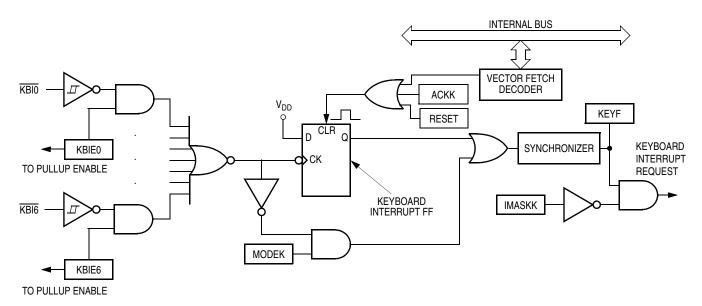

Figure 12-2. Keyboard Interrupt Block Diagram

Writing to the KBIE6–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin in port A also enables its internal pull-up device irrespective of PTAPUEx bits in the port A input pull-up enable register (see 10.2.3 Port A Input Pull-up Enable Register (PTAPUE)). A logic 0 applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

- If the keyboard interrupt is falling edge- and low level-sensitive, an interrupt request is present as long as any keyboard pin is low.

If the MODEK bit is set, the keyboard interrupt pins are both falling edge- and low level-sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register KBSCR. The ACKK bit is useful in applications that poll the keyboard interrupt pins and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt pins. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt pins to logic 1 As long as any enabled keyboard interrupt pin is at 0, the keyboard interrupt remains set.

MC68HC908JL3E Family Data Sheet, Rev. 4

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge-sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt pin stays at 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

To determine the logic level on a keyboard interrupt pin, disable the pull-up device, use the data direction register to configure the pin as an input and then read the data register.

#### NOTE

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

## 12.4.1 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pull-up to reach a logic 1. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- 1. Configure the keyboard pins as outputs by setting the appropriate DDRA bits in the data direction register A.

- 2. Write 1s to the appropriate port A data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

MC68HC908JL3E Family Data Sheet, Rev. 4

# 12.5 Keyboard Interrupt Registers

Two registers control the operation of the keyboard interrupt module:

- Keyboard status and control register

- Keyboard interrupt enable register

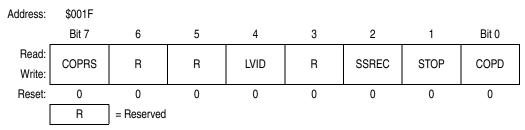

## 13.3.7 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register 1.

Figure 13-2. Configuration Register 1 (CONFIG1)

#### **COPRS** — **COP** Rate Select Bit

COPRS selects the COP timeout period. Reset clears COPRS.

- 1 = COP timeout period is 8176 × 20SCOUT cycles

- 0 = COP timeout period is 262,128 × 20SCOUT cycles

#### COPD — COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

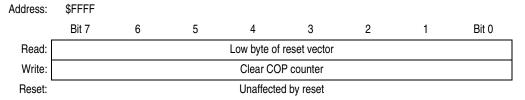

# 13.4 COP Control Register

The COP control register is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 13-3. COP Control Register (COPCTL)

# 13.5 Interrupts

The COP does not generate CPU interrupt requests.

## 13.6 Monitor Mode

The COP is disabled in monitor mode when  $V_{TST}$  is present on the  $\overline{IRQ}$  pin or on the  $\overline{RST}$  pin.

## 13.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

MC68HC908JL3E Family Data Sheet, Rev. 4

#### **Break Module (BREAK)**

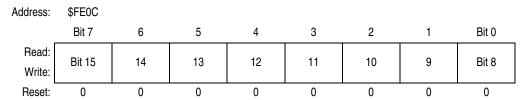

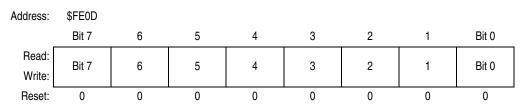

## 15.4.2 Break Address Registers

The break address registers contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

Figure 15-4. Break Address Register High (BRKH)

Figure 15-5. Break Address Register Low (BRKL)

## 15.4.3 Break Status Register

The break status register contains a flag to indicate that a break caused an exit from wait mode.

Figure 15-6. Break Status Register (BSR)

## SBSW — SIM Break Stop/Wait

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

- 1 = Wait mode was exited by break interrupt

- 0 = Wait mode was not exited by break interrupt

## **Electrical Specifications**

# 16.8 3V DC Electrical Characteristics

Table 16-7. DC Electrical Characteristics (3 V)

| Characteristic <sup>(1)</sup>                                                                                                                                                                             | Symbol                               | Min                   | Typ <sup>(2)</sup>     | Max                  | Unit                     |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|------------------------|----------------------|--------------------------|--|--|--|

| Output high voltage (I <sub>LOAD</sub> = -1.0mA)<br>PTA0-PTA6, PTB0-PTB7, PTD0-PTD7                                                                                                                       | V <sub>OH</sub>                      | V <sub>DD</sub> -0.4  | _                      | _                    | V                        |  |  |  |

| Output low voltage (I <sub>LOAD</sub> = 0.8mA)<br>PTA6, PTB0-PTB7, PTD0, PTD1, PTD4, PTD5                                                                                                                 | V <sub>OL</sub>                      | _                     | _                      | 0.4                  | ٧                        |  |  |  |

| Output low voltage (I <sub>LOAD</sub> = 20 mA)<br>PTD6, PTD7                                                                                                                                              | V <sub>OL</sub>                      | _                     | _                      | 0.5                  | ٧                        |  |  |  |

| LED drives (V <sub>OL</sub> = 1.8V)<br>PTA0–PTA5, PTD2, PTD3, PTD6, PTD7                                                                                                                                  | I <sub>OL</sub>                      | 3                     | 6                      | 10                   | mA                       |  |  |  |

| Input high voltage PTA0-PTA6, PTB0-PTB7, PTD0-PTD7, RST, IRQ, OSC1                                                                                                                                        | V <sub>IH</sub>                      | 0.7 × V <sub>DD</sub> | _                      | V <sub>DD</sub>      | V                        |  |  |  |

| Input low voltage PTA0-PTA6, PTB0-PTB7, PTD0-PTD7, RST, IRQ, OSC1                                                                                                                                         | V <sub>IL</sub>                      | V <sub>SS</sub>       | _                      | $0.3 \times V_{DD}$  | V                        |  |  |  |

| $V_{DD}$ supply current, $f_{OP}$ = 2MHz Run <sup>(3)</sup> MC68HC908JL3E/JK3E/JK1E  MC68HRC908JL3E/JK3E/JK1E  Wait <sup>(4)</sup> MC68HC908JL3E/JK3E/JK1E  MC68HRC908JL3E/JK3E/JK1E  Stop <sup>(5)</sup> | I <sub>DD</sub>                      | _<br>_<br>_<br>_      | 3<br>1.5<br>1.5<br>0.2 | 3.5<br>2<br>2<br>0.3 | mA<br>mA<br>mA           |  |  |  |

| (-40°C to 85°C)<br>MC68HC908JL3E/JK3E/JK1E<br>MC68HRC908JL3E/JK3E/JK1E                                                                                                                                    |                                      |                       | 1                      | 5<br>5               | μ <b>Α</b><br>μ <b>Α</b> |  |  |  |

| Digital I/O ports Hi-Z leakage current                                                                                                                                                                    | I <sub>IL</sub>                      | _                     | _                      | ± 10                 | μА                       |  |  |  |

| Input current                                                                                                                                                                                             | I <sub>IN</sub>                      | _                     | _                      | ± 1                  | μА                       |  |  |  |

| Capacitance Ports (as input or output)                                                                                                                                                                    | C <sub>OUT</sub><br>C <sub>IN</sub>  | _<br>_                | _                      | 12<br>8              | pF                       |  |  |  |

| POR rearm voltage <sup>(6)</sup>                                                                                                                                                                          | V <sub>POR</sub>                     | 0                     | _                      | 100                  | mV                       |  |  |  |

| POR rise time ramp rate <sup>(7)</sup>                                                                                                                                                                    | R <sub>POR</sub>                     | 0.035                 | _                      | _                    | V/ms                     |  |  |  |

| Monitor mode entry voltage                                                                                                                                                                                | V <sub>TST</sub>                     | $1.5 \times V_{DD}$   | _                      | 8.5                  | V                        |  |  |  |

| Pullup resistors <sup>(8)</sup> PTD6, PTD7 RST, IRQ, PTA0–PTA6                                                                                                                                            | R <sub>PU1</sub><br>R <sub>PU2</sub> | 1.8<br>16             | 3.3<br>26              | 4.8<br>36            | kΩ<br>kΩ                 |  |  |  |

Table continued on next page

#### NOTES:

POSITIONAL TOLERANCE OF LEADS, SHALL BE WITHIN 0.25 MM (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

3 DIMENSION DOES NOT INCLUDE MOLD FLASH.

- 4. 710-01 OBSOLETE, NEW STD 710-02.

- 5. CONTROLLING DIMENSION: INCH

|      | IN                               | СН    | MILL      | IMETER      |      | INCH      |         | MIL        | LIMETER |

|------|----------------------------------|-------|-----------|-------------|------|-----------|---------|------------|---------|

| DIM  | MIN                              | MAX   | MIN       | MAX         | DIM  | MIN       | MAX     | MIN        | MAX     |

| А    | 1.435                            | 1.465 | 36.45     | 37.21       |      |           |         |            |         |

| В    | 0.540                            | 0.560 | 13.72     | 14.22       |      |           |         |            |         |

| С    | 0.155                            | 0.200 | 3.94      | 5.08        |      |           |         |            |         |

| D    | 0.014                            | 0.022 | 0.36      | 0.56        |      |           |         |            |         |

| F    | 0.040                            | 0.060 | 1.02      | 1.52        |      |           |         |            |         |

| G    | 0.100                            | BSC   | 2.54      | 4 BSC       |      |           |         |            |         |

| Н    | 0.065                            | 0.085 | 1.65      | 2.16        |      |           |         |            |         |

| J    | 0.008                            | 0.015 | 0.20      | 0.38        |      |           |         |            |         |

| K    | 0.115                            | 0.135 | 2.92      | 3.43        |      |           |         |            |         |

| L    | 0.600                            | BSC   | 15.2      | 4 BSC       |      |           |         |            |         |

| М    | 0 *                              | 15°   | 0*        | 15 <b>°</b> |      |           |         |            |         |

| N    | 0.020                            | 0.040 | 0.51      | 1.02        |      |           |         |            |         |

|      |                                  |       |           |             |      |           |         |            |         |

| © FI | <br>  REESCALE SEM<br>  ALL RIGH | INC.  | MECHANICA | L OUT       | LINE | PRINT VER | SION NO | T TO SCALE |         |

|      |                                  |       |           |             |      |           |         |            |         |

TITLE:

28 LD PDIP

28 LD PDIP

28 LD PDIP

CASE NUMBER: 710-02

STANDARD: NON-JEDEC

**Ordering Information**

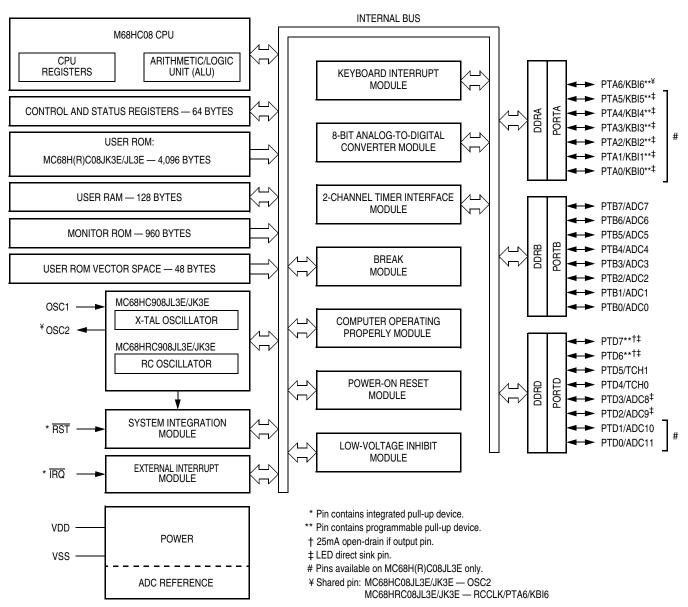

Figure B-1. MC68H(R)C08JL3E/JK3E Block Diagram

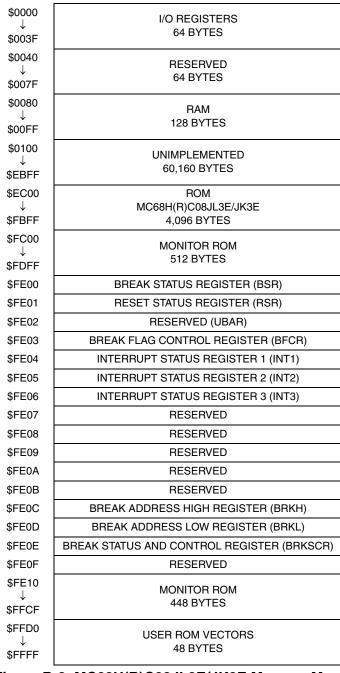

# **B.3 Memory Map**

The MC68H(R)C08JL3E/JK3E has 4,096 bytes of user ROM from \$EC00 to \$FBFF, and 48 bytes of user ROM vectors from \$FFD0 to \$FFFF. On the MC68H(R)C908JL3E/JK3E, these memory locations are Flash memory.

Figure B-2 shows the memory map of the MC68H(R)C08JL3E/JK3E.

Figure B-2. MC68H(R)C08JL3E/JK3E Memory Map

# **B.7 Electrical Specifications**

Electrical specifications for the MC68H(R)C908JL3E/JK3E apply to the MC68H(R)C08JL3E/JK3E, except for the parameters indicated below.

#### **B.7.1 DC Electrical Characteristics**

Table B-2. DC Electrical Characteristics (5V)

| Characteristic <sup>(1)</sup>                                                | Symbol                               | Min       | Typ <sup>(2)</sup> | Max       | Unit     |

|------------------------------------------------------------------------------|--------------------------------------|-----------|--------------------|-----------|----------|

| V <sub>DD</sub> supply current, f <sub>OP</sub> = 4MHz<br>Run <sup>(3)</sup> |                                      |           |                    |           |          |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 9                  | 11        | mA       |

| MC68HRC08JL3E/JK3E<br>Wait <sup>(4)</sup>                                    |                                      | _         | 4.3                | 5         | mA       |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 5.5                | 6.5       | mA       |

| MC68HRC08JL3E/JK3E<br>Stop <sup>(5)</sup><br>(–40°C to 85°C)                 | I <sub>DD</sub>                      | _         | 0.8                | 1.5       | mA       |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 1.8                | 5         | μΑ       |

| MC68HRC08JL3E/JK3E<br>(-40°C to 125°C)                                       |                                      | _         | 1.8                | 5         | μA       |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 5                  | 10        | μΑ       |

| MC68HRC08JL3E/JK3E                                                           |                                      | _         | 5                  | 10        | μА       |

| Pullup resistors <sup>(6)</sup> PTD6, PTD7 RST, IRQ, PTA0–PTA6               | R <sub>PU1</sub><br>R <sub>PU2</sub> | 1.8<br>16 | 4.3<br>31          | 4.8<br>36 | kΩ<br>kΩ |

<sup>1.</sup>  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

<sup>2.</sup> Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

<sup>3.</sup> Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{QP} = 4MHz$ ). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

<sup>4.</sup> Wait I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 4MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

5. Stop I<sub>DD</sub> measured with OSC1 grounded; no port pins sourcing current. LVI is disabled.

<sup>6.</sup>  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0 \text{ V}$ .

## MC68HC908KL3E

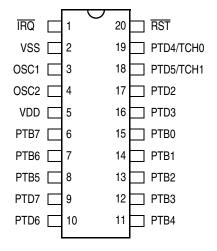

Figure C-2. 28-Pin PDIP/SOIC Pin Assignment

| Pins not available on 20-pin packages |      |  |  |  |  |

|---------------------------------------|------|--|--|--|--|

| PTA0/KBI0                             | PTD0 |  |  |  |  |

| PTA1/KBI1                             | PTD1 |  |  |  |  |

| PTA2/KBI2                             |      |  |  |  |  |

| PTA3/KBI3                             |      |  |  |  |  |

| PTA4/KBI4                             |      |  |  |  |  |

| PTA5/KBI5                             |      |  |  |  |  |

| Internal pads are unconnected.        |      |  |  |  |  |

## MC68HC908KK3E

Figure C-3. 20-Pin PDIP/SOIC Pin Assignment