# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LED, LVD, POR, PWM                                                    |

| Number of I/O              | 14                                                                    |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                           |

| Data Converters            | A/D 12x8b                                                             |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 20-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908jk1emdwe |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

General Description

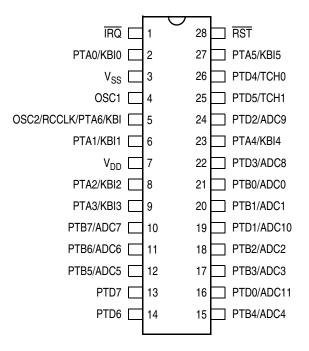

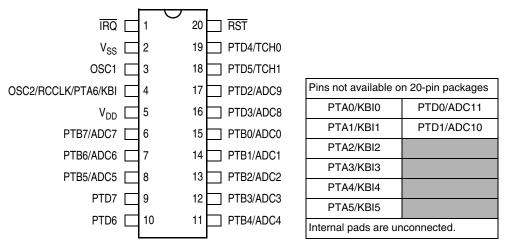

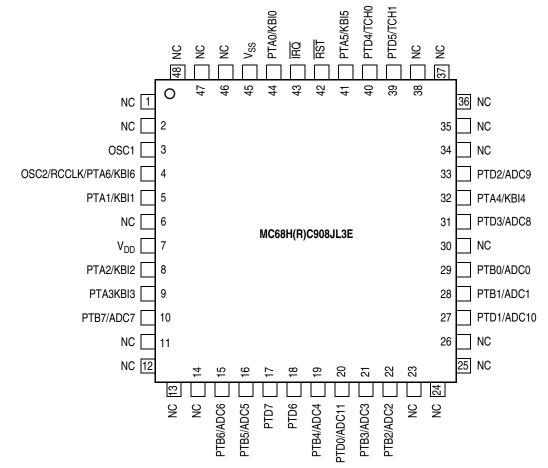

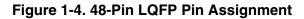

### 1.4 Pin Assignments

### MC68H(R)C908JL3E

### MC68H(R)C908JK3E/JK1E

#### **Pin Assignments**

NC: No connection

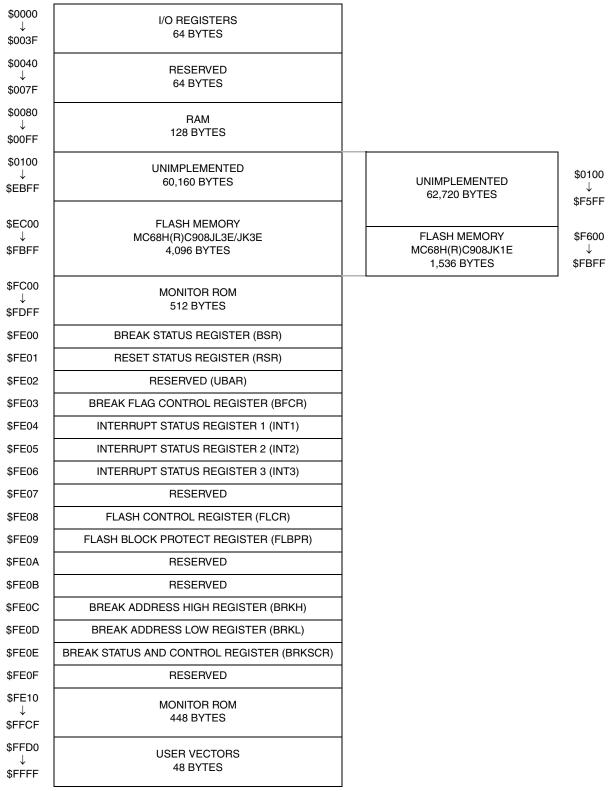

Memory

Figure 2-1. Memory Map

#### Memory

| Addr.                       | Register Name                           |                 | Bit 7 | 6     | 5       | 4            | 3            | 2      | 1     | Bit 0 |

|-----------------------------|-----------------------------------------|-----------------|-------|-------|---------|--------------|--------------|--------|-------|-------|

|                             |                                         | Read:           | 0     | IF5   | IF4     | IF3          | 0            | IF1    | 0     | 0     |

| \$FE04                      | Interrupt Status Register 1<br>(INT1)   | Write:          | R     | R     | R       | R            | R            | R      | R     | R     |

|                             | ((((((((((((((((((((((((((((((((((((((( | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

|                             |                                         | Read:           | IF14  | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE05                      | Interrupt Status Register 2<br>(INT2)   | Write:          | R     | R     | R       | R            | R            | R      | R     | R     |

|                             | (1112)                                  | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| Interrupt Status Deviator 9 | Read:                                   | 0               | 0     | 0     | 0       | 0            | 0            | 0      | IF15  |       |

| \$FE06                      | Interrupt Status Register 3<br>(INT3)   | Write:          | R     | R     | R       | R            | R            | R      | R     | R     |

| (IN 13)                     | Reset:                                  | 0               | 0     | 0     | 0       | 0            | 0            | 0      | 0     |       |

| \$FE07                      | Reserved                                | Read:<br>Write: | R     | R     | R       | R            | R            | R      | R     | R     |

|                             |                                         | Read:           | 0     | 0     | 0       | 0            |              |        |       |       |

| \$FE08                      | Flash Control Register                  | Write:          | 0     | 0     | 0       | 0            | HVEN         | MASS   | ERASE | PGM   |

| (FLCR)                      | Reset:                                  | 0               | 0     | 0     | 0       | 0            | 0            | 0      | 0     |       |

|                             |                                         | Read:           | 0     | 0     | 0       | U            | 0            | 0      | 0     | 0     |

| \$FE09                      | Flash Block Protect<br>Register (FLBPR) | Write:          | BPR7  | BPR6  | BPR5    | BPR4         | BPR3         | BPR2   | BPR1  | BPR0  |

|                             |                                         | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE0A<br>↓<br>\$FE0B       | Reserved                                | Read:<br>Write: | R     | R     | R       | R            | R            | R      | R     | R     |

| φΓΕΟΒ                       |                                         | f               |       |       |         | 1            |              |        |       |       |

| \$FE0C                      | Break Address High<br>Register (BRKH)   | Read:<br>Write: | Bit15 | Bit14 | Bit13   | Bit12        | Bit11        | Bit10  | Bit9  | Bit8  |

|                             |                                         | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE0D                      | Break Address Low                       | Read:<br>Write: | Bit7  | Bit6  | Bit5    | Bit4         | Bit3         | Bit2   | Bit1  | Bit0  |

|                             | Register (BRKL)                         | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

|                             |                                         | Read:           |       |       | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE0E                      | Break Status and Control                | Write:          | BRKE  | BRKA  |         |              |              |        |       |       |

| Register (BRKSCR)           | Reset:                                  | 0               | 0     | 0     | 0       | 0            | 0            | 0      | 0     |       |

|                             |                                         | Read:           |       |       |         | Low byte of  | reset vector |        |       |       |

| \$FFFF                      | COP Control Register                    | Write:          |       |       | Writing | g clears COP | counter (any | value) |       |       |

| SFFFF (COPCTI               |                                         | Reset:          |       | 1     |         | -            | d by reset   |        |       |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 4)

R

= Reserved

= Unimplemented

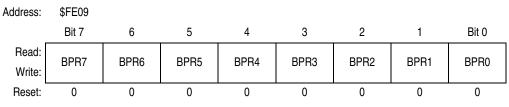

### 2.12 Flash Block Protect Register

The Flash Block Protect Register is implemented as an 8-bit I/O register. The value in this register determines the starting address of the protected range within the Flash memory.

Figure 2-6. Flash Block Protect Register (FLBPR)

#### BPR[7:0] — Flash Block Protect Register Bit 7 to Bit 0

BPR[7:1] represent bits [12:6] of a 16-bit memory address. Bits [15:13] are 1's and bits [5:0] are 0's.

Start address of Flash block protect

|   |   |   |  |    |     |              | • |   |   |   |   |   |   |

|---|---|---|--|----|-----|--------------|---|---|---|---|---|---|---|

| 1 | 1 | 1 |  |    |     |              |   | 0 | 0 | 0 | 0 | 0 | 0 |

|   |   |   |  | BP | R[7 | <b>'</b> :1] |   |   |   |   |   |   |   |

16-bit memory address

BPR0 is used only for BPR[7:0] = \$FF, for no block protection.

The resultant 16-bit address is used for specifying the start address of the Flash memory for block protection. The Flash is protected from this start address to the end of Flash memory, at \$FFFF. With this mechanism, the protect start address can be XX00, XX40, XX80, or XXC0 (at page boundaries — 64 bytes) within the Flash memory.

Examples of protect start address:

| BPR[7:0]                             | Start of Address of Protect Range         |

|--------------------------------------|-------------------------------------------|

| \$00–\$60                            | The entire Flash memory is protected.     |

| \$62 or \$63<br>( <b>0110 001x</b> ) | \$EC40 (111 <b>0 1100 01</b> 00 0000)     |

| \$64 or \$65<br>( <b>0110 010x</b> ) | \$EC80 (111 <b>0 1100 10</b> 00 0000)     |

| \$68 or \$69<br>( <b>0110 100x</b> ) | \$ED00 (111 <b>0 1101 00</b> 00 0000)     |

| and so on                            |                                           |

| \$DE or \$DF<br>( <b>1101 111x</b> ) | \$FBC0 (111 <b>1 1011 11</b> 00 0000)     |

| \$FE<br>(1111 1110)                  | \$FFC0 (111 <b>1 1111 11</b> 00 0000)     |

| \$FF                                 | The entire Flash memory is not protected. |

Note:

The end address of the protected range is always \$FFFF.

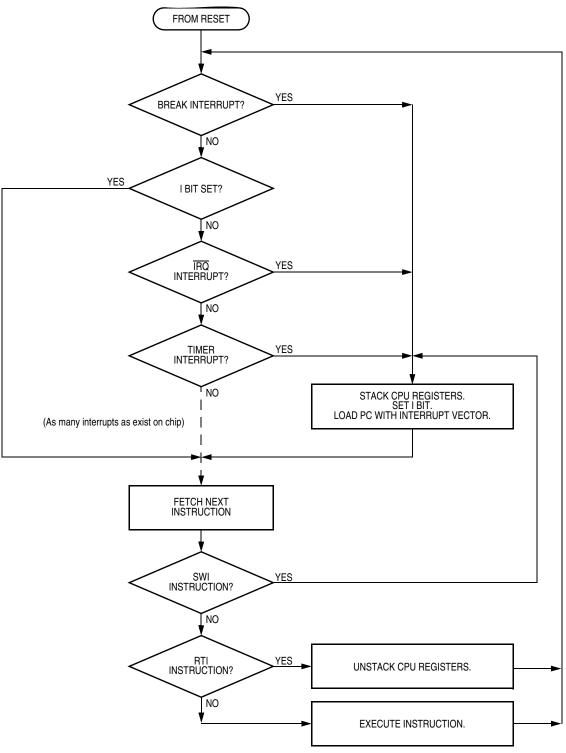

#### System Integration Module (SIM)

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared).

Figure 5-8. Interrupt Processing

Monitor ROM (MON)

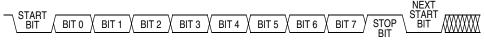

### 7.3.3 Data Format

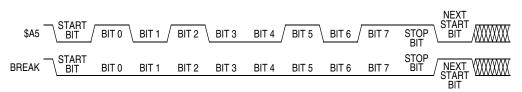

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. (See Figure 7-3 and Figure 7-4.)

Figure 7-3. Monitor Data Format

Figure 7-4. Sample Monitor Waveforms

The data transmit and receive rate can be anywhere from 4800 baud to 28.8k-baud. Transmit and receive baud rates must be identical.

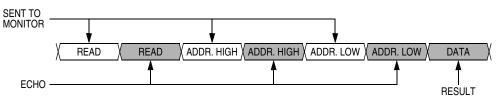

### 7.3.4 Echoing

As shown in Figure 7-5, the monitor ROM immediately echoes each received byte back to the PTB0 pin for error checking.

Figure 7-5. Read Transaction

Any result of a command appears after the echo of the last byte of the command.

### 7.3.5 Break Signal

A start bit followed by nine low bits is a break signal. (See **Figure 7-6**.) When the monitor receives a break signal, it drives the PTB0 pin high for the duration of two bits before echoing the break signal.

Figure 7-6. Break Transaction

### 8.4.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use the following initialization procedure:

- 1. In the TIM status and control register (TSC):

- a. Stop the TIM counter by setting the TIM stop bit, TSTOP.

- b. Reset the TIM counter and prescaler by setting the TIM reset bit, TRST.

- 2. In the TIM counter modulo registers (TMODH:TMODL), write the value for the required PWM period.

- 3. In the TIM channel x registers (TCHxH:TCHxL), write the value for the required pulse width.

- 4. In TIM channel x status and control register (TSCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB:MSxA. (See Table 8-3.)

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. (See Table 8-3.)

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM status control register (TSC), clear the TIM stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSC0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. (See 8.9.4 TIM Channel Status and Control Registers (TSC0:TSC1).)

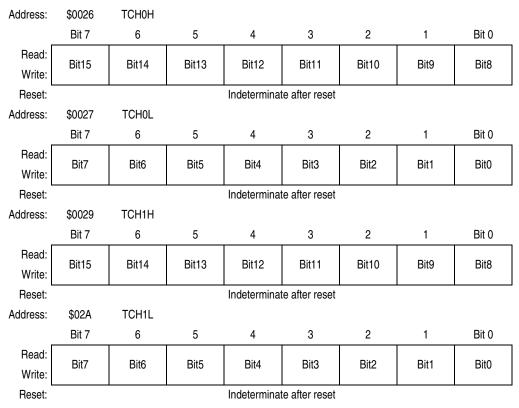

### 8.9.5 TIM Channel Registers (TCH0H/L:TCH1H/L)

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Figure 8-9. TIM Channel Registers (TCH0H/L:TCH1H/L)

Timer Interface Module (TIM)

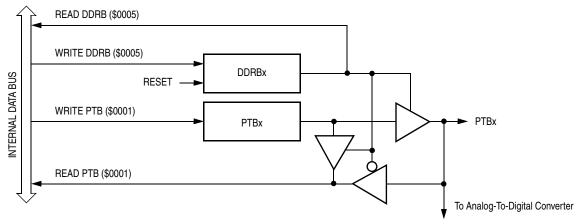

Figure 10-8. Port B I/O Circuit

When DDRBx is a 1, reading address \$0001 reads the PTBx data latch. When DDRBx is a 0, reading address \$0001 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 10-3 summarizes the operation of the port B pins.

| Table | 10-3. | Port  | <b>B</b> Pin | <b>Functions</b> |

|-------|-------|-------|--------------|------------------|

| TUDIC | 10 0. | 1 011 |              | 1 unouono        |

| DDRB Bit | PTB Bit          | I/O Pin Mode               | Accesses to DDRB | Accesses to PTB |                         |  |

|----------|------------------|----------------------------|------------------|-----------------|-------------------------|--|

|          | FIDDI            |                            | Read/Write       | Read            | Write                   |  |

| 0        | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRB[7:0]        | Pin             | PTB[7:0] <sup>(3)</sup> |  |

| 1        | Х                | Output                     | DDRB[7:0]        | Pin             | PTB[7:0]                |  |

1. X = don't care.

2. Hi-Z = high impedance.

3. Writing affects data register, but does not affect the input.

Input/Output (I/O) Ports

### 10.4 Port D

Port D is an 8-bit special function port that shares two of its pins with timer interface module, (see Chapter 8 Timer Interface Module (TIM)) and shares four of its pins with analog-to-digital converter module (see Chapter 9 Analog-to-Digital Converter (ADC)). PTD6 and PTD7 each has high current drive (25mA sink) and programmable pull-up. PTD2, PTD3, PTD6 and PTD7 each has LED driving (sink) capability.

#### **NOTE** PTD0–PTD1 are available on MC68H(R)C908JL3E only.

### 10.4.1 Port D Data Register (PTD)

The port D data register contains a data latch for each of the eight port D pins.

| Address:              | \$0003                   |                          |      |      |               |               |       |       |  |

|-----------------------|--------------------------|--------------------------|------|------|---------------|---------------|-------|-------|--|

|                       | Bit 7                    | 6                        | 5    | 4    | 3             | 2             | 1     | Bit 0 |  |

| Read:<br>Write:       | PTD7                     | PTD6                     | PTD5 | PTD4 | PTD3          | PTD2          | PTD1  | PTD0  |  |

| Reset:                |                          | Unaffected by reset      |      |      |               |               |       |       |  |

| Additional Functions: | LED<br>(Sink)            | LED<br>(Sink)            |      |      | LED<br>(Sink) | LED<br>(Sink) |       |       |  |

|                       |                          |                          |      |      | ADC8          | ADC9          | ADC10 | ADC11 |  |

|                       |                          |                          | TCH1 | TCH0 |               |               |       |       |  |

|                       | 25mA sink<br>(Slow Edge) | 25mA sink<br>(Slow Edge) |      |      |               |               |       |       |  |

|                       | 5k pull-up               | 5k pull-up               |      |      |               |               |       |       |  |

|                       |                          | 1                        |      |      |               |               |       |       |  |

= Unimplemented

Figure 10-9. Port D Data Register (PTD)

#### PTD[7:0] — Port D Data Bits

These read/write bits are software programmable. Data direction of each port D pin is under the control of the corresponding bit in data direction register D. Reset has no effect on port D data.

#### ADC[11:8] — ADC channels 11 to 8

ADC[11:8] are pins used for the input channels to the analog-to-digital converter module. The channel select bits, ADCH[4:0], in the ADC status and control register define which port pin will be used as an ADC input and overrides any control from the port I/O logic. See Chapter 9 Analog-to-Digital Converter (ADC).

#### TCH[1:0] — Timer Channel I/O

The TCH1 and TCH0 pins are the TIM input capture/output compare pins. The edge/level select bits, ELSxB:ELSxA, determine whether the PTD4/TCH0 and PTD5/TCH1 pins are timer channel I/O pins or general-purpose I/O pins. See Chapter 8 Timer Interface Module (TIM).

**Keyboard Interrupt Module (KBI)**

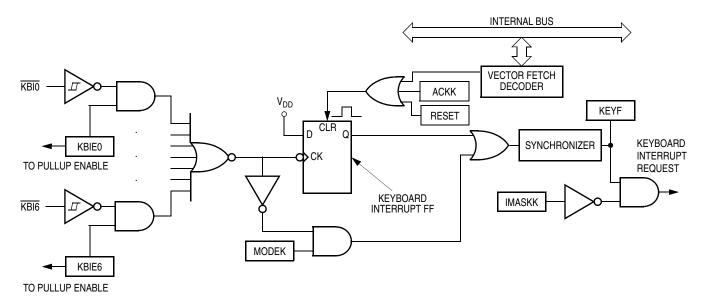

### 12.4 Functional Description

Writing to the KBIE6–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin in port A also enables its internal pull-up device irrespective of PTAPUEx bits in the port A input pull-up enable register (see 10.2.3 Port A Input Pull-up Enable Register (PTAPUE)). A logic 0 applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

- If the keyboard interrupt is falling edge- and low level-sensitive, an interrupt request is present as long as any keyboard pin is low.

If the MODEK bit is set, the keyboard interrupt pins are both falling edge- and low level-sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register KBSCR. The ACKK bit is useful in applications that poll the keyboard interrupt pins and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt pins. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt pins to logic 1 As long as any enabled keyboard interrupt pin is at 0, the keyboard interrupt remains set.

# Chapter 13 Computer Operating Properly (COP)

### 13.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG1 register.

### **13.2 Functional Description**

Figure 13-1 shows the structure of the COP module.

NOTE: See Chapter 5 System Integration Module (SIM) for more details.

#### **Computer Operating Properly (COP)**

### 13.7.1 Wait Mode

The COP continues to operate during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter in a CPU interrupt routine.

### 13.7.2 Stop Mode

Stop mode turns off the 2OSCOUT input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

### 13.8 COP Module During Break Mode

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

Low Voltage Inhibit (LVI)

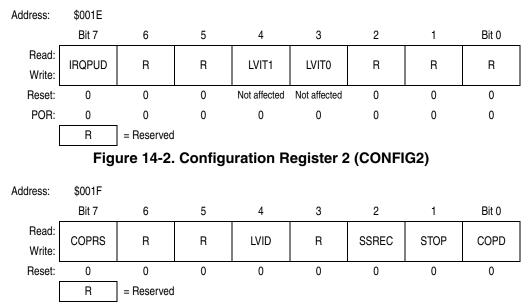

### 14.4 LVI Control Register (CONFIG2/CONFIG1)

The LVI module is controlled by three bits in the configuration registers, CONFIG1 and CONFIG2.

#### Figure 14-3. Configuration Register 1 (CONFIG1)

### LVID — Low Voltage Inhibit Disable Bit

1 = Low voltage inhibit disabled

0 = Low voltage inhibit enabled

#### LVIT1, LVIT0 — LVI Trip Voltage Selection

These two bits determine at which level of  $V_{DD}$  the LVI module will come into action. LVIT1 and LVIT0 are cleared by a Power-On Reset only.

| LVIT1 | LVIT0 | Trip Voltage <sup>(1)</sup> | Comments                          |

|-------|-------|-----------------------------|-----------------------------------|

| 0     | 0     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 0     | 1     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 1     | 0     | V <sub>LVR5</sub> (4.0V)    | For V <sub>DD</sub> =5V operation |

| 1     | 1     | Reserved                    |                                   |

1. See Chapter 16 Electrical Specifications for full parameters.

### 14.5 Low-Power Modes

The STOP and WAIT instructions put the MCU in low-power-consumption standby modes.

### 14.5.1 Wait Mode

The LVI module, when enabled, will continue to operate in WAIT Mode.

### 14.5.2 Stop Mode

The LVI module, when enabled, will continue to operate in STOP Mode.

**Electrical Specifications**

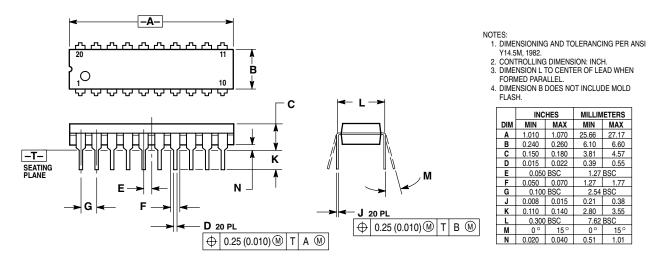

## Chapter 17 Mechanical Specifications

### **17.1 Introduction**

This section gives the dimensions for:

- 20-pin plastic dual in-line package (case #738)

- 20-pin small outline integrated circuit package (case #751D)

- 28-pin plastic dual in-line package (case #710)

- 28-pin small outline integrated circuit package (case #751F)

- 48-pin low-profile quad flat pack (case #932)

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Sales Office.

### 17.2 Package Dimensions

Refer to the following pages for detailed package dimensions.

20-Pin PDIP (Case #738)

### **B.7 Electrical Specifications**

Electrical specifications for the MC68H(R)C908JL3E/JK3E apply to the MC68H(R)C08JL3E/JK3E, except for the parameters indicated below.

### **B.7.1 DC Electrical Characteristics**

| Characteristic <sup>(1)</sup>                                                  | Symbol                               | Min       | Typ <sup>(2)</sup> | Max       | Unit     |  |  |

|--------------------------------------------------------------------------------|--------------------------------------|-----------|--------------------|-----------|----------|--|--|

| V <sub>DD</sub> supply current, f <sub>OP</sub> = 4MHz<br>Run <sup>(3)</sup>   |                                      |           |                    |           |          |  |  |

| MC68HC08JL3E/JK3E                                                              |                                      | _         | 9                  | 11        | mA       |  |  |

| MC68HRC08JL3E/JK3E<br>Wait <sup>(4)</sup>                                      |                                      | —         | 4.3                | 5         | mA       |  |  |

| MC68HC08JL3E/JK3E                                                              |                                      | _         | 5.5                | 6.5       | mA       |  |  |

| MC68HRC08JL3E/JK3E<br>Stop <sup>(5)</sup>                                      | I <sub>DD</sub>                      | —         | 0.8                | 1.5       | mA       |  |  |

| (–40°C to 85°C)<br>MC68HC08JL3E/JK3E<br>MC68HRC08JL3E/JK3E<br>(–40°C to 125°C) |                                      |           | 1.8<br>1.8         | 5<br>5    | μΑ<br>μΑ |  |  |

| MC68HC08JL3E/JK3E                                                              |                                      | _         | 5                  | 10        | μA       |  |  |

| MC68HRC08JL3E/JK3E                                                             |                                      | —         | 5                  | 10        | μA       |  |  |

| Pullup resistors <sup>(6)</sup><br>PTD6, PTD7<br>RST, IRQ, PTA0–PTA6           | R <sub>PU1</sub><br>R <sub>PU2</sub> | 1.8<br>16 | 4.3<br>31          | 4.8<br>36 | kΩ<br>kΩ |  |  |

#### Table B-2. DC Electrical Characteristics (5V)

1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

3. Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{OP} = 4MHz$ ). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

4. Wait  $I_{DD}$  measured using external square wave clock source ( $f_{OP} = 4$ MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait  $I_{DD}$ . 5. Stop  $I_{DD}$  measured with OSC1 grounded; no port pins sourcing current. LVI is disabled.

6.  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0$  V.

### C.4 Reserved Registers

The following registers are reserved location on the MC68HC908KL3E/KK3E.

| Addr.  | Register Name   |                 | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|--------|-----------------|-----------------|-------|---|---|---|---|---|---|-------|

| \$003C | \$003C Reserved | Read:<br>Write: | R     | R | R | R | R | R | R | R     |

|        |                 | Reset:          |       |   |   |   |   |   |   |       |

| \$003D | Reserved        | Read:<br>Write: | R     | R | R | R | R | R | R | R     |

| 4000D  | neserveu        | Reset:          |       |   |   |   |   |   |   |       |

| \$003E | Reserved        | Read:<br>Write: | R     | R | R | R | R | R | R | R     |

|        |                 | Reset:          |       | 1 |   |   |   |   |   |       |

### Figure C-4. Reserved Registers

### C.5 Reserved Vectors

The following vectors are reserved interrupt vectors on the MC68HC908KL3E/KK3E.

#### Table C-2. Reserved Vectors

| Vector Priority | INT Flag | Address | Vector   |

|-----------------|----------|---------|----------|

| _               | IF15     | \$FFDE  | Reserved |

|                 | 1115     | \$FFDF  | Reserved |

### C.6 Order Numbers

#### Table C-3. MC68HC908KL3E/KK3E Order Numbers

| MC order number  | Package     | Operating<br>Temperature | Operating<br>V <sub>DD</sub> | OSC  | Flash Memory |

|------------------|-------------|--------------------------|------------------------------|------|--------------|

| MC68HC908KL3ECP  | 28-pin PDIP |                          |                              |      |              |

| MC68HC908KL3ECDW | 28-pin SOIC | −40 to +85 °C            | 3V, 5V                       | XTAL | 4096 Bytes   |

| MC68HC908KK3ECP  | 20-pin PDIP | -40 10 +85 C             |                              |      |              |

| MC68HC908KK3ECDW | 20-pin SOIC |                          |                              |      |              |