# E·XFL

## NXP USA Inc. - MC908JK3ECDWER Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 × 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                            |

| Data Converters            | A/D 12x8b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908jk3ecdwer |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

\_\_\_\_\_

| Chapter 1 General Description                |     |

|----------------------------------------------|-----|

| Chapter 2 Memory                             |     |

| Chapter 3 Configuration Registers (CONFIG)   |     |

| Chapter 4 Central Processor Unit (CPU)       |     |

| Chapter 5 System Integration Module (SIM)    |     |

| Chapter 6 Oscillator (OSC)                   | 67  |

| Chapter 7 Monitor ROM (MON)                  | 71  |

| Chapter 8 Timer Interface Module (TIM)       |     |

| Chapter 9 Analog-to-Digital Converter (ADC)  |     |

| Chapter 10 Input/Output (I/O) Ports          | 103 |

| Chapter 11 External Interrupt (IRQ)          | 113 |

| Chapter 12 Keyboard Interrupt Module (KBI)   | 117 |

| Chapter 13 Computer Operating Properly (COP) | 123 |

| Chapter 14 Low Voltage Inhibit (LVI)         | 127 |

| Chapter 15 Break Module (BREAK)              | 129 |

| Chapter 16 Electrical Specifications         | 135 |

| Chapter 17 Mechanical Specifications         | 147 |

| Chapter 18 Ordering Information              | 157 |

| Appendix A MC68HLC908JL3E/JK3E/JK1E          | 159 |

| Appendix B MC68H(R)C08JL3E/JK3E              | 165 |

| Appendix C MC68HC908KL3E/KK3E                |     |

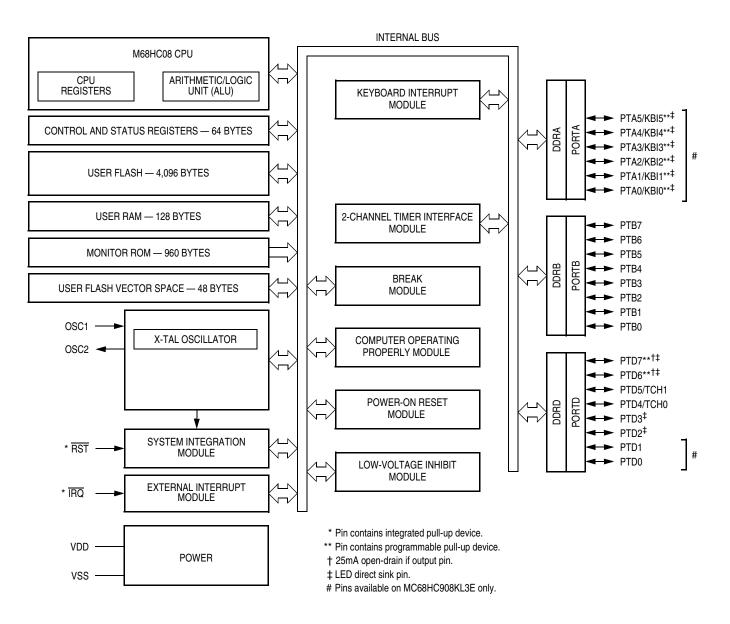

# Chapter 1 General Description

# 1.1 Introduction

The MC68H(R)C908JL3E is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is based on the customer-specified integrated circuit (CSIC) design strategy. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

A list of MC68H(R)C908JL3E device variations is shown in Table 1-1.

| Device<br>Type                      | Operating<br>Voltage | LVI               | ADC      | Oscillator<br>Option | Memory            | Pin<br>Count    | Device         |                   |    |                |

|-------------------------------------|----------------------|-------------------|----------|----------------------|-------------------|-----------------|----------------|-------------------|----|----------------|

|                                     |                      |                   |          |                      | 4,096 bytes Flash | 28              | MC68HC908JL3E  |                   |    |                |

|                                     |                      |                   |          | XTAL                 | 4,090 bytes mash  | 20              | MC68HC908JK3E  |                   |    |                |

| Flash                               | 3V, 5V               | Yes               | Yes      |                      | 1,536 bytes Flash | 20              | MC68HC908JK1E  |                   |    |                |

| FIASI                               | 30, 50               | ies               | 162      |                      | 4,096 bytes Flash | 28              | MC68HRC908JL3E |                   |    |                |

|                                     |                      |                   | RC       | 4,090 bytes mash     | 20                | MC68HRC908JK3E  |                |                   |    |                |

|                                     |                      |                   |          |                      | 1,536 bytes Flash | 20              | MC68HRC908JK1E |                   |    |                |

|                                     |                      | 4,096 bytes Flash | 28       | MC68HLC908JL3E       |                   |                 |                |                   |    |                |

| Low Voltage<br>Flash <sup>(1)</sup> | 2.2 to 5.5V          | No                | Yes XTAL | Yes                  | Yes               | s XTAL          | XTAL           | 4,090 bytes Flash | 20 | MC68HLC908JK3E |

|                                     |                      |                   |          |                      | 1,536 bytes Flash | 20              | MC68HLC908JK1E |                   |    |                |

|                                     |                      | Yes               |          | XTAL                 |                   |                 | VTAI           |                   | 28 | MC68HC08JL3E   |

| DOM(2)                              | 3V, 5V               |                   | Yes      | /es Yes —            |                   | 4 006 bytes BOM | 20             | MC68HC08JK3E      |    |                |

| ROM <sup>(2)</sup>                  | 30, 50               |                   |          |                      | 4,096 bytes ROM   | 28              | MC68HRC08JL3E  |                   |    |                |

|                                     |                      |                   | RC       |                      |                   | 20              | MC68HRC08JK3E  |                   |    |                |

| Flash,                              | 3V, 5V               |                   | XTAL     | 4,096 bytes Flash    | 28                | MC68HC908KL3E   |                |                   |    |                |

| ADC-less <sup>(3)</sup>             | 37,37                | Yes               | No       | A IAL                | 4,090 bytes ridsh | 20              | MC68HC908KK3E  |                   |    |                |

## Table 1-1. Summary of Device Variations

1. Low-voltage Flash devices are documented in Appendix A MC68HLC908JL3E/JK3E/JK1E.

2. ROM devices are documented in Appendix B MC68H(R)C08JL3E/JK3E.

3. Flash, ADC-less devices are documented in Appendix C MC68HC908KL3E/KK3E.

All references to the MC68H(R)C908JL3E in this data book apply equally to the MC68H(R)C908JK3E and MC68H(R)C908JK1E, unless otherwise stated.

#### Memory

| Addr.                 | Register Name                           |                 | Bit 7 | 6     | 5       | 4            | 3            | 2      | 1     | Bit 0 |

|-----------------------|-----------------------------------------|-----------------|-------|-------|---------|--------------|--------------|--------|-------|-------|

|                       |                                         | Read:           | 0     | IF5   | IF4     | IF3          | 0            | IF1    | 0     | 0     |

| \$FE04                | Interrupt Status Register 1<br>(INT1)   | Write:          | R     | R     | R       | R            | R            | R      | R     | R     |

|                       |                                         |                 | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

|                       |                                         | Read:           | IF14  | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE05                | Interrupt Status Register 2<br>(INT2)   | Write:          | R     | R     | R       | R            | R            | R      | R     | R     |

|                       | (1112)                                  | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

|                       |                                         | Read:           | 0     | 0     | 0       | 0            | 0            | 0      | 0     | IF15  |

| \$FE06                | Interrupt Status Register 3<br>(INT3)   | Write:          | R     | R     | R       | R            | R            | R      | R     | R     |

|                       | (1113)                                  | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE07                | Reserved                                | Read:<br>Write: | R     | R     | R       | R            | R            | R      | R     | R     |

|                       |                                         | Read:           | 0     | 0     | 0       | 0            |              |        |       |       |

| \$FE08                | Flash Control Register                  | Write:          | 0     | 0     | 0       | 0            | HVEN         | MASS   | ERASE | PGM   |

| φΓΕυο                 | (FLCR)                                  | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

|                       |                                         | Read:           | 0     | 0     | 0       | U            | 0            | 0      | 0     | 0     |

| \$FE09                | Flash Block Protect<br>Register (FLBPR) | Write:          | BPR7  | BPR6  | BPR5    | BPR4         | BPR3         | BPR2   | BPR1  | BPR0  |

|                       |                                         | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE0A<br>↓<br>\$FE0B | Reserved                                | Read:<br>Write: | R     | R     | R       | R            | R            | R      | R     | R     |

| φΓΕΟΒ                 |                                         | f               |       |       |         | 1            |              |        |       |       |

| \$FE0C                | Break Address High<br>Register (BRKH)   | Read:<br>Write: | Bit15 | Bit14 | Bit13   | Bit12        | Bit11        | Bit10  | Bit9  | Bit8  |

|                       |                                         | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

| \$FE0D                | Break Address Low                       | Read:<br>Write: | Bit7  | Bit6  | Bit5    | Bit4         | Bit3         | Bit2   | Bit1  | Bit0  |

|                       | Register (BRKL)                         | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

|                       |                                         | Read:           |       |       | 0       | 0            | 0            | 0      | 0     | 0     |

| SEENE                 | Break Status and Control                | Write:          | BRKE  | BRKA  |         |              |              |        |       |       |

|                       | Register (BRKSCR)                       | Reset:          | 0     | 0     | 0       | 0            | 0            | 0      | 0     | 0     |

|                       |                                         | Read:           |       |       |         | Low byte of  | reset vector |        |       |       |

| \$FFFF                | COP Control Register                    | Write:          |       |       | Writing | g clears COP | counter (any | value) |       |       |

| SFFFF (COPCTL)        |                                         | Reset:          |       | 1     |         | -            | d by reset   |        |       |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 4)

R

= Reserved

= Unimplemented

| Vector Priority     | INT Flag         | Address               | Vector                                |

|---------------------|------------------|-----------------------|---------------------------------------|

| Lowest              | _                | \$FFD0<br>↓<br>\$FFDD | Not Used                              |

|                     | IF15             | \$FFDE                | ADC Conversion Complete Vector (High) |

|                     | 1613             | \$FFDF                | ADC Conversion Complete Vector (Low)  |

|                     | IF14             | \$FFE0                | Keyboard Vector (High)                |

|                     | 1614             | \$FFE1                | Keyboard Vector (Low)                 |

|                     | IF13<br>↓<br>IF6 | _                     | Not Used                              |

|                     | IF5              | \$FFF2                | TIM Overflow Vector (High)            |

|                     |                  | \$FFF3                | TIM Overflow Vector (Low)             |

|                     | IF4              | \$FFF4                | TIM Channel 1 Vector (High)           |

|                     |                  | \$FFF5                | TIM Channel 1 Vector (Low)            |

|                     | IF3              | \$FFF6                | TIM Channel 0 Vector (High)           |

|                     | 11-3             | \$FFF7                | TIM Channel 0 Vector (Low)            |

|                     | IF2              | —                     | Not Used                              |

|                     | IF1              | \$FFFA                | IRQ Vector (High)                     |

|                     |                  | \$FFFB                | IRQ Vector (Low)                      |

|                     |                  | \$FFFC                | SWI Vector (High)                     |

|                     |                  | \$FFFD                | SWI Vector (Low)                      |

| <b>V</b><br>Highost |                  | \$FFFE                | Reset Vector (High)                   |

| Highest             |                  | \$FFFF                | Reset Vector (Low)                    |

Table 2-1. Vector Addresses

# 2.4 Random-Access Memory (RAM)

Addresses \$0080 through \$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

## NOTE

For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 128 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF, direct addressing mode instructions can access efficiently all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

## NOTE

For M6805 compatibility, the H register is not stacked.

#### MC68HC908JL3E Family Data Sheet, Rev. 4

Memory

# Chapter 3 Configuration Registers (CONFIG)

# 3.1 Introduction

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enables or disables the following options:

- Stop mode recovery time (32 × 20SCOUT cycles or 4096 × 20SCOUT cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS), 8176 × 20SCOUT or 262,128 × 20SCOUT

- Enable LVI circuit

- Select LVI trip voltage

# 3.2 Functional Description

The configuration register is used in the initialization of various options. The configuration register can be written once after each reset. All of the configuration register bits are cleared during reset. Since the various options affect the operation of the MCU it is recommended that this register be written immediately after reset. The configuration register is located at \$001E and \$001F, and may be read at anytime.

**NOTE** The CONFIG registers are one-time writable by the user after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 3-1 and Figure 3-2.

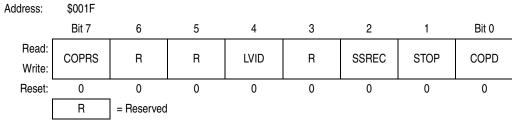

# 3.3 Configuration Register 1 (CONFIG1)

Figure 3-1. Configuration Register 1 (CONFIG1)

## COPRS — COP reset period selection bit

1 = COP reset cycle is  $8176 \times 20$ SCOUT 0 = COP reset cycle is  $262,128 \times 20$ SCOUT

MC68HC908JL3E Family Data Sheet, Rev. 4

# Chapter 4 Central Processor Unit (CPU)

# 4.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

# 4.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

# 4.3 CPU Registers

Figure 4-1 shows the five CPU registers. CPU registers are not part of the memory map.

#### System Integration Module (SIM)

Figure 5-1. SIM Block Diagram

| Addr.         | Register Name                         | _               | Bit 7           | 6   | 5   | 4    | 3          | 2      | 1            | Bit 0 |

|---------------|---------------------------------------|-----------------|-----------------|-----|-----|------|------------|--------|--------------|-------|

| \$FE00        | Break Status Register<br>(BSR)        | Read:<br>Write: | R               | R   | R   | R    | R          | R      | SBSW<br>NOTE | R     |

|               | (DON)                                 | Reset:          | 0               | 0   | 0   | 0    | 0          | 0      | 0            | 0     |

| Note: Writing | a 0 clears SBSW.                      |                 |                 |     |     |      |            |        |              |       |

|               | Reset Status Register                 | Read:           | POR             | PIN | COP | ILOP | ILAD       | MODRST | LVI          | 0     |

| \$FE01        | (RSR)                                 | Write:          |                 |     |     |      |            |        |              |       |

|               | (non)                                 | POR:            | 1               | 0   | 0   | 0    | 0          | 0      | 0            | 0     |

| \$FE02        | Reserved                              | Read:<br>Write: | R               | R   | R   | R    | R          | R      | R            | R     |

|               |                                       | Reset:          |                 | -   |     |      | -          |        |              |       |

| \$FE03        | Break Flag Control<br>Register (BFCR) | Read:<br>Write: | BCFE            | R   | R   | R    | R          | R      | R            | R     |

|               |                                       | Reset:          | 0               |     |     |      | -          |        |              |       |

|               |                                       |                 | = Unimplemented |     |     | R    | = Reserved |        |              |       |

Figure 5-2. SIM I/O Register Summary

MC68HC908JL3E Family Data Sheet, Rev. 4

System Integration Module (SIM)

# 5.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE-\$FFFF (\$FEFE-\$FEFF in Monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 5.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the reset status register (RSR). (See 5.7 SIM Registers.)

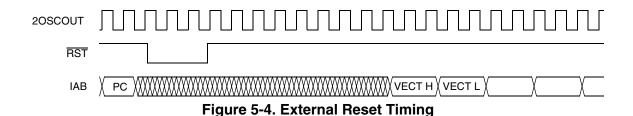

# 5.3.1 External Pin Reset

The  $\overline{\text{RST}}$  pin circuits include an internal pull-up device. Pulling the asynchronous  $\overline{\text{RST}}$  pin low halts all processing. The PIN bit of the reset status register (RSR) is set as long as  $\overline{\text{RST}}$  is held low for a minimum of 67 2OSCOUT cycles, assuming that the POR was not the source of the reset. See Table 5-2 for details. Figure 5-4 shows the relative timing.

| Reset Type | Number of Cycles Required to Set PIN |

|------------|--------------------------------------|

| POR        | 4163 (4096 + 64 + 3)                 |

| All others | 67 (64 + 3)                          |

# 5.3.2 Active Resets from Internal Sources

All internal reset sources actively pull the RST pin low for 32 2OSCOUT cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (Figure 5-5). An internal reset can be caused by an illegal address, illegal opcode, COP time-out, or POR. (See Figure 5-6.) Note that for POR resets, the SIM cycles through 4096 2OSCOUT cycles during which the SIM forces the RST pin low. The internal reset signal then follows the sequence from the falling edge of RST shown in Figure 5-5.

# Chapter 7 Monitor ROM (MON)

# 7.1 Introduction

This section describes the monitor ROM (MON) and the monitor mode entry methods. The monitor ROM allows complete testing of the MCU through a single-wire interface with a host computer. This mode is also used for programming and erasing of Flash memory in the MCU. Monitor mode entry can be achieved without use of the higher test voltage,  $V_{TST}$ , as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

# 7.2 Features

Features of the monitor ROM include the following:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between monitor ROM and host computer

- Standard mark/space non-return-to-zero (NRZ) communication with host computer

- Execution of code in RAM or Flash

- Flash memory security feature<sup>(1)</sup>

- Flash memory programming interface

- 960 bytes monitor ROM code size

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage, V<sub>TST</sub>, is applied to IRQ

# 7.3 Functional Description

The monitor ROM receives and executes commands from a host computer. Figure 7-1 shows a example circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute host-computer code in RAM while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTB0 pin. A level-shifting and multiplexing interface is required between PTB0 and the host computer. PTB0 is used in a wired-OR configuration and requires a pull-up resistor.

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the Flash difficult for unauthorized users.

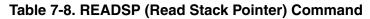

| Description        | Reads stack pointer                               |

|--------------------|---------------------------------------------------|

| Operand            | None                                              |

| Data Returned      | Returns stack pointer in high byte:low byte order |

| Opcode             | \$0C                                              |

| Command Sequence   |                                                   |

| SENT TO<br>MONITOR | READSP     SP HIGH     SP LOW       RESULT        |

## Table 7-9. RUN (Run User Program) Command

| Description        | Executes RTI instruction |

|--------------------|--------------------------|

| Operand            | None                     |

| Data Returned      | None                     |

| Opcode             | \$28                     |

| Command Sequence   |                          |

| SENT TO<br>MONITOR |                          |

| ECHO ———           |                          |

# 7.4 Security

A security feature discourages unauthorized reading of Flash locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6–\$FFFD. Locations \$FFF6–\$FFFD contain user-defined data.

#### NOTE

Do not leave locations \$FFF6-\$FFFD blank. For security reasons, program locations \$FFF6-\$FFFD even if they are not used for vectors.

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTB0. If the received bytes match those at locations \$FFF6-\$FFFD, the host bypasses the security feature and can read all Flash locations and execute code from Flash. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. (See Figure 7-7.)

#### Analog-to-Digital Converter (ADC)

## 9.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

# 9.6 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D.

# 9.6.1 ADC Voltage In (ADCVIN)

ADCVIN is the input voltage signal from one of the 12 ADC channels to the ADC module.

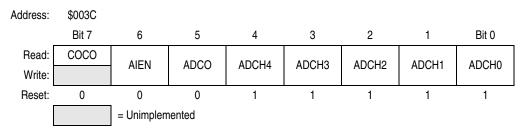

# 9.7 I/O Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

# 9.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register.

#### Figure 9-3. ADC Status and Control Register (ADSCR)

## COCO — Conversions Complete Bit

When the AIEN bit is a 0, the COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the ADC status and control register is written or whenever the ADC data register is read. Reset clears this bit.

1 = Conversion completed (AIEN = 0)

0 =Conversion not completed (AIEN = 0)

When the AIEN bit is a 1 (CPU interrupt enabled), the COCO is a read-only bit, and will always be 0 when read.

## AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register is read or the status/control register is written. Reset clears the AIEN bit.

1 = ADC interrupt enabled

0 = ADC interrupt disabled

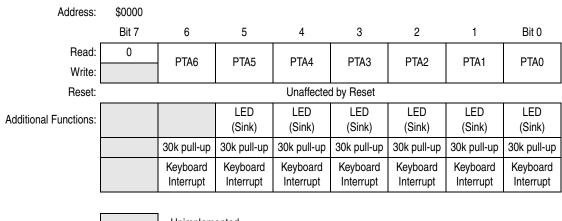

# 10.2 Port A

Port A is an 7-bit special function port that shares all seven of its pins with the keyboard interrupt (KBI) module (see Chapter 12 Keyboard Interrupt Module (KBI)). Each port A pin also has software configurable pull-up device if the corresponding port pin is configured as input port. PTA0 to PTA5 has direct LED drive capability.

## NOTE

PTA0–PTA5 pins are available on MC68H(R)C908JL3E only. PTA6 pin is available on MC68HRC908JL3E/JK3E/JK1E only.

# 10.2.1 Port A Data Register (PTA)

The port A data register (PTA) contains a data latch for each of the seven port A pins.

= Unimplemented

## Figure 10-2. Port A Data Register (PTA)

#### PTA[6:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

## KBI[6:0] — Port A Keyboard Interrupts

The keyboard interrupt enable bits, KBIE[6:0], in the keyboard interrupt control register (KBIER) enable the port A pins as external interrupt pins, (see Chapter 12 Keyboard Interrupt Module (KBI)).

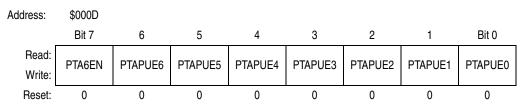

# 10.2.3 Port A Input Pull-up Enable Register (PTAPUE)

The port A input pull-up enable register (PTAPUE) contains a software configurable pull-up device for each of the seven port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx be configured as input. Each pull-up device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

Figure 10-5. Port A Input Pull-up Enable Register (PTAPUE)

## PTA6EN — Enable PTA6 on OSC2

This read/write bit configures the OSC2 pin function when RC oscillator option is selected. This bit has no effect for X-tal oscillator option.

- 1 = OSC2 pin configured for PTA6 I/O, and has all the interrupt and pull-up functions

- 0 = OSC2 pin outputs the RC oscillator clock (RCCLK)

## PTAPUE[6:0] — Port A Input Pull-up Enable Bits

These read/write bits are software programmable to enable pull-up devices on port A pins

- 1 = Corresponding port A pin configured to have internal pull-up if its DDRA bit is set to 0

- 0 = Pull-up device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

Table 10-2 summarizes the operation of the port A pins.

| PTAPUE Bit | DDRA | DDRA             | DDRA                                  | DDRA       | DDRA     | DDRA                    | DDRA | DDRA | DDRA | DDRA | DDRA | DDRA | DDRA | PTA Bit | I/O Pin Mode | Accesses to DDRA | Access | es to PTA |

|------------|------|------------------|---------------------------------------|------------|----------|-------------------------|------|------|------|------|------|------|------|---------|--------------|------------------|--------|-----------|

| FIAFUE DI  | Bit  |                  |                                       | Read/Write | Read     | Write                   |      |      |      |      |      |      |      |         |              |                  |        |           |

| 1          | 0    | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRA[6:0]  | Pin      | PTA[6:0] <sup>(3)</sup> |      |      |      |      |      |      |      |         |              |                  |        |           |

| 0          | 0    | х                | Input, Hi-Z <sup>(4)</sup>            | DDRA[6:0]  | Pin      | PTA[6:0] <sup>(3)</sup> |      |      |      |      |      |      |      |         |              |                  |        |           |

| Х          | 1    | х                | Output                                | DDRA[6:0]  | PTA[6:0] | PTA[6:0]                |      |      |      |      |      |      |      |         |              |                  |        |           |

Table 10-2. Port A Pin Functions

1. X = Don't care.

2. I/O pin pulled to  $V_{\text{DD}}$  by internal pull-up.

3. Writing affects data register, but does not affect input.

4. Hi-Z = High Impedance.

Keyboard Interrupt Module (KBI)

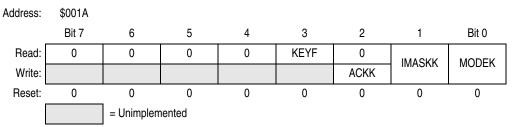

## 12.5.1 Keyboard Status and Control Register

- Flags keyboard interrupt requests

- Acknowledges keyboard interrupt requests

- Masks keyboard interrupt requests

- Controls keyboard interrupt triggering sensitivity

## Figure 12-3. Keyboard Status and Control Register (KBSCR)

## KEYF — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port-A. Reset clears the KEYF bit.

- 1 = Keyboard interrupt pending

- 0 = No keyboard interrupt pending

## ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard interrupt request on port-A. ACKK always reads as 0. Reset clears ACKK.

## IMASKK— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port-A. Reset clears the IMASKK bit.

- 1 = Keyboard interrupt requests masked

- 0 = Keyboard interrupt requests not masked

## MODEK — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins on port-A. Reset clears MODEK.

- 1 = Keyboard interrupt requests on falling edges and low levels

- 0 = Keyboard interrupt requests on falling edges only

#### Table 16-7. DC Electrical Characteristics (3V) (Continued)

| Characteristic <sup>(1)</sup> | Symbol            | Min | Typ <sup>(2)</sup> | Мах  | Unit |

|-------------------------------|-------------------|-----|--------------------|------|------|

| LVI reset voltage             | V <sub>LVR3</sub> | 2.0 | 2.4                | 2.69 | V    |

1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

3. Run (operating) I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 2MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs. CL = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run I<sub>DD</sub>. Measured with all modules enabled.

4. Wait I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 2MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait  $I_{DD}$ . 5. Stop  $I_{DD}$  measured with OSC1 grounded; no port pins sourcing current. LVI is disabled.

6. Maximum is highest voltage that POR is guaranteed.

7. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum V<sub>DD</sub> is reached.

8.  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0$  V.

# 16.9 3V Control Timing

## Table 16-8. Control Timing (3V)

| Characteristic <sup>(1)</sup>               | Symbol           | Min | Max | Unit |

|---------------------------------------------|------------------|-----|-----|------|

| Internal operating frequency <sup>(2)</sup> |                  | —   | 4   | MHz  |

| RST input pulse width low <sup>(3)</sup>    | t <sub>IRL</sub> | 1.5 | _   | μs   |

1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ ; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless otherwise noted.

2. Some modules may require a minimum frequency greater than dc for proper operation; see appropriate table for this information.

3. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

# A.5.3 Control Timing

| Characteristic <sup>(1)</sup>               | Symbol           | Min | Max | Unit |

|---------------------------------------------|------------------|-----|-----|------|

| Internal operating frequency <sup>(2)</sup> | f <sub>OP</sub>  | _   | 2   | MHz  |

| RST input pulse width low <sup>(3)</sup>    | t <sub>IRL</sub> | 1.5 | _   | μS   |

#### Table A-3. Control Timing

1.  $V_{DD}$  = 2.2 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ ; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless otherwise noted. 2. Some modules may require a minimum frequency greater than dc for proper operation; see appropriate table for this infor-

mation.

3. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

# A.5.4 Oscillator Characteristics

#### **Table A-4. Oscillator Component Specifications**

| Characteristic                                    | Symbol         | Min | Тур            | Max | Unit |  |

|---------------------------------------------------|----------------|-----|----------------|-----|------|--|

| Crystal frequency, XTALCLK                        | foscxclk       | —   | —              | 8   | MHz  |  |

| External clock reference frequency <sup>(1)</sup> | foscxclk       | dc  | _              | 8   | MHz  |  |

| Crystal load capacitance <sup>(2)</sup>           | CL             | —   | —              | —   |      |  |

| Crystal fixed capacitance <sup>(2)</sup>          | C <sub>1</sub> | —   | $2 \times C_L$ | —   |      |  |

| Crystal tuning capacitance <sup>(2)</sup>         | C <sub>2</sub> | —   | $2 \times C_L$ | —   |      |  |

| Feedback bias resistor                            | R <sub>B</sub> | —   | 10 MΩ          | —   |      |  |

| Series resistor <sup>(2), (3)</sup>               | R <sub>S</sub> | —   | —              | —   |      |  |

1. No more than 10% duty cycle deviation from 50%

2. Consult crystal vendor data sheet

3. Not Required for high frequency crystals

# A.5.5 ADC Characteristics

| Characteristic                                | Symbol            | Min                          | Max                          | Unit                    | Comments                                                         |

|-----------------------------------------------|-------------------|------------------------------|------------------------------|-------------------------|------------------------------------------------------------------|

| Supply voltage                                | V <sub>DDAD</sub> | 2.2<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                       |                                                                  |

| Input voltages                                | V <sub>ADIN</sub> | V <sub>SS</sub>              | V <sub>DD</sub>              | V                       |                                                                  |

| Resolution                                    | B <sub>AD</sub>   | 8                            | 8                            | Bits                    |                                                                  |

| Absolute accuracy                             | A <sub>AD</sub>   | $\pm 0.5$                    | ±2                           | LSB                     | Includes quantization                                            |

| ADC internal clock                            | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                     | t <sub>AIC</sub> = 1/f <sub>ADIC</sub> , tested<br>only at 1 MHz |

| Conversion range                              | R <sub>AD</sub>   | V <sub>SS</sub>              | V <sub>DD</sub>              | V                       |                                                                  |

| Power-up time                                 | t <sub>ADPU</sub> | 14                           | —                            | t <sub>AIC</sub> cycles |                                                                  |

| Conversion time                               | t <sub>ADC</sub>  | 14                           | 15                           | t <sub>AIC</sub> cycles |                                                                  |

| Sample time <sup>(1)</sup>                    | t <sub>ADS</sub>  | 5                            | —                            | t <sub>AIC</sub> cycles |                                                                  |

| Zero input reading <sup>(2)</sup>             | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                     | $V_{IN} = V_{SS}$                                                |

| Full-scale reading <sup>(3)</sup>             | F <sub>ADI</sub>  | FE                           | FF                           | Hex                     | $V_{IN} = V_{DD}$                                                |

| Input capacitance                             | C <sub>ADI</sub>  | _                            | (20) 8                       | pF                      | Not tested                                                       |

| Input leakage <sup>(3)</sup><br>Port B/port D | —                 | _                            | ± 1                          | μΑ                      |                                                                  |

## Table A-5. ADC Characteristics

1. Source impedances greater than 10 k $\Omega$  adversely affect internal RC charging time during input sampling.

2. Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

3. The external system error caused by input leakage current is approximately equal to the product of R source and input current.

Figure C-1. MC68HC908KL3E/KK3E Block Diagram

# C.4 Reserved Registers

The following registers are reserved location on the MC68HC908KL3E/KK3E.

| Addr.           | Register Name   |                 | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|-----------------|-----------------|-----------------|-------|---|---|---|---|---|---|-------|

| \$003C Reserved | Read:<br>Write: | R               | R     | R | R | R | R | R | R |       |

|                 |                 | Reset:          |       |   |   |   |   |   |   |       |

| \$003D          | Reserved        | Read:<br>Write: | R     | R | R | R | R | R | R | R     |

|                 |                 | Reset:          |       |   |   |   |   |   |   |       |

| \$003E          | Reserved        | Read:<br>Write: | R     | R | R | R | R | R | R | R     |

|                 |                 | Reset:          |       |   |   |   |   |   |   |       |

## Figure C-4. Reserved Registers

# C.5 Reserved Vectors

The following vectors are reserved interrupt vectors on the MC68HC908KL3E/KK3E.

## Table C-2. Reserved Vectors

| Vector Priority | INT Flag | Address | Vector   |

|-----------------|----------|---------|----------|

| _               | IF15     | \$FFDE  | Reserved |

|                 | 1115     | \$FFDF  | Reserved |

# C.6 Order Numbers

## Table C-3. MC68HC908KL3E/KK3E Order Numbers

| MC order number  | Package     | Operating<br>Temperature | Operating<br>V <sub>DD</sub> | OSC  | Flash Memory |  |

|------------------|-------------|--------------------------|------------------------------|------|--------------|--|

| MC68HC908KL3ECP  | 28-pin PDIP |                          |                              |      |              |  |

| MC68HC908KL3ECDW | 28-pin SOIC | −40 to +85 °C            | 3V, 5V                       | XTAL | 4096 Bytes   |  |

| MC68HC908KK3ECP  | 20-pin PDIP |                          |                              |      |              |  |

| MC68HC908KK3ECDW | 20-pin SOIC |                          |                              |      |              |  |