Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>.</b>                   |                                                             |

|----------------------------|-------------------------------------------------------------|

| Details                    |                                                             |

| Product Status             | Active                                                      |

| Core Processor             | HC08                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | -                                                           |

| Peripherals                | LED, LVD, POR, PWM                                          |

| Number of I/O              | 23                                                          |

| Program Memory Size        | 4KB (4K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 128 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                 |

| Data Converters            | A/D 12x8b                                                   |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                              |

| Supplier Device Package    | 28-SOIC                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908jl3ecdwer |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

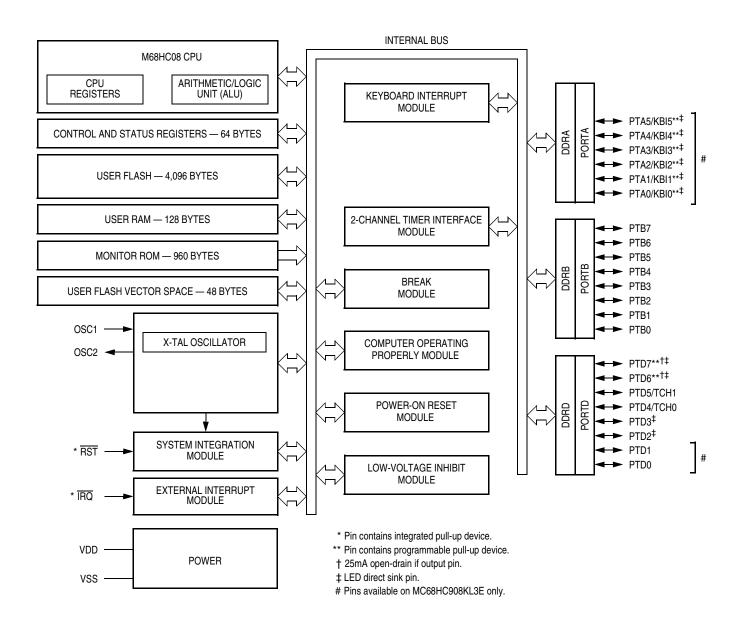

### Appendix C MC68HC908KL3E/KK3E

| C.1 | Introduction       | 175 |

|-----|--------------------|-----|

| C.2 | MCU Block Diagram  | 175 |

| C.3 | Pin Assignments    | 175 |

| C.4 | Reserved Registers | 178 |

| C.5 | Reserved Vectors   | 178 |

| C.6 | Order Numbers      | 178 |

#### **General Description**

#### 1.2 Features

Features of the MC68H(R)C908JL3E include the following:

- EMC enhanced version of MC68H(R)C908JL3/JK3/JK1

- High-performance M68HC08 architecture

- Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

- Low-power design; fully static with stop and wait modes

- Maximum internal bus frequency:

- 8-MHz at 5V operating voltage

- 4-MHz at 3V operating voltage

- Oscillator options:

- Crystal oscillator for MC68HC908JL3E/JK3E/JK1E

- RC oscillator for MC68HRC908JL3E/JK3E/JK1E

- User program Flash memory with security<sup>(1)</sup> feature

- 4.096 bytes for MC68H(R)C908JL3E/JK3E

- 1,536 bytes for MC68H(R)C908JK1E

- 128 bytes of on-chip RAM

- 2-channel, 16-bit timer interface module (TIM)

- 12-channel, 8-bit analog-to-digital converter (ADC)

- 23 general purpose I/O ports for MC68H(R)C908JL3E:

- 7 keyboard interrupt with internal pull-up (6 keyboard interrupt for MC68HC908JL3E)

- 10 LED drivers (sink)

- 2 × 25mA open-drain I/O with pull-up

- 15 general purpose I/O ports for MC68H(R)C908JK3E/JK1E:

- 1 keyboard interrupt with internal pull-up (MC68HRC908JK3E/JK1E only)

- 4 LED drivers (sink)

- 2 × 25mA open-drain I/O with pull-up

- 10-channel ADC

- System protection features:

- Optional computer operating properly (COP) reset

- Optional low-voltage detection with reset and selectable trip points for 3V and 5V operation

- Illegal opcode detection with reset

- Illegal address detection with reset

- Master reset pin with internal pull-up and power-on reset

- IRQ with schmitt-trigger input and programmable pull-up

- 28-pin PDIP, 28-pin SOIC, and 48-pin LQFP packages for MC68H(R)C908JL3E

- 20-pin PDIP and 20-pin SOIC packages for MC68H(R)C908JK3E/JK1E

MC68HC908JL3E Family Data Sheet, Rev. 4

Freescale Semiconductor

16

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the Flash difficult for unauthorized users.

#### **General Description**

#### 1.5 Pin Functions

Description of the pin functions are provided in Table 1-2.

**Table 1-2. Pin Functions**

| PIN NAME              | PIN DESCRIPTION                                                                                                                                 | IN/OUT | VOLTAGE LEVEL                       |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------|

| V <sub>DDJL3JL3</sub> | Power supply.                                                                                                                                   | In     | 5V or 3V                            |

| V <sub>SS</sub>       | Power supply ground                                                                                                                             | Out    | 0V                                  |

| RST                   | RESET input, active low. With Internal pull-up and Schmitt trigger input.                                                                       | Input  | V <sub>DD</sub> to V <sub>TST</sub> |

| ĪRQ                   | IRQ  External IRQ pin.  With software programmable internal pull-up and schmitt trigger input.  This pin is also used for mode entry selection. |        | V <sub>DD</sub> to V <sub>TST</sub> |

| OSC1                  | X-tal or RC oscillator input.                                                                                                                   | In     | Analog                              |

|                       | MC68HC908JL3E/JK3E/JK1E:<br>X-tal oscillator output, this is the inverting OSC1 signal.                                                         | Out    | Analog                              |

| OSC2                  | MC68HRC908JL3E/JK3E/JK1E: Default is RC oscillator clock output, RCCLK. Shared with PTA6/KBI6, with programmable pull-up.                       | In/Out | $V_{DD}$                            |

|                       | 7-bit general purpose I/O port.                                                                                                                 | In/Out | V <sub>DD</sub>                     |

| DTA(O.C)              | Shared with 7 keyboard interrupts KBI[0:6].                                                                                                     | In     | V <sub>DD</sub>                     |

| PTA[0:6]              | Each pin has programmable internal pull-up device.                                                                                              | In     | V <sub>DD</sub>                     |

|                       | PTA[0:5] have LED direct sink capability                                                                                                        | In     | V <sub>SS</sub>                     |

| PTB[0:7]              | 8-bit general purpose I/O port.                                                                                                                 | In/Out | V <sub>DD</sub>                     |

| РТБ[0:7]              | Shared with 8 ADC inputs, ADC[0:7].                                                                                                             | In     | Analog                              |

|                       | 8-bit general purpose I/O port.                                                                                                                 | In/Out | V <sub>DD</sub>                     |

|                       | PTD[3:0] shared with 4 ADC inputs, ADC[8:11].                                                                                                   | Input  | Analog                              |

| PTD[0:7]              | PTD[4:5] shared with TIM channels, TCH0 and TCH1.                                                                                               | In/Out | V <sub>DD</sub>                     |

|                       | PTD[2:3], PTD[6:7] have LED direct sink capability                                                                                              | In     | V <sub>SS</sub>                     |

|                       | PTD[6:7] can be configured as 25mA open-drain output with pull-up.                                                                              | In/Out | V <sub>DD</sub>                     |

#### **NOTE**

On the MC68H(R)C908JK3E/JK1E, the following pins are not available: PTA0, PTA1, PTA2, PTA3, PTA4, PTA5, PTD0, and PTD1.

| Vector Priority | INT Flag         | Address               | Vector                                |

|-----------------|------------------|-----------------------|---------------------------------------|

| Lowest          | _                | \$FFD0<br>↓<br>\$FFDD | Not Used                              |

|                 | IF15             | \$FFDE                | ADC Conversion Complete Vector (High) |

|                 | IF15             | \$FFDF                | ADC Conversion Complete Vector (Low)  |

|                 | IF14             | \$FFE0                | Keyboard Vector (High)                |

|                 | IF 14            | \$FFE1                | Keyboard Vector (Low)                 |

|                 | IF13<br>↓<br>IF6 | _                     | Not Used                              |

|                 | IF5              | \$FFF2                | TIM Overflow Vector (High)            |

|                 | 11 3             | \$FFF3                | TIM Overflow Vector (Low)             |

|                 | IF4              | \$FFF4                | TIM Channel 1 Vector (High)           |

|                 | IF4<br>          | \$FFF5                | TIM Channel 1 Vector (Low)            |

|                 | IF3              | \$FFF6                | TIM Channel 0 Vector (High)           |

|                 | 11-3             | \$FFF7                | TIM Channel 0 Vector (Low)            |

|                 | IF2              | _                     | Not Used                              |

|                 | IF1              | \$FFFA                | IRQ Vector (High)                     |

|                 | II I             | \$FFFB                | IRQ Vector (Low)                      |

|                 |                  | \$FFFC                | SWI Vector (High)                     |

| $\downarrow$    |                  | \$FFFD                | SWI Vector (Low)                      |

| <b>▼</b>        |                  | \$FFFE                | Reset Vector (High)                   |

| Highest         | _                | \$FFFF                | Reset Vector (Low)                    |

**Table 2-1. Vector Addresses**

#### 2.4 Random-Access Memory (RAM)

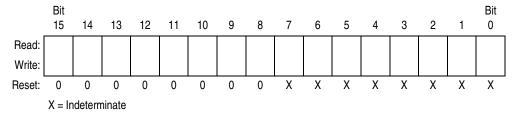

Addresses \$0080 through \$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

#### **NOTE**

For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 128 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF, direct addressing mode instructions can access efficiently all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

#### NOTE

For M6805 compatibility, the H register is not stacked.

MC68HC908JL3E Family Data Sheet, Rev. 4

#### **Central Processor Unit (CPU)**

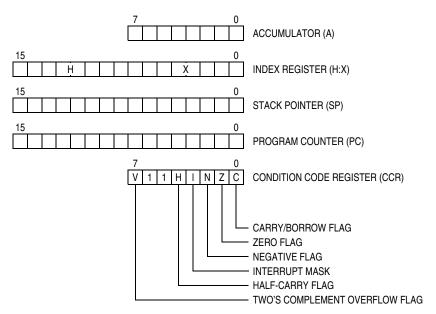

Figure 4-1. CPU Registers

#### 4.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 4-2. Accumulator (A)

#### 4.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 4-3. Index Register (H:X)

MC68HC908JL3E Family Data Sheet, Rev. 4

**Central Processor Unit (CPU)**

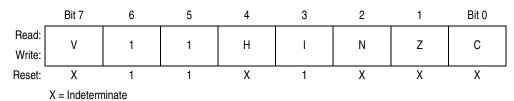

#### 4.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 4-6. Condition Code Register (CCR)

#### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

#### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

- 1 = Carry between bits 3 and 4

- 0 = No carry between bits 3 and 4

#### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

#### **NOTE**

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

#### **Central Processor Unit (CPU)**

Table 4-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation Description            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | Effect son CCR |     |          | Address<br>Mode | Opcode   | Operand                                             | es                                               |                                                 |                                      |

|------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-----|----------|-----------------|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ٧ | Н              | I   | N        | Z               | С        | Add                                                 | obc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR,X<br>CLR opr,SP                            | Clear                            | M ← \$00<br>A ← \$00<br>X ← \$00<br>H ← \$00<br>M ← \$00<br>M ← \$00<br>M ← \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 | _              | _   | 0        | 1               | _        | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff                                        | 3 1 1 1 3 2 4                        |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP  | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 | _              | _   | 1        | ‡               | Į.       | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                      | 0 | _              | 1   | 1        | ‡               | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | -              | 1   | ‡        | 1               | ‡        | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | î | _              |     | 1        | 1               | <b>1</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff          | 23443245                             |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U | -              | _   | 1        | ‡               | ‡        | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 4 + rel? \text{ (result)} \neq 0 \end{array}$ | _ | _              | -   | _        | -               | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | -              | -   | <b>‡</b> | <b>‡</b>        | -        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | $A \leftarrow (H:A)/(X)$<br>$H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - | -              | _   | -        | ‡               | ‡        | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 | _              | -   | ‡        | <b>‡</b>        | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | _              | - 1 | 1        | <b>‡</b>        | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

**System Integration Module (SIM)**

#### 5.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE-\$FFFF (\$FEFE-\$FEFF in Monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 5.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the reset status register (RSR). (See 5.7 SIM Registers.)

#### 5.3.1 External Pin Reset

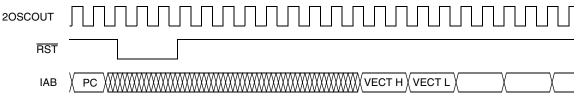

The RST pin circuits include an internal pull-up device. Pulling the asynchronous RST pin low halts all processing. The PIN bit of the reset status register (RSR) is set as long as RST is held low for a minimum of 67 2OSCOUT cycles, assuming that the POR was not the source of the reset. See Table 5-2 for details. Figure 5-4 shows the relative timing.

**Table 5-2. PIN Bit Set Timing**

| Reset Type | Number of Cycles Required to Set PIN |

|------------|--------------------------------------|

| POR        | 4163 (4096 + 64 + 3)                 |

| All others | 67 (64 + 3)                          |

Figure 5-4. External Reset Timing

#### 5.3.2 Active Resets from Internal Sources

All internal reset sources actively pull the  $\overline{RST}$  pin low for 32 2OSCOUT cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (Figure 5-5). An internal reset can be caused by an illegal address, illegal opcode, COP time-out, or POR. (See Figure 5-6.) Note that for POR resets, the SIM cycles through 4096 2OSCOUT cycles during which the SIM forces the  $\overline{RST}$  pin low. The internal reset signal then follows the sequence from the falling edge of  $\overline{RST}$  shown in Figure 5-5.

#### Oscillator (OSC)

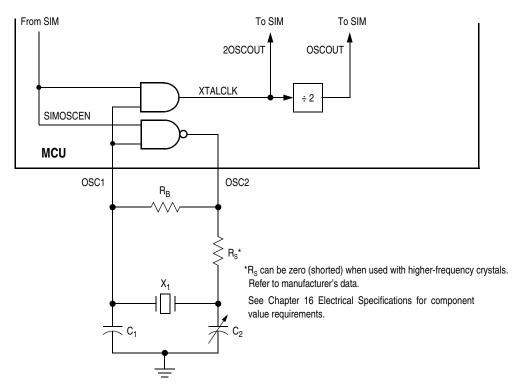

Figure 6-1. X-tal Oscillator External Connections

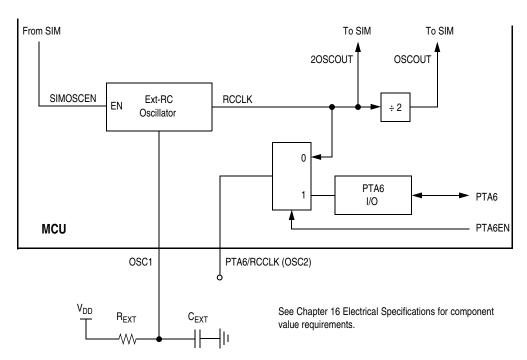

Figure 6-2. RC Oscillator External Connections

MC68HC908JL3E Family Data Sheet, Rev. 4

Table 7-2 is a summary of the vector differences between user mode and monitor mode.

**Table 7-2. Monitor Mode Vector Differences**

|         | Functions               |                         |                        |                         |                        |                       |                      |  |  |

|---------|-------------------------|-------------------------|------------------------|-------------------------|------------------------|-----------------------|----------------------|--|--|

| Modes   | СОР                     | Reset<br>Vector<br>High | Reset<br>Vector<br>Low | Break<br>Vector<br>High | Break<br>Vector<br>Low | SWI<br>Vector<br>High | SWI<br>Vector<br>Low |  |  |

| User    | Enabled                 | \$FFFE                  | \$FFFF                 | \$FFFC                  | \$FFFD                 | \$FFFC                | \$FFFD               |  |  |

| Monitor | Disabled <sup>(1)</sup> | \$FEFE                  | \$FEFF                 | \$FEFC                  | \$FEFD                 | \$FEFC                | \$FEFD               |  |  |

<sup>1.</sup> If the high voltage  $(V_{TST})$  is removed from the  $\overline{IRQ}$  pin or the  $\overline{RST}$  pin, the SIM asserts its COP enable output. The COP is a mask option enabled or disabled by the COPD bit in the configuration register.

When the host computer has completed downloading code into the MCU RAM, the host then sends a RUN command, which executes an RTI, which sends control to the address on the stack pointer.

#### 7.3.2 Baud Rate

The communication baud rate is dependant on oscillator frequency. The state of PTB3 also affects baud rate if entry to monitor mode is by  $\overline{IRQ} = V_{TST}$ . When PTB3 is high, the divide by ratio is 1024. If the PTB3 pin is at logic zero upon entry into monitor mode, the divide by ratio is 512.

Table 7-3. Monitor Baud Rate Selection

| Monitor Mode<br>Entry By:  | Input Clock<br>Frequency | РТВ3 | Baud Rate |

|----------------------------|--------------------------|------|-----------|

|                            | 4.9152 MHz               | 0    | 9600 bps  |

| $\overline{IRQ} = V_{TST}$ | 9.8304 MHz               | 1    | 9600 bps  |

|                            | 4.9152 MHz               | 1    | 4800 bps  |

| Blank reset vector,        | 9.8304 MHz               | Х    | 9600 bps  |

| $\overline{IRQ} = V_{DD}$  | 4.9152 MHz               | Х    | 4800 bps  |

Freescale Semiconductor 75

MC68HC908JL3E Family Data Sheet, Rev. 4

Input/Output (I/O) Ports

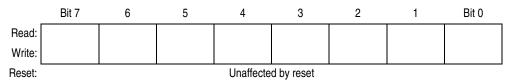

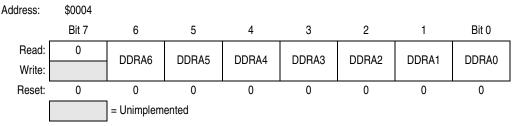

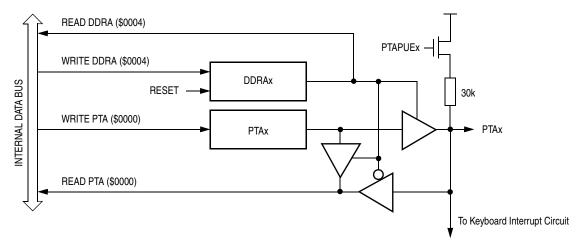

#### 10.2.2 Data Direction Register A (DDRA)

Data direction register A determines whether each port A pin is an input or an output. Writing a one to a DDRA bit enables the output buffer for the corresponding port A pin; a zero disables the output buffer.

Figure 10-3. Data Direction Register A (DDRA)

#### DDRA[6:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[6:0], configuring all port A pins as inputs.

- 1 = Corresponding port A pin configured as output

- 0 = Corresponding port A pin configured as input

#### NOTE

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

Figure 10-4 shows the port A I/O logic.

Figure 10-4. Port A I/O Circuit

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

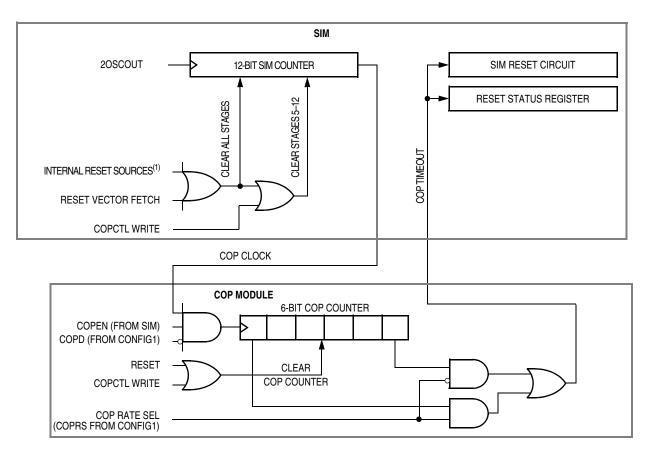

# **Chapter 13 Computer Operating Properly (COP)**

#### 13.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG1 register.

#### 13.2 Functional Description

Figure 13-1 shows the structure of the COP module.

NOTE: See Chapter 5 System Integration Module (SIM) for more details.

Figure 13-1. COP Block Diagram

MC68HC908JL3E Family Data Sheet, Rev. 4

#### 15.4 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

- Break status register (BSR)

- Break flag control register (BFCR)

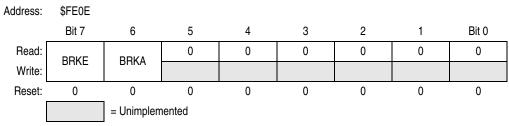

#### 15.4.1 Break Status and Control Register (BRKSCR)

The break status and control register contains break module enable and status bits.

Figure 15-3. Break Status and Control Register (BRKSCR)

#### **BRKE** — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a zero to bit 7. Reset clears the BRKE bit.

- 1 = Breaks enabled on 16-bit address match

- 0 = Breaks disabled

#### **BRKA** — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a one to BRKA generates a break interrupt. Clear BRKA by writing a zero to it before exiting the break routine. Reset clears the BRKA bit.

- 1 = Break address match

- 0 = No break address match

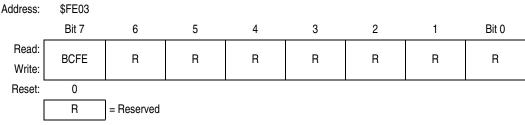

#### 15.4.4 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 15-7. Break Flag Control Register (BFCR)

#### **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

#### 15.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power-consumption standby modes.

#### 15.5.1 Wait Mode

If enabled, the break module is active in wait mode. In the break routine, the user can subtract one from the return address on the stack if SBSW is set (see 5.6 Low-Power Modes). Clear the SBSW bit by writing zero to it.

#### 15.5.2 Stop Mode

A break interrupt causes exit from stop mode and sets the SBSW bit in the break status register. See 5.7 SIM Registers.

Freescale Semiconductor 133

MC68HC908JL3E Family Data Sheet, Rev. 4

Break Module (BREAK)

#### 16.7 5V Oscillator Characteristics

Table 16-6. Oscillator Component Specifications (5V)

| Characteristic                                    | Symbol               | Min             | Тур            | Max | Unit |  |

|---------------------------------------------------|----------------------|-----------------|----------------|-----|------|--|

| Crystal frequency, XTALCLK                        | f <sub>OSCXCLK</sub> | _               | 10             | 32  | MHz  |  |

| RC oscillator frequency, RCCLK                    | f <sub>RCCLK</sub>   | 2               | 10             | 12  | MHz  |  |

| External clock reference frequency <sup>(1)</sup> | foscxclk             | dc              | _              | 32  | MHz  |  |

| Crystal load capacitance <sup>(2)</sup>           | C <sub>L</sub>       | _               | _              | _   |      |  |

| Crystal fixed capacitance <sup>(2)</sup>          | C <sub>1</sub>       | _               | $2 \times C_L$ | _   |      |  |

| Crystal tuning capacitance <sup>(2)</sup>         | C <sub>2</sub>       | _               | $2 \times C_L$ | _   |      |  |

| Feedback bias resistor                            | R <sub>B</sub>       | _               | 10 MΩ          | _   |      |  |

| Series resistor <sup>(2), (3)</sup>               | R <sub>S</sub>       | _               | _              | _   |      |  |

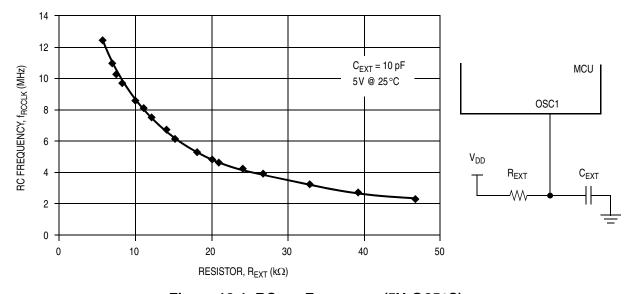

| RC oscillator external R                          | R <sub>EXT</sub>     | See Figure 16-1 |                |     |      |  |

| RC oscillator external C                          | C <sub>EXT</sub>     | _               | 10             | _   | pF   |  |

- 1. No more than 10% duty cycle deviation from 50%.

- 2. Consult crystal vendor data sheet.

- 3. Not required for high frequency crystals.

Figure 16-1. RC vs. Frequency (5V @25°C)

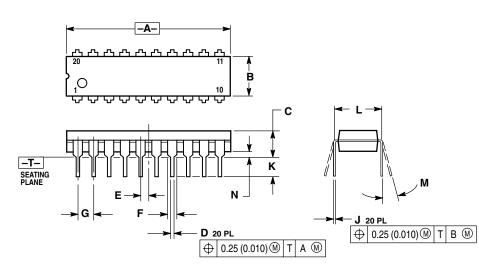

## **Chapter 17 Mechanical Specifications**

#### 17.1 Introduction

This section gives the dimensions for:

- 20-pin plastic dual in-line package (case #738)

- 20-pin small outline integrated circuit package (case #751D)

- 28-pin plastic dual in-line package (case #710)

- 28-pin small outline integrated circuit package (case #751F)

- 48-pin low-profile quad flat pack (case #932)

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Sales Office.

#### 17.2 Package Dimensions

Refer to the following pages for detailed package dimensions.

- DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982.

CONTROLLING DIMENSION: INCH.

- DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | INC   | HES   | MILLIN   | IETERS |  |

|-----|-------|-------|----------|--------|--|

| DIM | MIN   | MAX   | MIN      | MAX    |  |

| Α   | 1.010 | 1.070 | 25.66    | 27.17  |  |

| В   | 0.240 | 0.260 | 6.10     | 6.60   |  |

| С   | 0.150 | 0.180 | 3.81     | 4.57   |  |

| D   | 0.015 | 0.022 | 0.39     | 0.55   |  |

| Е   | 0.050 | BSC   | 1.27     | BSC    |  |

| 7   | 0.050 | 0.070 | 1.27     | 1.77   |  |

| G   | 0.100 | BSC   | 2.54     | BSC    |  |

| J   | 0.008 | 0.015 | 0.21     | 0.38   |  |

| K   | 0.110 | 0.140 | 2.80     | 3.55   |  |

| L   | 0.300 | BSC   | 7.62 BSC |        |  |

| M   | 0°    | 15°   | 0°       | 15°    |  |

| N   | 0.020 | 0.040 | 0.51     | 1.01   |  |

20-Pin PDIP (Case #738)

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- 4. 751F-01 THRU -04 OBSOLETE. NEW STANDARD: 751F-05

<u>/5\</u>

THIS DIMENSION DOES NOT INCLUDE DAM BAR PROTRUSION ALLOWABLE DAM BAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THIS DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA    | L OUTLINE   | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|--------------|-------------|------------------|-------------|

| TITLE: SOIC, WIDE BOD                                | ΟY.          | DOCUMENT NO | : 98ASB42345B    | REV: G      |

| 28 LEAD                                              | - · ,        | CASE NUMBER | 2: 751F-05       | 10 MAR 2005 |

| CASEOUTLINE                                          | STANDARD: MS | :_0134F     |                  |             |

#### A.5.5 ADC Characteristics

**Table A-5. ADC Characteristics**

| Characteristic                                | Symbol            | Min                          | Max                          | Unit                    | Comments                                                         |

|-----------------------------------------------|-------------------|------------------------------|------------------------------|-------------------------|------------------------------------------------------------------|

| Supply voltage                                | V <sub>DDAD</sub> | 2.2<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                       |                                                                  |

| Input voltages                                | V <sub>ADIN</sub> | V <sub>SS</sub>              | V <sub>DD</sub>              | V                       |                                                                  |

| Resolution                                    | B <sub>AD</sub>   | 8                            | 8                            | Bits                    |                                                                  |

| Absolute accuracy                             | A <sub>AD</sub>   | ± 0.5                        | ± 2                          | LSB                     | Includes quantization                                            |

| ADC internal clock                            | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                     | t <sub>AIC</sub> = 1/f <sub>ADIC</sub> , tested<br>only at 1 MHz |

| Conversion range                              | R <sub>AD</sub>   | $V_{SS}$                     | $V_{DD}$                     | V                       |                                                                  |

| Power-up time                                 | t <sub>ADPU</sub> | 14                           | _                            | t <sub>AIC</sub> cycles |                                                                  |

| Conversion time                               | t <sub>ADC</sub>  | 14                           | 15                           | t <sub>AIC</sub> cycles |                                                                  |

| Sample time <sup>(1)</sup>                    | t <sub>ADS</sub>  | 5                            | _                            | t <sub>AIC</sub> cycles |                                                                  |

| Zero input reading <sup>(2)</sup>             | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                     | $V_{IN} = V_{SS}$                                                |

| Full-scale reading <sup>(3)</sup>             | F <sub>ADI</sub>  | FE                           | FF                           | Hex                     | $V_{IN} = V_{DD}$                                                |

| Input capacitance                             | C <sub>ADI</sub>  | _                            | (20) 8                       | pF                      | Not tested                                                       |

| Input leakage <sup>(3)</sup><br>Port B/port D | _                 | _                            | ± 1                          | μА                      |                                                                  |

<sup>1.</sup> Source impedances greater than 10 k $\Omega$  adversely affect internal RC charging time during input sampling.

<sup>2.</sup> Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

<sup>3.</sup> The external system error caused by input leakage current is approximately equal to the product of R source and input current.

Figure C-1. MC68HC908KL3E/KK3E Block Diagram