Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | -                                                          |

| Peripherals                | LED, LVD, POR, PWM                                         |

| Number of I/O              | 23                                                         |

| Program Memory Size        | 4KB (4K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 128 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                |

| Data Converters            | A/D 12x8b                                                  |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-LQFP                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908jl3ecfae |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 4.3.4          | Program Counter                       |    |

|----------------|---------------------------------------|----|

| 4.3.5          | Condition Code Register               |    |

| 4.4            | Arithmetic/Logic Unit (ALU)           |    |

| 4.5            | Low-Power Modes                       |    |

| 4.5.1          | Wait Mode                             |    |

| 4.5.2          | Stop Mode                             |    |

| 4.6            | CPU During Break Interrupts           |    |

| 4.7            | Instruction Set Summary               | 42 |

| 4.8            | Opcode Map                            | 47 |

|                | Chapter 5                             |    |

|                | System Integration Module (SIM)       |    |

| 5.1            | Introduction                          |    |

| 5.2            | SIM Bus Clock Control and Generation  |    |

| 5.2.1          | Bus Timing                            |    |

| 5.2.2          | Clock Start-Up from POR               |    |

| 5.2.3          | Clocks in Stop Mode and Wait Mode     | 51 |

| 5.3            | Reset and System Initialization       |    |

| 5.3.1          | External Pin Reset                    |    |

| 5.3.2          | Active Resets from Internal Sources   |    |

| 5.3.2.1        |                                       |    |

| 5.3.2.2        | 3 - p                                 |    |

| 5.3.2.3        | <b>3</b> 1                            |    |

| 5.3.2.4        |                                       |    |

| 5.3.2.5        |                                       |    |

| 5.4            | SIM Counter                           |    |

| 5.4.1          | SIM Counter During Power-On Reset     |    |

| 5.4.2          | SIM Counter During Stop Mode Recovery |    |

| 5.4.3          | SIM Counter and Reset States          |    |

| 5.5            | Exception Control                     |    |

| 5.5.1          | Interrupts                            |    |

| 5.5.1.1        | · ·                                   |    |

| 5.5.1.2        |                                       |    |

| 5.5.2          | Interrupt Status Registers            |    |

| 5.5.2.1        | · · · · · · · · · · · · · · · · · · · |    |

| 5.5.2.2        | · · · · · · · · · · · · · · · · · · · |    |

| 5.5.2.3        | ı                                     |    |

| 5.5.3          | Reset                                 |    |

| 5.5.4<br>5.5.5 | Break Interrupts                      |    |

|                | Status Flag Protection in Break Mode  |    |

| 5.6            | Low-Power Modes                       |    |

| 5.6.1          | Wait Mode                             |    |

| 5.6.2          | Stop Mode                             |    |

| 5.7            | SIM Registers                         |    |

| 5.7.1          | Break Status Register (BSR)           |    |

| 5.7.2          | Reset Status Register (RSR)           |    |

| 5.7.3          | Break Flag Control Register (BFCR)    | 65 |

MC68HC908JL3E Family Data Sheet, Rev. 4

| Table 0          | i Contents                                 |     |

|------------------|--------------------------------------------|-----|

| 13.7.1           | Wait Mode                                  | 126 |

| 13.7.2           | Stop Mode                                  | 126 |

| 13.8             | COP Module During Break Mode               | 126 |

|                  | Chapter 14                                 |     |

|                  | Low Voltage Inhibit (LVI)                  |     |

| 14.1             | Introduction                               | 127 |

| 14.2             | Features                                   |     |

| 14.3             | Functional Description                     |     |

| 14.4             | LVI Control Register (CONFIG2/CONFIG1)     |     |

| 14.5             | Low-Power Modes                            | 128 |

| 14.5.1           | Wait Mode                                  |     |

| 14.5.2           | Stop Mode                                  | 128 |

|                  | Chapter 15                                 |     |

|                  | Break Module (BREAK)                       |     |

| 15.1             | Introduction                               | 129 |

| 15.2             | Features                                   | 129 |

| 15.3             | Functional Description                     |     |

| 15.3.1           | Flag Protection During Break Interrupts    |     |

| 15.3.2<br>15.3.3 | J 1                                        |     |

| 15.3.4           |                                            |     |

| 15.4             | Break Module Registers                     |     |

| 15.4.1           | Break Status and Control Register (BRKSCR) |     |

| 15.4.2           |                                            |     |

| 15.4.3<br>15.4.4 | <b>3</b>                                   |     |

| 15.4.4           | Break Flag Control Register (BFCR)         |     |

| 15.5.1           | Wait Mode                                  |     |

| 15.5.2           |                                            |     |

|                  | 01 1 10                                    |     |

|                  | Chapter 16 Electrical Specifications       |     |

| 16.1             | Introduction                               | 135 |

| 16.2             | Absolute Maximum Ratings                   |     |

| 16.3             | Functional Operating Range                 |     |

| 16.4             | Thermal Characteristics                    |     |

| 16.5             | 5V DC Electrical Characteristics           | 137 |

| 16.6             | 5V Control Timing                          | 138 |

| 16.7             | 5V Oscillator Characteristics              | 139 |

| 16.8             | 3V DC Electrical Characteristics           | 140 |

| 16.9             | 3V Control Timing                          | 141 |

| 16.10            | 3V Oscillator Characteristics              | 142 |

| 16.11            | Typical Supply Currents                    | 143 |

|                  |                                            |     |

MC68HC908JL3E Family Data Sheet, Rev. 4

12 Freescale Semiconductor

#### **Table of Contents**

# Appendix C MC68HC908KL3E/KK3E

| C.1 | Introduction       | 175 |

|-----|--------------------|-----|

| C.2 | MCU Block Diagram  | 175 |

| C.3 | Pin Assignments    | 175 |

| C.4 | Reserved Registers | 178 |

| C.5 | Reserved Vectors   | 178 |

| C.6 | Order Numbers      | 178 |

#### **General Description**

# 1.5 Pin Functions

Description of the pin functions are provided in Table 1-2.

**Table 1-2. Pin Functions**

| PIN NAME              | PIN DESCRIPTION                                                                                                                          | IN/OUT | VOLTAGE LEVEL                       |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------|

| V <sub>DDJL3JL3</sub> | Power supply.                                                                                                                            | In     | 5V or 3V                            |

| V <sub>SS</sub>       | Power supply ground                                                                                                                      | Out    | 0V                                  |

| RST                   | RESET input, active low. With Internal pull-up and Schmitt trigger input.                                                                | Input  | V <sub>DD</sub> to V <sub>TST</sub> |

| ĪRQ                   | External IRQ pin. With software programmable internal pull-up and schmitt trigger input. This pin is also used for mode entry selection. | Input  | V <sub>DD</sub> to V <sub>TST</sub> |

| OSC1                  | X-tal or RC oscillator input.                                                                                                            | In     | Analog                              |

|                       | MC68HC908JL3E/JK3E/JK1E:<br>X-tal oscillator output, this is the inverting OSC1 signal.                                                  | Out    | Analog                              |

| OSC2                  | MC68HRC908JL3E/JK3E/JK1E: Default is RC oscillator clock output, RCCLK. Shared with PTA6/KBI6, with programmable pull-up.                | In/Out | $V_{DD}$                            |

|                       | 7-bit general purpose I/O port.                                                                                                          | In/Out | V <sub>DD</sub>                     |

| DTA(O.C)              | Shared with 7 keyboard interrupts KBI[0:6].                                                                                              | In     | V <sub>DD</sub>                     |

| PTA[0:6]              | Each pin has programmable internal pull-up device.                                                                                       | In     | V <sub>DD</sub>                     |

|                       | PTA[0:5] have LED direct sink capability                                                                                                 | In     | V <sub>SS</sub>                     |

| PTB[0:7]              | 8-bit general purpose I/O port.                                                                                                          | In/Out | V <sub>DD</sub>                     |

| РТБ[0:7]              | Shared with 8 ADC inputs, ADC[0:7].                                                                                                      | In     | Analog                              |

|                       | 8-bit general purpose I/O port.                                                                                                          | In/Out | V <sub>DD</sub>                     |

|                       | PTD[3:0] shared with 4 ADC inputs, ADC[8:11].                                                                                            | Input  | Analog                              |

| PTD[0:7]              | PTD[4:5] shared with TIM channels, TCH0 and TCH1.                                                                                        | In/Out | V <sub>DD</sub>                     |

|                       | PTD[2:3], PTD[6:7] have LED direct sink capability                                                                                       | In     | V <sub>SS</sub>                     |

|                       | PTD[6:7] can be configured as 25mA open-drain output with pull-up.                                                                       | In/Out | V <sub>DD</sub>                     |

#### **NOTE**

On the MC68H(R)C908JK3E/JK1E, the following pins are not available: PTA0, PTA1, PTA2, PTA3, PTA4, PTA5, PTD0, and PTD1.

| Vector Priority | INT Flag         | Address               | Vector                                |

|-----------------|------------------|-----------------------|---------------------------------------|

| Lowest          | _                | \$FFD0<br>↓<br>\$FFDD | Not Used                              |

|                 | IF15             | \$FFDE                | ADC Conversion Complete Vector (High) |

|                 | IF15             | \$FFDF                | ADC Conversion Complete Vector (Low)  |

|                 | IF14             | \$FFE0                | Keyboard Vector (High)                |

|                 | IF 14            | \$FFE1                | Keyboard Vector (Low)                 |

|                 | IF13<br>↓<br>IF6 | _                     | Not Used                              |

|                 | IF5              | \$FFF2                | TIM Overflow Vector (High)            |

|                 | IFS              | \$FFF3                | TIM Overflow Vector (Low)             |

|                 | IF4              | \$FFF4                | TIM Channel 1 Vector (High)           |

|                 | 1174             | \$FFF5                | TIM Channel 1 Vector (Low)            |

|                 | IF3              | \$FFF6                | TIM Channel 0 Vector (High)           |

|                 | 11-3             | \$FFF7                | TIM Channel 0 Vector (Low)            |

|                 | IF2              | _                     | Not Used                              |

|                 | IF1              | \$FFFA                | IRQ Vector (High)                     |

|                 | II I             | \$FFFB                | IRQ Vector (Low)                      |

|                 | \$               |                       | SWI Vector (High)                     |

| $\downarrow$    |                  | \$FFFD                | SWI Vector (Low)                      |

| <b>▼</b>        |                  | \$FFFE                | Reset Vector (High)                   |

| Highest         | _                | \$FFFF                | Reset Vector (Low)                    |

**Table 2-1. Vector Addresses**

# 2.4 Random-Access Memory (RAM)

Addresses \$0080 through \$00FF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

#### **NOTE**

For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 128 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF, direct addressing mode instructions can access efficiently all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

#### NOTE

For M6805 compatibility, the H register is not stacked.

MC68HC908JL3E Family Data Sheet, Rev. 4

**Central Processor Unit (CPU)**

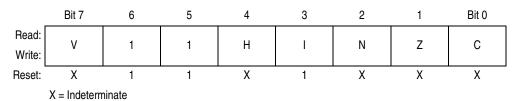

## 4.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 4-6. Condition Code Register (CCR)

#### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

#### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

- 1 = Carry between bits 3 and 4

- 0 = No carry between bits 3 and 4

# I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

#### **NOTE**

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

# Table 4-1. Instruction Set Summary (Sheet 2 of 6)

| Source                                                                                                | Operation                                         | Description                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   | Effect<br>on CCR |                                                                                              |                                                  |                                                                      |                                       |  | Opcode | Operand | es |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------|---------------------------------------|--|--------|---------|----|

| Form                                                                                                  | Operation                                         | Bescription                                                                                                                                                                                                                                                                                                                                                                          | ٧ | Н | I | N | Z | С                | Add                                                                                          | Opc                                              | Ope                                                                  | Cycles                                |  |        |         |    |

| BHS rel                                                                                               | Branch if Higher or Same (Same as BCC)            | $PC \leftarrow (PC) + 2 + rel? (C) = 0$                                                                                                                                                                                                                                                                                                                                              | - | - | - | - | ı | -                | REL                                                                                          | 24                                               | rr                                                                   | 3                                     |  |        |         |    |

| BIH rel                                                                                               | Branch if IRQ Pin High                            | PC ← (PC) + 2 + <i>rel</i> ? IRQ = 1                                                                                                                                                                                                                                                                                                                                                 | - | - | - | - | - | -                | REL                                                                                          | 2F                                               | rr                                                                   | 3                                     |  |        |         |    |

| BIL rel                                                                                               | Branch if IRQ Pin Low                             | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                                                                  | _ | _ | _ | - | - | _                | REL                                                                                          | 2E                                               | rr                                                                   | 3                                     |  |        |         |    |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT,X<br>BIT opr,SP<br>BIT opr,SP         | Bit Test                                          | (A) & (M)                                                                                                                                                                                                                                                                                                                                                                            | 0 | _ | ı | 1 | ‡ | _                | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 |                                                                      | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5  |  |        |         |    |

| BLE opr                                                                                               | Branch if Less Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (Z) \mid (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                            | _ | - | ı | _ | ı | _                | REL                                                                                          | 93                                               | rr                                                                   | 3                                     |  |        |         |    |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                     | $PC \leftarrow (PC) + 2 + rel? (C) = 1$                                                                                                                                                                                                                                                                                                                                              | _ | - | _ | - | - | _                | REL                                                                                          | 25                                               | rr                                                                   | 3                                     |  |        |         |    |

| BLS rel                                                                                               | Branch if Lower or Same                           | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                                                                     | L | - | L | - | - | -                | REL                                                                                          | 23                                               | rr                                                                   | 3                                     |  |        |         |    |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                                     | _ | - | - | - | - | _                | REL                                                                                          | 91                                               | rr                                                                   | 3                                     |  |        |         |    |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                    | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                                                              | _ | - | _ | - | _ | _                | REL                                                                                          | 2C                                               | rr                                                                   | 3                                     |  |        |         |    |

| BMI rel                                                                                               | Branch if Minus                                   | PC ← (PC) + 2 + rel? (N) = 1                                                                                                                                                                                                                                                                                                                                                         | - | - | - | - | - | -                | REL                                                                                          | 2B                                               | rr                                                                   | 3                                     |  |        |         |    |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                      | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                                                                                                                                                                                                                                                                                                                                 | - | - | - | - | - | -                | REL                                                                                          | 2D                                               | rr                                                                   | 3                                     |  |        |         |    |

| BNE rel                                                                                               | Branch if Not Equal                               | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                                                              | - | - | - | - | - | -                | REL                                                                                          | 26                                               | rr                                                                   | 3                                     |  |        |         |    |

| BPL rel                                                                                               | Branch if Plus                                    | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                                                              | _ | _ | _ | - | - | _                | REL                                                                                          | 2A                                               | rr                                                                   | 3                                     |  |        |         |    |

| BRA rel                                                                                               | Branch Always                                     | PC ← (PC) + 2 + <i>rel</i>                                                                                                                                                                                                                                                                                                                                                           | - | - | - | - | - | -                | REL                                                                                          | 20                                               | rr                                                                   | 3                                     |  |        |         |    |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                 | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                                                                | _ | _ | _ | _ | - | ‡                | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                              |  |        |         |    |

| BRN rel                                                                                               | Branch Never                                      | PC ← (PC) + 2                                                                                                                                                                                                                                                                                                                                                                        | _ | - | _ | _ | _ | _                | REL                                                                                          | 21                                               | rr                                                                   | 3                                     |  |        |         |    |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                                                                | _ | _ | ı | _ | ı | ‡                | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |  |        |         |    |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                             | Mn ← 1                                                                                                                                                                                                                                                                                                                                                                               | _ | _ |   | _ | - | _                | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C           | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                         | 4<br>4<br>4<br>4<br>4<br>4<br>4       |  |        |         |    |

| BSR rel                                                                                               | Branch to Subroutine                              | $ \begin{array}{c} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array} $                                                                                                                                                                                                         | _ | _ | _ | _ | _ | _                | REL                                                                                          | AD                                               | rr                                                                   | 4                                     |  |        |         |    |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                       | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel \; ? \; (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel \; ? \; (A) - (M) = \$00 \\ \end{array}$ | _ | _ | - | - | - | -                | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 71                                               | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6            |  |        |         |    |

| CLC                                                                                                   | Clear Carry Bit                                   | C ← 0                                                                                                                                                                                                                                                                                                                                                                                | Ŀ | - | Ŀ | Ŀ |   | 0                | INH                                                                                          | 98                                               |                                                                      | 1                                     |  |        |         |    |

| CLI                                                                                                   | Clear Interrupt Mask                              | I ← 0                                                                                                                                                                                                                                                                                                                                                                                | - | - | 0 | _ | - | -                | INH                                                                                          | 9A                                               |                                                                      | 2                                     |  |        |         |    |

# **Central Processor Unit (CPU)**

Table 4-1. Instruction Set Summary (Sheet 5 of 6)

| Source                                                                                         | Operation Description                                          |                                                                                                                                                                                                                                 | Effect on CCR |   |   | Effect on CCR |   |          |                                                     |                                                  |                                                 | Opcode                               | Operand | es |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|---|---------------|---|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|---------|----|

| Form                                                                                           | Operation                                                      | Bescription                                                                                                                                                                                                                     | ٧             | Н | ı | N             | Z | С        | Add<br>Mod                                          | Opc                                              | Ope                                             | Cycles                               |         |    |

| PULA                                                                                           | Pull A from Stack                                              | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                                              | -             | - | - | -             | - | -        | INH                                                 | 86                                               |                                                 | 2                                    |         |    |

| PULH                                                                                           | Pull H from Stack                                              | SP ← (SP + 1); Pull (H)                                                                                                                                                                                                         | -             | - | - | -             | - | -        | INH                                                 | 8A                                               |                                                 | 2                                    |         |    |

| PULX                                                                                           | Pull X from Stack                                              | $SP \leftarrow (SP + 1); Pull (X)$                                                                                                                                                                                              | -             | - | - | -             | - | -        | INH                                                 | 88                                               |                                                 | 2                                    |         |    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                   | Rotate Left through Carry                                      | b7 b0                                                                                                                                                                                                                           | 1             | _ | _ | ţ             | ţ | ‡        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |         |    |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                   | Rotate Right through Carry                                     | b7 b0                                                                                                                                                                                                                           | 1             | _ | _ | 1             | 1 | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |         |    |

| RSP                                                                                            | Reset Stack Pointer                                            | SP ← \$FF                                                                                                                                                                                                                       | -             | - | _ | _             | _ | _        | INH                                                 | 9C                                               |                                                 | 1                                    |         |    |

| RTI                                                                                            | Return from Interrupt                                          | $\begin{array}{l} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ SP \leftarrow (SP) + 1;  Pull  (A) \\ SP \leftarrow (SP) + 1;  Pull  (X) \\ SP \leftarrow (SP) + 1;  Pull  (PCH) \\ SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$ | 1             | 1 | ţ | 1             | ţ | ţ        | INH                                                 | 80                                               |                                                 | 7                                    |         |    |

| RTS                                                                                            | Return from Subroutine                                         | $SP \leftarrow SP + 1$ ; Pull (PCH)<br>$SP \leftarrow SP + 1$ ; Pull (PCL)                                                                                                                                                      | -             | - | _ | -             | - | _        | INH                                                 | 81                                               |                                                 | 4                                    |         |    |

| SBC #opr<br>SBC opr<br>SBC opr,<br>SBC opr,X<br>SBC opr,X<br>SBC X<br>SBC opr,SP<br>SBC opr,SP | Subtract with Carry                                            | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                  | 1             | - | _ | 1             | 1 | 1        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>9EE2<br>9ED2 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |         |    |

| SEC                                                                                            | Set Carry Bit                                                  | C ← 1                                                                                                                                                                                                                           | -             | - | - | -             | - | 1        | INH                                                 | 99                                               |                                                 | 1                                    |         |    |

| SEI                                                                                            | Set Interrupt Mask                                             | I ← 1                                                                                                                                                                                                                           | -             | - | 1 | -             | - | -        | INH                                                 | 9B                                               |                                                 | 2                                    |         |    |

| STA opr<br>STA opr,<br>STA opr,X<br>STA opr,X<br>STA ,X<br>STA opr,SP<br>STA opr,SP            | Store A in M                                                   | $M \leftarrow (A)$                                                                                                                                                                                                              | 0             | _ | _ | 1             | 1 | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | B7<br>C7<br>D7<br>E7<br>F7<br>9EE7<br>9ED7       | dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff       | 3<br>4<br>4<br>3<br>2<br>4<br>5      |         |    |

| STHX opr                                                                                       | Store H:X in M                                                 | (M:M + 1) ← (H:X)                                                                                                                                                                                                               | 0             | - | - | 1             | 1 | -        | DIR                                                 | 35                                               | dd                                              | 4                                    |         |    |

| STOP                                                                                           | Enable Interrupts, Stop Processing, Refer to MCU Documentation | $I \leftarrow 0$ ; Stop Processing                                                                                                                                                                                              | -             | - | 0 | -             | - | -        | INH                                                 | 8E                                               |                                                 | 1                                    |         |    |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX,X<br>STX,X<br>STX opr,SP<br>STX opr,SP     | Store X in M                                                   | $M \leftarrow (X)$                                                                                                                                                                                                              | 0             | _ | _ | 1             | 1 | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       | dd<br>hh II<br>ee ff<br>ff<br>ee ff             | 3<br>4<br>4<br>3<br>2<br>4<br>5      |         |    |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB,X<br>SUB opr,SP<br>SUB opr,SP  | Subtract                                                       | A ← (A) − (M)                                                                                                                                                                                                                   | ţ             | _ | _ | 1             | 1 | <b>1</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff          | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |         |    |

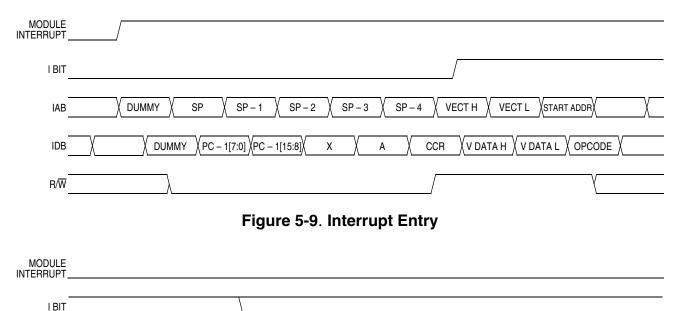

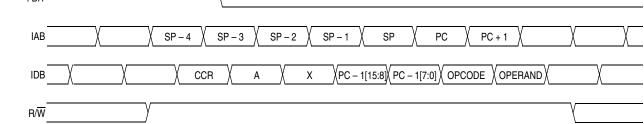

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the RTI instruction recovers the CPU register contents from the stack so that normal processing can resume. Figure 5-9 shows interrupt entry timing. Figure 5-10 shows interrupt recovery timing.

Figure 5-10. Interrupt Recovery

#### 5.5.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register), and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. Figure 5-11 demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

# 6.4 I/O Signals

The following paragraphs describe the oscillator I/O signals.

# 6.4.1 Crystal Amplifier Input Pin (OSC1)

OSC1 pin is an input to the crystal oscillator amplifier or the input to the RC oscillator circuit.

## 6.4.2 Crystal Amplifier Output Pin (OSC2/PTA6/RCCLK)

For the X-tal oscillator device, OSC2 pin is the output of the crystal oscillator inverting amplifier.

For the RC oscillator device, OSC2 pin can be configured as a general purpose I/O pin PTA6, or the output of the internal RC oscillator clock, RCCLK.

| Device                   | Oscillator | OSC2 pin function                                                                        |

|--------------------------|------------|------------------------------------------------------------------------------------------|

| MC68HC908JL3E/JK3E/JK1E  | X-tal      | Inverting OSC1                                                                           |

| MC68HRC908JL3E/JK3E/JK1E | RC         | Controlled by PTA6EN bit in PTAPUER (\$0D) PTA6EN = 0: RCCLK output PTA6EN = 1: PTA6 I/O |

## 6.4.3 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and enables/disables the X-tal oscillator circuit or the RC-oscillator.

## 6.4.4 X-tal Oscillator Clock (XTALCLK)

XTALCLK is the X-tal oscillator output signal. It runs at the full speed of the crystal (f<sub>XCLK</sub>) and comes directly from the crystal oscillator circuit. Figure 6-1 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. Also, the frequency and amplitude of XTALCLK can be unstable at start-up.

#### 6.4.5 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of the external R and C. Figure 6-2 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

## 6.4.6 Oscillator Out 2 (2OSCOUT)

2OSCOUT is same as the input clock (XTALCLK or RCCLK). This signal is driven to the SIM module and is used to determine the COP cycles.

#### 6.4.7 Oscillator Out (OSCOUT)

The frequency of this signal is equal to half of the 2OSCOUT, this signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. OSCOUT will be divided again in the SIM and results in the internal bus frequency being one fourth of the XTALCLK or RCCLK frequency.

MC68HC908JL3E Family Data Sheet, Rev. 4

Monitor ROM (MON)

#### 7.3.3 Data Format

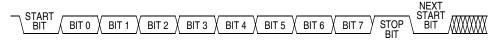

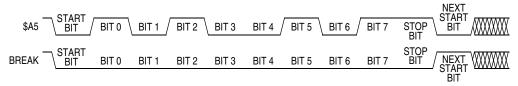

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. (See Figure 7-3 and Figure 7-4.)

Figure 7-3. Monitor Data Format

Figure 7-4. Sample Monitor Waveforms

The data transmit and receive rate can be anywhere from 4800 baud to 28.8k-baud. Transmit and receive baud rates must be identical.

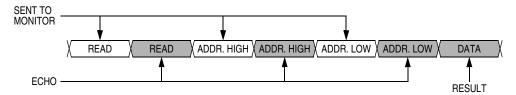

## 7.3.4 Echoing

As shown in Figure 7-5, the monitor ROM immediately echoes each received byte back to the PTB0 pin for error checking.

Figure 7-5. Read Transaction

Any result of a command appears after the echo of the last byte of the command.

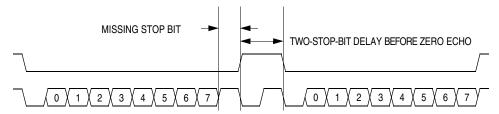

# 7.3.5 Break Signal

A start bit followed by nine low bits is a break signal. (See **Figure 7-6**.) When the monitor receives a break signal, it drives the PTB0 pin high for the duration of two bits before echoing the break signal.

Figure 7-6. Break Transaction

# **Chapter 8 Timer Interface Module (TIM)**

#### 8.1 Introduction

This section describes the timer interface module (TIM2, Version B). The TIM is a two-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions. Figure 8-1 is a block diagram of the TIM.

#### 8.2 Features

Features of the TIM include the following:

- Two input capture/output compare channels

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered pulse width modulation (PWM) signal generation

- Programmable TIM clock input with 7-frequency internal bus clock prescaler selection

- Free-running or modulo up-count operation

- · Toggle any channel pin on overflow

- TIM counter stop and reset bits

#### 8.3 Pin Name Conventions

The TIM share two I/O pins with two port D I/O pins. The full name of the TIM I/O pins are listed in Table 8-1. The generic pin name appear in the text that follows.

**Table 8-1. Pin Name Conventions**

| TIM Generic Pin Names: | TCH0      | TCH1      |

|------------------------|-----------|-----------|

| Full TIM Pin Names:    | PTD4/TCH0 | PTD5/TCH1 |

**Timer Interface Module (TIM)**

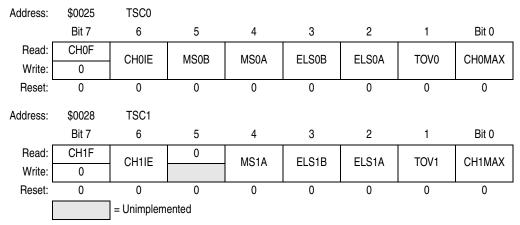

## 8.9.4 TIM Channel Status and Control Registers (TSC0:TSC1)

Each of the TIM channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- · Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 8-7. TIM Channel Status and Control Registers (TSC0:TSC1)

#### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

When TIM CPU interrupt requests are enabled (CHxIE=1), clear CHxF by reading the TIM channel x status and control register with CHxF set and then writing a zero to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing zero to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a one to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

#### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

Input/Output (I/O) Ports

#### 10.3 Port B

Port B is an 8-bit special function port that shares all eight of its port pins with the analog-to-digital converter (ADC) module, see Chapter 9 Analog-to-Digital Converter (ADC).

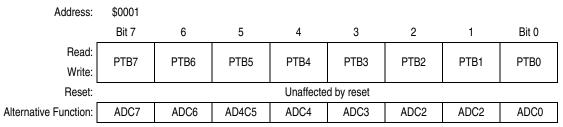

# 10.3.1 Port B Data Register (PTB)

The port B data register contains a data latch for each of the eight port B pins.

Figure 10-6. Port B Data Register (PTB)

#### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

#### ADC[7:0] — ADC channels 7 to 0

ADC[7:0] are pins used for the input channels to the analog-to-digital converter module. The channel select bits, ADCH[4:0], in the ADC status and control register define which port pin will be used as an ADC input and overrides any control from the port I/O logic. See Chapter 9 Analog-to-Digital Converter (ADC).

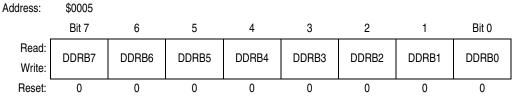

# 10.3.2 Data Direction Register B (DDRB)

Data direction register B determines whether each port B pin is an input or an output. Writing a one to a DDRB bit enables the output buffer for the corresponding port B pin; a zero disables the output buffer.

Figure 10-7. Data Direction Register B (DDRB)

#### DDRB[7:0] — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB[7:0], configuring all port B pins as inputs.

- 1 = Corresponding port B pin configured as output

- 0 = Corresponding port B pin configured as input

#### NOTE

Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1.

MC68HC908JL3E Family Data Sheet, Rev. 4

# **Chapter 13 Computer Operating Properly (COP)**

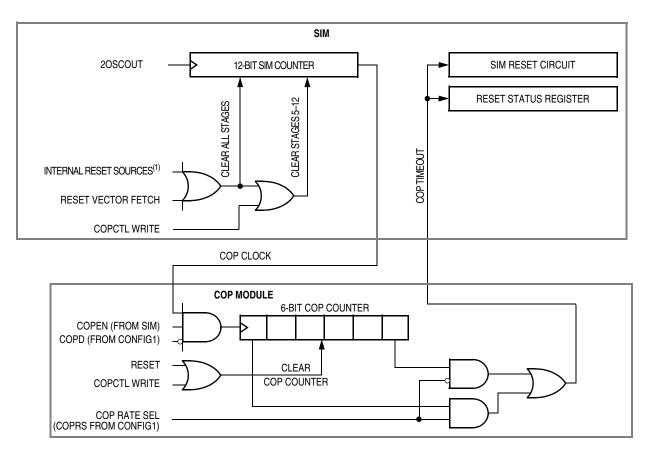

#### 13.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG1 register.

# 13.2 Functional Description

Figure 13-1 shows the structure of the COP module.

NOTE: See Chapter 5 System Integration Module (SIM) for more details.

Figure 13-1. COP Block Diagram

MC68HC908JL3E Family Data Sheet, Rev. 4

#### **Electrical Specifications**

## Table 16-4. DC Electrical Characteristics (5V) (Continued)

| Characteristic <sup>(1)</sup> | Symbol            | Min | Typ <sup>(2)</sup> | Max | Unit |

|-------------------------------|-------------------|-----|--------------------|-----|------|

| LVI reset voltage             | V <sub>LVR5</sub> | 3.6 | 4.0                | 4.4 | V    |

- 1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted. 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

- 3. Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{OP}$  = 4MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_1 = 20 \text{ pF}$  on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run I<sub>DD</sub>. Measured with all modules enabled.

- 4. Wait I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 4MHz). All inputs 0.2V from rail. No dc loads. Less than  $\overline{100}$  pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

- 5. Stop I<sub>DD</sub> measured with OSC1 grounded; no port pins sourcing current. LVI is disabled.

- 6. Maximum is highest voltage that POR is guaranteed.

- 7. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum  $V_{DD}$  is reached.

- 8.  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0 \, \text{V}$ .

# 16.6 5V Control Timing

## Table 16-5. Control Timing (5V)

| Characteristic <sup>(1)</sup>               | Symbol           | Min | Max | Unit |

|---------------------------------------------|------------------|-----|-----|------|

| Internal operating frequency <sup>(2)</sup> | f <sub>OP</sub>  | _   | 8   | MHz  |

| RST input pulse width low <sup>(3)</sup>    | t <sub>IRL</sub> | 750 | _   | ns   |

- 1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ ; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{SS}$ , unless otherwise

- 2. Some modules may require a minimum frequency greater than dc for proper operation; see appropriate table for this

- 3. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

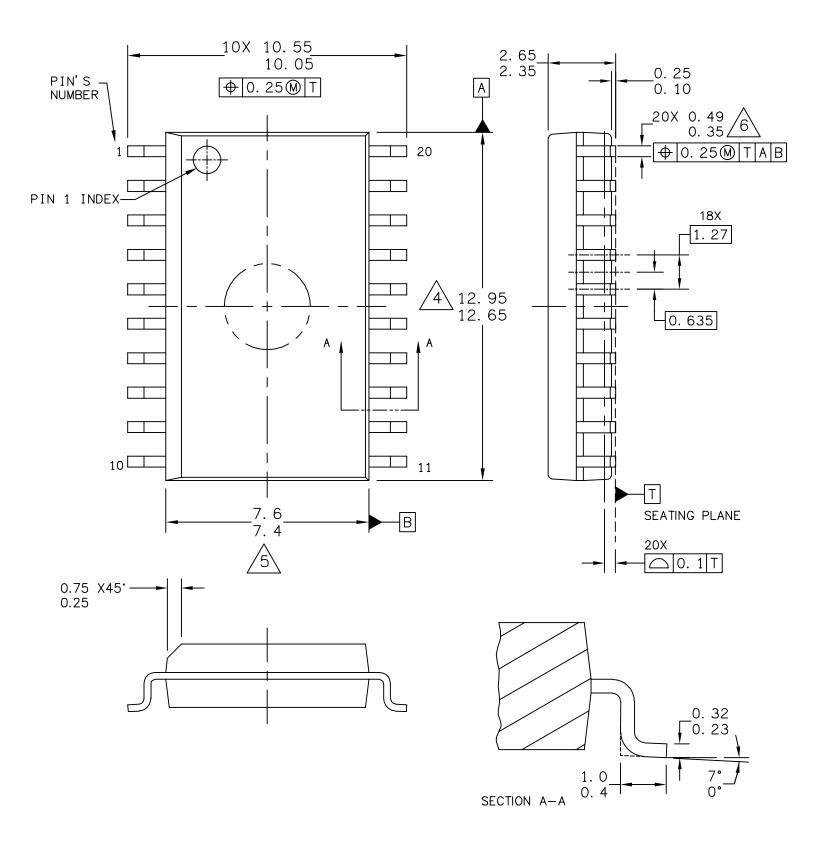

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO: 98ASB42343B |                  | REV: J      |

| 20LD SOIC W/B, 1.<br>CASF-OUTLI                      |           | CASE NUMBER: 751D-07     |                  | 23 MAR 2005 |

| CASE OOTET                                           |           | STANDARD: JE             | DEC MS-013AC     |             |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICA |  | L OUTLINE          | PRINT VERSION NOT TO SCALE |             |  |

|-----------------------------------------------------------------|--|--------------------|----------------------------|-------------|--|

| TITLE: SOIC, WIDE BODY, 28 LEAD CASEOUTLINE                     |  | DOCUMENT NO        | ): 98ASB42345B             | REV: G      |  |

|                                                                 |  | CASE NUMBER        | 2: 751F-05                 | 10 MAR 2005 |  |

|                                                                 |  | STANDARD: MS-013AE |                            |             |  |

# Appendix B MC68H(R)C08JL3E/JK3E

# **B.1 Introduction**

This appendix introduces four devices, that are ROM versions of MC68H(R)C908JL3E/JK3E:

- MC68HC08JL3E

- MC68HC08JK3E

- MC68HRC08JL3E

- MC68HRC08JK3E

The entire data book apply to these ROM devices, with exceptions outlined in this appendix.

Table B-1. Summary of Device Differences

|                                                  | MC68H(R)C08JL3E/JK3E                                                          | MC68H(R)C908JL3E/JK3E                                       |

|--------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|

| Memory (\$EC00-\$FBFF)                           | 4,096 bytes ROM                                                               | 4,096 bytes Flash                                           |

| User vectors (\$FFD0-\$FFFF)                     | 48 bytes ROM                                                                  | 48 bytes Flash                                              |

| Registers at \$FE08 and \$FE09                   | Not used;<br>locations are reserved.                                          | Flash related registers.<br>\$FE08 — FLCR<br>\$FF09 — FLBPR |

| Monitor ROM<br>(\$FC00–\$FDFF and \$FE10–\$FFCF) | \$FC00–\$FDFF: Not used.<br>\$FE10–\$FFCF: Used for testing<br>purposes only. | Used for testing and Flash programming/erasing.             |

# **B.2 MCU Block Diagram**

Figure B-1 shows the block diagram of the MC68H(R)C08JL3E/JK3E.

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of  $32 \times 20$ SCOUT cycles instead of a  $4096 \times 20$ SCOUT cycle delay.

- 1 = Stop mode recovery after 32 × 2OSCOUT cycles

- 0 = Stop mode recovery after 4096 × 20SCOUT cycles

#### NOTE

Exiting stop mode by pulling reset will result in the long stop recovery.

If using an external crystal, do not set the SSREC bit.

#### STOP — STOP Instruction Enable

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### **COPD** — **COP** Disable Bit

COPD disables the COP module. (See Chapter 13 Computer Operating Properly (COP).)

- 1 = COP module disabled

- 0 = COP module enabled

# **B.5.3 Mask Option Register 2 (MOR2)**

| Address: | \$001E |            |        |              |              |   |   |       |

|----------|--------|------------|--------|--------------|--------------|---|---|-------|

|          | Bit 7  | 6          | 5      | 4            | 3            | 2 | 1 | Bit 0 |

| Read:    | IRQPUD | 0          | 0      | LVIT1        | LVIT0        | 0 | 0 | 0     |

| Write:   |        |            |        |              |              |   |   |       |

| Reset:   | 0      | 0          | 0      | Not affected | Not affected | 0 | 0 | 0     |

| POR:     | 0      | 0          | 0      | 0            | 0            | 0 | 0 | 0     |

|          |        | = Unimplem | nented |              |              |   |   |       |

Figure 18-2. Mask Option Register 2 (MOR2)

#### IRQPUD — IRQ Pin Pull-up control bit

- 1 = Internal pull-up is disconnected

- $0 = Internal pull-up is connected between <math>\overline{IRQ}$  pin and  $V_{DD}$

# LVIT1, LVIT0 — Low Voltage Inhibit trip voltage selection bits

Detail description of the LVI control signals is given in Chapter 14 Low Voltage Inhibit (LVI)

#### **B.6 Monitor ROM**

The monitor program (monitor ROM: \$FE10-\$FFCF) on the MC68H(R)C08JL3E/JK3E is for device testing only. \$FC00-\$FDFF are unused.