Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 14                                                                     |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                            |

| Data Converters            | A/D 12x8b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 20-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908jk1ecpe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 4.3.4          | Program Counter                       |    |

|----------------|---------------------------------------|----|

| 4.3.5          | Condition Code Register               |    |

| 4.4            | Arithmetic/Logic Unit (ALU)           |    |

| 4.5            | Low-Power Modes                       |    |

| 4.5.1          | Wait Mode                             |    |

| 4.5.2          | Stop Mode                             |    |

| 4.6            | CPU During Break Interrupts           |    |

| 4.7            | Instruction Set Summary               | 42 |

| 4.8            | Opcode Map                            | 47 |

|                | Chapter 5                             |    |

|                | System Integration Module (SIM)       |    |

| 5.1            | Introduction                          |    |

| 5.2            | SIM Bus Clock Control and Generation  |    |

| 5.2.1          | Bus Timing                            |    |

| 5.2.2          | Clock Start-Up from POR               |    |

| 5.2.3          | Clocks in Stop Mode and Wait Mode     | 51 |

| 5.3            | Reset and System Initialization       |    |

| 5.3.1          | External Pin Reset                    |    |

| 5.3.2          | Active Resets from Internal Sources   |    |

| 5.3.2.1        |                                       |    |

| 5.3.2.2        | 3 - p                                 |    |

| 5.3.2.3        | <b>3</b> 1                            |    |

| 5.3.2.4        |                                       |    |

| 5.3.2.5        |                                       |    |

| 5.4            | SIM Counter                           |    |

| 5.4.1          | SIM Counter During Power-On Reset     |    |

| 5.4.2          | SIM Counter During Stop Mode Recovery |    |

| 5.4.3          | SIM Counter and Reset States          |    |

| 5.5            | Exception Control                     |    |

| 5.5.1          | Interrupts                            |    |

| 5.5.1.1        | · ·                                   |    |

| 5.5.1.2        |                                       |    |

| 5.5.2          | Interrupt Status Registers            |    |

| 5.5.2.1        | · · · · · · · · · · · · · · · · · · · |    |

| 5.5.2.2        | · · · · · · · · · · · · · · · · · · · |    |

| 5.5.2.3        | ı                                     |    |

| 5.5.3          | Reset                                 |    |

| 5.5.4<br>5.5.5 | Break Interrupts                      |    |

|                | Status Flag Protection in Break Mode  |    |

| 5.6            | Low-Power Modes                       |    |

| 5.6.1          | Wait Mode                             |    |

| 5.6.2          | Stop Mode                             |    |

| 5.7            | SIM Registers                         |    |

| 5.7.1          | Break Status Register (BSR)           |    |

| 5.7.2          | Reset Status Register (RSR)           |    |

| 5.7.3          | Break Flag Control Register (BFCR)    | 65 |

MC68HC908JL3E Family Data Sheet, Rev. 4

## **General Description**

# 1.4 Pin Assignments

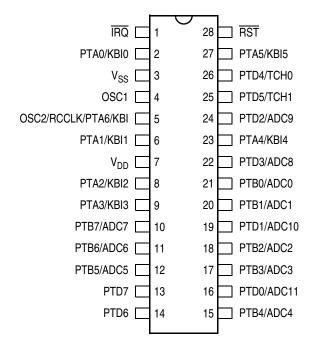

MC68H(R)C908JL3E

Figure 1-2. 28-Pin PDIP/SOIC Pin Assignment

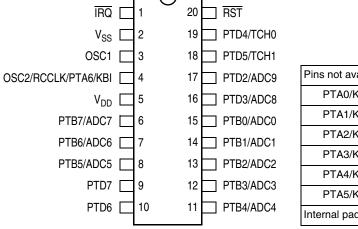

| Pins not available on 20-pin packages |            |  |  |  |  |  |  |

|---------------------------------------|------------|--|--|--|--|--|--|

| PTA0/KBI0                             | PTD0/ADC11 |  |  |  |  |  |  |

| PTA1/KBI1                             | PTD1/ADC10 |  |  |  |  |  |  |

| PTA2/KBI2                             |            |  |  |  |  |  |  |

| PTA3/KBI3                             |            |  |  |  |  |  |  |

| PTA4/KBI4                             |            |  |  |  |  |  |  |

| PTA5/KBI5                             |            |  |  |  |  |  |  |

| Internal pads are unconnected.        |            |  |  |  |  |  |  |

MC68H(R)C908JK3E/JK1E

Figure 1-3. 20-Pin PDIP/SOIC Pin Assignment

# 2.10 Flash Program Operation

Programming of the Flash memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0 or \$XXE0. Use this step-by-step procedure to program a row of Flash memory (Figure 2-5 shows a flowchart of the programming algorithm):

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Write any data to any Flash location within the address range of the row to be programmed.

- 3. Wait for a time,  $t_{nvs}$  (10 $\mu$ s).

- 4. Set the HVEN bit.

- 5. Wait for a time,  $t_{pqs}$  (5µs).

- 6. Write data to the byte being programmed.

- 7. Wait for time, t<sub>PROG</sub> (30μs).

- 8. Repeat step 6 and 7 until all the bytes within the row are programmed.

- 9. Clear the PGM bit.

- 10. Wait for time,  $t_{nvh}$  (5µs).

- Clear the HVEN bit.

- 12. After time,  $t_{rcv}$  (1 $\mu$ s), the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

The time between each Flash address change (step 6 to step 6), or the time between the last Flash addressed programmed to clearing the PGM bit (step 6 to step 10), must not exceed the maximum programming time,  $t_{PBOG}$  max.

## NOTE

Programming and erasing of Flash locations cannot be performed by code being executed from the Flash memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps.

# 2.11 Flash Protection

Due to the ability of the on-board charge pump to erase and program the Flash memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a Flash Block Protect Register (FLBPR). The FLBPR determines the range of the Flash memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the Flash memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

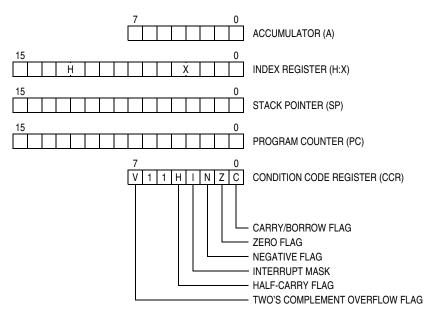

## **Central Processor Unit (CPU)**

Figure 4-1. CPU Registers

## 4.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 4-2. Accumulator (A)

# 4.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 4-3. Index Register (H:X)

# **Central Processor Unit (CPU)**

Table 4-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | Effect on CCR |   |          |          | Effect on CCR |                                                     |                                                  | Operand                                         | es                                   |

|------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|---|----------|----------|---------------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ٧ | Н             | I | N        | Z        | С             | Address<br>Mode                                     | Opcode                                           | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR,X<br>CLR opr,SP                            | Clear                            | M ← \$00<br>A ← \$00<br>X ← \$00<br>H ← \$00<br>M ← \$00<br>M ← \$00<br>M ← \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 | _             | _ | 0        | 1        | _             | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff                                        | 3 1 1 1 3 2 4                        |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP  | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 | _             | _ | 1        | ‡        | Į.            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                      | 0 | _             | 1 | 1        | ‡        | 1             | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | -             | 1 | ‡        | 1        | ‡             | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | î | _             |   | 1        | 1        | <b>1</b>      | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff          | 23443245                             |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U | -             | _ | 1        | ‡        | ‡             | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 4 + rel? \text{ (result)} \neq 0 \end{array}$ | _ | _             | - | _        | -        | _             | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | -             | - | <b>‡</b> | <b>‡</b> | -             | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | $A \leftarrow (H:A)/(X)$<br>$H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - | -             | _ | -        | ‡        | ‡             | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 | _             | _ | ‡        | <b>‡</b> | _             | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | _             | Ī | 1        | <b>‡</b> | _             | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

# Table 4-1. Instruction Set Summary (Sheet 6 of 6)

| Source                                                       | Operation                             | Description                                                                                                                                                                                                                                                                                                                                                                  | Effect on CCR |   |   |          |       |   | Address<br>Mode                       | Opcode                             | Operand        | es                         |

|--------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|---|----------|-------|---|---------------------------------------|------------------------------------|----------------|----------------------------|

| Form                                                         | Operation                             |                                                                                                                                                                                                                                                                                                                                                                              |               |   | I | N        | N Z C |   | Add                                   | Opc                                | Ope            | Cycles                     |

| SWI                                                          | Software Interrupt                    | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  I \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ | _             | _ | 1 | _        | _     | _ | INH                                   | 83                                 |                | 9                          |

| TAP                                                          | Transfer A to CCR                     | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                    | 1             | 1 | ‡ | ‡        | ‡     | ‡ | INH                                   | 84                                 |                | 2                          |

| TAX                                                          | Transfer A to X                       | X ← (A)                                                                                                                                                                                                                                                                                                                                                                      | -             | - | _ | -        | -     | - | INH                                   | 97                                 |                | 1                          |

| TPA                                                          | Transfer CCR to A                     | $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                         | -             | - | _ | -        | -     | - | INH                                   | 85                                 |                | 1                          |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP | Test for Negative or Zero             | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                       | 0             | _ | _ | <b>‡</b> | Î     | - | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 3<br>1<br>1<br>3<br>2<br>4 |

| TSX                                                          | Transfer SP to H:X                    | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                               | -             | - | - | -        | -     | - | INH                                   | 95                                 |                | 2                          |

| TXA                                                          | Transfer X to A                       | A ← (X)                                                                                                                                                                                                                                                                                                                                                                      | -             | - | _ | -        | _     | - | INH                                   | 9F                                 |                | 1                          |

| TXS                                                          | Transfer H:X to SP                    | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                             | -             | - | _ | _        | -     | - | INH                                   | 94                                 |                | 2                          |

| WAIT                                                         | Enable Interrupts; Wait for Interrupt | I bit ← 0; Inhibit CPU clocking until interrupted                                                                                                                                                                                                                                                                                                                            | -             | _ | 0 | -        | -     | _ | INH                                   | 8F                                 |                | 1                          |

| Α     | Accumulator                                                         | n            | Any bit                                     |

|-------|---------------------------------------------------------------------|--------------|---------------------------------------------|

| С     | Carry/borrow bit                                                    | opr          | Operand (one or two bytes)                  |

| CCR   | Condition code register                                             | PC           | Program counter                             |

| dd    | Direct address of operand                                           | PCH          | Program counter high byte                   |

| dd rr | Direct address of operand and relative offset of branch instruction | PCL          | Program counter low byte                    |

| DD    | Direct to direct addressing mode                                    | REL          | Relative addressing mode                    |

| DIR   | Direct addressing mode                                              | rel          | Relative program counter offset byte        |

| DIX+  | Direct to indexed with post increment addressing mode               | rr           | Relative program counter offset byte        |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | SP1          | Stack pointer, 8-bit offset addressing mode |

| EXT   | Extended addressing mode                                            | SP2          | Stack pointer 16-bit offset addressing mode |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | SP           | Stack pointer                               |

| Н     | Half-carry bit                                                      | U            | Undefined                                   |

| Н     | Index register high byte                                            | V            | Overflow bit                                |

| hh II | High and low bytes of operand address in extended addressing        | Χ            | Index register low byte                     |

|       | Interrupt mask                                                      | Z            | Zero bit                                    |

| ii    | Immediate operand byte                                              | &            | Logical AND                                 |

| IMD   | Immediate source to direct destination addressing mode              | 1            | Logical OR                                  |

| IMM   | Immediate addressing mode                                           | $\oplus$     | Logical EXCLUSIVE OR                        |

| INH   | Inherent addressing mode                                            | ()           | Contents of                                 |

| IX    | Indexed, no offset addressing mode                                  | <u>–(</u> )  | Negation (two's complement)                 |

| IX+   | Indexed, no offset, post increment addressing mode                  | #            | Immediate value                             |

| IX+D  | Indexed with post increment to direct addressing mode               | **           | Sign extend                                 |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$ | Loaded with                                 |

| IX1+  | Indexed, 8-bit offset, post increment addressing mode               | ?            | If                                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | :            | Concatenated with                           |

| M     | Memory location                                                     | ‡            | Set or cleared                              |

| N     | Negative bit                                                        | _            | Not affected                                |

# 4.8 Opcode Map

See Table 4-2.

**System Integration Module (SIM)**

# 5.3 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE-\$FFFF (\$FEFE-\$FEFF in Monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see 5.4 SIM Counter), but an external reset does not. Each of the resets sets a corresponding bit in the reset status register (RSR). (See 5.7 SIM Registers.)

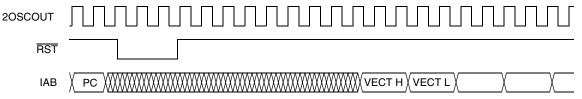

## 5.3.1 External Pin Reset

The RST pin circuits include an internal pull-up device. Pulling the asynchronous RST pin low halts all processing. The PIN bit of the reset status register (RSR) is set as long as RST is held low for a minimum of 67 2OSCOUT cycles, assuming that the POR was not the source of the reset. See Table 5-2 for details. Figure 5-4 shows the relative timing.

**Table 5-2. PIN Bit Set Timing**

| Reset Type | Number of Cycles Required to Set PIN |

|------------|--------------------------------------|

| POR        | 4163 (4096 + 64 + 3)                 |

| All others | 67 (64 + 3)                          |

Figure 5-4. External Reset Timing

# 5.3.2 Active Resets from Internal Sources

All internal reset sources actively pull the  $\overline{RST}$  pin low for 32 2OSCOUT cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (Figure 5-5). An internal reset can be caused by an illegal address, illegal opcode, COP time-out, or POR. (See Figure 5-6.) Note that for POR resets, the SIM cycles through 4096 2OSCOUT cycles during which the SIM forces the  $\overline{RST}$  pin low. The internal reset signal then follows the sequence from the falling edge of  $\overline{RST}$  shown in Figure 5-5.

## 7.3.1 Entering Monitor Mode

Table 7-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a POR and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- 1. If  $\overline{IRQ} = V_{TST}$ :

- Clock on OSC1 is 4.9125MHz (EXT OSC or XTAL)

- PTB3 = low

- 2. If  $\overline{IRQ} = V_{TST}$ :

- Clock on OSC1 is 9.8304MHz (EXT OSC or XTAL)

- PTB3 = high

- 3. If \$FFFE & \$FFFF is blank (contains \$FF):

- Clock on OSC1 is 9.8304MHz (EXT OSC or XTAL or RC)

- $\overline{IRQ} = V_{DD}$

**Table 7-1. Monitor Mode Entry Requirements and Options**

| ĪRQ                             | \$FFFE<br>and<br>\$FFFF    | PTB3 <sup>(1)</sup> | PTB2 | PTB1 | PTB0 | OSC1 Frequency       | Bus<br>Frequency        | Comments                                                                              |

|---------------------------------|----------------------------|---------------------|------|------|------|----------------------|-------------------------|---------------------------------------------------------------------------------------|

| V <sub>TST</sub> <sup>(2)</sup> | Х                          | 0                   | 0    | 1    | 1    | 4.9152MHz            | 2.4576MHz<br>(OSC1 ÷ 2) | High-voltage entry to monitor mode. (3)                                               |

| V <sub>TST</sub>                | Х                          | 1                   | 0    | 1    | 1    | 9.8304MHz            | 2.4576MHz<br>(OSC1 ÷ 4) | 9600 baud communication on PTB0. COP disabled.                                        |

| V <sub>DD</sub>                 | BLANK<br>(contain<br>\$FF) | х                   | x    | X    | 1    | 9.8304MHz            | 2.4576MHz<br>(OSC1 ÷ 4) | Low-voltage entry to monitor mode. (4) 9600 baud communication on PTB0. COP disabled. |

| V <sub>DD</sub>                 | NOT<br>BLANK               | Х                   | Х    | Х    | Х    | At desired frequency | OSC1 ÷ 4                | Enters User mode.                                                                     |

<sup>1.</sup> PTB3 = 0: Bypasses the divide-by-two prescaler to SIM when using  $V_{TST}$  for monitor mode entry. The OSC1 clock must be 50% duty cycle for this condition.

MC68HRC908JL3E/JK3E/JK1E — clock must be EXT OSC.

MC68HC908JL3E/JK3E/JK1E — clock can be EXT OSC or XTAL.

MC68HRC908JL3E/JK3E/JK1E — clock must be RC OSC.

MC68HC908JL3E/JK3E/JK1E — clock can be EXT OSC or XTAL.

If  $V_{TST}$  is applied to IRQ and PTB3 is low upon monitor mode entry (Table 7-1 condition set 1), the bus frequency is a divide-by-two of the clock input to OSC1. If PTB3 is high with  $V_{TST}$  applied to  $\overline{IRQ}$  upon monitor mode entry (Table 7-1 condition set 2), the bus frequency is a divide-by-four of the clock input to OSC1. Holding the PTB3 pin low when entering monitor mode causes a bypass of a divide-by-two stage at the oscillator *only if*  $V_{TST}$  *is applied to*  $\overline{IRQ}$ . In this event, the OSCOUT frequency is equal to the 2OSCOUT frequency, and OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.

<sup>2.</sup> See Table 16-4. DC Electrical Characteristics (5V) for V<sub>TST</sub> voltage level requirements.

<sup>3.</sup> For  $\overline{IRQ} = V_{TST}$

<sup>4.</sup> For  $\overline{IRQ} = V_{DD}$ :

## Monitor ROM (MON)

# Table 7-6. IREAD (Indexed Read) Command

| Description           | Read next 2 bytes in memory from last address accessed |  |  |  |  |  |

|-----------------------|--------------------------------------------------------|--|--|--|--|--|

| Operand               | Specifies 2-byte address in high byte:low byte order   |  |  |  |  |  |

| Data Returned         | Returns contents of next two addresses                 |  |  |  |  |  |

| Opcode                | \$1A                                                   |  |  |  |  |  |

| Command Sequence      |                                                        |  |  |  |  |  |

| SENT TO MONITOR IREAD | IREAD   DATA   DATA                                    |  |  |  |  |  |

| ECHO —                | RESULT                                                 |  |  |  |  |  |

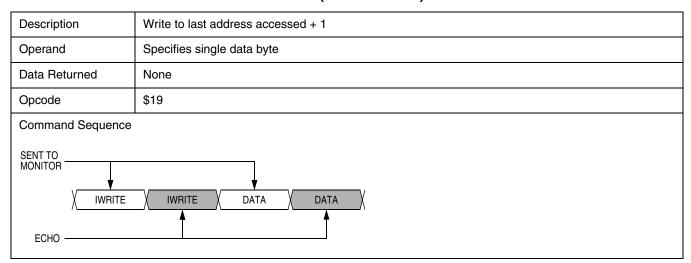

# Table 7-7. IWRITE (Indexed Write) Command

## NOTE

A sequence of IREAD or IWRITE commands can sequentially access a block of memory over the full 64-Kbyte memory map.

## 8.4.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use the following initialization procedure:

- 1. In the TIM status and control register (TSC):

- a. Stop the TIM counter by setting the TIM stop bit, TSTOP.

- b. Reset the TIM counter and prescaler by setting the TIM reset bit, TRST.

- 2. In the TIM counter modulo registers (TMODH:TMODL), write the value for the required PWM period.

- 3. In the TIM channel x registers (TCHxH:TCHxL), write the value for the required pulse width.

- 4. In TIM channel x status and control register (TSCx):

- Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB:MSxA. (See Table 8-3.)

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. (See Table 8-3.)

## NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM status control register (TSC), clear the TIM stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSC0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. (See 8.9.4 TIM Channel Status and Control Registers (TSC0:TSC1).)

MC68HC908JL3E Family Data Sheet, Rev. 4 Freescale Semiconductor 87

## 9.3.2 Voltage Conversion

When the input voltage to the ADC equals  $V_{DD}$ , the ADC converts the signal to \$FF (full scale). If the input voltage equals  $V_{SS}$ , the ADC converts it to \$00. Input voltages between  $V_{DD}$  and  $V_{SS}$  are a straight-line linear conversion. All other input voltages will result in \$FF if greater than  $V_{DD}$  and \$00 if less than  $V_{SS}$ .

#### NOTE

Input voltage should not exceed the analog supply voltages.

#### 9.3.3 Conversion Time

Fourteen ADC internal clocks are required to perform one conversion. The ADC starts a conversion on the first rising edge of the ADC internal clock immediately following a write to the ADSCR. If the ADC internal clock is selected to run at 1 MHz, then one conversion will take  $14\mu s$  to complete. With a 1 MHz ADC internal clock the maximum sample rate is 71.43kHz.

Number of Bus Cycles = Conversion Time  $\times$  Bus Frequency

## 9.3.4 Continuous Conversion

In the continuous conversion mode, the ADC continuously converts the selected channel filling the ADC data register with new data after each conversion. Data from the previous conversion will be overwritten whether that data has been read or not. Conversions will continue until the ADCO bit is cleared. The COCO bit (ADC status and control register, \$003C) is set after each conversion and can be cleared by writing the ADC status and control register or reading of the ADC data register.

## 9.3.5 Accuracy and Precision

The conversion process is monotonic and has no missing codes.

# 9.4 Interrupts

When the AIEN bit is set, the ADC module is capable of generating a CPU interrupt after each ADC conversion. A CPU interrupt is generated if the COCO bit is at 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

## 9.5 Low-Power Modes

The following subsections describe the ADC in low-power modes.

## 9.5.1 Wait Mode

The ADC continues normal operation during wait mode. Any enabled CPU interrupt request from the ADC can bring the MCU out of wait mode. If the ADC is not required to bring the MCU out of wait mode, power down the ADC by setting the ADCH[4:0] bits in the ADC status and control register to 1's before executing the WAIT instruction.

MC68HC908JL3E Family Data Sheet, Rev. 4

## Analog-to-Digital Converter (ADC)

## 9.5.2 Stop Mode

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

# 9.6 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D.

# 9.6.1 ADC Voltage In (ADCVIN)

ADCVIN is the input voltage signal from one of the 12 ADC channels to the ADC module.

# 9.7 I/O Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

## 9.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register.

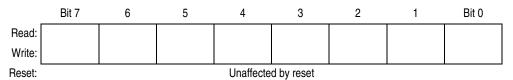

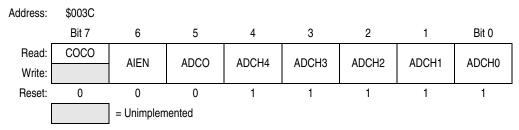

Figure 9-3. ADC Status and Control Register (ADSCR)

## **COCO** — Conversions Complete Bit

When the AIEN bit is a 0, the COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the ADC status and control register is written or whenever the ADC data register is read. Reset clears this bit.

- 1 = Conversion completed (AIEN = 0)

- 0 = Conversion not completed (AIEN = 0)

When the AIEN bit is a 1 (CPU interrupt enabled), the COCO is a read-only bit, and will always be 0 when read.

# AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register is read or the status/control register is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

## **Analog-to-Digital Converter (ADC)**

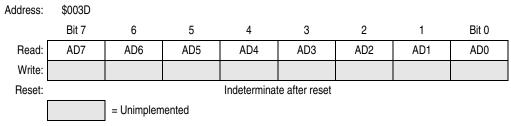

# 9.7.2 ADC Data Register

One 8-bit result register is provided. This register is updated each time an ADC conversion completes.

Figure 9-4. ADC Data Register (ADR)

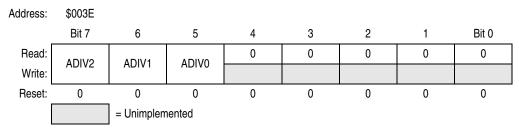

# 9.7.3 ADC Input Clock Register

This register selects the clock frequency for the ADC

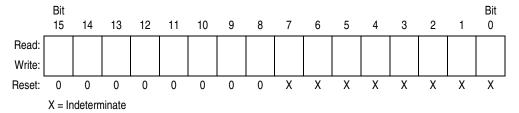

Figure 9-5. ADC Input Clock Register (ADICLK)

## ADIV[2:0] — ADC Clock Prescaler Bits

ADIV[2:0] form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock. Table 9-2 shows the available clock configurations. The ADC clock should be set to approximately 1 MHz.

Table 9-2. ADC Clock Divide Ratio

| ADIV2 | ADIV1 | ADIV0 | ADC Clock Rate       |

|-------|-------|-------|----------------------|

| 0     | 0     | 0     | ADC Input Clock ÷ 1  |

| 0     | 0     | 1     | ADC Input Clock ÷ 2  |

| 0     | 1     | 0     | ADC Input Clock ÷ 4  |

| 0     | 1     | 1     | ADC Input Clock ÷ 8  |

| 1     | Х     | Х     | ADC Input Clock ÷ 16 |

X = don't care

102

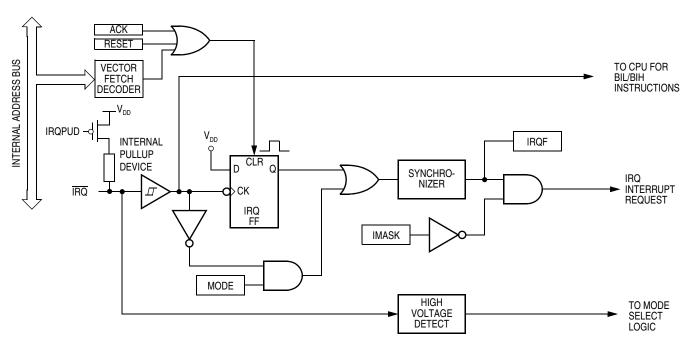

## External Interrupt (IRQ)

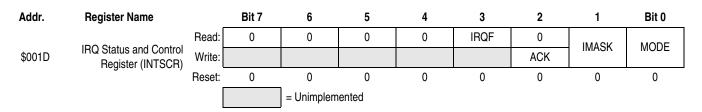

The vector fetch or software clear may occur before or after the interrupt pin returns to one. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

When set, the IMASK bit in the INTSCR mask all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

#### NOTE

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests. See 5.5 Exception Control.

Figure 11-1. IRQ Module Block Diagram

Figure 11-2. IRQ I/O Register Summary

# **Chapter 13 Computer Operating Properly (COP)**

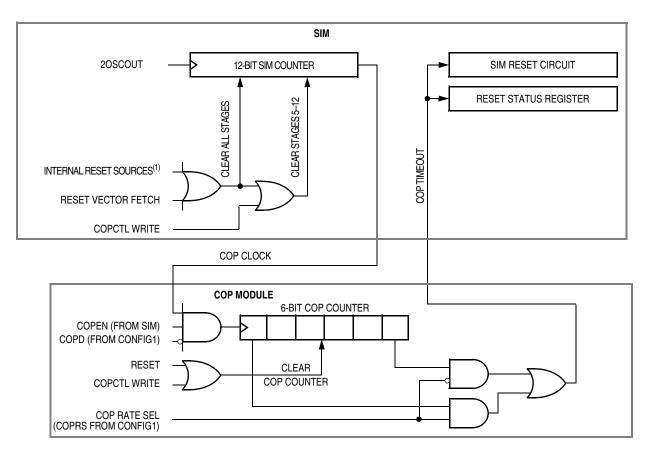

## 13.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG1 register.

# 13.2 Functional Description

Figure 13-1 shows the structure of the COP module.

NOTE: See Chapter 5 System Integration Module (SIM) for more details.

Figure 13-1. COP Block Diagram

MC68HC908JL3E Family Data Sheet, Rev. 4

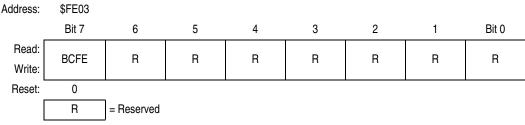

# 15.4.4 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 15-7. Break Flag Control Register (BFCR)

## **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

## 15.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power-consumption standby modes.

## 15.5.1 Wait Mode

If enabled, the break module is active in wait mode. In the break routine, the user can subtract one from the return address on the stack if SBSW is set (see 5.6 Low-Power Modes). Clear the SBSW bit by writing zero to it.

# 15.5.2 Stop Mode

A break interrupt causes exit from stop mode and sets the SBSW bit in the break status register. See 5.7 SIM Registers.

Freescale Semiconductor 133

## NOTES:

POSITIONAL TOLERANCE OF LEADS, SHALL BE WITHIN 0.25 MM (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

3 DIMENSION DOES NOT INCLUDE MOLD FLASH.

- 4. 710-01 OBSOLETE, NEW STD 710-02.

- 5. CONTROLLING DIMENSION: INCH

|      | IN           | СН                      | MILL  | IMETER    |       |        | INCH        |         | LIMETER    |

|------|--------------|-------------------------|-------|-----------|-------|--------|-------------|---------|------------|

| DIM  | MIN          | MAX                     | MIN   | MAX       | DIM   | MIN    | MAX         | MIN     | MAX        |

| А    | 1.435        | 1.465                   | 36.45 | 37.21     |       |        |             |         |            |

| В    | 0.540        | 0.560                   | 13.72 | 14.22     |       |        |             |         |            |

| С    | 0.155        | 0.200                   | 3.94  | 5.08      |       |        |             |         |            |

| D    | 0.014        | 0.022                   | 0.36  | 0.56      |       |        |             |         |            |

| F    | 0.040        | 0.060                   | 1.02  | 1.52      |       |        |             |         |            |

| G    | 0.100        | BSC                     | 2.54  | 4 BSC     |       |        |             |         |            |

| Н    | 0.065        | 0.085                   | 1.65  | 2.16      |       |        |             |         |            |

| J    | 0.008        | 0.015                   | 0.20  | 0.38      |       |        |             |         |            |

| K    | 0.115        | 0.135                   | 2.92  | 3.43      |       |        |             |         |            |

| L    | 0.600        | BSC                     | 15.2  | 4 BSC     |       |        |             |         |            |

| М    | 0 *          | 15°                     | 0*    | 15°       |       |        |             |         |            |

| N    | 0.020        | 0.040                   | 0.51  | 1.02      |       |        |             |         |            |

|      |              |                         |       |           |       |        |             |         |            |

| © FI | REESCALE SEM | ICONDUCTOR, S RESERVED. | INC.  | MECHANICA | L OUT | L I NE | PRINT VER   | SION NO | T TO SCALE |

|      |              | O NEGENTED.             |       |           | T     |        | 1 004004000 |         |            |

TITLE:

28 LD PDIP

28 LD PDIP

28 LD PDIP

CASE NUMBER: 710-02

STANDARD: NON-JEDEC

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- 4. 751F-01 THRU -04 OBSOLETE. NEW STANDARD: 751F-05

<u>/5\</u>

THIS DIMENSION DOES NOT INCLUDE DAM BAR PROTRUSION ALLOWABLE DAM BAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THIS DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                     | PRINT VERSION NO | OT TO SCALE |  |

|------------------------------------------------------|-----------|-------------------------------|------------------|-------------|--|

| TITLE: SOIC, WIDE BOD                                | ΟY.       | DOCUMENT NO                   | REV: G           |             |  |

| 28 LEAD                                              | - · ,     | CASE NUMBER: 751F-05 10 MAR 2 |                  |             |  |

| CASEOUTLINE                                          |           | STANDARD: MS                  | :_0134F          |             |  |

# A.5.6 Memory Characteristics

The Flash memory can only be read at an operating voltage of 2.2 to 5.5V. Program and erase are achieved at an operating voltage of 2.7 to 5.5 V. The program and erase parameters in Table A-6 are for  $V_{DD} = 2.7 \text{ to } 5.5 \text{ V only.}$

**Table A-6. Memory Characteristics**

| Characteristic                             | Symbol                            | Min | Max | Unit   |

|--------------------------------------------|-----------------------------------|-----|-----|--------|

| RAM data retention voltage                 | V <sub>RDR</sub>                  | 1.3 | _   | V      |

| Flash program bus clock frequency          | _                                 | 1   | _   | MHz    |

| Flash read bus clock frequency             | f <sub>Read</sub> <sup>(1)</sup>  | 32k | 8M  | Hz     |

| Flash page erase time                      | t <sub>Erase</sub> <sup>(2)</sup> | 1   | _   | ms     |

| Flash mass erase time                      | t <sub>MErase</sub> (3)           | 4   | _   | ms     |

| Flash PGM/ERASE to HVEN set up time        | 10                                | _   | μS  |        |

| Flash high-voltage hold time               | t <sub>nvh</sub>                  | 5   | _   | μS     |

| Flash high-voltage hold time (mass erase)  | t <sub>nvhl</sub>                 | 100 | _   | μS     |

| Flash program hold time                    | t <sub>pgs</sub>                  | 5   | _   | μS     |

| Flash program time                         | t <sub>PROG</sub>                 | 30  | 40  | μS     |

| Flash return to read time                  | t <sub>rcv</sub> <sup>(4)</sup>   | 1   | _   | μS     |

| Flash cumulative program hv period         | t <sub>HV</sub> <sup>(5)</sup>    | _   | 4   | ms     |

| Flash row erase endurance <sup>(6)</sup>   | _                                 | 10k | _   | cycles |

| Flash row program endurance <sup>(7)</sup> | _                                 | 10k | _   | cycles |

| Flash data retention time <sup>(8)</sup>   | _                                 | 10  | _   | years  |

- 1.  $f_{\mbox{\scriptsize Read}}$  is defined as the frequency range for which the Flash memory can be read.

- 2. If the page erase time is longer than t<sub>Erase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the Flash mem-

- 3. If the mass erase time is longer than t<sub>MErase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the Flash

- 4. t<sub>rcv</sub> is defined as the time it needs before the Flash can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

- 5. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

- $t_{HV}$  must satisfy this condition:  $t_{nvs} + t_{nvh} + t_{pgs} + (t_{PROG} \times 32) \le t_{HV}$  max. 6. The minimum row endurance value specifies each row of the Flash memory is guaranteed to work for at least this many erase / program cycles.

- 7. The minimum row endurance value specifies each row of the Flash memory is guaranteed to work for at least this many erase / program cycles.

- 8. The Flash is guaranteed to retain data over the entire operating temperature range for at least the minimum time specified.

163

## SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of  $32 \times 20$ SCOUT cycles instead of a  $4096 \times 20$ SCOUT cycle delay.

- 1 = Stop mode recovery after 32 × 20SCOUT cycles

- 0 = Stop mode recovery after 4096 × 20SCOUT cycles

#### NOTE

Exiting stop mode by pulling reset will result in the long stop recovery.

If using an external crystal, do not set the SSREC bit.

## STOP — STOP Instruction Enable

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

## **COPD** — **COP** Disable Bit

COPD disables the COP module. (See Chapter 13 Computer Operating Properly (COP).)

- 1 = COP module disabled

- 0 = COP module enabled

# **B.5.3 Mask Option Register 2 (MOR2)**

| Address: | \$001E |            |        |                 |                 |   |   |       |

|----------|--------|------------|--------|-----------------|-----------------|---|---|-------|

|          | Bit 7  | 6          | 5      | 4               | 3               | 2 | 1 | Bit 0 |

| Read:    | IRQPUD | 0          | 0      | LVIT1           | LVIT0           | 0 | 0 | 0     |

| Write:   |        |            |        |                 |                 |   |   |       |

| Reset:   | 0      | 0          | 0      | Not<br>affected | Not<br>affected | 0 | 0 | 0     |

| POR:     | 0      | 0          | 0      | 0               | 0               | 0 | 0 | 0     |

|          |        | = Unimplem | nented |                 |                 |   |   |       |

Figure 18-2. Mask Option Register 2 (MOR2)

## IRQPUD — IRQ Pin Pull-up control bit

- 1 = Internal pull-up is disconnected

- $0 = Internal pull-up is connected between <math>\overline{IRQ}$  pin and  $V_{DD}$

# LVIT1, LVIT0 — Low Voltage Inhibit trip voltage selection bits

Detail description of the LVI control signals is given in Chapter 14 Low Voltage Inhibit (LVI)

## **B.6 Monitor ROM**

The monitor program (monitor ROM: \$FE10-\$FFCF) on the MC68H(R)C08JL3E/JK3E is for device testing only. \$FC00-\$FDFF are unused.