#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                            |

| Data Converters            | A/D 12x8b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 20-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc908jk3ecpe |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

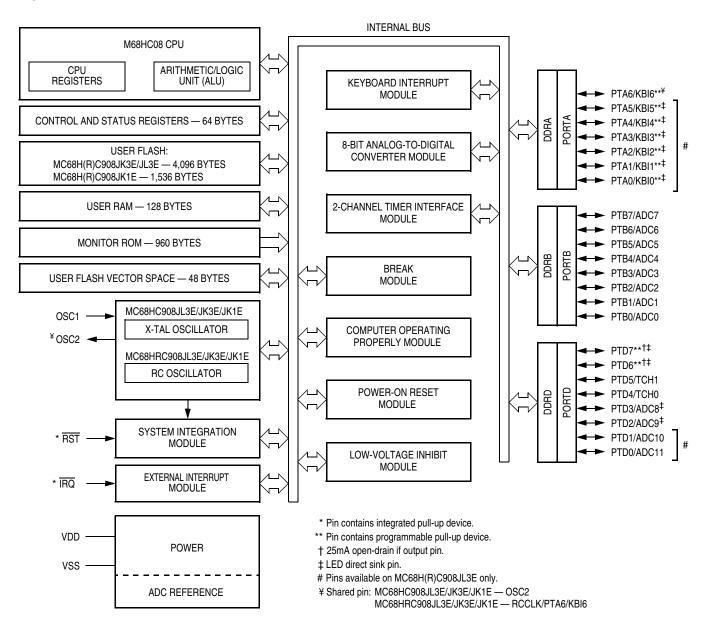

## 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68H(R)C908JL3E.

Figure 1-1. MCU Block Diagram

**General Description**

## **1.5 Pin Functions**

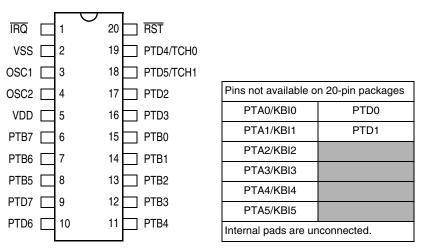

Description of the pin functions are provided in Table 1-2.

| PIN NAME              | PIN DESCRIPTION                                                                                                                                   | IN/OUT | VOLTAGE LEVEL         |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|

| V <sub>DDJL3JL3</sub> | Power supply.                                                                                                                                     | In     | 5V or 3V              |

| V <sub>SS</sub>       | Power supply ground                                                                                                                               | Out    | 0V                    |

| RST                   | RESET input, active low.<br>With Internal pull-up and Schmitt trigger input.                                                                      | Input  | $V_{DD}$ to $V_{TST}$ |

| ĪRQ                   | External IRQ pin.<br>With software programmable internal pull-up and schmitt<br>trigger input.<br>This pin is also used for mode entry selection. | Input  | $V_{DD}$ to $V_{TST}$ |

| OSC1                  | X-tal or RC oscillator input.                                                                                                                     | In     | Analog                |

|                       | MC68HC908JL3E/JK3E/JK1E:<br>X-tal oscillator output, this is the inverting OSC1 signal.                                                           |        | Analog                |

| OSC2                  | MC68HRC908JL3E/JK3E/JK1E:<br>Default is RC oscillator clock output, RCCLK.<br>Shared with PTA6/KBI6, with programmable pull-up.                   | In/Out | V <sub>DD</sub>       |

|                       | 7-bit general purpose I/O port.                                                                                                                   | In/Out | V <sub>DD</sub>       |

| DTAIO.61              | Shared with 7 keyboard interrupts KBI[0:6].                                                                                                       | In     | V <sub>DD</sub>       |

| PTA[0:6]              | Each pin has programmable internal pull-up device.                                                                                                | In     | V <sub>DD</sub>       |

|                       | PTA[0:5] have LED direct sink capability                                                                                                          | In     | V <sub>SS</sub>       |

| PTB[0:7]              | 8-bit general purpose I/O port.                                                                                                                   | In/Out | V <sub>DD</sub>       |

| F1D[0.7]              | Shared with 8 ADC inputs, ADC[0:7].                                                                                                               | In     | Analog                |

|                       | 8-bit general purpose I/O port.                                                                                                                   | In/Out | V <sub>DD</sub>       |

|                       | PTD[3:0] shared with 4 ADC inputs, ADC[8:11].                                                                                                     | Input  | Analog                |

| PTD[0:7]              | PTD[4:5] shared with TIM channels, TCH0 and TCH1.                                                                                                 | In/Out | V <sub>DD</sub>       |

|                       | PTD[2:3], PTD[6:7] have LED direct sink capability                                                                                                | In     | V <sub>SS</sub>       |

|                       | PTD[6:7] can be configured as 25mA open-drain output with pull-up.                                                                                | In/Out | V <sub>DD</sub>       |

#### Table 1-2. Pin Functions

#### NOTE

On the MC68H(R)C908JK3E/JK1E, the following pins are not available: PTA0, PTA1, PTA2, PTA3, PTA4, PTA5, PTD0, and PTD1.

\_\_\_\_\_

| Source<br>Form                                                                                        | Operation                                            | Description                                                                                                                                                                                                                                                                                                                                   |   |    | Effect<br>on CCR |   |   |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                                                       | les                                  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|------------------|---|---|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|

| Form                                                                                                  | ·                                                    | •                                                                                                                                                                                                                                                                                                                                             |   |    | I                | Ν | z | С | Add<br>Moo                                                                                   | opc                                              | Ope                                                                           | Cycles                               |

| BHS rel                                                                                               | Branch if Higher or Same<br>(Same as BCC)            | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 0$                                                                                                                                                                                                                                                                                             | - | -  | -                | - | - | - | REL                                                                                          | 24                                               | rr                                                                            | 3                                    |

| BIH rel                                                                                               | Branch if IRQ Pin High                               | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 1$                                                                                                                                                                                                                                                                                           | - | -  | -                | - | - | - | REL                                                                                          | 2F                                               | rr                                                                            | 3                                    |

| BIL rel                                                                                               | Branch if IRQ Pin Low                                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? \overline{IRQ} = 0$                                                                                                                                                                                                                                                                                  | - | -  | Ι                | Ι |   | Ι | REL                                                                                          | 2E                                               | rr                                                                            | 3                                    |

| BIT #opr<br>BIT opr<br>BIT opr,<br>BIT opr,X<br>BIT opr,X<br>BIT x<br>BIT opr,SP<br>BIT opr,SP        | Bit Test                                             | (A) & (M)                                                                                                                                                                                                                                                                                                                                     | 0 | _  | _                | ţ | ţ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff                                     | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| BLE opr                                                                                               | Branch if Less Than or Equal To<br>(Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$                                                                                                                                                                                                                                                                           | - | -  | -                | - | - | - | REL                                                                                          | 93                                               | rr                                                                            | 3                                    |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                                                                                                                                                                                                                                                                                             | - | -  | -                | - | - | - | REL                                                                                          | 25                                               | rr                                                                            | 3                                    |

| BLS rel                                                                                               | Branch if Lower or Same                              | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                    | - | -  | -                | - |   | - | REL                                                                                          | 23                                               | rr                                                                            | 3                                    |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                    | - | -  | -                | - | - | - | REL                                                                                          | 91                                               | rr                                                                            | 3                                    |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                       | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                          | 2C                                               | rr                                                                            | 3                                    |

| BMI rel                                                                                               | Branch if Minus                                      | $PC \leftarrow (PC) + 2 + rel? (N) = 1$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                          | 2B                                               | rr                                                                            | 3                                    |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                         | $PC \leftarrow (PC) + 2 + rel? (I) = 1$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                          | 2D                                               | rr                                                                            | 3                                    |

| BNE rel                                                                                               | Branch if Not Equal                                  | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                          | 26                                               | rr                                                                            | 3                                    |

| BPL rel                                                                                               | Branch if Plus                                       | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                       | - | -  | -                | - | - | - | REL                                                                                          | 2A                                               | rr                                                                            | 3                                    |

| BRA rel                                                                                               | Branch Always                                        | $PC \leftarrow (PC) + 2 + rel$                                                                                                                                                                                                                                                                                                                | - | -  | -                | - | - | - | REL                                                                                          | 20                                               | rr                                                                            | 3                                    |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                    | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                         | _ | _  | _                | _ | _ | ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 555555555                            |

| BRN rel                                                                                               | Branch Never                                         | $PC \leftarrow (PC) + 2$                                                                                                                                                                                                                                                                                                                      | - | -  | -                | - | - | - | REL                                                                                          | 21                                               | rr                                                                            | 3                                    |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                      | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                         | _ | _  | _                | _ | _ | Ţ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5555555555                           |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                                | Mn ← 1                                                                                                                                                                                                                                                                                                                                        | _ | _  | _                | _ | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                            | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BSR rel                                                                                               | Branch to Subroutine                                 | $\begin{array}{l} PC \leftarrow (PC) + 2;  push \; (PCL) \\ SP \leftarrow (SP) - 1;  push \; (PCH) \\  SP \leftarrow (SP) - 1 \\  PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                              | _ | _  | _                | _ | _ | - | REL                                                                                          | AD                                               | rr                                                                            | 4                                    |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                          | $\begin{array}{c} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \end{array}$ | _ | _  | _                | _ | _ | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 31<br>41<br>51<br>61<br>71<br>9E61               | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                               | 5<br>4<br>4<br>5<br>4<br>6           |

| CLC                                                                                                   | Clear Carry Bit                                      | C ← 0                                                                                                                                                                                                                                                                                                                                         | - | -  | -                | - | - | 0 | INH                                                                                          | 98                                               |                                                                               | 1                                    |

| CLI                                                                                                   | Clear Interrupt Mask                                 | l ← 0                                                                                                                                                                                                                                                                                                                                         | - | 1- | 0                | - | - | - | INH                                                                                          | 9A                                               |                                                                               | 2                                    |

| Table 4-1. Instruction Set S | Summary ( | (Sheet 2 of 6) |

|------------------------------|-----------|----------------|

|------------------------------|-----------|----------------|

#### 5.3.2.5 LVI Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI trip voltage  $V_{TRIP}$ . The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RSTB) is held low while the SIM counter counts out 4096 2OSCOUT cycles. Sixty-four 2OSCOUT cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur. The SIM actively pulls down the (RSTB) pin for all internal reset sources.

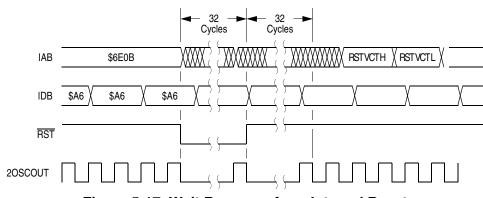

## 5.4 SIM Counter

The SIM counter is used by the power-on reset module (POR) and in stop mode recovery to allow the oscillator time to stabilize before enabling the internal bus (IBUS) clocks. The SIM counter also serves as a prescaler for the computer operating properly module (COP). The SIM counter uses 12 stages for counting, followed by a 13th stage that triggers a reset of SIM counters and supplies the clock for the COP module. The SIM counter is clocked by the falling edge of 2OSCOUT.

#### 5.4.1 SIM Counter During Power-On Reset

The power-on reset module (POR) detects power applied to the MCU. At power-on, the POR circuit asserts the signal PORRST. Once the SIM is initialized, it enables the oscillator to drive the bus clock state machine.

#### 5.4.2 SIM Counter During Stop Mode Recovery

The SIM counter also is used for stop mode recovery. The STOP instruction clears the SIM counter. After an interrupt, break, or reset, the SIM senses the state of the short stop recovery bit, SSREC, in the mask option register. If the SSREC bit is a one, then the stop recovery is reduced from the normal delay of 4096 2OSCOUT cycles down to 32 2OSCOUT cycles. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode. External crystal applications should use the full stop recovery time, that is, with SSREC cleared in the configuration register (CONFIG).

#### 5.4.3 SIM Counter and Reset States

External reset has no effect on the SIM counter. (See 5.6.2 Stop Mode for details.) The SIM counter is free-running after all reset states. (See 5.3.2 Active Resets from Internal Sources for counter control and internal reset recovery sequences.)

## 5.5 Exception Control

Normal, sequential program execution can be changed in three different ways:

- Interrupts

- Maskable hardware CPU interrupts

- Non-maskable software interrupt instruction (SWI)

- Reset

- Break interrupts

#### 5.5.1 Interrupts

An interrupt temporarily changes the sequence of program execution to respond to a particular event. Figure 5-8 flow charts the handling of system interrupts.

#### System Integration Module (SIM)

Figure 5-17. Wait Recovery from Internal Reset

#### 5.6.2 Stop Mode

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

The SIM disables the oscillator signals (OSCOUT and 2OSCOUT) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in the configuration register (CONFIG). If SSREC is set, stop recovery is reduced from the normal delay of 4096 2OSCOUT cycles down to 32. This is ideal for applications using canned oscillators that do not require long start-up times from stop mode.

NOTE

External crystal applications should use the full stop recovery time by clearing the SSREC bit.

A break interrupt during stop mode sets the SIM break stop/wait bit (SBSW) in the break status register (BSR).

The SIM counter is held in reset from the execution of the STOP instruction until the beginning of stop recovery. It is then used to time the recovery period. Figure 5-18 shows stop mode entry timing.

**NOTE** To minimize stop current, all pins configured as inputs should be driven to a logic 1 or logic 0.

| CPUSTOP |                                         |

|---------|-----------------------------------------|

| IAB     | STOP ADDR X STOP ADDR + 1 X SAME X SAME |

| IDB     | PREVIOUS DATA NEXT OPCODE SAME          |

| R/W     | у                                       |

NOTE: Previous data can be operand data or the STOP opcode, depending on the last instruction.

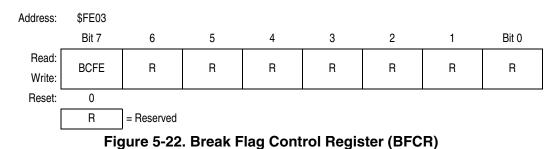

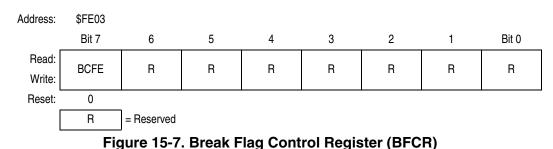

## 5.7.3 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear status bits while the MCU is in a break state.

#### BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

1 = Status bits clearable during break

0 = Status bits not clearable during break

#### Monitor ROM (MON)

Entering monitor mode with  $V_{TST}$  on  $\overline{IRQ}$ , the COP is disabled as long as  $V_{TST}$  is applied to either the  $\overline{IRQ}$  or the  $\overline{RST}$ . (See Chapter 5 System Integration Module (SIM) for more information on modes of operation.)

If entering monitor mode without high voltage on  $\overline{IRQ}$  and reset vector being blank (\$FFFE and \$FFFF) (Table 7-1 condition set 3, where applied voltage is  $V_{DD}$ ), then all port B pin requirements and conditions, including the PTB3 frequency divisor selection, are not in effect. This is to reduce circuit requirements when performing in-circuit programming.

Entering monitor mode with the reset vector being blank, the COP is always disabled regardless of the state of IRQ or the RST.

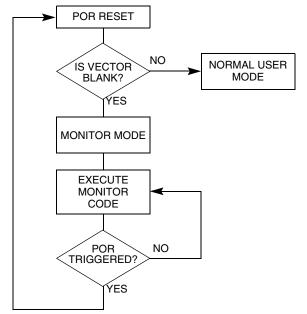

Figure 7-2. shows a simplified diagram of the monitor mode entry when the reset vector is blank and  $\overline{IRQ} = V_{DD}$ . An OSC1 frequency of 9.8304MHz is required for a baud rate of 9600.

Figure 7-2. Low-Voltage Monitor Mode Entry Flowchart

Enter monitor mode with the pin configuration shown above by pulling  $\overline{RST}$  low and then high. The rising edge of  $\overline{RST}$  latches monitor mode. Once monitor mode is latched, the values on the specified pins can change.

Once out of reset, the MCU waits for the host to send eight security bytes. (See 7.4 Security.) After the security bytes, the MCU sends a break signal (10 consecutive logic zeros) to the host, indicating that it is ready to receive a command. The break signal also provides a timing reference to allow the host to determine the necessary baud rate.

In monitor mode, the MCU uses different vectors for reset, SWI, and break interrupt. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

Input/Output (I/O) Ports

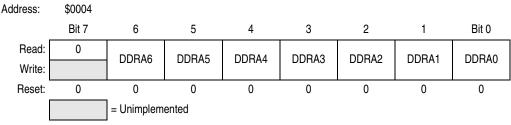

## 10.2.2 Data Direction Register A (DDRA)

Data direction register A determines whether each port A pin is an input or an output. Writing a one to a DDRA bit enables the output buffer for the corresponding port A pin; a zero disables the output buffer.

#### Figure 10-3. Data Direction Register A (DDRA)

#### DDRA[6:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[6:0], configuring all port A pins as inputs.

1 = Corresponding port A pin configured as output

0 = Corresponding port A pin configured as input

**NOTE** Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

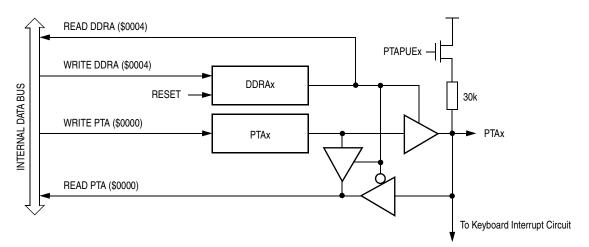

Figure 10-4 shows the port A I/O logic.

#### Figure 10-4. Port A I/O Circuit

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

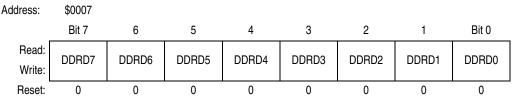

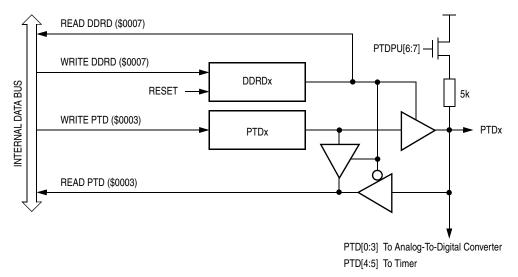

## 10.4.2 Data Direction Register D (DDRD)

Data direction register D determines whether each port D pin is an input or an output. Writing a one to a DDRD bit enables the output buffer for the corresponding port D pin; a zero disables the output buffer.

Figure 10-10. Data Direction Register D (DDRD)

#### DDRD[7:0] — Data Direction Register D Bits

These read/write bits control port D data direction. Reset clears DDRD[7:0], configuring all port D pins as inputs.

1 = Corresponding port D pin configured as output

0 = Corresponding port D pin configured as input

NOTE

Avoid glitches on port D pins by writing to the port D data register before changing data direction register D bits from 0 to 1. Figure 10-11 shows the port D I/O logic.

#### Figure 10-11. Port D I/O Circuit

When DDRDx is a 1, reading address \$0003 reads the PTDx data latch. When DDRDx is a 0, reading address \$0003 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 10-4 summarizes the operation of the port D pins.

## 11.3.1 IRQ Pin

A zero on the IRQ pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

If the MODE bit is set, the IRQ pin is both falling-edge-sensitive and low-level-sensitive. With MODE set, both of the following actions must occur to clear IRQ:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the latch. Software may generate the interrupt acknowledge signal by writing a logic one to the ACK bit in the interrupt status and control register (INTSCR). The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to the ACK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to the ACK bit latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the vector address at locations \$FFFA and \$FFFB.

- Return of the IRQ pin to logic one As long as the IRQ pin is at logic zero, IRQ remains active.

The vector fetch or software clear and the return of the  $\overline{IRQ}$  pin to logic one may occur in any order. The interrupt request remains pending as long as the  $\overline{IRQ}$  pin is at logic zero. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

If the MODE bit is clear, the IRQ pin is falling-edge-sensitive only. With MODE clear, a vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH or BIL instruction to read the logic level on the IRQ pin.

#### NOTE

When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

#### NOTE

An internal pull-up resistor to  $V_{DD}$  is connected to the  $\overline{IRQ}$  pin; this can be disabled by setting the IRQPUD bit in the CONFIG2 register (\$001E).

## 11.4 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear the latches during the break state. (See Chapter 5 System Integration Module (SIM).)

To allow software to clear the IRQ latch during a break interrupt, write a one to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latches during the break state, write a zero to the BCFE bit. With BCFE at zero (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

# Chapter 12 Keyboard Interrupt Module (KBI)

## **12.1 Introduction**

The keyboard interrupt module (KBI) provides seven independently maskable external interrupts which are accessible via PTA0–PTA6 pins.

## 12.2 Features

Features of the keyboard interrupt module include the following:

- Seven keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Software configurable pull-up device if input pin is configured as input port bit

- Programmable edge-only or edge- and level- interrupt sensitivity

- Exit from low-power modes

| Addr.  | Register Name                                   |                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1       | Bit 0 |

|--------|-------------------------------------------------|-----------------|-------|-------|-------|-------|-------|-------|---------|-------|

|        |                                                 | Read:           | 0     | 0     | 0     | 0     | KEYF  | 0     | IMASKK  | MODEK |

| \$001A | Keyboard Status and Control<br>Register (KBSCR) | Write:          |       |       |       |       |       | ACKK  | INIAGRA | WODER |

|        |                                                 | Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0       | 0     |

|        |                                                 | Read:           | 0     | KBIE6 | KBIE5 | KBIE4 | KBIE3 | KBIE2 | KBIE1   | KBIE0 |

| \$001B | Keyboard Interrupt Enable<br>Register (KBIER)   | Write:          |       | NDIEO | NDIED | NDIE4 | NDIES | NDIEZ | NDIEI   | NDIEU |

|        |                                                 | Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0       | 0     |

|        |                                                 | = Unimplemented |       |       |       |       |       |       |         |       |

#### Figure 12-1. KBI I/O Register Summary

## 12.3 I/O Pins

The seven keyboard interrupt pins are shared with standard port I/O pins. The full name of the KBI pins are listed in Table 12-1. The generic pin name appear in the text that follows.

#### Table 12-1. Pin Name Conventions

| KBI<br>Generic Pin Name | Full MCU Pin Name              | Pin Selected for KBI Function<br>by KBIEx Bit in KBIER |

|-------------------------|--------------------------------|--------------------------------------------------------|

| KBI0–KBI5               | PTA0/KBI0–PTA5/KBI5            | KBIE0–KBIE5                                            |

| KBI6                    | RCCLK/PTA6/KBI6 <sup>(1)</sup> | KBIE6                                                  |

1. RCCLK/PTA6/KBI6 pin is only available on MC68HRC908JL3E/JK3E/JK1E devices (RC option).

#### **Computer Operating Properly (COP)**

#### 13.7.1 Wait Mode

The COP continues to operate during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter in a CPU interrupt routine.

#### 13.7.2 Stop Mode

Stop mode turns off the 2OSCOUT input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

## 13.8 COP Module During Break Mode

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

# Chapter 14 Low Voltage Inhibit (LVI)

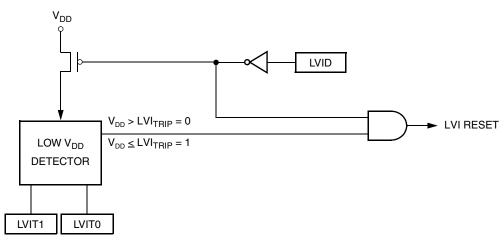

## 14.1 Introduction

This section describes the low-voltage inhibit module (LVI), which monitors the voltage on the  $V_{DD}$  pin and generates a reset when the  $V_{DD}$  voltage falls to the LVI trip (LVI<sub>TRIP</sub>) voltage.

## 14.2 Features

Features of the LVI module include the following:

- Selectable LVI trip voltage

- Selectable LVI circuit disable

## 14.3 Functional Description

Figure 14-1 shows the structure of the LVI module. The LVI is enabled after a reset. The LVI module contains a bandgap reference circuit and comparator. Setting LVI disable bit (LVID) disables the LVI to monitor  $V_{DD}$  voltage. The LVI trip voltage selection bits (LVIT1, LVIT0) determine at which  $V_{DD}$  level the LVI module should take actions.

The LVI module generates one output signal:

**LVI Reset** — an reset signal will be generated to reset the CPU when  $V_{DD}$  drops to below the set trip point.

Figure 14-1. LVI Module Block Diagram

# NP

#### **Break Module (BREAK)**

| Addr.        | Register Name                  |                 | Bit 7 | 6          | 5     | 4     | 3          | 2     | 1                | Bit 0 |

|--------------|--------------------------------|-----------------|-------|------------|-------|-------|------------|-------|------------------|-------|

| \$FE00       | Break Status Register<br>(BSR) | Read:<br>Write: | R     | R          | R     | R     | R          | R     | SBSW<br>See note | R     |

|              | ()                             | Reset:          |       |            |       |       |            |       | 0                |       |

| \$FE03       | Break Flag Control<br>Register | Read:<br>Write: | BCFE  | R          | R     | R     | R          | R     | R                | R     |

|              | (BFCR)                         | Reset:          | 0     |            |       |       |            |       |                  |       |

| \$FE0C       | Break Address High<br>Register | Read:<br>Write: | Bit15 | Bit14      | Bit13 | Bit12 | Bit11      | Bit10 | Bit9             | Bit8  |

|              | (BRKH)                         | Reset:          | 0     | 0          | 0     | 0     | 0          | 0     | 0                | 0     |

| \$FE0D       | Break Address low<br>Register  | Read:<br>Write: | Bit7  | Bit6       | Bit5  | Bit4  | Bit3       | Bit2  | Bit1             | Bit0  |

|              | (BRKL)                         | Reset:          | 0     | 0          | 0     | 0     | 0          | 0     | 0                | 0     |

|              | Break Status and Control       | Read:           | BRKE  | BRKA       | 0     | 0     | 0          | 0     | 0                | 0     |

| \$FE0E       | Register                       | Write:          | DAKE  | DHKA       |       |       |            |       |                  |       |

|              | (BRKSCR)                       | Reset:          | 0     | 0          | 0     | 0     | 0          | 0     | 0                | 0     |

| Note: Writir | ng a 0 clears SBSW.            |                 |       | = Unimplem | ented | R     | = Reserved |       |                  |       |

#### Figure 15-2. Break I/O Register Summary

#### **15.3.1 Flag Protection During Break Interrupts**

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. (See 5.7.3 Break Flag Control Register (BFCR) and see the Break Interrupts subsection for each module.)

## 15.3.2 CPU During Break Interrupts

The CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD (\$FEFC:\$FEFD in monitor mode)

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

## 15.3.3 TIM During Break Interrupts

A break interrupt stops the timer counter.

## 15.3.4 COP During Break Interrupts

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

## 15.4.4 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear status bits while the MCU is in a break state.

#### BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

#### 15.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power-consumption standby modes.

#### 15.5.1 Wait Mode

If enabled, the break module is active in wait mode. In the break routine, the user can subtract one from the return address on the stack if SBSW is set (see 5.6 Low-Power Modes). Clear the SBSW bit by writing zero to it.

#### 15.5.2 Stop Mode

A break interrupt causes exit from stop mode and sets the SBSW bit in the break status register. See 5.7 SIM Registers.

**Electrical Specifications**

#### Table 16-4. DC Electrical Characteristics (5V) (Continued)

| Characteristic <sup>(1)</sup> | Symbol     | Min | Typ <sup>(2)</sup> | Мах | Unit |

|-------------------------------|------------|-----|--------------------|-----|------|

| LVI reset voltage             | $V_{LVR5}$ | 3.6 | 4.0                | 4.4 | V    |

1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted. 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

3. Run (operating) I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 4MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run I<sub>DD</sub>. Measured with all modules enabled.

4. Wait I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 4MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

5. Stop I<sub>DD</sub> measured with OSC1 grounded; no port pins sourcing current. LVI is disabled.

6. Maximum is highest voltage that POR is guaranteed.

7. If minimum V<sub>DD</sub> is not reached before the internal POR reset is released, RST must be driven low externally until minimum V<sub>DD</sub> is reached.

8.  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0$  V.

## 16.6 5V Control Timing

#### Table 16-5. Control Timing (5V)

| Characteristic <sup>(1)</sup>               | Symbol           | Min | Max | Unit |

|---------------------------------------------|------------------|-----|-----|------|

| Internal operating frequency <sup>(2)</sup> | f <sub>OP</sub>  | —   | 8   | MHz  |

| RST input pulse width low <sup>(3)</sup>    | t <sub>IRL</sub> | 750 |     | ns   |

1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ ; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{SS}$ , unless otherwise noted.

2. Some modules may require a minimum frequency greater than dc for proper operation; see appropriate table for this information.

3. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

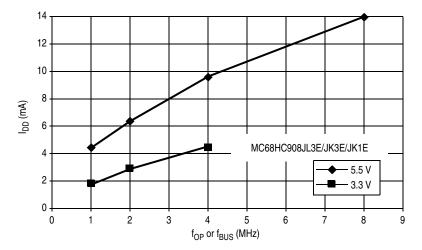

## **16.11 Typical Supply Currents**

Figure 16-3. Typical Operating I<sub>DD</sub> (MC68HC908JL3E/JK3E/JK1E), with All Modules Turned On (25°C)

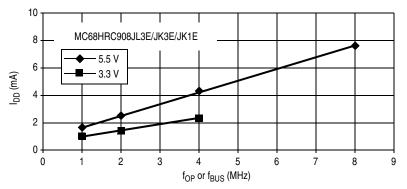

Figure 16-4. Typical Operating I<sub>DD</sub> (MC68HRC908JL3E/JK3E/JK1E), with All Modules Turned On (25°C)

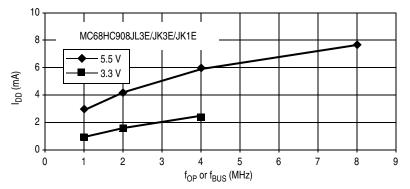

Figure 16-5. Typical Wait Mode I<sub>DD</sub> (MC68HC908JL3E/JK3E/JK1E), with All Modules Turned Off ( $25^{\circ}$ C)

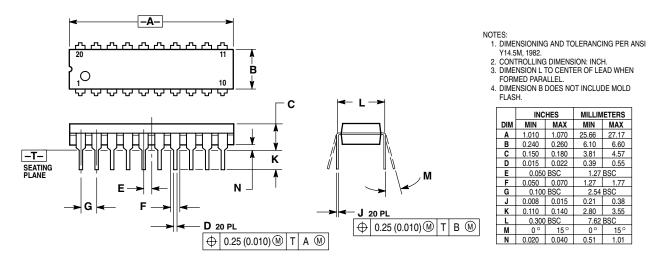

# Chapter 17 Mechanical Specifications

## 17.1 Introduction

This section gives the dimensions for:

- 20-pin plastic dual in-line package (case #738)

- 20-pin small outline integrated circuit package (case #751D)

- 28-pin plastic dual in-line package (case #710)

- 28-pin small outline integrated circuit package (case #751F)

- 48-pin low-profile quad flat pack (case #932)

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Sales Office.

## 17.2 Package Dimensions

Refer to the following pages for detailed package dimensions.

20-Pin PDIP (Case #738)

## MC68HC908KL3E

## **MC68HC908KK3E**

Figure C-3. 20-Pin PDIP/SOIC Pin Assignment