Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 23                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 12x8b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 28-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcr908jl3emdwe |

#### **General Description**

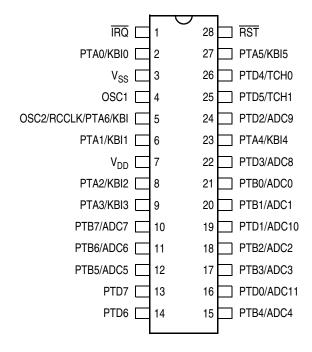

# 1.4 Pin Assignments

MC68H(R)C908JL3E

Figure 1-2. 28-Pin PDIP/SOIC Pin Assignment

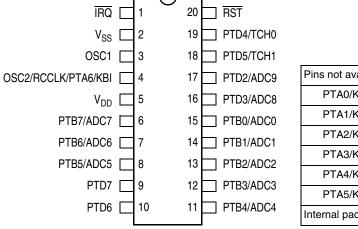

| Pins not available on 20-pin packages |            |  |  |  |  |

|---------------------------------------|------------|--|--|--|--|

| PTA0/KBI0                             | PTD0/ADC11 |  |  |  |  |

| PTA1/KBI1                             | PTD1/ADC10 |  |  |  |  |

| PTA2/KBI2                             |            |  |  |  |  |

| PTA3/KBI3                             |            |  |  |  |  |

| PTA4/KBI4                             |            |  |  |  |  |

| PTA5/KBI5                             |            |  |  |  |  |

| Internal pads are un                  | connected. |  |  |  |  |

MC68H(R)C908JK3E/JK1E

Figure 1-3. 20-Pin PDIP/SOIC Pin Assignment

## Memory

| Addr.                           | Register Name                                   |                 | Bit 7        | 6             | 5            | 4            | 3              | 2          | 1        | Bit 0  |

|---------------------------------|-------------------------------------------------|-----------------|--------------|---------------|--------------|--------------|----------------|------------|----------|--------|

|                                 |                                                 | Read:           | 0            | 0             | 0            | 0            | KEYF           | 0          | IMACIZIZ | MODEK  |

| \$001A                          | Keyboard Status and Control<br>Register (KBSCR) | Write:          |              |               |              |              |                | ACKK       | IMASKK   | MODEK  |

|                                 | g.s.s. (2001.)                                  |                 | 0            | 0             | 0            | 0            | 0              | 0          | 0        | 0      |

| ****                            | Keyboard Interrupt Enable                       | Read:           | 0            | KBIE6         | KBIE5        | KBIE4        | KBIE3          | KBIE2      | KBIE1    | KBIE0  |

| \$001B Register (KBIER)         | Write:                                          |                 |              |               |              |              |                | •          |          |        |

|                                 |                                                 | Reset:          | 0            | 0             | 0            | 0            | 0              | 0          | 0        | 0      |

| \$001C                          | Unimplemented                                   | Read:           |              |               |              |              |                |            |          |        |

|                                 | Unimplemented                                   | Write:          |              |               |              |              |                |            |          |        |

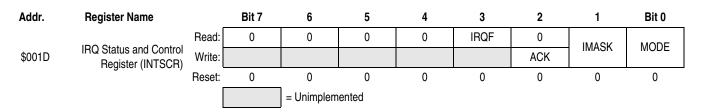

|                                 | 10000                                           | Read:           | 0            | 0             | 0            | 0            | IRQF           | 0          |          |        |

| \$001D                          | IRQ Status and Control<br>Register              | Write:          | 0            | 0             |              | 0            | IIIQI          | ACK        | IMASK    | MODE   |

| φοστΒ                           | (INTSCR)                                        | Reset:          | 0            | 0             | 0            | 0            | 0              | 0          | 0        | 0      |

|                                 |                                                 | Read:           |              |               |              |              |                |            |          | -      |

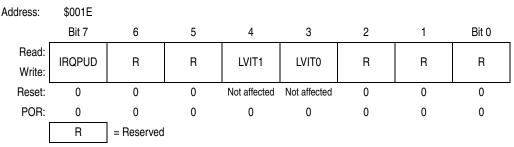

| \$001E                          | Configuration Register 2                        | Write:          | IRQPUD       | R             | R            | LVIT1        | LVIT0          | R          | R        | R      |

| ,                               | (CONFIG2) <sup>†</sup>                          | Reset:          | 0            | 0             | 0            | 0*           | 0*             | 0          | 0        | 0      |

|                                 |                                                 | Read:           | 00000        | _             | _            | 1145         |                | 20050      | 0700     | 0000   |

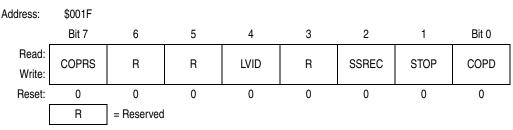

| \$001F Configuration Register 1 | Write:                                          | COPRS           | R            | R             | LVID         | R            | SSREC          | STOP       | COPD     |        |

|                                 | (CONFIG1) <sup>†</sup>                          | Reset:          | 0            | 0             | 0            | 0            | 0              | 0          | 0        | 0      |

| † One-tii                       | me writable register after each r               | eset. * L'      | VIT1 and LVI | T0 reset to 0 | by a power-o | n reset (POR | ) only.        |            |          |        |

|                                 |                                                 |                 |              | T             | 1            | T            | T              | T          |          |        |

|                                 | TIM Status and Control                          | Read:           | TOF          | TOIE          | TSTOP        | 0            | 0              | PS2        | PS1      | PS0    |

| \$0020                          | \$0020 Register (TSC)                           | Write:          | 0            |               | 10101        | TRST         |                |            |          | . 00   |

|                                 |                                                 | Reset:          | 0            | 0             | 1            | 0            | 0              | 0          | 0        | 0      |

|                                 | TIM Counter Register High                       | Read:           | Bit15        | Bit14         | Bit13        | Bit12        | Bit11          | Bit10      | Bit9     | Bit8   |

| \$0021                          | (TCNTH)                                         | Write:          |              |               |              |              |                |            |          |        |

|                                 |                                                 | Reset:          | 0            | 0             | 0            | 0            | 0              | 0          | 0        | 0      |

|                                 | TIM Counter Register                            | Read:           | Bit7         | Bit6          | Bit5         | Bit4         | Bit3           | Bit2       | Bit1     | Bit0   |

| \$0022                          | Low (TCNTL)                                     | Write:          |              |               |              |              |                |            |          |        |

|                                 |                                                 | Reset:          | 0            | 0             | 0            | 0            | 0              | 0          | 0        | 0      |

| ФОООО                           | TIM Counter Modulo Register                     | Read:           | Bit15        | Bit14         | Bit13        | Bit12        | Bit11          | Bit10      | Bit9     | Bit8   |

| \$0023                          | High (TMODH)                                    | Write:          | 1            | <u> </u><br>1 | 1            | 1            | 1              | 1          | 1        | 1      |

|                                 |                                                 | Reset:<br>Read: | - 1          | <u> </u>      | 1            | <u> </u>     | <u> </u>       | ı          | ı        |        |

| \$0024                          | TIM Counter Modulo Register                     | Write:          | Bit7         | Bit6          | Bit5         | Bit4         | Bit3           | Bit2       | Bit1     | Bit0   |

| ψυυΖ4                           | Low (TMODL)                                     | Reset:          | 1            | 1             | 1            | 1            | 1              | 1          | 1        | 1      |

|                                 |                                                 | Read:           | CH0F         | <u>'</u>      | <u>'</u>     | <u>'</u>     | <u>'</u>       | '          | '        |        |

| \$0025                          | TIM Channel 0 Status and                        | Write:          | 0            | CH0IE         | MS0B         | MS0A         | ELS0B          | ELS0A      | TOV0     | CH0MAX |

| ψ <b>υυ</b> Ξυ                  | Control Register (TSC0)                         | Reset:          | 0            | 0             | 0            | 0            | 0              | 0          | 0        | 0      |

|                                 |                                                 | Read:           |              |               |              |              |                |            |          |        |

| \$0026                          | TIM Channel 0 Register High                     | Write:          | Bit15        | Bit14         | Bit13        | Bit12        | Bit11          | Bit10      | Bit9     | Bit8   |

|                                 | (TCH0H)                                         | Reset:          |              | ı             | I            | Indetermina  | te after reset | 1          |          |        |

|                                 |                                                 |                 |              | = Unimplem    | nented       |              | R              | = Reserved |          |        |

|                                 |                                                 | L               |              | •             |              |              |                |            |          |        |

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 4)

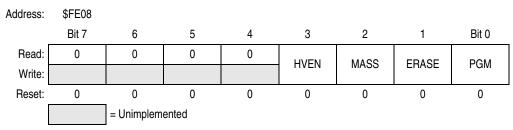

# 2.7 Flash Control Register

The Flash Control Register controls Flash program and erase operations.

Figure 2-4. Flash Control Register (FLCR)

## **HVEN** — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM=1 or ERASE=1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation or page erase operation when the ERASE bit is set.

- 1 = Mass erase operation selected

- 0 = Page erase operation selected

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. This bit and the PGM bit should not be set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation not selected

## **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. This bit and the ERASE bit should not be set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation not selected

# 2.10 Flash Program Operation

Programming of the Flash memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0 or \$XXE0. Use this step-by-step procedure to program a row of Flash memory (Figure 2-5 shows a flowchart of the programming algorithm):

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Write any data to any Flash location within the address range of the row to be programmed.

- 3. Wait for a time,  $t_{nvs}$  (10 $\mu$ s).

- 4. Set the HVEN bit.

- 5. Wait for a time,  $t_{pqs}$  (5µs).

- 6. Write data to the byte being programmed.

- 7. Wait for time, t<sub>PROG</sub> (30μs).

- 8. Repeat step 6 and 7 until all the bytes within the row are programmed.

- 9. Clear the PGM bit.

- 10. Wait for time,  $t_{nvh}$  (5µs).

- Clear the HVEN bit.

- 12. After time,  $t_{rcv}$  (1 $\mu$ s), the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

The time between each Flash address change (step 6 to step 6), or the time between the last Flash addressed programmed to clearing the PGM bit (step 6 to step 10), must not exceed the maximum programming time,  $t_{PBOG}$  max.

#### NOTE

Programming and erasing of Flash locations cannot be performed by code being executed from the Flash memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps.

# 2.11 Flash Protection

Due to the ability of the on-board charge pump to erase and program the Flash memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a Flash Block Protect Register (FLBPR). The FLBPR determines the range of the Flash memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the Flash memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

#### **System Integration Module (SIM)**

#### IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 5-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 0 to 6 — Always read 0

#### 5.5.2.3 Interrupt Status Register 3

| Address: | \$FE06 |            |   |   |   |   |   |       |

|----------|--------|------------|---|---|---|---|---|-------|

|          | Bit 7  | 6          | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Read:    | 0      | 0          | 0 | 0 | 0 | 0 | 0 | IF15  |

| Write:   | R      | R          | R | R | R | R | R | R     |

| Reset:   | 0      | 0          | 0 | 0 | 0 | 0 | 0 | 0     |

|          | R      | = Reserved |   |   |   |   |   |       |

Figure 5-14. Interrupt Status Register 3 (INT3)

#### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 5-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

## Bit 1 to 7 — Always read 0

#### 5.5.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

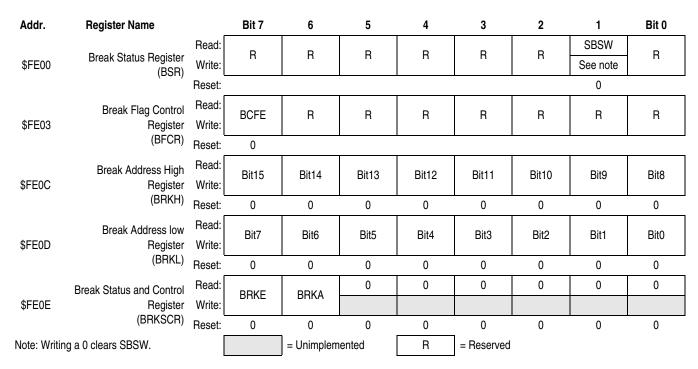

#### 5.5.4 Break Interrupts

The break module can stop normal program flow at a software-programmable break point by asserting its break interrupt output. (See Chapter 15 Break Module (BREAK).) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

## 5.5.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

## 5.6 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low-power-consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

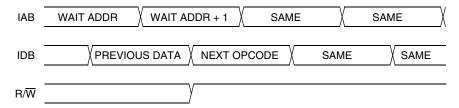

#### 5.6.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 5-15 shows the timing for wait mode entry.

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset or break. A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the break status register (BSR). If the COP disable bit, COPD, in the mask option register is zero, then the computer operating properly module (COP) is enabled and remains active in wait mode.

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

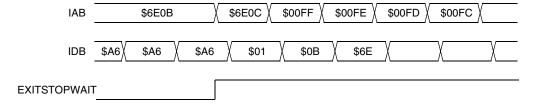

Figure 5-15. Wait Mode Entry Timing

Figure 5-16 and Figure 5-17 show the timing for WAIT recovery.

NOTE: EXITSTOPWAIT =  $\overline{RST}$  pin OR CPU interrupt OR break interrupt

Figure 5-16. Wait Recovery from Interrupt or Break

# Chapter 7 Monitor ROM (MON)

#### 7.1 Introduction

This section describes the monitor ROM (MON) and the monitor mode entry methods. The monitor ROM allows complete testing of the MCU through a single-wire interface with a host computer. This mode is also used for programming and erasing of Flash memory in the MCU. Monitor mode entry can be achieved without use of the higher test voltage, V<sub>TST</sub>, as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

#### 7.2 Features

Features of the monitor ROM include the following:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between monitor ROM and host computer

- Standard mark/space non-return-to-zero (NRZ) communication with host computer

- Execution of code in RAM or Flash

- Flash memory security feature<sup>(1)</sup>

- Flash memory programming interface

- 960 bytes monitor ROM code size

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage, V<sub>TST</sub>, is applied to IRQ

# 7.3 Functional Description

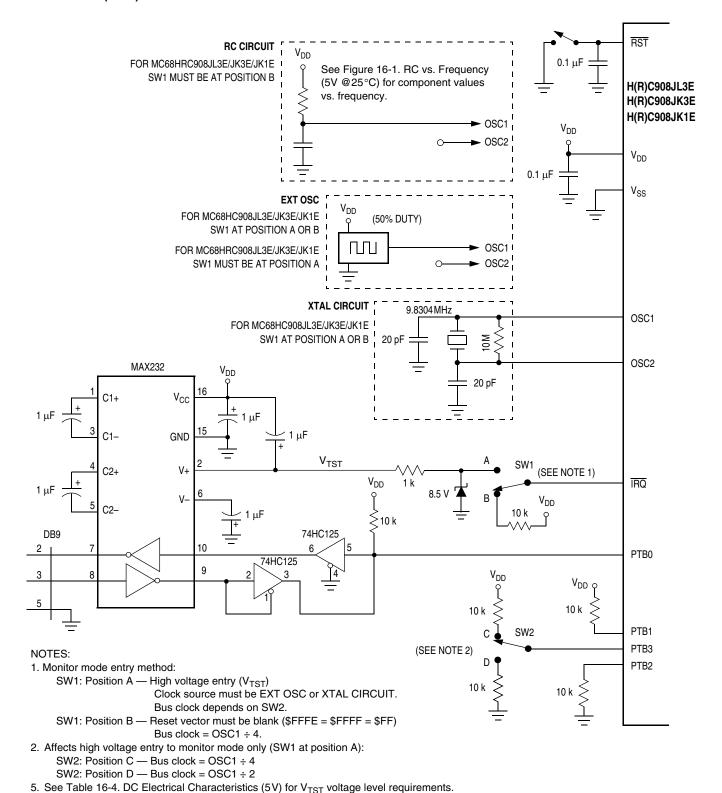

The monitor ROM receives and executes commands from a host computer. Figure 7-1 shows a example circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute host-computer code in RAM while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTB0 pin. A level-shifting and multiplexing interface is required between PTB0 and the host computer. PTB0 is used in a wired-OR configuration and requires a pull-up resistor.

MC68HC908JL3E Family Data Sheet, Rev. 4

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the Flash difficult for unauthorized users.

#### **Monitor ROM (MON)**

Figure 7-1. Monitor Mode Circuit

MC68HC908JL3E Family Data Sheet, Rev. 4

Table 7-2 is a summary of the vector differences between user mode and monitor mode.

**Table 7-2. Monitor Mode Vector Differences**

|         | Functions               |                         |                        |                         |                        |                       |                      |  |  |

|---------|-------------------------|-------------------------|------------------------|-------------------------|------------------------|-----------------------|----------------------|--|--|

| Modes   | СОР                     | Reset<br>Vector<br>High | Reset<br>Vector<br>Low | Break<br>Vector<br>High | Break<br>Vector<br>Low | SWI<br>Vector<br>High | SWI<br>Vector<br>Low |  |  |

| User    | Enabled                 | \$FFFE                  | \$FFFF                 | \$FFFC                  | \$FFFD                 | \$FFFC                | \$FFFD               |  |  |

| Monitor | Disabled <sup>(1)</sup> | \$FEFE                  | \$FEFF                 | \$FEFC                  | \$FEFD                 | \$FEFC                | \$FEFD               |  |  |

<sup>1.</sup> If the high voltage  $(V_{TST})$  is removed from the  $\overline{IRQ}$  pin or the  $\overline{RST}$  pin, the SIM asserts its COP enable output. The COP is a mask option enabled or disabled by the COPD bit in the configuration register.

When the host computer has completed downloading code into the MCU RAM, the host then sends a RUN command, which executes an RTI, which sends control to the address on the stack pointer.

#### 7.3.2 Baud Rate

The communication baud rate is dependant on oscillator frequency. The state of PTB3 also affects baud rate if entry to monitor mode is by  $\overline{IRQ} = V_{TST}$ . When PTB3 is high, the divide by ratio is 1024. If the PTB3 pin is at logic zero upon entry into monitor mode, the divide by ratio is 512.

Table 7-3. Monitor Baud Rate Selection

| Monitor Mode<br>Entry By:  | Input Clock<br>Frequency | РТВ3 | Baud Rate |

|----------------------------|--------------------------|------|-----------|

|                            | 4.9152 MHz               | 0    | 9600 bps  |

| $\overline{IRQ} = V_{TST}$ | 9.8304 MHz               | 1    | 9600 bps  |

|                            | 4.9152 MHz               | 1    | 4800 bps  |

| Blank reset vector,        | 9.8304 MHz               | Х    | 9600 bps  |

| $\overline{IRQ} = V_{DD}$  | 4.9152 MHz               | Х    | 4800 bps  |

Freescale Semiconductor 75

#### **Monitor ROM (MON)**

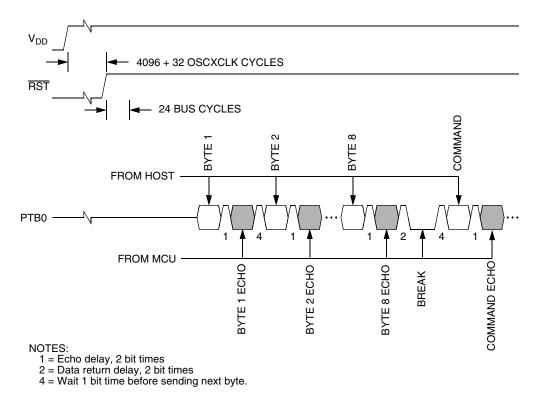

Figure 7-7. Monitor Mode Entry Timing

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6—\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a Flash location returns an invalid value and trying to execute code from Flash causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

#### NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$80 is set. If it is, then the correct security code has been entered and Flash can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the Flash module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

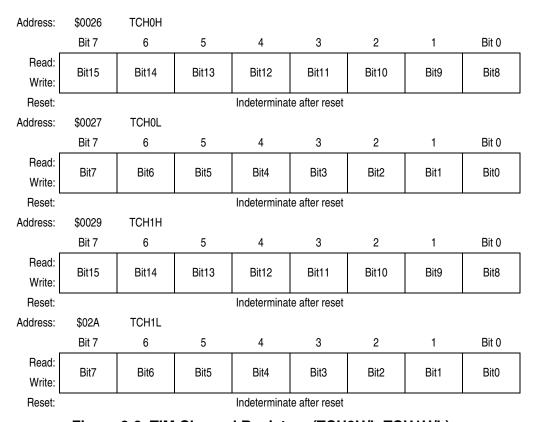

# 8.9.5 TIM Channel Registers (TCH0H/L:TCH1H/L)

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Figure 8-9. TIM Channel Registers (TCH0H/L:TCH1H/L)

Freescale Semiconductor 95

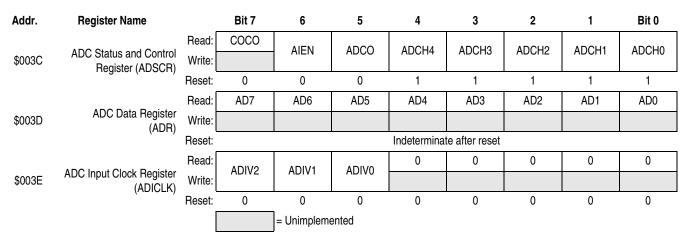

# Chapter 9 Analog-to-Digital Converter (ADC)

## 9.1 Introduction

This section describes the 12-channel, 8-bit linear successive approximation analog-to-digital converter (ADC).

#### 9.2 Features

Features of the ADC module include:

- 12 channels with multiplexed input

- Linear successive approximation with monotonicity

- 8-bit resolution

- Single or continuous conversion

- Conversion complete flag or conversion complete interrupt

- Selectable ADC clock

Figure 9-1. ADC I/O Register Summary

# 9.3 Functional Description

Twelve ADC channels are available for sampling external sources at pins PTB0–PTB7 and PTD0–PTD3. An analog multiplexer allows the single ADC converter to select one of the 12 ADC channels as ADC voltage input (ADCVIN). ADCVIN is converted by the successive approximation register-based counters. The ADC resolution is 8 bits. When the conversion is completed, ADC puts the result in the ADC data register and sets a flag or generates an interrupt. Figure 9-2 shows a block diagram of the ADC.

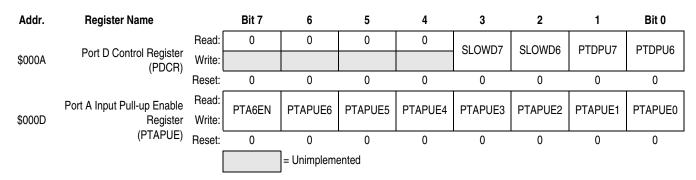

#### Input/Output (I/O) Ports

Figure 10-1. I/O Port Register Summary

Table 10-1. Port Control Register Bits Summary

| Down Dia |     | 222   |            | Module Control                    |                 | D'                             |

|----------|-----|-------|------------|-----------------------------------|-----------------|--------------------------------|

| Port     | Bit | DDR   | Module     | Register                          | Control Bit     | Pin                            |

|          | 0   | DDRA0 |            | LADIED (\$004D)                   | KBIE0           | PTA0/KBI0                      |

|          | 1   | DDRA1 |            |                                   | KBIE1           | PTA1/KBI1                      |

|          | 2   | DDRA2 | KBI        |                                   | KBIE2           | PTA2/KBI2                      |

| ۸        | 3   | DDRA3 | KDI        | KBIER (\$001B)                    | KBIE3           | PTA3/KBI3                      |

| Α        | 4   | DDRA4 |            |                                   | KBIE4           | PTA4/KBI4                      |

|          | 5   | DDRA5 |            |                                   | KBIE5           | PTA5/KBI5                      |

|          | 6   | DDRA6 | OSC<br>KBI | PTAPUE (\$000D)<br>KBIER (\$001B) | PTA6EN<br>KBIE6 | RCCLK/PTA6/KBI6 <sup>(1)</sup> |

|          | 0   | DDRB0 |            |                                   |                 | PTB0/ADC0                      |

|          | 1   | DDRB1 | ADC        | ADSCR (\$003C)                    | ADCH[4:0]       | PTB1/ADC1                      |

|          | 2   | DDRB2 |            |                                   |                 | PTB2/ADC2                      |

|          | 3   | DDRB3 |            |                                   |                 | PTB3/ADC3                      |

| В        | 4   | DDRB4 |            |                                   |                 | PTB4/ADC4                      |

|          | 5   | DDRB5 |            |                                   |                 | PTB5/ADC5                      |

|          | 6   | DDRB6 |            |                                   |                 | PTB6/ADC6                      |

|          | 7   | DDRB7 |            |                                   |                 | PTB7/ADC7                      |

|          | 0   | DDRD0 |            |                                   |                 | PTD0/ADC11                     |

|          | 1   | DDRD1 | ADC        | ADCCD (\$002C)                    | ADCH[4:0]       | PTD1/ADC10                     |

|          | 2   | DDRD2 | ADC        | ADSCR (\$003C)                    | ADCH[4:0]       | PTD2/ADC9                      |

| D        | 3   | DDRD3 |            |                                   |                 | PTD3/ADC8                      |

| D        | 4   | DDRD4 | TIM        | TSC0 (\$0025)                     | ELS0B:ELS0A     | PTD4/TCH0                      |

|          | 5   | DDRD5 | I IIVI     | TSC1 (\$0028)                     | ELS1B:ELS1A     | PTD5/TCH1                      |

|          | 6   | DDRD6 | _          | _                                 | _               | PTD6                           |

|          | 7   | DDRD7 | _          | _                                 | _               | PTD7                           |

RCCLK/PTA6/KBI6 pin is only available on MC68HRC908JL3E/JK3E/JK1E devices (RC option); PTAPUE register has priority control over the port pin. RCCLK/PTA6/KBI6 is the OSC2 pin on MC68HC908JL3E/JK3E/JK1E devices (X-TAL option).

MC68HC908JL3E Family Data Sheet, Rev. 4

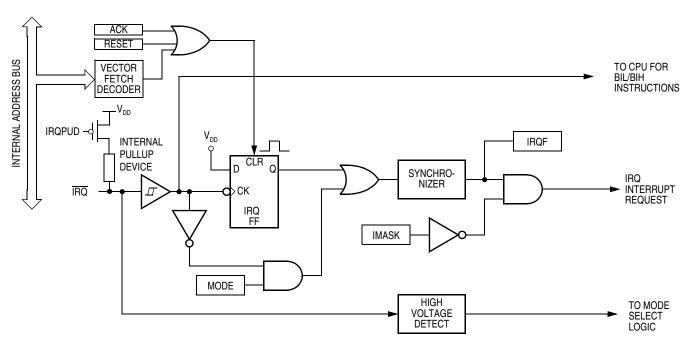

#### External Interrupt (IRQ)

The vector fetch or software clear may occur before or after the interrupt pin returns to one. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

When set, the IMASK bit in the INTSCR mask all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

#### NOTE

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests. See 5.5 Exception Control.

Figure 11-1. IRQ Module Block Diagram

Figure 11-2. IRQ I/O Register Summary

**Keyboard Interrupt Module (KBI)**

# 12.4 Functional Description

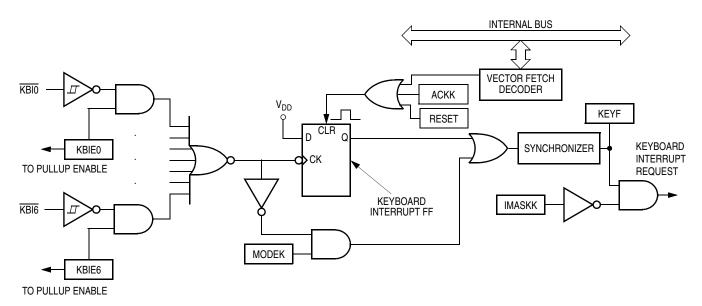

Figure 12-2. Keyboard Interrupt Block Diagram

Writing to the KBIE6–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin in port A also enables its internal pull-up device irrespective of PTAPUEx bits in the port A input pull-up enable register (see 10.2.3 Port A Input Pull-up Enable Register (PTAPUE)). A logic 0 applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

- If the keyboard interrupt is falling edge- and low level-sensitive, an interrupt request is present as long as any keyboard pin is low.

If the MODEK bit is set, the keyboard interrupt pins are both falling edge- and low level-sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register KBSCR. The ACKK bit is useful in applications that poll the keyboard interrupt pins and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt pins. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt pins to logic 1 As long as any enabled keyboard interrupt pin is at 0, the keyboard interrupt remains set.

Low Voltage Inhibit (LVI)

# 14.4 LVI Control Register (CONFIG2/CONFIG1)

The LVI module is controlled by three bits in the configuration registers, CONFIG1 and CONFIG2.

Figure 14-2. Configuration Register 2 (CONFIG2)

Figure 14-3. Configuration Register 1 (CONFIG1)

## LVID — Low Voltage Inhibit Disable Bit

- 1 = Low voltage inhibit disabled

- 0 = Low voltage inhibit enabled

#### LVIT1, LVIT0 — LVI Trip Voltage Selection

These two bits determine at which level of V<sub>DD</sub> the LVI module will come into action. LVIT1 and LVIT0 are cleared by a Power-On Reset only.

| LVIT1 | LVIT0 | Trip Voltage <sup>(1)</sup> | Comments                          |

|-------|-------|-----------------------------|-----------------------------------|

| 0     | 0     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 0     | 1     | V <sub>LVR3</sub> (2.4V)    | For V <sub>DD</sub> =3V operation |

| 1     | 0     | V <sub>LVR5</sub> (4.0V)    | For V <sub>DD</sub> =5V operation |

| 1     | 1     | Reserved                    |                                   |

<sup>1.</sup> See Chapter 16 Electrical Specifications for full parameters.

# 14.5 Low-Power Modes

The STOP and WAIT instructions put the MCU in low-power-consumption standby modes.

#### **14.5.1 Wait Mode**

The LVI module, when enabled, will continue to operate in WAIT Mode.

# 14.5.2 Stop Mode

The LVI module, when enabled, will continue to operate in STOP Mode.

MC68HC908JL3E Family Data Sheet, Rev. 4

#### **Break Module (BREAK)**

Figure 15-2. Break I/O Register Summary

## 15.3.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. (See 5.7.3 Break Flag Control Register (BFCR) and see the Break Interrupts subsection for each module.)

# 15.3.2 CPU During Break Interrupts

The CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD (\$FEFC:\$FEFD in monitor mode)

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

#### 15.3.3 TIM During Break Interrupts

A break interrupt stops the timer counter.

# 15.3.4 COP During Break Interrupts

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

# **Electrical Specifications**

# **B.7 Electrical Specifications**

Electrical specifications for the MC68H(R)C908JL3E/JK3E apply to the MC68H(R)C08JL3E/JK3E, except for the parameters indicated below.

#### **B.7.1 DC Electrical Characteristics**

Table B-2. DC Electrical Characteristics (5V)

| Characteristic <sup>(1)</sup>                                                | Symbol                               | Min       | Typ <sup>(2)</sup> | Max       | Unit     |

|------------------------------------------------------------------------------|--------------------------------------|-----------|--------------------|-----------|----------|

| V <sub>DD</sub> supply current, f <sub>OP</sub> = 4MHz<br>Run <sup>(3)</sup> |                                      |           |                    |           |          |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 9                  | 11        | mA       |

| MC68HRC08JL3E/JK3E<br>Wait <sup>(4)</sup>                                    |                                      | _         | 4.3                | 5         | mA       |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 5.5                | 6.5       | mA       |

| MC68HRC08JL3E/JK3E<br>Stop <sup>(5)</sup><br>(-40°C to 85°C)                 | I <sub>DD</sub>                      | _         | 0.8                | 1.5       | mA       |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 1.8                | 5         | μΑ       |

| MC68HRC08JL3E/JK3E<br>(-40°C to 125°C)                                       |                                      | _         | 1.8                | 5         | μA       |

| MC68HC08JL3E/JK3E                                                            |                                      | _         | 5                  | 10        | μΑ       |

| MC68HRC08JL3E/JK3E                                                           |                                      | _         | 5                  | 10        | μΑ       |

| Pullup resistors <sup>(6)</sup> PTD6, PTD7 RST, IRQ, PTA0–PTA6               | R <sub>PU1</sub><br>R <sub>PU2</sub> | 1.8<br>16 | 4.3<br>31          | 4.8<br>36 | kΩ<br>kΩ |

<sup>1.</sup>  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

<sup>2.</sup> Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

<sup>3.</sup> Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{QP} = 4MHz$ ). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

<sup>4.</sup> Wait I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 4MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

5. Stop I<sub>DD</sub> measured with OSC1 grounded; no port pins sourcing current. LVI is disabled.

<sup>6.</sup>  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0 \text{ V}$ .