Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                            |                                                                                                   |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                            |

| Core Processor                     | ARM® Cortex®-A5                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 500MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ MPE                                                                             |

| RAM Controllers                    | LPDDR1, LPDDR2, LPDDR3, DDR2, DDR3, DDR3L, QSPI                                                   |

| Graphics Acceleration              | Yes                                                                                               |

| Display & Interface<br>Controllers | Keyboard, LCD, Touchscreen                                                                        |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 + HSIC                                                                                    |

| Voltage - I/O                      | 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 85°C (TA)                                                                                 |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 196-TFBGA, CSBGA                                                                                  |

| Supplier Device Package            | 196-TFBGA (11x11)                                                                                 |

| Purchase URL                       | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d21a-cu                          |

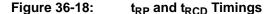

4 cycles before performing a read command

The multiport controller is designed to mask these timings and thus improve the bandwidth of the system.

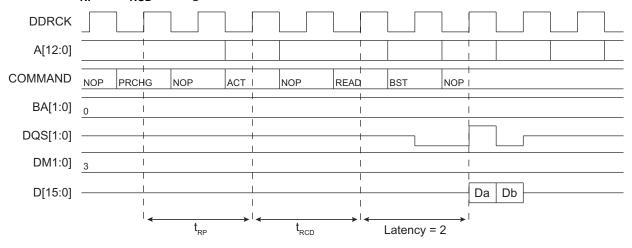

The MPDDRC is a multiport controller whereby eight masters can simultaneously reach the controller. This feature improves the bandwidth of the system because it can detect eight requests on the AHB slave inputs and thus anticipate the commands that follow, Precharge and Activate command in bank X during the current access in bank Y. This masks  $t_{RP}$  and  $t_{RCD}$  timings (see Figure 36-19). In the best case, all accesses are done as if the banks and rows were already open. The best condition is met when the eight masters work in different banks. In case of eight simultaneous read accesses, when the four or eight banks and associated rows are open, the controller reads with a continuous flow and masks the CAS latency for each access. To allow a continuous flow, the read command must be set at 2 or 3 cycles (CAS latency) before the end of the current access. This requires that the scheme of arbitration changes since arbitration cannot be respected. If the controller anticipates a read access, and thus a master with a high priority arises before the end of the current access, then this master will not be serviced.

Figure 36-19: Anticipate Precharge/Activate Command in Bank 2 during Read Access in Bank 1

MPDDRC is a multiport controller that embeds three arbitration mechanisms based on round -robin arbitration which allows to share the external device between different masters when two or more masters try to access the DDR-SDRAM device at the same time.

The three arbitration types are round-robin arbitration and two weighted round-robin arbitrations. For weighted round-robin arbitrations, the priority can be given either depending on the number of requests or words per port, or depending on the required bandwidth per port. The type of arbitration can be chosen by setting the ARB field in the Configuration Arbiter register (MPDDRC\_CONF\_ARBITER) (see Section 36.7.16 "MPDDRC Configuration Arbiter Register").

This field reports when the device autoinitialization is complete.

| Value | Name            | Description           |

|-------|-----------------|-----------------------|

| 0     | DAI_COMPLETE    | DAI complete          |

| 1     | DAI_IN_PROGESSS | DAI still in progress |

## MRS: Mode Register Select LPDDR2/LPDDR3

Configure this 8-bit field to program all mode registers included in the low-power DDR2-SDRAM device. This field is unique to the low-power DDR2-SDRAM devices and low-power DDR3-SDRAM devices.

### 37.20.36 Timings Register

Name: HSMC\_TIMINGSx [x=0..3]

Address: 0xF801470C [0], 0xF8014720 [1], 0xF8014734 [2], 0xF8014748 [3]

Access: Read/Write

| 31    | 30 | 29 | 28   | 27 | 26 | 25 | 24 |

|-------|----|----|------|----|----|----|----|

| NFSEL | _  | -  | _    |    | TV | /B |    |

| 23    | 22 | 21 | 20   | 19 | 18 | 17 | 16 |

| _     | _  | _  | _    |    | TF | RR |    |

|       |    |    |      |    |    |    |    |

| 15    | 14 | 13 | 12   | 11 | 10 | 9  | 8  |

| _     | _  | _  | OCMS |    | TA | .R |    |

|       |    |    |      |    |    |    |    |

| 7     | 6  | 5  | 4    | 3  | 2  | 1  | 0  |

|       | TA | DL |      |    | TC | LR |    |

This register can only be written if the WPEN bit is cleared in the Write Protection Mode Register.

### TCLR: CLE to REN Low Delay

Command Latch Enable falling edge to Read Enable falling edge timing.

Latch Enable Falling to Read Enable Falling = (TCLR[3] \* 64) + TCLR[2:0] clock cycles.

#### **TADL: ALE to Data Start**

Last address latch cycle to the first rising edge of WEN for data input.

Last address latch to first rising edge of WEN = (TADL[3] \* 64) + TADL[2:0] clock cycles.

#### TAR: ALE to REN Low Delay

Address Latch Enable falling edge to Read Enable falling edge timing.

Address Latch Enable to Read Enable = (TAR[3] \* 64) + TAR[2:0] clock cycles.

#### **OCMS: Off Chip Memory Scrambling Enable**

When set to one, the memory scrambling is activated. (Value must be zero if external memory is NAND Flash and NFC is used).

#### TRR: Ready to REN Low Delay

Ready/Busy signal to Read Enable falling edge timing.

Read to REN = (TRR[3] \* 64) + TRR[2:0] clock cycles.

#### TWB: WEN High to REN to Busy

Write Enable rising edge to Ready/Busy falling edge timing.

Write Enable to Read/Busy = (TWB[3] \* 64) + TWB[2:0] clock cycles.

### **NFSEL: NAND Flash Selection**

If this bit is set to one, the chip select is assigned to NAND Flash write enable and read enable lines drive the Error Correcting Code module.

39.7.30 Base Layer Configuration Register 3

Name: LCDC\_BASECFG3

Address: 0xF0000078

Access: Read/Write

| 31 | 30   | 29 | 28  | 27 | 26 | 25 | 24 |  |  |

|----|------|----|-----|----|----|----|----|--|--|

| _  | -    | _  | -   | _  | -  | _  | _  |  |  |

| 23 | 22   | 21 | 20  | 19 | 18 | 17 | 16 |  |  |

|    | RDEF |    |     |    |    |    |    |  |  |

| 15 | 14   | 13 | 12  | 11 | 10 | 9  | 8  |  |  |

|    |      |    | GD  | EF |    |    |    |  |  |

| 7  | 6    | 5  | 4   | 3  | 2  | 1  | 0  |  |  |

|    |      |    | BDI | EF |    |    |    |  |  |

**RDEF: Red Default**

Default Red color when the Base DMA channel is disabled

**GDEF: Green Default**

Default Green color when the Base DMA channel is disabled

**BDEF: Blue Default**

Default Blue color when the Base DMA channel is disabled

## 40.8.50 GMAC Broadcast Frames Transmitted Register

Name: GMAC\_BCFT

Address: 0xF800810C

Access: Read-only

| 31 | 30   | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|----|------|----|----|----|----|----|----|--|--|

|    |      |    | BF | TX |    |    |    |  |  |

| 23 | 22   | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|    | BFTX |    |    |    |    |    |    |  |  |

| 15 | 14   | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

|    |      |    | BF | TX |    |    |    |  |  |

| 7  | 6    | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|    |      |    | BF | TX |    |    |    |  |  |

## **BFTX: Broadcast Frames Transmitted without Error**

Broadcast frames transmitted without error. This register counts the number of broadcast frames successfully transmitted without error, i.e., no underrun and not too many retries. Excludes pause frames.

### 41.6.6 Endpoint Configuration

The endpoint 0 is always a control endpoint, it must be programmed and active in order to be enabled when the End Of Reset interrupt occurs.

To configure the endpoints:

- Fill the configuration register (UDPHS\_EPTCFG) with the endpoint size, direction (IN or OUT), type (CTRL, Bulk, IT, ISO) and the number of banks.

- Fill the number of transactions (NB\_TRANS) for isochronous endpoints.

Note: For control endpoints the direction has no effect.

- Verify that the EPT\_MAPD flag is set. This flag is set if the endpoint size and the number of banks are correct compared to the FIFO

maximum capacity and the maximum number of allowed banks.

- Configure control flags of the endpoint and enable it in UDPHS\_EPTCTLENBx according to Section 41.7.12 "UDPHS Endpoint Control Disable Register (Isochronous Endpoint)".

Control endpoints can generate interrupts and use only 1 bank.

All endpoints (except endpoint 0) can be configured either as Bulk, Interrupt or Isochronous. Refer to Table 41-4: UDPHS Endpoint Description.

The maximum packet size they can accept corresponds to the maximum endpoint size.

Note: The endpoint size of 1024 is reserved for isochronous endpoints.

The size of the DPRAM is 8 Kbytes. The DPR is shared by all active endpoints. The memory size required by the active endpoints must not exceed the size of the DPRAM.

SIZE\_DPRAM = SIZE \_EPT0

- + NB\_BANK\_EPT1 x SIZE\_EPT1

- + NB\_BANK\_EPT2 x SIZE\_EPT2

- + NB\_BANK\_EPT3 x SIZE\_EPT3

- + NB\_BANK\_EPT4 x SIZE\_EPT4

- + NB\_BANK\_EPT5 x SIZE\_EPT5

- + NB\_BANK\_EPT6 x SIZE\_EPT6

- +... (refer to 41.7.8 UDPHS Endpoint Configuration Register)

If a user tries to configure endpoints with a size the sum of which is greater than the DPRAM, then the EPT\_MAPD is not set.

The application has access to the physical block of DPR reserved for the endpoint through a 64-Kbyte logical address space.

The physical block of DPR allocated for the endpoint is remapped all along the 64-Kbyte logical address space. The application can write a 64-Kbyte buffer linearly.

This bit is set by hardware after a new packet has been stored in the endpoint FIFO.

This bit is cleared by the device firmware after reading the OUT data from the endpoint.

For multi-bank endpoints, this bit may remain active even when cleared by the device firmware, this if an other packet has been received meanwhile.

Hardware assertion of this bit may generate an interrupt if enabled by the UDPHS\_EPTCTLx register RXRDY\_TXKL bit.

This bit is reset by UDPHS\_EPTRST register EPT\_x (reset endpoint) and by UDPHS\_EPTCTLDISx (disable endpoint).

- KILL Bank (for IN endpoint):

- The bank is really cleared or the bank is sent, BUSY BANK STA is decremented.

- The bank is not cleared but sent on the IN transfer, TX COMPLT

- The bank is not cleared because it was empty. The user should wait that this bit is cleared before trying to clear another packet.

Note: "Kill a packet" may be refused if at the same time, an IN token is coming and the current packet is sent on the UDPHS line. In this case, the TX\_COMPLT bit is set. Take notice however, that if at least two banks are ready to be sent, there is no problem to kill a packet even if an IN token is coming. In fact, in that case, the current bank is sent (IN transfer) and the last bank is killed.

### TX\_COMPLT: Transmitted IN Data Complete (cleared upon USB reset)

This bit is set by hardware after an IN packet has been sent.

This bit is reset by UDPHS\_EPTRST register EPT\_x (reset endpoint), and by UDPHS\_EPTCTLDISx (disable endpoint).

## TXRDY\_TRER: TX Packet Ready/Transaction Error (cleared upon USB reset)

– TX Packet Ready:

This bit is cleared by hardware, as soon as the packet has been sent.

For Multi-bank endpoints, this bit may remain clear even after software is set if another bank is available to transmit.

Hardware clear of this bit may generate an interrupt if enabled by the UDPHS\_EPTCTLx register TXRDY\_TRER bit.

This bit is reset by UDPHS\_EPTRST register EPT\_x (reset endpoint), and by UDPHS\_EPTCTLDISx (disable endpoint).

Transaction Error (for high bandwidth isochronous OUT endpoints) (Read-Only):

This bit is set by hardware when a transaction error occurs inside one microframe.

If one toggle sequencing problem occurs among the n-transactions (n = 1, 2 or 3) inside a microframe, then this bit is still set as long as the current bank contains one "bad" n-transaction (refer to "CURBK: Current Bank (cleared upon USB reset)"). As soon as the current bank is relative to a new "good" n-transactions, then this bit is reset.

- **Note 1:** A transaction error occurs when the toggle sequencing does not comply with the *Universal Serial Bus Specification, Rev 2.0* (5.9.2 High Bandwidth Isochronous endpoints) (Bad PID, missing data, etc.)

- 2: When a transaction error occurs, the user may empty all the "bad" transactions by clearing the Received OUT Data flag (RXRDY\_TXKL).

If this bit is reset, then the user should consider that a new n-transaction is coming.

This bit is reset by UDPHS\_EPTRST register EPT\_x (reset endpoint), and by UDPHS\_EPTCTLDISx (disable endpoint).

#### ERR\_FL\_ISO: Error Flow (cleared upon USB reset)

This bit is set by hardware when a transaction error occurs.

- Isochronous IN transaction is missed, the micro has no time to fill the endpoint (underflow).

- Isochronous OUT data is dropped because the bank is busy (overflow).

This bit is reset by UDPHS\_EPTRST register EPT\_x (reset endpoint) and by UDPHS\_EPTCTLDISx (disable endpoint).

#### ERR\_CRC\_NTR: CRC ISO Error/Number of Transaction Error (cleared upon USB reset)

CRC ISO Error (for Isochronous OUT endpoints) (Read-only):

This bit is set by hardware if the last received data is corrupted (CRC error on data).

This bit is updated by hardware when new data is received (Received OUT Data bit).

Number of Transaction Error (for High Bandwidth Isochronous IN endpoints):

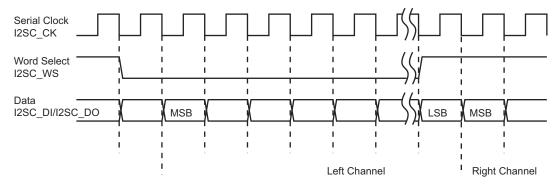

Figure 44-2: I<sup>2</sup>S Reception and Transmission Sequence

Data bits are sent on the falling edge of the serial clock and sampled on the rising edge of the serial clock. the word select line indicates the channel in transmission, a low level for the left channel and a high level for the right channel.

The length of transmitted words can be chosen among 8, 16, 18, 20, 24, and 32 bits by writing the I2SC\_MR.DATALENGTH field.

If the time slot allows for more data bits than written in the I2SC\_MR.DATALENGTH field, zeroes are appended to the transmitted data word or extra received bits are discarded.

#### 44.6.5 Serial Clock and Word Select Generation

The generation of clocks in the I2SC is described in Figure 44-3 "I2SC Clock Generation".

In Slave mode, the serial clock and word select clock are driven by an external master. I2SC\_CK and I2SC\_WS pins are inputs.

In Master mode, the user can configure the master clock, serial clock, and word select clock through the I2SC\_MR. I2SC\_MCK, I2SC\_CK, and I2SC\_WS pins are outputs and MCK is used to derive the I2SC clocks.

In Master mode, if the peripheral clock frequency is higher than 96 MHz, GCLK[PID] from the PMC must be selected as the I2SC input clock by writing a '1' in the CLKSELx bit of the SFR\_I2SCLKSEL register located in SFR.

Audio codecs connected to the I2SC pins may require a master clock (I2SC\_MCK) signal with a frequency multiple of the audio sample frequency (f<sub>s</sub>), such as 256f<sub>s</sub>. When the I2SC is in Master mode, writing a '1' to I2SC\_MR.IMCKMODE outputs MCK as master clock to the I2SC\_MCK pin, and divides MCK to create the internal bit clock, output on the I2SC\_CK pin. The clock division factor is defined by writing to I2SC\_MR.IMCKFS and I2SC\_MR.DATALENGTH, as described in the I2SC\_MR.IMCKFS field description.

The master clock (I2SC\_MCK) frequency is  $(2\times16\times(IMCKFS+1))$  / (IMCKDIV + 1) times the sample frequency (f<sub>s</sub>), i.e., I2SC\_WS frequency.

Example: If the sampling rate is 44.1 kHz with an I2S master clock (I2SC\_MCK) ratio of 256, the core frequency must be an integer multiple of 11.2896 MHz. Assuming an integer multiple of 4, the IMCKDIV field must be configured to 4; the field IMCKFS must then be set to 31.

The serial clock (I2SC\_CK) frequency is  $2 \times \text{Slot}$  Length times the sample frequency ( $f_s$ ), where Slot Length is defined in Table 44-4.

Table 44-4: Slot Length

| I2SC_MR.DATALENGTH | Word Length            | Slot Length                                    |  |  |

|--------------------|------------------------|------------------------------------------------|--|--|

| 0                  | 32 bits                | 32                                             |  |  |

| 1                  | 24 bits                | 00 % 1000 140 1140 0                           |  |  |

| 2                  | 20 bits                | 32 if I2SC_MR.IWS = 0<br>24 if I2SC_MR.IWS = 1 |  |  |

| 3                  | 18 bits                | 24 II 1230_IVIN.1VV3 = 1                       |  |  |

| 4                  | 16 bits                | 16                                             |  |  |

| 5                  | 16 bits compact stereo | - 16                                           |  |  |

| 6                  | 6 8 bits               |                                                |  |  |

| 7                  | 8 bits compact stereo  | 8                                              |  |  |

Warning: I2SC\_MR.IMCKMODE must be written to '1' if the master clock frequency is strictly higher than the serial clock.

#### **RSTSTA: Reset Status Bits**

0: No effect.

1: Resets the status bits PARE, FRAME, OVRE, MANE, LINBE, LINISFE, LINIPE, LINCE, LINSNRE, LINSTE, LINHTE, LINID, LINTC, LINBK, CMP and RXBRK in FLEX\_US\_CSR. Also resets the status bits TXFEF, TXFFF, TXFTHF, RXFEF, RXFTHF, TXFPTEF, RXFPTEF in FLEX\_US\_FESR.

#### STTBRK: Start Break

0: No effect.

1: Starts transmission of a break after the characters present in FLEX\_US\_THR and the Transmit Shift Register have been transmitted. No effect if a break is already being transmitted.

#### STPBRK: Stop Break

0: No effect.

1: Stops transmission of the break after a minimum of one character length and transmits a high level during 12-bit periods. No effect if no break is being transmitted.

#### STTTO: Clear TIMEOUT Flag and Start Timeout After Next Character Received

0: No effect.

1: Starts waiting for a character before clocking the timeout counter. Immediately disables a timeout period in progress. Resets the FLEX\_US\_CSR.TIMEOUT status bit.

#### **SENDA: Send Address**

0: No effect.

1: In Multidrop mode only, the next character written to FLEX\_US\_THR is sent with the address bit set.

#### **RSTIT: Reset Iterations**

0: No effect.

1: Resets FLEX\_US\_CSR.ITER. No effect if the ISO7816 is not enabled.

#### **RSTNACK: Reset Non Acknowledge**

0: No effect

1: Resets FLEX\_US\_CSR.NACK.

## **RETTO: Start Timeout Immediately**

0: No effect

1: Immediately restarts timeout period.

### **RTSEN: Request to Send Enable**

0: No effect.

1: Drives the RTS pin to 1 if FLEX\_US\_MR.USART\_MODE field = 2, else drives the RTS pin to 0 if FLEX\_US\_MR.USART\_MODE field = 0.

#### **RTSDIS: Request to Send Disable**

0: No effect.

1: Drives the RTS pin to 0 if FLEX\_US\_MR.USART\_MODE field = 2, else drives the RTS pin to 1 if FLEX\_US\_MR.USART\_MODE field = 0.

#### **LINABT: Abort LIN Transmission**

0: No effect.

1: Aborts the current LIN transmission.

## LINWKUP: Send LIN Wakeup Signal

0: No effect:

1: Sends a wakeup signal on the LIN bus.

## 47.10.15 USART Interrupt Mask Register (SPI\_MODE)

Name: FLEX\_US\_IMR (SPI\_MODE)

Address: 0xF8034210 (0), 0xF8038210 (1), 0xFC010210 (2), 0xFC014210 (3), 0xFC018210 (4)

Access: Read-only

| 31 | 30  | 29   | 28 | 27   | 26   | 25      | 24    |

|----|-----|------|----|------|------|---------|-------|

| _  | -   | _    | -  | _    | -    | _       | _     |

| 23 | 22  | 21   | 20 | 19   | 18   | 17      | 16    |

| _  | CMP | _    | -  | NSSE | -    | _       | _     |

| 15 | 14  | 13   | 12 | 11   | 10   | 9       | 8     |

| _  | -   | _    | -  | _    | UNRE | TXEMPTY | _     |

| 7  | 6   | 5    | 4  | 3    | 2    | 1       | 0     |

| _  | _   | OVRE | _  | _    | _    | TXRDY   | RXRDY |

This configuration is relevant only if USART\_MODE = 0xE or 0xF in the USART Mode Register.

The following configuration values are valid for all listed bit names of this register:

0: The corresponding interrupt is not enabled.

1: The corresponding interrupt is enabled.

RXRDY: RXRDY Interrupt Mask

TXRDY: TXRDY Interrupt Mask

OVRE: Overrun Error Interrupt Mask

TXEMPTY: TXEMPTY Interrupt Mask

**UNRE: SPI Underrun Error Interrupt Mask**

NSSE: NSS Line (Driving CTS Pin) Rising or Falling Edge Event

**CMP: Comparison Interrupt Mask**

## 47.10.26 USART Transmitter Timeguard Register

Name: FLEX\_US\_TTGR

Address: 0xF8034228 (0), 0xF8038228 (1), 0xFC010228 (2), 0xFC014228 (3), 0xFC018228 (4)

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|----|----|----|----|----|----|----|----|--|--|

| _  | _  | -  | _  | _  | _  | _  | -  |  |  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

| _  | _  | _  | _  | _  | _  | _  | _  |  |  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

| _  | _  | _  | _  | _  | _  | _  | _  |  |  |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|    | TG |    |    |    |    |    |    |  |  |

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

## **TG: Timeguard Value**

0: The transmitter timeguard is disabled.

1–255: The transmitter timeguard is enabled and TG is timeguard delay / bit period.

## 47.10.74 TWI Transmit Holding Register (FIFO Enabled)

Name: FLEX\_TWI\_THR (FIFO\_ENABLED)

Address: 0xF8034634 (0), 0xF8038634 (1), 0xFC010634 (2), 0xFC014634 (3), 0xFC018634 (4)

Access: Write-only

| 31 | 30      | 29 | 28  | 27   | 26 | 25 | 24 |  |  |  |

|----|---------|----|-----|------|----|----|----|--|--|--|

|    | TXDATA3 |    |     |      |    |    |    |  |  |  |

| 23 | 22      | 21 | 20  | 19   | 18 | 17 | 16 |  |  |  |

|    | TXDATA2 |    |     |      |    |    |    |  |  |  |

| 15 | 14      | 13 | 12  | 11   | 10 | 9  | 8  |  |  |  |

|    |         |    | TXD | ATA1 |    |    |    |  |  |  |

| 7  | 6       | 5  | 4   | 3    | 2  | 1  | 0  |  |  |  |

|    |         |    | TXD | ATA0 |    |    |    |  |  |  |

Note: If FIFO is enabled (FLEX\_US\_CR.FIFOEN bit) and FLEX\_TWI\_FMR.TXRDYM > 0, see Section 47.9.6.8 "TWI Multiple Data

Mode" for details.

**TXDATA0: Master or Slave Transmit Holding Data 0**

**TXDATA1: Master or Slave Transmit Holding Data 1**

**TXDATA2: Master or Slave Transmit Holding Data 2**

**TXDATA3: Master or Slave Transmit Holding Data 3**

## 47.10.75 TWI SMBus Timing Register

Name: FLEX\_TWI\_SMBTR

Address: 0xF8034638 (0), 0xF8038638 (1), 0xFC010638 (2), 0xFC014638 (3), 0xFC018638 (4)

Access: Read/Write

| 31 | 30    | 29 | 28  | 27  | 26  | 25 | 24 |  |  |  |

|----|-------|----|-----|-----|-----|----|----|--|--|--|

|    | THMAX |    |     |     |     |    |    |  |  |  |

| 23 | 22    | 21 | 20  | 19  | 18  | 17 | 16 |  |  |  |

|    | TLOWM |    |     |     |     |    |    |  |  |  |

| 15 | 14    | 13 | 12  | 11  | 10  | 9  | 8  |  |  |  |

|    |       |    | TLC | )WS |     |    |    |  |  |  |

| 7  | 6     | 5  | 4   | 3   | 2   | 1  | 0  |  |  |  |

| -  | _     | -  | -   |     | PRE | SC |    |  |  |  |

#### **PRESC: SMBus Clock Prescaler**

Used to specify how to prescale the TLOWS, TLOWM and THMAX counters in SMBTR. Counters are prescaled according to the following formula:  $PRESC = Log(fMCK / f_{Prescaled}) / Log(2) - 1$

## **TLOWS: Slave Clock Stretch Maximum Cycles**

0: TLOW:SEXT timeout check disabled.

1-255: Clock cycles in slave maximum clock stretch count. Prescaled by PRESC. Used to time TLOW:SEXT.

#### **TLOWM: Master Clock Stretch Maximum Cycles**

0: TLOW:MEXT timeout check disabled.

1–255: Clock cycles in master maximum clock stretch count. Prescaled by PRESC. Used to time TLOW:MEXT.

### **THMAX: Clock High Maximum Cycles**

Clock cycles in clock high maximum count. Prescaled by PRESC. Used for bus free detection. Used to time THIGH:MAX.

# 50.7.4 QSPI Transmit Data Register

Name: QSPI\_TDR

Address: 0xF002000C (0), 0xF002400C (1)

Access: Write-only

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |  |

|----|----|----|----|----|----|----|----|--|

| _  | _  | ı  | ı  | ı  | ı  | ı  | _  |  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |

| _  | _  | ı  | ı  | ı  | ı  | ı  | _  |  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |  |

|    |    |    | Т  | D  |    |    |    |  |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

|    | TD |    |    |    |    |    |    |  |

## **TD: Transmit Data**

Data to be transmitted by the QSPI is stored in this register. Information to be transmitted must be written to the Transmit Data register in a right-justified format.

52.6.59 ISC DMA Stride 2 Register

Name: ISC\_DST2

Address: 0xF0008400

Access: Read/Write

| 31 | 30  | 29 | 28             | 27 | 26 | 25 | 24 |  |  |  |

|----|-----|----|----------------|----|----|----|----|--|--|--|

|    | ST2 |    |                |    |    |    |    |  |  |  |

| 23 | 22  | 21 | 20             | 19 | 18 | 17 | 16 |  |  |  |

|    | ST2 |    |                |    |    |    |    |  |  |  |

| 15 | 14  | 13 | 12             | 11 | 10 | 9  | 8  |  |  |  |

|    |     |    | S <sup>-</sup> | Γ2 |    |    |    |  |  |  |

| 7  | 6   | 5  | 4              | 3  | 2  | 1  | 0  |  |  |  |

|    |     |    | S              | Γ2 |    |    |    |  |  |  |

ST2: Channel 2 Stride

**BOE: Bus\_Off Status Interrupt Enable**

**WDIE: Watchdog Interrupt Enable**

**PEAE: Protocol Error in Arbitration Phase Enable**

PEDE: Protocol Error in Data Phase Enable

**ARAE: Access to Reserved Address Enable**

© 2017 Microchip Technology Inc.

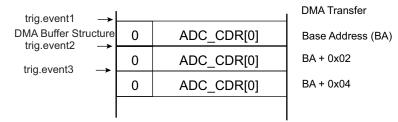

Figure 65-9: Independent Trigger Measurement for Last Channel (ADC\_CHSR[LCI] = 0 and ADC\_TRGR.TRGMOD = 1, 2, 3, 5)

ADC LCTMR.DUALTRIG = 1 period defined by RTC\_MR.OUT1 Internal RTC C conv. scheduled on TRGSEL trigger event Trigger event Internal/External Trigger Event (Defined by TRGSEL) С C ADC SEL ADC\_CDR[0] C1 C2 C3 C4 C5 C<sub>0</sub> and ADC LCDR

LC1

LC<sub>2</sub>

Notes: ADC\_SEL: Command to the ADC analog cell

LC<sub>0</sub>

Cx: All ADC channel values except the last channel (highest index)

LCx: Last channel value LCI: Last channel index

## Assuming ADC\_CHSR[0] = 1

ADC\_CDR[LCI]

If DUALTRIG = 1 and field ADC\_TRGR.TRGMOD = 0 and none of the channels are enabled in ADC\_CHSR (ADC\_CHSR = 0), then only channel 11 is converted at a rate defined by the trigger event signal that can be configured in RTC\_MR.OUT1 (see Figure 65-10).

This mode of operation, when combined with the Sleep mode operation of the ADC Controller, provides a low-power mode for last channel measure. This assumes there is no other ADC conversion to schedule at a high sampling rate or no other channel to convert.

DS60001476B-page 2402

## 65.7.20 ADC Analog Control Register

Name: ADC\_ACR

Address: 0xFC030094

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26 | 25         | 24 |

|----|----|----|----|----|----|------------|----|

| _  | _  | _  | -  | _  | _  | _          | _  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17         | 16 |

| _  | _  | _  | -  | _  | _  | _          | _  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9          | 8  |

| _  | -  | -  | _  | _  | _  | IBCTL      |    |

| 7  | 6  | 5  | 4  | 3  | 2  | 1          | 0  |

| _  | _  | _  | _  | _  | _  | PENDETSENS |    |

This register can only be written if the WPEN bit is cleared in the ADC Write Protection Mode Register.

Note 1: By default, bits 12 and 13 are set to 1 and 0, respectively, and must not be modified.

## **PENDETSENS: Pen Detection Sensitivity**

Modifies the pen detection input pull-up resistor value. Refer to section "Electrical Characteristics" for further details.

#### **IBCTL: ADC Bias Current Control**

Adapts performance versus power consumption. Refer to "Electrical Characteristics" for further details.

# Table 72-3: SAMA5D2 Datasheet Rev. 11267E Revision History

| Issue Date | Changes                                |  |

|------------|----------------------------------------|--|

| 25-Jul-16  | Deleted Section 61. "Security Module". |  |

## Table 72-4: SAMA5D2 Datasheet Rev. 11267D Revision History

| Issue Date | Changes                                                                                                                                                                                                                                                                                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Minor formatting and editorial changes throughout                                                                                                                                                                                                                                                                                                                   |

|            | "Introduction"                                                                                                                                                                                                                                                                                                                                                      |

|            | Updated listed DDR memories                                                                                                                                                                                                                                                                                                                                         |

|            | "Features"                                                                                                                                                                                                                                                                                                                                                          |

|            | Frequency of digital fractional PLL for audio "11.289 MHz" corrected to "11.2896 MHz"                                                                                                                                                                                                                                                                               |

|            | "Two 64-bit, 16-channel DMA controllers" changed to "51 DMA Channels including two 16-channel 64-bit Central DMA Controllers"                                                                                                                                                                                                                                       |

|            | Section 1. "Description"                                                                                                                                                                                                                                                                                                                                            |

|            | Updated description of Low-power modes                                                                                                                                                                                                                                                                                                                              |

|            | Section 2. "Configuration Summary"                                                                                                                                                                                                                                                                                                                                  |

|            | "Class D amplifier" changed to "stereo Class D amplifier"                                                                                                                                                                                                                                                                                                           |

|            | Updated text at end of section                                                                                                                                                                                                                                                                                                                                      |

|            | Section 3. "Block Diagram"                                                                                                                                                                                                                                                                                                                                          |

|            | Figure 3-1 "SAMA5D2 Series Block Diagram": added ISC_MSK input; updated description of crystal oscillators; "PWMEXTRIGO-1" renumbered to "PWMEXTRG1–2"                                                                                                                                                                                                              |

|            | Added note "See Section 35. "DMA Controller (XDMAC)" for peripheral connections to DMA."                                                                                                                                                                                                                                                                            |

| 12-May-16  | Section 4. "Signal Description"                                                                                                                                                                                                                                                                                                                                     |

|            | Table 4-1 "Signal Description List": NRST signal function "Microcontroller Reset" changed to "Microprocessor Reset"; "PWMEXTRG0-1" renumbered to "PWMEXTRG1–2"; "Self-refresh mode" changed to "Backup Self-refresh mode" in DDR_CKE comments                                                                                                                       |

|            | Section 5. "Package and Pinout"                                                                                                                                                                                                                                                                                                                                     |

|            | Separated content into Section 5.1 "Packages" and Section 5.2 "Pinouts"                                                                                                                                                                                                                                                                                             |

|            | Table 5-2 "Pin Description (SAMA5D21, SAMA5D22, SAMA5D24, SAMA5D26, SAMA5D27, SAMA5D28A)": "ADVREFP" corrected to "ADVREF"; "PWMEXTRG0" and "PWMEXTRG1" renumbered to "PWMEXTRG1" and "PWMEXTRG2"; removed empty function cells for primary signals PA30, PA31, and PB0–PB7; removed "SEC, FILTER" from "Reset State" column header; added footnote on reset states |

|            | Added Table 5-3 "Pin Description (SAMA5D23 pins different from those in SAMA5D21/SAMA5D22)" and Table 5-4 "Pin Description (SAMA5D28B pins different from those in SAMA5D28A)"                                                                                                                                                                                      |

|            | Section 6. "Power Considerations"                                                                                                                                                                                                                                                                                                                                   |

|            | Table 6-1 "SAMA5D2 Power Supplies": updated rows VDDUTMIC, VDDHSIC and VDDOSC                                                                                                                                                                                                                                                                                       |

|            | Section 6.4.1 "VDDBU Power Architecture": reworded second paragraph and deleted "typically less than 2 µA"                                                                                                                                                                                                                                                          |

|            | Section 7. "Memories"                                                                                                                                                                                                                                                                                                                                               |

|            | Section 7.2.1 "External Bus Interface": "The slew rates are determined by programming the SFR_EBICFG bit in SFR registers" changed to "The drive levels are configured with the DRIVEx field in the EBI Configuration Register (SFR_EBICFG)"                                                                                                                        |

© 2017 Microchip Technology Inc.

Table 72-4: SAMA5D2 Datasheet Rev. 11267D Revision History (Continued)

| Issue Date  | Changes                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Section 8. "Event System"                                                                                                                                                                                                      |

|             | Section 8-1 "Real-time Event Mapping List": instance of "ADC_ADTRG" corrected to "ADTRG"                                                                                                                                       |

|             | Section 9. "System Controller"                                                                                                                                                                                                 |

|             | Section 9.1 "Power-On Reset": "dedicated to VDDBU, VDDIOP and VDDCORE" changed to "dedicated to monitoring VDDBU, VDDIOP and VDDCORE"                                                                                          |

|             | Section 10. "Peripherals"                                                                                                                                                                                                      |

|             | Table 10-1 "Peripheral identifiers": in 'Instance Name' column, renamed CAN0 and CAN1 to MCAN0 and MCAN1                                                                                                                       |

|             | Section 10.4 "Peripheral Clock Types": in SLOW_CLOCK description, "32768-Hz crystal oscillator or by the on-chip 32-kHz RC oscillator" changed to "32.768 kHz crystal oscillator or by the on-chip 64 kHz RC oscillator"       |

|             | Section 11. "Chip Identifier (CHIPID)"                                                                                                                                                                                         |

|             | Updated Table 11-1 "SAMA5D2 Chip ID Registers"                                                                                                                                                                                 |

|             | Section 13. "L2 Cache Controller (L2CC)"                                                                                                                                                                                       |

|             | Table 13-2 "Register Mapping": reset value 0x0000_0000 changed to 0x0000_0111 for L2CC_TRCR and L2CC_DRCR                                                                                                                      |

|             | Section 14. "Debug and Test Features"                                                                                                                                                                                          |

|             | Table 14-1 "Debug and Test Pin List": NRST pin function "Microcontroller Reset" changed to "Microprocessor Reset"                                                                                                              |

|             | Section 15. "Standard Boot Strategies"                                                                                                                                                                                         |

|             | "Boot Sequence Control Register (BSCR)" renamed to "Boot Sequence Controller Configuration Register"                                                                                                                           |

|             | Section 15.1 "Description": "This microcontroller can be configured" changed to "This microprocessor can be configured"                                                                                                        |

|             | Figure 15-10 "Galois Field Table Mapping": modified Galois field table offsets                                                                                                                                                 |

| 12-May-16   | Section 15.4.2 "Boot Sequence Controller Configuration Register": added address                                                                                                                                                |

| 12-1Vlay-10 | Section 15.4.3 "Boot Configuration Word": added reference to "Customer Fuse Matrix"                                                                                                                                            |

|             | Added Section 15.4.6.5 "QSPI Flash Boot"                                                                                                                                                                                       |

|             | Table 15-3 "PIO Driven during Boot Program Execution": NAND Flash PIO line PIOC17 changed to PIOB0                                                                                                                             |

|             | Section 18. "Special Function Registers (SFR)"                                                                                                                                                                                 |

|             | Table 18-1 "Register Mapping": removed EBI Configuration Register / SFR_EBICFG (offset 0x40 now reserved)                                                                                                                      |

|             | Section 18.3.1 "DDR Configuration Register": added note                                                                                                                                                                        |

|             | Removed section "EBI Configuration Register"                                                                                                                                                                                   |

|             | Section 21. "Watchdog Timer (WDT)"                                                                                                                                                                                             |

|             | Section 21.4 "Functional Description": in eighth paragraph, "To prevent a software deadlock that continuously triggers the watchdog, the reload of the watchdog must occur" changed to "The reload of the watchdog must occur" |

|             | Section 25. "Real-time Clock (RTC)"                                                                                                                                                                                            |

|             | Reworked Section 25.5.6 "Updating Time/Calendar"                                                                                                                                                                               |

|             | Reworked Figure 25-7 "Calibration Circuitry Waveforms"                                                                                                                                                                         |

|             | AD index '7' replaced with generic 'n' in Section 25.5.8 "Waveform Generation"                                                                                                                                                 |

|             | Updated Figure 25-8 "Waveform Generation for ADC Trigger Event"                                                                                                                                                                |

|             | Section 25.6.2 "RTC Mode Register":                                                                                                                                                                                            |

|             | - updated descriptions of fields OUT0 and OUT1                                                                                                                                                                                 |

|             | - added fields TPERIOD and THIGH                                                                                                                                                                                               |

|             | Section 27. "Low Power Asynchronous Receiver (RXLP)"                                                                                                                                                                           |

|             | Pin/signal name "LPRXD" changed to "RXD"                                                                                                                                                                                       |