#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

-XF

| Product Status                     | Obsolete                                                                                          |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A5                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 500MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ MPE                                                                             |

| RAM Controllers                    | LPDDR1, LPDDR2, LPDDR3, DDR2, DDR3, DDR3L, QSPI                                                   |

| Graphics Acceleration              | Yes                                                                                               |

| Display & Interface<br>Controllers | Keyboard, LCD, Touchscreen                                                                        |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 + HSIC                                                                                    |

| Voltage - I/O                      | 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 85°C (TA)                                                                                 |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 196-TFBGA, CSBGA                                                                                  |

| Supplier Device Package            | 196-TFBGA (11x11)                                                                                 |

| Purchase URL                       | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d21b-cur                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 289-        | 256-        | 196- |            |                | Primary      |      | Alternat | e    |              | PIO peripheral |          |              | Reset State                                         |      |       |   |   |     |              |           |     |                |  |

|-------------|-------------|------|------------|----------------|--------------|------|----------|------|--------------|----------------|----------|--------------|-----------------------------------------------------|------|-------|---|---|-----|--------------|-----------|-----|----------------|--|

| pin         | pin<br>BGA  | pin  | Power Rail | I/O Type       | Signal       | Dir  | Signal   | Dir  | Func         | Signal         | Dir      | IO<br>Set    | (Signal, Dir, PU,<br>PD, HiZ, ST) <sup>(1)(2)</sup> |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | А            | SPI0_SPCK      | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | В            | TK1            | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             | D47         |      |            |                | DAAA         |      |          |      | С            | QSPI0_SCK      | 0        | 2            |                                                     |      |       |   |   |     |              |           |     |                |  |

| M14         | P17         | -    | VDDIOP1    | GPIO_QSPI      | PA14         | I/O  |          | -    | D            | I2SC1_MCK      | 0        | 2            | PIO, I, PU, ST                                      |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      |              |                | Е        | FLEXCOM3_IO2 | I/O                                                 | 1    |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          | F    | D9           | I/O            | 2        |              |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | А            | SPI0_MOSI      | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | В            | TF1            | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             | <b>D</b> 40 |      |            | 0510           | DAAF         |      | D – –    | С    | QSPI0_CS     | 0              | 2        |              |                                                     |      |       |   |   |     |              |           |     |                |  |

| N16         | R18         | -    | VDDIOP1    | GPIO           | PA15         | I/O  |          | -  - | D            | I2SC1_CK       | I/O      | 2            | PIO, I, PU, ST                                      |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          | Е    | FLEXCOM3_IO0 | I/O            | 1        |              |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          | F    | D10          | I/O            | 2        |              |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | А            | SPI0_MISO      | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            | GPIO_IO        | O PA16 I/O - |      |          |      |              | В              | TD1      | 0            | 1                                                   |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              | I/O  |          | _    | С            | QSPI0_IO0      | I/O      | 2            | PIO, I, PU, ST                                      |      |       |   |   |     |              |           |     |                |  |

| M10         | N15         | -    | VDDIOP1    |                |              |      |          |      | D            | I2SC1_WS       | I/O      | 2            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      |              |                | Е        | FLEXCOM3_IO3 | 0                                                   | 1    |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      |              | F              | D11      | I/O          | 2                                                   |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      |              |                | А        | SPI0_NPCS0   | I/O                                                 | 1    |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                | PA17         | PA17 | PA17     | PA17 | PA17         | PA17 I/O       | PA17 I/O | PA17 I/O     | PA17 I/                                             |      |       |   | В | RD1 | Ι            | 1         |     |                |  |

| 147         | <b>D</b> 40 |      |            |                |              |      |          |      |              |                |          |              |                                                     | PA17 | 54.47 |   |   |     | С            | QSPI0_IO1 | I/O | 2              |  |

| N17         | P18         | _    | VDDIOP1    | GPIO_IO        |              |      |          |      |              |                |          |              |                                                     |      | 1/0   | - | - | D   | I2SC1_DI0    | I         | 2   | PIO, I, PU, ST |  |

|             |             |      |            |                |              |      |          |      |              |                |          |              |                                                     |      |       |   |   | Е   | FLEXCOM3_IO4 | 0         | 1   |                |  |

|             |             |      |            |                |              |      |          |      | F            | D12            | I/O      | 2            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | А            | SPI0_NPCS1     | 0        | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | В            | RK1            | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                | DA40         |      |          |      | С            | QSPI0_IO2      | I/O      | 2            |                                                     |      |       |   |   |     |              |           |     |                |  |

| U14         | M9          | L9   | VDDIOP1    | GPIO_IO        | PA18         | I/O  | -        | -    | D            | I2SC1_DO0      | 0        | 2            | PIO, I, PU, ST                                      |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | Е            | SDMMC1_DAT0    | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | F            | D13            | I/O      | 2            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | А            | SPI0_NPCS2     | 0        | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | В            | RF1            | I/O      | 1            |                                                     |      |       |   |   |     |              |           |     |                |  |

| <b>T</b> 44 | 140         | NG   |            |                | DAAO         |      |          |      | С            | QSPI0_IO3      | I/O      | 2            |                                                     |      |       |   |   |     |              |           |     |                |  |

| 114         | T14 V13     | N9   | VUUIOP1    | DDIOP1 GPIO_IO | PA19         | I/O  | -        |      | D            | TIOA0          | I/O      | 1            | PIO, I, PU, ST                                      |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          | Е    | SDMMC1_DAT1  | I/O            | 1        |              |                                                     |      |       |   |   |     |              |           |     |                |  |

|             |             |      |            |                |              |      |          |      | F            | D14            | I/O      | 2            |                                                     |      |       |   |   |     |              |           |     |                |  |

## Table 6-2: Pin Description (Continued)

## 8.1 Embedded Memories

### 8.1.1 Internal SRAM

The SAMA5D2 embeds a total of 128 Kbytes of high-speed SRAM. After reset, and until the Remap command is performed, the SRAM is accessible at address 0x0020 0000. When the AXI Bus Matrix is remapped, the SRAM is also available at address 0x0.

The device features a second 128-Kbyte SRAM that can be allocated either to the L2 cache controller or used as an internal SRAM. After reset, this block is connected to the system SRAM, making the two 128-Kbyte RAMs contiguous. The SRAM\_SEL bit, located in the SFR\_L2CC\_HRAMC register, is used to reassign this memory as a L2 cache memory.

## 8.1.2 Internal ROM

The product embeds one 160-Kbyte secured internal ROM mapped at address 0 after reset. The ROM contains a standard and secure bootloader as well as the BCH (Bose, Chaudhuri and Hocquenghem) code tables for NAND Flash ECC correction. The memory area containing the secure boot is automatically hidden after the execution of the secure boot while the one containing the code tables for ECC remains visible.

### 8.1.3 Boot Strategies

For standard boot strategies, refer to Section 16. "Standard Boot Strategies" of this datasheet.

For secure boot strategies, refer to the document "SAMA5D2x Secure Boot Strategy", document no. 44040 (Non-Disclosure Agreement required).

## 8.2 External Memory

The SAMA5D2 offers connections to a wide range of external memories or to parallel peripherals.

### 8.2.1 External Bus Interface

The External Bus Interface (EBI) is a 16-bit wide interface working at MCK/2.

The EBI supports:

- Static memories

- 8-bit NAND Flash with 32-bit BCH ECC

- 16-bit NAND Flash

EBI I/Os accept three drive levels (Low, Medium, High) to avoid overshoots and provide the best performances according to the bus load and external memories voltage.

The drive levels are configured with the DRVSTR field in the PIO Configuration Register (PIO\_CFGRx) if the corresponding line is nonsecure or the Secure PIO Configuration Register (S\_PIO\_CFGRx) if the I/O line is secure.

At reset, the selected drive is low. The user must make sure to program the correct drive according to the device load. The I/O embeds serial resistors for impedance matching.

#### 8.2.2 Supported Memories on DDR2/DDR3/LPDDR1/LPDDR2/LPDDR3 Interface

- 16-bit or 32-bit external interface

- 512 Mbytes of address space on DDR CS and DDR/AES CS in 32-bit mode

- 256 Mbytes of address space on DDR CS and DDR/AES CS in 16-bit mode

- Supports 16-bit or 32-bit 8-bank DDR2, DDR3, LPDDR1, LPDDR2 and LPDDR3 memories

- Automatic drive level control

- Multiport

- · Scramblable data path

- Port 0 of this interface has an embedded automatic AES encryption and decryption mechanism (refer to Section 59. "Advanced Encryption Standard Bridge (AESB)"). Writing to or reading from the address 0x40000000 may trigger the encryption and decryption mechanism depending on the AESB on External Memories configuration.

- TrustZone: The multiport feature of this interface implies TrustZone configuration constraints. Refer to Section 18.12 "TrustZone Extension to AHB and APB" for more details.

#### 8.2.3 Supported Memories on Static Memories and NAND Flash Interfaces

The Static Memory Controller is dedicated to interfacing external memory devices:

• Asynchronous SRAM-like memories and parallel peripherals

# SAMA5D2 SERIES

## 18.13.8 Master Error Status Register

| Name:    | MATRIX_ME                        | SR    |          |      |        |        |       |       |  |  |  |  |

|----------|----------------------------------|-------|----------|------|--------|--------|-------|-------|--|--|--|--|

| Address: | : 0xF001815C (0), 0xFC03C15C (1) |       |          |      |        |        |       |       |  |  |  |  |

| Access:  | Read-only                        |       |          |      |        |        |       |       |  |  |  |  |

| 31       |                                  | 30    | 29       | 28   | 27     | 26     | 25    | 24    |  |  |  |  |

| -        |                                  | -     | -        | -    | _      | _      | -     | -     |  |  |  |  |

| 23       |                                  | 22    | 21       | 20   | 19     | 18     | 17    | 16    |  |  |  |  |

| -        |                                  | -     | —        | -    | _      | _      | -     | _     |  |  |  |  |

| 15       |                                  | 14    | 13       | 12   | 11     | 10     | 9     | 8     |  |  |  |  |

| -        |                                  | -     | -        | -    | MERR11 | MERR10 | MERR9 | MERR8 |  |  |  |  |

| 7        |                                  | 6     | 5        | 4    | 3      | 2      | 1     | 0     |  |  |  |  |

| MERF     | R7 ME                            | RR6 M | /IERR5 M | ERR4 | MERR3  | MERR2  | MERR1 | MERR0 |  |  |  |  |

## MERRx: Master x Access Error

0: No Master Access Error has occurred since the last read of the MATRIX\_MESR.

1: At least one Master Access Error has occurred since the last read of the MATRIX\_MESR.

| Name:<br>Address: | SFR_UTMIHSTRIM<br>0xF8030034 |        |    |    |        |         |    |  |

|-------------------|------------------------------|--------|----|----|--------|---------|----|--|

| Access:           | Read/Write                   |        |    |    |        |         |    |  |

| 31                | 30                           | 29     | 28 | 27 | 26     | 25      | 24 |  |

| _                 | -                            | -      | _  | _  | -      | -       | _  |  |

| 23                | 22                           | 21     | 20 | 19 | 18     | 17      | 16 |  |

| _                 | -                            | _      | _  | _  |        | SLOPE2  |    |  |

| 15                | 14                           | 13     | 12 | 11 | 10     | 9       | 8  |  |

| -                 |                              | SLOPE1 |    |    | SLOPE0 |         |    |  |

| 7                 | 6                            | 5      | 4  | 3  | 2      | 1       | 0  |  |

| _                 |                              | DISC   |    | _  |        | SQUELCH |    |  |

## 19.3.6 UTMI High-Speed Trimming Register

#### SQUELCH: UTMI HS SQUELCH Voltage Trimming

Calibration bits to adjust squelch threshold.

## **DISC: UTMI Disconnect Voltage Trimming**

Calibration bits to adjust disconnect threshold.

## SLOPEx: UTMI HS PORTx Transceiver Slope Trimming

Calibration bits to adjust HS Transceiver output slope for PORTx.

## 23.5.2 RSTC Status Register

| Address: 0xF | TC_SR<br>8048004<br>ad-only |    |    |    |    |             |             |

|--------------|-----------------------------|----|----|----|----|-------------|-------------|

| 31           | 30                          | 29 | 28 | 27 | 26 | 25          | 24          |

| —            | -                           | _  | —  | —  | _  | _           | -           |

| 23           | 22                          | 21 | 20 | 19 | 18 | 17<br>SRCMP | 16<br>NRSTL |

|              |                             |    |    |    |    | GICOMI      | NICOTE      |

| 15           | 14                          | 13 | 12 | 11 | 10 | 9           | 8           |

| _            | —                           | _  | —  | —  |    | RSTTYP      |             |

| 7            | 6                           | 5  | 4  | 3  | 2  | 1           | 0           |

| _            | _                           | _  | _  | _  |    | -           | URSTS       |

#### **URSTS: User Reset Status**

0: No high-to-low edge on NRST happened since the last read of RSTC\_SR.

1: At least one high-to-low transition of NRST has been detected since the last read of RSTC\_SR. Reading the RSTC\_SR resets the URSTS bit and clears the interrupt.

#### **RSTTYP: Reset Type**

This field reports the cause of the last processor reset. Reading this RSTC\_SR does not reset this field.

| Value | Name        | Description                              |  |  |  |  |

|-------|-------------|------------------------------------------|--|--|--|--|

| 0     | GENERAL_RST | Both VDDCORE and VDDBU rising            |  |  |  |  |

| 1     | WKUP_RST    | VDDCORE rising                           |  |  |  |  |

| 2     | WDT_RST     | Watchdog fault occurred                  |  |  |  |  |

| 3     | SOFT_RST    | Processor reset required by the software |  |  |  |  |

| 4     | USER_RST    | NRST pin detected low                    |  |  |  |  |

#### **NRSTL: NRST Pin Level**

This bit records the level of the NRST pin sampled on each Master Clock (MCK) rising edge.

#### SRCMP: Software Reset Command in Progress

0: No software command is being performed by the reset controller. The reset controller is ready for a software command.

1: A software reset command is being performed by the reset controller. The reset controller is busy.

## 26.6.12 RTC Interrupt Enable Register

## Address: 0xF80480D0

#### Access: Write-only

| 31 | 30 | 29      | 28    | 27    | 26    | 25    | 24    |

|----|----|---------|-------|-------|-------|-------|-------|

| -  | -  |         | —     | -     | -     | -     | _     |

| 23 | 22 | 21      | 20    | 19    | 18    | 17    | 16    |

| -  | -  |         | —     | -     | -     | -     | _     |

| 15 | 14 | 13      | 12    | 11    | 10    | 9     | 8     |

| _  | -  | I       | _     | -     | -     | -     | _     |

| 7  | 6  | 5       | 4     | 3     | 2     | 1     | 0     |

| _  | _  | TDERREN | CALEN | TIMEN | SECEN | ALREN | ACKEN |

#### ACKEN: Acknowledge Update Interrupt Enable

0: No effect.

1: The acknowledge for update interrupt is enabled.

#### ALREN: Alarm Interrupt Enable

0: No effect.

1: The alarm interrupt is enabled.

#### SECEN: Second Event Interrupt Enable

0: No effect.

1: The second periodic interrupt is enabled.

#### **TIMEN: Time Event Interrupt Enable**

0: No effect.

1: The selected time event interrupt is enabled.

If the RTC is configured in UTC mode, this bit has no effect.

#### CALEN: Calendar Event Interrupt Enable

0: No effect.

1: The selected calendar event interrupt is enabled.

If the RTC is configured in UTC mode, this bit has no effect.

#### **TDERREN: Time and/or Date Error Interrupt Enable**

0: No effect.

1: The time and date error interrupt is enabled.

If the RTC is configured in UTC mode, this bit has no effect.

## 29.7.1 PTC Command Register

| Name: | PTC | CMD |

|-------|-----|-----|

| nume. | 110 |     |

Access: Write-only

| 7 | 6 | 5 | 4 | 3 | 2  | 1  | 0 |

|---|---|---|---|---|----|----|---|

| - | - | - | - |   | CN | 1D |   |

#### **CMD: Host Command**

Issues commands to the pPP.

| Value   | Name      | Description                                              |

|---------|-----------|----------------------------------------------------------|

| 0x0     | NO_ACTION | -                                                        |

| 0x1     | STOP      | Waits for ongoing execution to complete, then stops.     |

| 0x2     | RESET     | Stops and resets.                                        |

| 0x3     | Reserved  | -                                                        |

| 0x4     | ABORT     | Stops without waiting for ongoing execution to complete. |

| 0x5     | RUN       | Starts execution (from stopped state).                   |

| 0x6–0xF | Reserved  | -                                                        |

## 33.22.27 PMC Peripheral Control Register

| Address: | PMC_PCR<br>0xF001410C<br>Read/Write |            |           |         |         |             |         |

|----------|-------------------------------------|------------|-----------|---------|---------|-------------|---------|

| 31       | 30                                  | 29         | 28        | 27      | 26      | 25          | 24      |

| _        | _                                   | GCKEN      | EN        |         | GCK     | DIV         |         |

| 23       | 22<br>GCł                           | 21<br>KDIV | 20        | 19<br>— | 18<br>- | 17          | 16<br>- |

| 15       | 14                                  | 13         | 12<br>CMD | 11      | 10      | 9<br>GCKCSS | 8       |

| 7        | 6                                   | 5          | 4         | 3       | 2       | 1           | 0       |

| -        |                                     |            |           | PID     |         |             |         |

#### **PID: Peripheral ID**

Peripheral ID selection from PID2 to the maximum PID number. This refers to identifiers as defined in the section "Peripheral Identifiers".

#### GCKCSS: Generic Clock Source Selection

| Value | Name      | Description                 |

|-------|-----------|-----------------------------|

| 0     | SLOW_CLK  | Slow clock is selected      |

| 1     | MAIN_CLK  | Main clock is selected      |

| 2     | PLLA_CLK  | PLLACK is selected          |

| 3     | UPLL_CLK  | UPLL Clock is selected      |

| 4     | MCK_CLK   | Master Clock is selected    |

| 5     | AUDIO_CLK | Audio PLL clock is selected |

#### **CMD: Command**

0: Read mode

1: Write mode

#### **GCKDIV: Generic Clock Division Ratio**

Generic clock is: selected clock period divided by GCKDIV + 1. GCKDIV must not be changed while the peripheral selects GCLK (e.g., bit rate, etc.).

#### **EN: Enable**

0: The selected peripheral clock is disabled.

1: The selected peripheral clock is enabled.

#### **GCKEN: Generic Clock Enable**

0: The selected generic clock is disabled.

1: The selected generic clock is enabled.

## 34.7.16 Secure PIO Configuration Register

Name: S\_PIO\_CFGRx [x=0..3]

Address: 0xFC039004 [0], 0xFC039044 [1], 0xFC039084 [2], 0xFC0390C4 [3]

Access: Read/Write

| 31      | 30   | 29     | 28   | 27 | 26   | 25     | 24   |

|---------|------|--------|------|----|------|--------|------|

| -       | ICFS | PCFS   | -    |    |      | EVTSEL |      |

| 23      | 22   | 21     | 20   | 19 | 18   | 17     | 16   |

| -       | -    | —      | -    | —  | -    | DRV    | ′STR |

| 15      | 14   | 13     | 12   | 11 | 10   | 9      | 8    |

| SCHMITT | OPD  | IFSCEN | IFEN | —  | PDEN | PUEN   | DIR  |

| 7       | 6    | 5      | 4    | 3  | 2    | 1      | 0    |

| -       | -    | -      | -    | —  |      | FUNC   |      |

This register can only be written if the WPEN bit is cleared in the Secure PIO Write Protection Mode Register.

Writing this register will only affect I/O lines enabled in the S\_PIO\_MSKRx.

#### **FUNC: I/O Line Function**

This field defines the function for I/O lines of the I/O group x according to the Secure PIO Mask Register.

| Value | Name     | Description                                         |

|-------|----------|-----------------------------------------------------|

| 0     | GPIO     | Select the PIO mode for the selected I/O lines.     |

| 1     | PERIPH_A | Select the peripheral A for the selected I/O lines. |

| 2     | PERIPH_B | Select the peripheral B for the selected I/O lines. |

| 3     | PERIPH_C | Select the peripheral C for the selected I/O lines. |

| 4     | PERIPH_D | Select the peripheral D for the selected I/O lines. |

| 5     | PERIPH_E | Select the peripheral E for the selected I/O lines. |

| 6     | PERIPH_F | Select the peripheral F for the selected I/O lines. |

| 7     | PERIPH_G | Select the peripheral G for the selected I/O lines. |

#### **DIR: Direction**

This bit defines the direction of the I/O lines of the I/O group x according to the Secure PIO Mask Register.

0 (INPUT): The selected I/O lines are pure inputs.

1 (OUTPUT): The selected I/O lines are enabled in output.

#### **PUEN: Pull-Up Enable**

This bit defines the pull-up configuration of the I/O lines of the I/O group x according to the Secure PIO Mask Register.

0 (DISABLED): Pull-Up is disabled for the selected I/O lines.

1 (ENABLED): Pull-Up is enabled for the selected I/O lines.

#### PDEN: Pull-Down Enable

This bit defines the pull-down configuration of the I/O lines of the I/O group x according to the Secure PIO Mask Register. 0 (DISABLED): Pull-Down is disabled for the selected I/O lines.

1 (ENABLED): Pull-Down is enabled for the selected I/O lines only if PUEN is  $0^{(1)}$ .

Note 1: PDEN can be written to 1 only if PUEN is written to 0.

#### **IFEN: Input Filter Enable**

This bit defines if the glitch filtering is used for the I/O lines of the I/O group x according to the Secure PIO Mask Register.

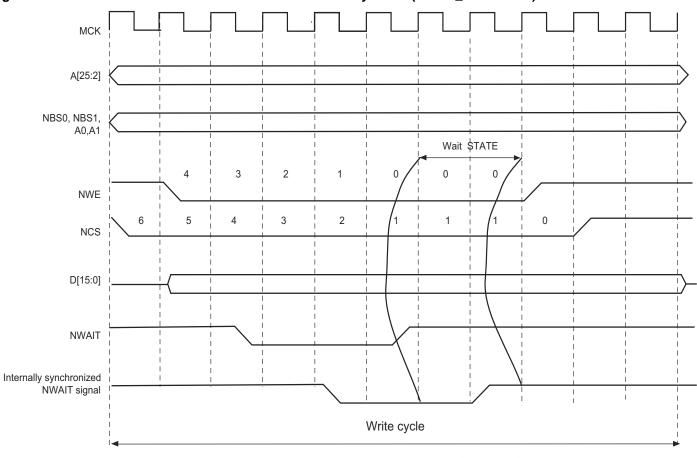

Figure 37-25: NWAIT Assertion in Write Access: Ready Mode (EXNW\_MODE = 11)

EXNW\_MODE = 11 (Ready mode) WRITE\_MODE = 1 (NWE\_controlled)

NWE\_PULSE = 5 NCS\_WR\_PULSE = 7

#### 39.6.4.12 19 bpp Unpacked Memory Mapping with Transparency Bit, RGB 1:6:6:6

#### Table 39-23: 19 bpp Unpacked Memory Mapping, Little Endian Organization

| Mem addr     | 0x3 | •  |    |    |    |    |    |    | 0x2 | 2  |    |    |    |    |    |    | 0x1 |      |    |    |    |    |     |      | 0x0 | ) |   |   |     |      |   |   |

|--------------|-----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|-----|------|----|----|----|----|-----|------|-----|---|---|---|-----|------|---|---|

| Bit          | 31  | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14   | 13 | 12 | 11 | 10 | 9   | 8    | 7   | 6 | 5 | 4 | 3   | 2    | 1 | 0 |

| Pixel 19 bpp |     |    |    | -  | -  |    |    |    |     |    | -  |    |    | A0 |    |    | R0[ | 5:0] |    |    |    |    | G0[ | 5:0] |     |   |   |   | B0[ | 5:0] |   |   |

#### 39.6.4.13 19 bpp Packed Memory Mapping with Transparency Bit, ARGB 1:6:6:6

#### Table 39-24: 19 bpp Packed Memory Mapping, Little Endian Organization at Address 0x0, 0x1, 0x2, 0x3

| Mem addr     | 0x3 | 3     |    |    |     |      |    |    | 0x2 | 2  |    |    |    |    |    |    | 0x1 |      |    |    |    |    |     |      | 0x0 | ) |   |   |     |      |   |   |

|--------------|-----|-------|----|----|-----|------|----|----|-----|----|----|----|----|----|----|----|-----|------|----|----|----|----|-----|------|-----|---|---|---|-----|------|---|---|

| Bit          | 31  | 30    | 29 | 28 | 27  | 26   | 25 | 24 | 23  | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14   | 13 | 12 | 11 | 10 | 9   | 8    | 7   | 6 | 5 | 4 | 3   | 2    | 1 | 0 |

| Pixel 19 bpp | G1  | [1:0] |    |    | B1[ | 5:0] |    |    |     |    | -  |    |    | A0 |    |    | R0[ | 5:0] |    |    |    |    | G0[ | 5:0] |     |   |   |   | B0[ | 5:0] |   |   |

#### Table 39-25: 19 bpp Packed Memory Mapping, Little Endian Organization at Address 0x4, 0x5, 0x6, 0x7

| Mem addr     | 0x7 | ,   |      |    |    |    |     |      | 0x6 | 5  |    |    |     |      |    |    | 0x5 |    |    |    |    |    |   |   | 0x4 | Ļ    |   |   |   |     |      |   |

|--------------|-----|-----|------|----|----|----|-----|------|-----|----|----|----|-----|------|----|----|-----|----|----|----|----|----|---|---|-----|------|---|---|---|-----|------|---|

| Bit          | 31  | 30  | 29   | 28 | 27 | 26 | 25  | 24   | 23  | 22 | 21 | 20 | 19  | 18   | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6    | 5 | 4 | 3 | 2   | 1    | 0 |

| Pixel 19 bpp |     | R2[ | 3:0] |    |    |    | G2[ | 5:0] |     |    |    |    | B2[ | 5:0] |    |    |     |    | _  |    |    | A1 |   |   | R1[ | 5:2] |   |   |   | G1[ | 5:2] |   |

#### Table 39-26: 18 bpp Packed Memory Mapping, Little Endian Organization at Address 0x8, 0x9, 0xA, 0xB

| Mem addr     | 0xE | 3    |    |    |     |      |    |    | 0xA | ٩  |    |    |    |    |     |      | 0x9 |    |    |    |     |      |   |   | 0x8 | ; |     |      |   |   |     |      |

|--------------|-----|------|----|----|-----|------|----|----|-----|----|----|----|----|----|-----|------|-----|----|----|----|-----|------|---|---|-----|---|-----|------|---|---|-----|------|

| Bit          | 31  | 30   | 29 | 28 | 27  | 26   | 25 | 24 | 23  | 22 | 21 | 20 | 19 | 18 | 17  | 16   | 15  | 14 | 13 | 12 | 11  | 10   | 9 | 8 | 7   | 6 | 5   | 4    | 3 | 2 | 1   | 0    |

| Pixel 19 bpp | G4[ | 1:0] |    |    | B4[ | 5:0] |    |    |     | -  |    | A3 |    |    | R3[ | 5:0] |     |    |    |    | G3[ | 5:0] |   |   |     |   | B3[ | 3:0] |   |   | R2[ | 5:4] |

#### 39.6.4.14 24 bpp Unpacked Memory Mapping, RGB 8:8:8

#### Table 39-27: 24 bpp Memory Mapping, Little Endian Organization

| Mem addr     | 0x3 | 3  |    |    |    |    |    |    | 0x2 | 2  |    |     |      |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |      |   |   |   |

|--------------|-----|----|----|----|----|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|------|---|---|---|

| Bit          | 31  | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

| Pixel 24 bpp |     |    |    | -  | _  |    |    |    |     |    |    | R0[ | 7:0] |    |    |    | ·   |    | ·  | G0[ | 7:0] | ·  |   |   |     |   |   | B0[ | 7:0] |   |   |   |

#### 39.6.4.15 24 bpp Packed Memory Mapping, RGB 8:8:8

#### Table 39-28: 24 bpp Packed Memory Mapping, Little Endian Organization at Address 0x0, 0x1, 0x2, 0x3

| Mem addr     | 0x3 | 3  |    |     |       |    |    |    | 0x2 | 2  |    |     |      |    |    |    | 0x1 |    |    |     |      |    |   |   | 0x0 | ) |   |     |      |   |   |   |

|--------------|-----|----|----|-----|-------|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|------|---|---|---|

| Bit          | 31  | 30 | 29 | 28  | 27    | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

| Pixel 24 bpp |     |    |    | B1[ | [7:0] |    |    |    |     |    |    | R0[ | 7:0] | ·  |    |    |     |    |    | G0[ | 7:0] |    |   |   |     |   |   | B0[ | 7:0] |   |   |   |

#### Table 39-29: 24 bpp Packed Memory Mapping, Little Endian Organization at Address 0x4, 0x5, 0x6, 0x7

| Mem addr     | <b>0</b> x | 7  |    |     |      |    |    |    | 0x6 | 5  |    |     |      |    |    |    | 0x5 | 5  |    |     |      |    |   |   | 0x4 | 4 |   |     |       |   |   |   |

|--------------|------------|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|----|----|-----|----|----|-----|------|----|---|---|-----|---|---|-----|-------|---|---|---|

| Bit          | 31         | 30 | 29 | 28  | 27   | 26 | 25 | 24 | 23  | 22 | 21 | 20  | 19   | 18 | 17 | 16 | 15  | 14 | 13 | 12  | 11   | 10 | 9 | 8 | 7   | 6 | 5 | 4   | 3     | 2 | 1 | 0 |

| Pixel 24 bpp |            |    |    | G2[ | 7:0] |    |    |    |     |    |    | B2[ | 7:0] |    |    |    |     |    |    | R1[ | 7:0] |    |   |   |     |   |   | G1[ | [7:0] |   |   |   |

# SAMA5D2 SERIES

## 40.8.6 GMAC Transmit Status Register

| Address: 0xF8 | C_TSR<br>008014<br>d/Write |             |          |           |          |          |            |

|---------------|----------------------------|-------------|----------|-----------|----------|----------|------------|

| 31            | 30                         | 29          | 28       | 27        | 26       | 25       | 24         |

| -             | -                          | -           | -        | -         | -        | -        | -          |

| 23            | 22                         | 21          | 20       | 19<br>—   | 18<br>—  | 17       | 16         |

| 15            | 14                         | 13          | 12       | 11        | 10       | 9        | 8<br>HRESP |

| 7             | 6                          | 5<br>TXCOMP | 4<br>TFC | 3<br>TXGO | 2<br>RLE | 1<br>COL | 0<br>UBR   |

#### UBR: Used Bit Read

Set when a transmit buffer descriptor is read with its used bit set. Writing a one clears this bit.

#### **COL: Collision Occurred**

Set by the assertion of collision. Writing a one clears this bit. When operating in 10/100 mode, this status indicates either a collision or a late collision.

#### **RLE: Retry Limit Exceeded**

Writing a one clears this bit.

#### **TXGO: Transmit Go**

Transmit go, if high transmit is active. When using the DMA interface this bit represents the TXGO variable as specified in the transmit buffer description.

#### TFC: Transmit Frame Corruption Due to AHB Error

Transmit frame corruption due to AHB error. Set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted).

Also set in DMA packet buffer mode if single frame is too large for configured packet buffer memory size.

Writing a one clears this bit.

#### **TXCOMP: Transmit Complete**

Set when a frame has been transmitted. Writing a one clears this bit.

#### HRESP: HRESP Not OK

Set when the DMA block sees HRESP not OK. Writing a one clears this bit.

| 40.8.38  | GMAC Specific Ad | dress 1 Mask B | Bottom Registe | er |    |    |    |

|----------|------------------|----------------|----------------|----|----|----|----|

| Name:    | GMAC_SAMB1       |                |                |    |    |    |    |

| Address: | 0xF80080C8       |                |                |    |    |    |    |

| Access:  | Read/Write       |                |                |    |    |    |    |

| 31       | 30               | 29             | 28             | 27 | 26 | 25 | 24 |

|          |                  |                | AD             | DR |    |    |    |

| 23       | 22               | 21             | 20             | 19 | 18 | 17 | 16 |

|          |                  |                | AD             | DR |    |    |    |

| 15       | 14               | 13             | 12             | 11 | 10 | 9  | 8  |

|          |                  |                | AD             | DR |    |    |    |

| 7        | 6                | 5              | 4              | 3  | 2  | 1  | 0  |

|          |                  |                | AD             | DR |    |    |    |

#### onifin Address 1 Mark Pottom Pogistor 10 0 20 CMAC C.

## ADDR: Specific Address 1 Mask

Setting a bit to one masks the corresponding bit in the Specific Address 1 Register.

## 41.7.13 UDPHS Endpoint Control Register (Control, Bulk, Interrupt Endpoints)

#### Name: UDPHS\_EPTCTLx [x=0..15]

Read-only

Access:

Address: 0xFC02C10C [0], 0xFC02C12C [1], 0xFC02C14C [2], 0xFC02C16C [3], 0xFC02C18C [4], 0xFC02C1AC [5], 0xFC02C1CC [6], 0xFC02C1EC [7], 0xFC02C20C [8], 0xFC02C22C [9], 0xFC02C24C [10], 0xFC02C26C [11], 0xFC02C28C [12], 0xFC02C2AC [13], 0xFC02C2CC [14], 0xFC02C2EC [15]

| 31        | 30     | 29        | 28       | 27         | 26        | 25         | 24        |  |  |  |   |

|-----------|--------|-----------|----------|------------|-----------|------------|-----------|--|--|--|---|

| SHRT_PCKT | —      | —         |          |            |           |            |           |  |  |  | — |

| 23        | 22     | 21        | 20       | 19 18 17   |           | 16         |           |  |  |  |   |

| -         | -      | -         | -        | -          | BUSY_BANK | -          | -         |  |  |  |   |

| 15        | 14     | 13        | 12       | 11         | 10        | 9          | 8         |  |  |  |   |

| NAK_OUT   | NAK_IN | STALL_SNT | RX_SETUP | TXRDY      | TX_COMPLT | RXRDY_TXKL | ERR_OVFLW |  |  |  |   |

| 7         | 6      | 5         | 4        | 3          | 2         | 1          | 0         |  |  |  |   |

| -         | -      | -         | NYET_DIS | INTDIS_DMA | -         | AUTO_VALID | EPT_ENABL |  |  |  |   |

This register view is relevant only if EPT\_TYPE = 0x0, 0x2 or 0x3 in "UDPHS Endpoint Configuration Register".

#### EPT\_ENABL: Endpoint Enable (cleared upon USB reset)

0: The endpoint is disabled according to the device configuration. Endpoint 0 should always be enabled after a hardware or UDPHS bus reset and participate in the device configuration.

1: The endpoint is enabled according to the device configuration.

#### AUTO\_VALID: Packet Auto-Valid Enabled (Not for CONTROL Endpoints) (cleared upon USB reset)

Set this bit to automatically validate the current packet and switch to the next bank for both IN and OUT endpoints.

#### For IN Transfer:

If this bit is set, the UDPHS\_EPTSTAx register TXRDY bit is set automatically when the current bank is full and at the end of DMA buffer if the UDPHS\_DMACONTROLx register END\_B\_EN bit is set.

The user may still set the UDPHS\_EPTSTAx register TXRDY bit if the current bank is not full, unless the user needs to send a Zero Length Packet by software.

#### For OUT Transfer:

If this bit is set, the UDPHS\_EPTSTAx register RXRDY\_TXKL bit is automatically reset for the current bank when the last packet byte has been read from the bank FIFO or at the end of DMA buffer if the UDPHS\_DMACONTROLx register END\_B\_EN bit is set. For example, to truncate a padded data packet when the actual data transfer size is reached.

The user may still clear the UDPHS\_EPTSTAx register RXRDY\_TXKL bit, for example, after completing a DMA buffer by software if UDPHS\_DMACONTROLx register END\_B\_EN bit was disabled or in order to cancel the read of the remaining data bank(s).

#### INTDIS\_DMA: Interrupt Disables DMA (cleared upon USB reset)

If set, when an enabled endpoint-originated interrupt is triggered, the DMA request is disabled regardless of the UDPHS\_IEN register EPT\_x bit for this endpoint. Then, the firmware will have to clear or disable the interrupt source or clear this bit if transfer completion is needed.

If the exception raised is associated with the new system bank packet, then the previous DMA packet transfer is normally completed, but the new DMA packet transfer is not started (not requested).

If the exception raised is not associated to a new system bank packet (NAK\_IN, NAK\_OUT, etc.), then the request cancellation may happen at any time and may immediately stop the current DMA transfer.

This may be used, for example, to identify or prevent an erroneous packet to be transferred into a buffer or to complete a DMA buffer by software after reception of a short packet.

#### NYET\_DIS: NYET Disable (Only for High Speed Bulk OUT Endpoints) (cleared upon USB reset)

0: Lets the hardware handle the handshake response for the High Speed Bulk OUT transfer.

| Name:    | TWIHS_FIER           |                                |       |       |        |       |       |  |  |  |

|----------|----------------------|--------------------------------|-------|-------|--------|-------|-------|--|--|--|

| Address: | 0xF8028064 (0), 0xF0 | 0xF8028064 (0), 0xFC028064 (1) |       |       |        |       |       |  |  |  |

| Access:  | Write-only           |                                |       |       |        |       |       |  |  |  |

| 31       | 30                   | 29                             | 28    | 27    | 26     | 25    | 24    |  |  |  |

| _        | -                    | -                              | _     | _     | _      | _     | _     |  |  |  |

| 23       | 22                   | 21                             | 20    | 19    | 18     | 17    | 16    |  |  |  |

| _        | _                    | _                              | _     | _     | _      | _     | _     |  |  |  |

| 15       | 14                   | 13                             | 12    | 11    | 10     | 9     | 8     |  |  |  |

| -        | -                    | -                              | —     | —     | —      | —     | -     |  |  |  |

| 7        | 6                    | 5                              | 4     | 3     | 2      | 1     | 0     |  |  |  |

| RXFPT    | EF TXFPTEF           | RXFTHF                         | RXFFF | RXFEF | TXFTHF | TXFFF | TXFEF |  |  |  |

## 46.7.23 TWIHS FIFO Interrupt Enable Register

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Enables the corresponding interrupt.

**TXFEF: TXFEF Interrupt Enable**

**TXFFF: TXFFF Interrupt Enable**

**TXFTHF: TXFTHF Interrupt Enable**

**RXFEF: RXFEF Interrupt Enable**

**RXFFF: RXFFF Interrupt Enable**

**RXFTHF: RXFTHF Interrupt Enable**

**TXFPTEF: TXFPTEF Interrupt Enable**

**RXFPTEF: RXFPTEF Interrupt Enable**

## SAMA5D2 SERIES

## 47.10.6 USART Mode Register

Name: FLEX\_US\_MR

Address: 0xF8034204 (0), 0xF8038204 (1), 0xFC010204 (2), 0xFC014204 (3), 0xFC018204 (4)

Access: Read/Write

| 31      | 30       | 29     | 28     | 27         | 26   | 25            | 24   |  |  |

|---------|----------|--------|--------|------------|------|---------------|------|--|--|

| ONEBIT  | MODSYNC  | MAN    | FILTER | _          |      | MAX_ITERATION |      |  |  |

| 23      | 22       | 21     | 20     | 19         | 18   | 17            | 16   |  |  |

| INVDATA | VAR_SYNC | DSNACK | INACK  | OVER       | CLKO | MODE9         | MSBF |  |  |

| 15      | 14       | 13     | 12     | 11         | 10   | 9             | 8    |  |  |

| CHN     | NODE     | NBSTOP |        | PAR SYN    |      |               | SYNC |  |  |

| 7       | 6        | 5      | 4      | 3          | 2    | 1             | 0    |  |  |

| CH      | HRL      | USC    | LKS    | USART_MODE |      |               |      |  |  |

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

For SPI configuration, see Section 47.10.7 "USART Mode Register (SPI\_MODE)".

## USART\_MODE: USART Mode of Operation

| Value | Name           | Description                                                        |

|-------|----------------|--------------------------------------------------------------------|

| 0x0   | NORMAL         | Normal mode                                                        |

| 0x1   | RS485          | RS485                                                              |

| 0x2   | HW_HANDSHAKING | Hardware handshaking                                               |

| 0x4   | IS07816_T_0    | IS07816 Protocol: T = 0                                            |

| 0x6   | IS07816_T_1    | IS07816 Protocol: T = 1                                            |

| 0x8   | IRDA           | IrDA                                                               |

| 0xA   | LIN_MASTER     | LIN Master mode                                                    |

| 0xB   | LIN_SLAVE      | LIN Slave mode                                                     |

| 0xE   | SPI_MASTER     | SPI Master mode (CLKO must be written to 1 and USCLKS = 0, 1 or 2) |

| 0xF   | SPI_SLAVE      | SPI Slave mode                                                     |

## **USCLKS: Clock Selection**

| Value | Name | Description                                                                                              |

|-------|------|----------------------------------------------------------------------------------------------------------|

| 0     | MCK  | Peripheral clock is selected                                                                             |

| 1     | DIV  | Peripheral clock divided (DIV = 8) is selected                                                           |

| 2     | GCLK | PMC generic clock is selected. If the SCK pin is driven (CLKO = 1), the CD field must be greater than 1. |

| 3     | SCK  | External pin SCK is selected                                                                             |

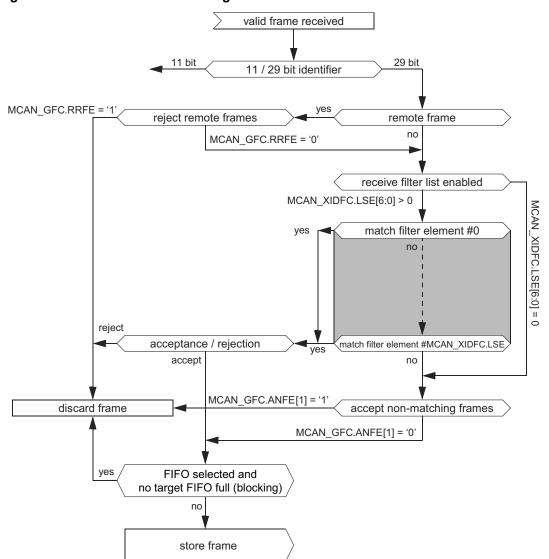

#### • Extended Message ID Filtering

Figure 53-6 below shows the flow for extended Message ID (29-bit Identifier) filtering. The Extended Message ID Filter element is described in Section 53.5.7.6.

Controlled by MCAN\_GFC and MCAN\_XIDFC Message ID, Remote Transmission Request bit (RTR), and the Identifier Extension bit (IDE) of received frames are compared against the list of configured filter elements.

MCAN\_XIDAM is ANDed with the received identifier before the filter list is executed.

## Figure 53-6: Extended Message ID Filter Path

## 53.6.21 MCAN Standard ID Filter Configuration

|         | MCAN_SIDFC<br>0xF8054084 (0), 0> | FC050084 (1) |     |     |    |    |   |

|---------|----------------------------------|--------------|-----|-----|----|----|---|

| Access: | Read/Write                       |              |     |     |    |    |   |

| 31      | 30                               | 29           | 28  | 27  | 26 | 25 |   |

| -       | -                                | -            | -   | -   | -  | -  |   |

| 23      | 22                               | 21           | 20  | 19  | 18 | 17 |   |

|         |                                  |              | L   | SS  |    |    |   |

| 15      | 14                               | 13           | 12  | 11  | 10 | 9  |   |

|         |                                  |              | FL  | SSA |    |    |   |

| 7       | 6                                | 5            | 4   | 3   | 2  | 1  |   |

|         |                                  | FLS          | SSA |     |    | _  | Τ |

|         |                                  |              |     |     |    |    |   |

Settings for 11-bit standard Message ID filtering. The Standard ID Filter Configuration controls the filter path for standard messages as described in Figure 53-5.

This register can only be written if the bits CCE and INIT are set in MCAN CC Control Register.

#### FLSSA: Filter List Standard Start Address

Start address of standard Message ID filter list (32-bit word address, see Figure 53-12).

Write FLSSA with the bits [15:2] of the 32-bit address.

### LSS: List Size Standard

0: No standard Message ID filter.

1-128: Number of standard Message ID filter elements.

>128: Values greater than 128 are interpreted as 128.

24 -16

8

0

## 53.6.38 MCAN Transmit Buffer Request Pending

Name: MCAN\_TXBRP

Address: 0xF80540CC (0), 0xFC0500CC (1)

#### Access: Read-only

| 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TRP31 | TRP30 | TRP29 | TRP28 | TRP27 | TRP26 | TRP25 | TRP24 |

| 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| TRP23 | TRP22 | TRP21 | TRP20 | TRP19 | TRP18 | TRP17 | TRP16 |

| 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| TRP15 | TRP14 | TRP13 | TRP12 | TRP11 | TRP10 | TRP9  | TRP8  |

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| TRP7  | TRP6  | TRP5  | TRP4  | TRP3  | TRP2  | TRP1  | TRP0  |

#### TRPx: Transmission Request Pending for Buffer x

Each Tx Buffer has its own Transmission Request Pending bit. The bits are set via register MCAN\_TXBAR. The bits are reset after a requested transmission has completed or has been cancelled via register MCAN\_TXBCR.

TXBRP bits are set only for those Tx Buffers configured via MCAN\_TXBC. After a MCAN\_TXBRP bit has been set, a Tx scan (see Section 53.5.5) is started to check for the pending Tx request with the highest priority (Tx Buffer with lowest Message ID).

A cancellation request resets the corresponding transmission request pending bit of register MCAN\_TXBRP. In case a transmission has already been started when a cancellation is requested, this is done at the end of the transmission, regardless whether the transmission was successful or not. The cancellation request bits are reset directly after the corresponding TXBRP bit has been reset.

After a cancellation has been requested, a finished cancellation is signalled via MCAN\_TXBCF.

- after successful transmission together with the corresponding MCAN\_TXBTO bit.

- when the transmission has not yet been started at the point of cancellation.

- when the transmission has been aborted due to lost arbitration.

- when an error occurred during frame transmission.

In DAR mode, all transmissions are automatically cancelled if they are not successful. The corresponding MCAN\_TXBCF bit is set for all unsuccessful transmissions.

0: No transmission request pending

1: Transmission request pending

**Note:** MCAN\_TXBRP bits which are set while a Tx scan is in progress are not considered during this particular Tx scan. In case a cancellation is requested for such a Tx Buffer, this Add Request is cancelled immediately, the corresponding MCAN\_TXBRP bit is reset.

### Table 66-97: ISC IOSET3 Timings

|                  | Power Supply                                           |     | BV  | 3.: |     |      |

|------------------|--------------------------------------------------------|-----|-----|-----|-----|------|

| Symbol           | Parameter                                              | Min | Max | Min | Max | Unit |

| ISC <sub>1</sub> | DATA setup time before PIXCLK rises                    | 4.6 | -   | 4.2 | -   | ns   |

| ISC <sub>2</sub> | DATA hold time after PIXCLK rises                      | 0.5 | _   | 0.4 | _   | ns   |

| ISC <sub>3</sub> | VSYNC/HSYNC/FIELD setup time before PIXCLK rises       | 4.3 | _   | 4   | _   | ns   |

| ISC <sub>4</sub> | CONTROL VSYNC/HSYNC/FIELD hold time after PIXCLK rises | 1.5 | _   | 0.4 | -   | ns   |

| ISC <sub>5</sub> | PIXCLK frequency                                       | -   | 96  | -   | 96  | MHz  |

### Table 66-98: ISC IOSET4 Timings

|                  | Power Supply                                           | 1.3 | 8V  | 3.  |     |      |

|------------------|--------------------------------------------------------|-----|-----|-----|-----|------|

| Symbol           | Parameter                                              | Min | Max | Min | Max | Unit |

| ISC <sub>1</sub> | DATA setup time before PIXCLK rises                    | 4.3 | _   | 4   | -   | ns   |

| ISC <sub>2</sub> | DATA hold time after PIXCLK rises                      | 0.5 | _   | 0.4 | _   | ns   |

| ISC <sub>3</sub> | VSYNC/HSYNC/FIELD setup time before PIXCLK rises       | 4.2 | _   | 4   | _   | ns   |

| ISC <sub>4</sub> | CONTROL VSYNC/HSYNC/FIELD hold time after PIXCLK rises | 0.5 | _   | 0.3 | _   | ns   |

| ISC <sub>5</sub> | PIXCLK frequency                                       | _   | 96  | _   | 96  | MHz  |

## 66.25 SDMMC Timings

The Secure Digital Multimedia Card (SDMMC) Controller supports the embedded MultiMedia Card (e.MMC) Specification V4.51, the SD Memory Card Specification V3.0, and the SDIO V3.0 specification. It is compliant with the SD Host Controller Standard V3.0 specification.

Features are different for the two instances of SDMMC:

SDMMC0: SD 3.0, eMMC 4.51, 8 bits

SDMMC1: SD 2.0, eMMC 4.41, 4 bits only

In SDR104 mode (SD 3.0), SDMMC0 is limited to 120 MHz (instead of 208 MHz). In HS200 mode (eMMC 4.51), SDMMC0 is limited to 120 MHz (instead of 200 MHz).