#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

-XF

| Product Status                     | Active                                                                                            |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A5                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 500MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ MPE                                                                             |

| RAM Controllers                    | LPDDR1, LPDDR2, LPDDR3, DDR2, DDR3, DDR3L, QSPI                                                   |

| Graphics Acceleration              | Yes                                                                                               |

| Display & Interface<br>Controllers | Keyboard, LCD, Touchscreen                                                                        |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 + HSIC                                                                                    |

| Voltage - I/O                      | 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 85°C (TA)                                                                                 |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 196-TFBGA, CSBGA                                                                                  |

| Supplier Device Package            | 196-TFBGA (11x11)                                                                                 |

| Purchase URL                       | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d21c-cu                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 34.7.28 Secure PIO I/O Security Status Register

Name: S\_PIO\_IOSSRx [x=0..3]

Address: 0xFC039038 [0], 0xFC039078 [1], 0xFC0390B8 [2], 0xFC0390F8 [3]

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

#### P0-P31: I/O Security Status

0 (SECURE): The I/O line of the I/O group x is in Secure mode.

1 (NON\_SECURE): The I/O line of the I/O group x is in Non-Secure mode.

- 5. A NOP command is issued to the DDR2-SDRAM. Program the NOP command in the MPDDRC\_MR. The application must configure the MODE field to 1 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any DDR2-SDRAM address to acknowledge this command. CKE is now driven high.

- 6. An All Banks Precharge command is issued to the DDR2-SDRAM. Program All Banks Precharge command in the MPDDRC\_MR. The application must configure the MODE field to 2 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any DDR2-SDRAM address to acknowledge this command.

- 7. An Extended Mode Register Set (EMRS2) cycle is issued to choose between commercial or high temperature operations. The application must configure the MODE field to 5 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to the DDR2-SDRAM to acknowledge this command. The write address must be chosen so that signal BA[1] is set to 1 and signal BA[0] is set to 0. For example: with a 16-bit, 128-Mbit, DDR2-SDRAM (12 rows, 9 columns, 4 banks), the DDR2-SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x00800000; with a 32-bit, 1-Gbit, DDR2-SDRAM (14 rows, 10 columns, 8 banks), the SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x08000000.

Note: This address is given as an example only. The real address depends on implementation in the product.

- 8. An Extended Mode Register Set (EMRS3) cycle is issued to set the Extended Mode register to 0. The application must configure the MODE field to 5 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to the DDR2-SDRAM to acknowledge this command. The write address must be chosen so that signal BA[1] is set to 1 and signal BA[0] is set to 1. For example: with a 16-bit, 128-Mbit, DDR2-SDRAM (12 rows, 9 columns, 4 banks), the DDR2-SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x00C00000; with a 32-bit, 1-Gbit, DDR2-SDRAM (14 rows, 10 columns, 8 banks), the SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x00C00000.

- 9. An Extended Mode Register Set (EMRS1) cycle is issued to enable DLL and to program D.I.C. (Output Driver Impedance Control). The application must configure the MODE field to 5 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to the DDR2-SDRAM to acknowledge this command. The write address must be chosen so that signal BA[1] is set to 0 and signal BA[0] is set to 1. For example: with a 16-bit, 128-Mbit, DDR2-SDRAM (12 rows, 9 columns, 4 banks), the DDR2-SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x00400000; with a 32-bit, 1-Gbit, DDR2-SDRAM (14 rows, 10 columns, 8 banks), the SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x0400000.

- 10. An additional 200 cycles of clock are required for locking DLL

- 11. Write a '1' to the DLL bit (enable DLL reset) in the Configuration register (MPDDRC\_CR).

- 12. A Mode Register Set (MRS) cycle is issued to reset DLL. The application must configure the MODE field to 3 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to the DDR2-SDRAM to acknowledge this command. The write address must be chosen so that signals BA[1:0] are set to 0. For example, the SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR.

- 13. An All Banks Precharge command is issued to the DDR2-SDRAM. Program the All Banks Precharge command in the MPDDRC\_MR. The application must configure the MODE field to 2 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any DDR2-SDRAM address to acknowledge this command.

- 14. Two autorefresh (CBR) cycles are provided. Program the Autorefresh command (CBR) in the MPDDRC\_MR. The application must configure the MODE field to 4 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any DDR2-SDRAM location twice to acknowledge these commands.

- 15. Write a '0' to the DLL bit (disable DLL reset) in the MPDDRC\_CR.

- 16. A Mode Register Set (MRS) cycle is issued to program parameters of the DDR2-SDRAM device, in particular CAS latency and to disable DLL reset. The application must configure the MODE field to 3 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to the DDR2-SDRAM to acknowledge this command. The write address must be chosen so that signals BA[1:0] are set to 0. For example: with a 16-bit, 128-Mbit, DDR2-SDRAM (12 rows, 9 columns, 4 banks) bank address, the SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR; with a 32-bit, 1-Gbit, DDR2-SDRAM (14 rows, 10 columns, 8 banks), the SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR.

- 17. Configure the OCD field (default OCD calibration) to 7 in the MPDDRC\_CR.

- 18. An Extended Mode Register Set (EMRS1) cycle is issued to the default OCD value. The application must configure the MODE field to 5 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to the DDR2-SDRAM to acknowledge this command. The write address must be chosen so that signal BA[1] is set to 0 and signal BA[0] is set to 1. For example: with a 16-bit, 128-Mbit, DDR2-SDRAM (12 rows, 9 columns, 4 banks), the DDR2-SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x00400000; with a 32-bit, 1-Gbit, DDR2-SDRAM (14 rows, 10 columns, 8 banks), the SDRAM write access should be done at the address: BASE\_ADDRESS\_DDR + 0x0400000.

to 63. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Reset command is now issued.

- 8. A pause of at least t<sub>INIT5</sub> must be observed before issuing any commands.

- 9. A Calibration command is issued to the low-power DDR3-SDRAM. Program the type of calibration in the Configuration register (MPDDRC\_CR): set the ZQ field to 3. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 10. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The ZQ Calibration command is now issued. Program the type of calibration in the MPDDRC\_CR: set the ZQ field to 2.

- 10. A Mode register Write command is issued to the low-power DDR3-SDRAM. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 1. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Write command is now issued.

- 11. A Mode register Write command is issued to the low-power DDR3-SDRAM. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 2. The Mode register Write command cycle is issued to program parameters of the low-power DDR3-SDRAM device, in particular CAS Latency. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Write command is now issued.

- 12. A Mode register Write command is issued to the low-power DDR3-SDRAM. In the MPDDRC\_MR, configure the MODE field 7 and the MRS field to 3. The Mode register Write command cycle is issued to program parameters of the low-power DDR3-SDRAM device, in particular Drive Strength and Slew Rate. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Write command is now issued.

- 13. A Mode register Write command is issued to the low-power DDR3-SDRAM. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 16. The Mode register Write command cycle is issued to program parameters of the low-power DDR3-SDRAM device, in particular Partial Array Self Refresh (PASR). Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Write command is now issued.

- 14. In the DDR Configuration register (SFR\_DDRCFG), the application must write a '1' to bits 17 and 16 to open the input buffers.

- 15. A NOP command is issued to the low-power DDR3-SDRAM. Program the NOP command in the Mode register (MPDDRC\_MR). The application must configure the MODE field to 1 in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command.

- 16. A Mode register Read command is issued to the low-power DDR3-SDRAM. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 5. The Mode register Read command cycle is used to read the LPDDR3 Manufacturer ID from the low-power DDR3-SDRAM mode registers. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Read command is now issued. The LPDDR3 Manufacturer ID is set in register MPDDRC\_MD. See Section 36.7.8 "MPDDRC Memory Device Register".

- 17. A Mode register Read command is issued to the low-power DDR3-SDRAM. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 6. The Mode register Read command cycle is used to read the Revision ID1 from the low-power DDR3-SDRAM mode registers. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Read command is now issued. Revision ID1 is set in register MPDDRC\_MD. See Section 36.7.8 "MPDDRC Memory Device Register".

- 18. A Mode register Read command is issued to the low-power DDR3-SDRAM. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 8. The Mode register Read command cycle is used to read memory organization (I/O width, Density, Type) from the low-power DDR3-SDRAM mode registers. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Read command is now issued. Memory organization is set in register MPDDRC\_MD. See Section 36.7.8 "MPDDRC Memory Device Register".

- 19. A Mode register Read command is issued to the low-power DDR3-SDRAM. In MPDDRC\_MR, configure the MODE field to 7 and the MRS field to 0. The Mode register Read command cycle is used to read the device information (RZQI, DAI) from the low-power DDR3-SDRAM mode registers. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowledge this command. The Mode register Read command is now issued. Device information RZQI is set in register Timing Calibration (see Section 36.7.11 "MPDDRC Low-power DDR3 and DDR3 Timing Calibration Register") and DAI is set in Mode register (see Section 36.7.1 "MPDDRC Mode Register").

- 20. A Normal Mode command is provided. Program the Normal mode in the MPDDRC\_MR. Read the MPDDRC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any low-power DDR3-SDRAM address to acknowl-

| Name: HSM    | MC_ELPRIM |    |    |    |    |    |    |  |  |

|--------------|-----------|----|----|----|----|----|----|--|--|

| Address: 0xF | 8014504   |    |    |    |    |    |    |  |  |

| Access: Rea  | id-only   |    |    |    |    |    |    |  |  |

| 31           | 30        | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

| _            | —         | _  | —  | —  | —  | _  | -  |  |  |

| 23           | 22        | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

| -            | —         | -  | -  | -  | -  | —  | -  |  |  |

| 15           | 14        | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

| PRIMITIV     |           |    |    |    |    |    |    |  |  |

| 7            | 6         | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|              | PRIMITIV  |    |    |    |    |    |    |  |  |

# 37.20.22 PMECC Error Location Primitive Register

#### **PRIMITIV: Primitive Polynomial**

This field indicates the Primitive Polynomial used in the ECC computation.

# 38.7 XDMAC Maintenance Software Operations

### 38.7.1 Disabling a Channel

A disable channel request occurs when a write operation is performed in the XDMAC\_GD register. If the channel is source peripheral synchronized (bit XDMAC\_CCx.TYPE is set and bit XDMAC\_CCx.DSYNC is cleared), then pending bytes (bytes located in the FIFO) are written to memory and bit XDMAC\_CISx.DIS is set. If the channel is not source peripheral synchronized, the current channel transaction (read or write) is terminated and XDMAC\_CISx.DIS is set. XDMAC\_GS.STx is cleared by hardware when the current transfer is completed. The channel is no longer active and can be reused.

#### 38.7.2 Suspending a Channel

A read request suspend command is issued by writing to the XDMAC\_GRS register. A write request suspend command is issued by writing to the XDMAC\_GWS register. A read write suspend channel is issued by writing to the XDMAC\_GRWS register. These commands have an immediate effect on the scheduling of both read and write transactions. If a transaction is already in progress, it is terminated normally. The channel is not disabled. The FIFO content is preserved. The scheduling can resume normally, clearing the bit in the same registers. Pending bytes located in the FIFO are not written out to memory. The write suspend command does not affect read request operations, i.e., read operations can still occur until the FIFO is full.

#### 38.7.3 Flushing a Channel

A FIFO flush command is issued by writing to the XDMAC\_SWF register. The content of the FIFO is written to memory. XDMAC\_CISx.FIS (End of Flush Interrupt Status bit) is set when the last byte is successfully transferred to memory. The channel is not disabled. The flush operation is not blocking, meaning that read operation can be scheduled during the flush write operation. The flush operation is only relevant for peripheral to memory transfer where pending peripheral bytes are buffered into the channel FIFO.

#### 38.7.4 Maintenance Operation Priority

#### 38.7.4.1 Disable Operation Priority

- When a disable request occurs on a suspended channel, the XDMAC\_GWS.WSx (Channel x Write Suspend bit) is cleared. If the transfer is source peripheral synchronized, the pending bytes are drained to memory. The bit XDMAC\_CISx.DIS is set.

- When a disable request follows a flush request, if the flush last transaction is not yet scheduled, the flush request is discarded and the disable procedure is applied. Bit XDMAC\_CISx.FIS is not set. Bit XDMAC\_CISx.DIS is set when the disable request is completed. If the flush request transaction is already scheduled, the XDMAC\_CISx.FIS is set. XDMAC\_CISx.DIS is also set when the disable request is completed.

#### 38.7.4.2 Flush Operation Priority

- When a flush request occurs on a suspended channel, if there are pending bytes in the FIFO, they are written out to memory, XDMAC\_CISx.FIS is set. If the FIFO is empty, XDMAC\_CISx.FIS is also set.

- If the flush operation is performed after a disable request, the flush command is ignored. XDMAC\_CISx.FIS is not set.

#### 38.7.4.3 Suspend Operation Priority

If the suspend operation is performed after a disable request, the write suspend operation is ignored.

| LCDC | LCDDAT15 | PC21 | А |

|------|----------|------|---|

| LCDC | LCDDAT16 | PB27 | А |

| LCDC | LCDDAT17 | PB28 | А |

| LCDC | LCDDAT18 | PB29 | А |

| LCDC | LCDDAT18 | PC22 | А |

| LCDC | LCDDAT19 | PB30 | А |

| LCDC | LCDDAT19 | PC23 | А |

| LCDC | LCDDAT20 | PB31 | А |

| LCDC | LCDDAT20 | PC24 | А |

| LCDC | LCDDAT21 | PC0  | А |

| LCDC | LCDDAT21 | PC25 | А |

| LCDC | LCDDAT22 | PC1  | А |

| LCDC | LCDDAT22 | PC26 | А |

| LCDC | LCDDAT23 | PC2  | А |

| LCDC | LCDDAT23 | PC27 | А |

| LCDC | LCDDEN   | PC8  | А |

| LCDC | LCDDEN   | PD1  | А |

| LCDC | LCDDISP  | PC4  | А |

| LCDC | LCDDISP  | PC29 | А |

| LCDC | LCDHSYNC | PC6  | А |

| LCDC | LCDHSYNC | PC31 | А |

| LCDC | LCDPCK   | PC7  | А |

| LCDC | LCDPCK   | PD0  | А |

| LCDC | LCDPWM   | PC3  | А |

| LCDC | LCDPWM   | PC28 | А |

| LCDC | LCDVSYNC | PC5  | А |

| LCDC | LCDVSYNC | PC30 | А |

|      |          |      |   |

Table 39-2: I/O Lines (Continued)

#### 39.5.2 Power Management

The LCD Controller is not continuously clocked. The user must first enable the LCD Controller clock in the Power Management Controller (PMC\_PCER) before using it.

#### 39.5.3 Interrupt Sources

The LCD Controller interrupt line is connected to one of the internal sources of the interrupt controller. Using the LCD Controller interrupt requires prior programming of the interrupt controller.

Table 39-3:Peripheral IDs

| Instance | ID |

|----------|----|

| LCDC     | 45 |

| 39.7.101 | High-End Overlay Configuration Register 6 |    |      |      |    |    |    |  |  |

|----------|-------------------------------------------|----|------|------|----|----|----|--|--|

| Name:    | LCDC_HEOCFG6                              |    |      |      |    |    |    |  |  |

| Address: | 0xF00003A4                                |    |      |      |    |    |    |  |  |

| Access:  | Read/Write                                |    |      |      |    |    |    |  |  |

| 31       | 30                                        | 29 | 28   | 27   | 26 | 25 | 24 |  |  |

|          | PSTRIDE                                   |    |      |      |    |    |    |  |  |

| 23       | 22                                        | 21 | 20   | 19   | 18 | 17 | 16 |  |  |

|          |                                           |    | PSTI | RIDE |    |    |    |  |  |

| 15       | 14                                        | 13 | 12   | 11   | 10 | 9  | 8  |  |  |

|          |                                           |    | PSTI | RIDE |    |    |    |  |  |

| 7        | 6                                         | 5  | 4    | 3    | 2  | 1  | 0  |  |  |

|          | PSTRIDE                                   |    |      |      |    |    |    |  |  |

# 39.7.101 High-End Overlay Configuration Register 6

#### **PSTRIDE: Pixel Stride**

PSTRIDE represents the memory offset, in bytes, between two pixels of the image memory.

#### 40.6.3.5 DMA Bursting on the AHB

The DMA will always use SINGLE, or INCR type AHB accesses for buffer management operations. When performing data transfers, the AHB burst length used can be programmed using bits 4:0 of the DMA Configuration register so that either SINGLE, INCR or fixed length incrementing bursts (INCR4, INCR8 or INCR16) are used where possible.

When there is enough space and enough data to be transferred, the programmed fixed length bursts will be used. If there is not enough data or space available, for example when at the beginning or the end of a buffer, SINGLE type accesses are used. Also SINGLE type accesses are used at 1024 byte boundaries, so that the 1 Kbyte boundaries are not burst over as per AHB requirements.

The DMA will not terminate a fixed length burst early, unless an error condition occurs on the AHB or if receive or transmit are disabled in the Network Control register.

#### 40.6.3.6 DMA Packet Buffer

The DMA uses packet buffers for both transmit and receive paths. This mode allows multiple packets to be buffered in both transmit and receive directions. This allows the DMA to withstand far greater access latencies on the AHB and make more efficient use of the AHB bandwidth. There are two modes of operation—Full Store and Forward and Partial Store and Forward.

As described above (Section 40.6.3.2 "Partial Store and Forward Using Packet Buffer DMA"), the DMA can be programmed into a low latency mode, known as Partial Store and Forward. For further details of this mode, see Section 40.6.3.2 "Partial Store and Forward Using Packet Buffer DMA".

When the DMA is in full store and forward mode, full packets are buffered which provides the possibility to:

- Discard packets with error on the receive path before they are partially written out of the DMA, thus saving AHB bus bandwidth and driver processing overhead,

- · Retry collided transmit frames from the buffer, thus saving AHB bus bandwidth,

- Implement transmit IP/TCP/UDP checksum generation offload.

With the packet buffers included, the structure of the GMAC data paths is shown in Figure 40-2.

# SAMA5D2 SERIES

#### 40.8.109 GMAC Transmit LPI Time Name: GMAC\_TXLPITIME 0xF800827C Address: Access: Read-only 24 31 30 29 28 27 26 25 \_ \_ \_ \_ \_ ---23 22 21 20 18 16 19 17 LPITIME 15 14 13 12 10 9 8 11 LPITIME 2 0 7 6 5 4 3 1 LPITIME

### LPITIME: Time in LPI (cleared on read)

This field increments once every 16 MCK cycles when the bit Enable LPI Transmission (bit 19) is set in the Network Control register.

# 42.7.15 EHCI: REG02 - Programmable Packet Buffer Depth

| Name:   | UHPHS_INSNREG02 |    |    |        |    |    |    |

|---------|-----------------|----|----|--------|----|----|----|

| Access: | Read/Write      |    |    |        |    |    |    |

| 31      | 30              | 29 | 28 | 27     | 26 | 25 | 24 |

|         |                 |    | -  | -      |    |    |    |

| 23      | 22              | 21 | 20 | 19     | 18 | 17 | 16 |

|         |                 |    | -  | -      |    |    |    |

| 15      | 14              | 13 | 12 | 11     | 10 | 9  | 8  |

|         | _               |    |    | Dwords |    |    |    |

| 7       | 6               | 5  | 4  | 3      | 2  | 1  | 0  |

|         | Dwords          |    |    |        |    |    |    |

Programmable Packet Buffer Depth (in CONFIG1 mode only, not applicable in Config2 mode).

The value specified here is the number of DWORDs (32-bit entries).

#### **Dwords: Number of Entries**

For a maximum 256 entries for 1-Kbyte packet buffer, bits [8:0] are sufficient.

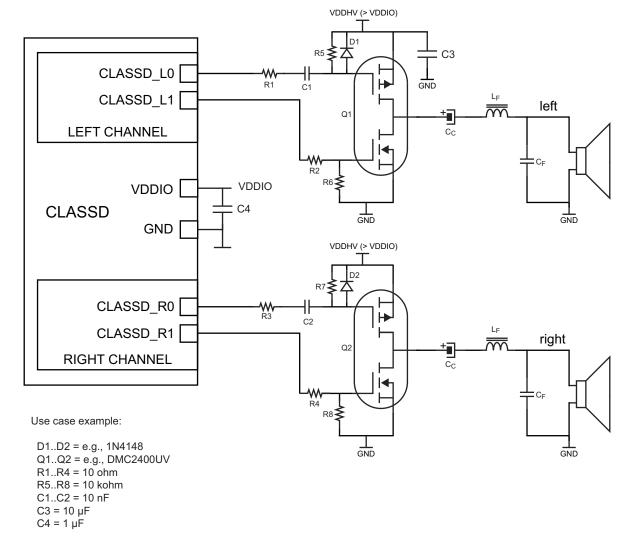

#### Figure 43-15: Use Case 2: Stereo Class D Amplifier With External Single-ended Power Stage

In the Use Case 2 application schematic, the drive network of the MOSFETs gates follows the principles described in Use Case 1.

### FSEDGE: Frame Sync Edge Detection

Determines which edge on Frame Sync will generate the interrupt RXSYN in the SSC Status Register.

| Value | Name     | Description             |

|-------|----------|-------------------------|

| 0     | POSITIVE | Positive Edge Detection |

| 1     | NEGATIVE | Negative Edge Detection |

#### FSLEN\_EXT: FSLEN Field Extension

Extends FSLEN field. For details, refer to "FSLEN: Receive Frame Sync Length".

| 45.9.11<br>Name:<br>Address:<br>Access: | SSC Receive Compare 0 Register<br>SSC_RC0R<br>0xF8004038 (0), 0xFC004038 (1)<br>Read/Write |    |    |         |    |    |    |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------|----|----|---------|----|----|----|--|

| Access.<br>31                           | Seau/Wille 30                                                                              | 29 | 28 | 27      | 26 | 25 | 24 |  |

| -                                       | -                                                                                          | -  | -  | -       | -  | _  | _  |  |

| 23                                      | 22                                                                                         | 21 | 20 | 19      | 18 | 17 | 16 |  |

| -                                       | -                                                                                          | -  | -  | -       | —  | —  | -  |  |

| 15                                      | 14                                                                                         | 13 | 12 | 11      | 10 | 9  | 8  |  |

|                                         | CP0                                                                                        |    |    |         |    |    |    |  |

| 7                                       | 6                                                                                          | 5  | 4  | 3<br>P0 | 2  | 1  | 0  |  |

|                                         |                                                                                            |    | 0  |         |    |    |    |  |

This register can only be written if the WPEN bit is cleared in the SSC Write Protection Mode Register.

CP0: Receive Compare Data 0

24

16

8

0

# 46.7.17 TWIHS SleepWalking Matching Register

| Name:<br>Address:<br>Access: | TWIHS_SWMR<br>0xF802804C (0), 0xFC02804C (1)<br>Read/Write |       |    |       |    |    |  |

|------------------------------|------------------------------------------------------------|-------|----|-------|----|----|--|

| 31                           | 30                                                         | 29    | 28 | 27    | 26 | 25 |  |

|                              |                                                            | DATAM |    |       |    |    |  |

| 23                           | 22                                                         | 21    | 20 | 19    | 18 | 17 |  |

| _                            |                                                            |       |    | SADR3 |    |    |  |

| 15                           | 14                                                         | 13    | 12 | 11    | 10 | 9  |  |

| _                            |                                                            |       |    | SADR2 |    |    |  |

| 7                            | 6                                                          | 5     | 4  | 3     | 2  | 1  |  |

| -                            |                                                            |       |    | SADR1 |    |    |  |

This register can only be written if the WPEN bit is cleared in the TWIHS Write Protection Mode Register.

#### SADR1: Slave Address 1

Slave address 1. The TWIHS module matches on this additional address if SADR1EN bit is enabled.

#### SADR2: Slave Address 2

Slave address 2. The TWIHS module matches on this additional address if SADR2EN bit is enabled.

#### SADR3: Slave Address 3

Slave address 3. The TWIHS module matches on this additional address if SADR3EN bit is enabled.

#### **DATAM: Data Match**

The TWIHS module extends the SleepWalking matching process to the first received data, comparing it with DATAM if DATAMEN bit is enabled.

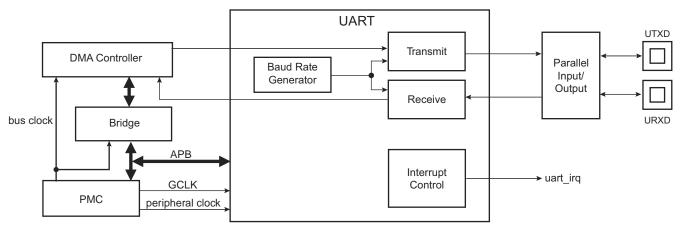

# 48. Universal Asynchronous Receiver Transmitter (UART)

# 48.1 Description

The Universal Asynchronous Receiver Transmitter (UART) features a two-pin UART that can be used for communication and trace purposes and offers an ideal medium for in-situ programming solutions.

Moreover, the association with a DMA controller permits packet handling for these tasks with processor time reduced to a minimum.

# 48.2 Embedded Characteristics

- Two-pin UART

- Independent Receiver and Transmitter with a Common Programmable Baud Rate Generator

- Baud Rate can be Driven by Processor-Independent Generic Source Clock

- Even, Odd, Mark or Space Parity Generation

- Parity, Framing and Overrun Error Detection

- Automatic Echo, Local Loopback and Remote Loopback Channel Modes

- Digital Filter on Receive Line

- Interrupt Generation

- Support for Two DMA Channels with Connection to Receiver and Transmitter

- Supports Asynchronous Partial Wakeup on Receive Line Activity (SleepWalking)

- Comparison Function on Received Character

- Receiver Timeout

- Register Write Protection

### 48.3 Block Diagram

#### Figure 48-1: UART Block Diagram

#### Table 48-1:UART Pin Description

| Pin Name | Description        | Туре   |

|----------|--------------------|--------|

| URXD     | UART Receive Data  | Input  |

| UTXD     | UART Transmit Data | Output |

| 51.13.57 | SDMMC | Capabilities | Control | Register |

|----------|-------|--------------|---------|----------|

|----------|-------|--------------|---------|----------|

|     | IMC_CACR<br>d/Write |    |    |    |    |    |         |  |

|-----|---------------------|----|----|----|----|----|---------|--|

| 31  | 30                  | 29 | 28 | 27 | 26 | 25 | 24      |  |

| _   | _                   | _  | _  | _  | _  | _  | —       |  |

| 23  | 22                  | 21 | 20 | 19 | 18 | 17 | 16      |  |

| _   | -                   | -  | -  | _  | -  | _  | -       |  |

| 15  | 14                  | 13 | 12 | 11 | 10 | 9  | 8       |  |

| KEY |                     |    |    |    |    |    |         |  |

| 7   | 6                   | 5  | 4  | 3  | 2  | 1  | 0       |  |

| _   | -                   | _  | -  | -  | _  | _  | CAPWREN |  |

#### **CAPWREN: Capabilities Write Enable**

This bit can only be written if KEY correspond to 46h.

0: Capabilities registers (SDMMC\_CA0R and SDMMC\_CA1R) cannot be written.

1: Capabilities registers (SDMMC\_CA0R and SDMMC\_CA1R) can be written.

#### **KEY: Key**

| Value | Name | Description                                                                                                |

|-------|------|------------------------------------------------------------------------------------------------------------|

| 46h   | KEY  | Writing any other value in this field aborts the write operation of the CAPWREN bit.<br>Always reads as 0. |

# 52.6.44 ISC Contrast And Brightness, Contrast Register

| Address: 0xF0 | _CBC_CONTRAS<br>00083C0<br>d/Write | Т  |    |          |    |    |    |  |

|---------------|------------------------------------|----|----|----------|----|----|----|--|

| 31            | 30                                 | 29 | 28 | 27       | 26 | 25 | 24 |  |

| -             | —                                  | -  | -  | -        | _  | -  | -  |  |

| 23            | 22                                 | 21 | 20 | 19       | 18 | 17 | 16 |  |

| -             | -                                  | _  | -  | _        | _  | _  | -  |  |

| 15            | 14                                 | 13 | 12 | 11       | 10 | 9  | 8  |  |

| _             | _                                  | _  | -  | CONTRAST |    |    |    |  |

| 7             | 6                                  | 5  | 4  | 3        | 2  | 1  | 0  |  |

|               | CONTRAST                           |    |    |          |    |    |    |  |

CONTRAST: Contrast (unsigned 12 bits 1:3:8)

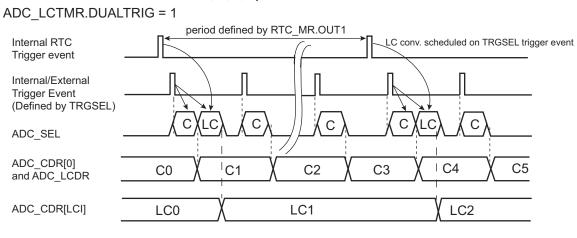

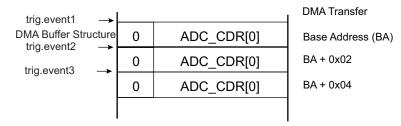

# Figure 65-9: Independent Trigger Measurement for Last Channel (ADC\_CHSR[LCI] = 0 and ADC\_TRGR.TRGMOD = 1, 2, 3, 5)

Notes: ADC\_SEL: Command to the ADC analog cell Cx: All ADC channel values except the last channel (highest index) LCx: Last channel value

LCI: Last channel index

Assuming ADC\_CHSR[0] = 1

If DUALTRIG = 1 and field ADC\_TRGR.TRGMOD = 0 and none of the channels are enabled in ADC\_CHSR (ADC\_CHSR = 0), then only channel 11 is converted at a rate defined by the trigger event signal that can be configured in RTC\_MR.OUT1 (see Figure 65-10).

This mode of operation, when combined with the Sleep mode operation of the ADC Controller, provides a low-power mode for last channel measure. This assumes there is no other ADC conversion to schedule at a high sampling rate or no other channel to convert.

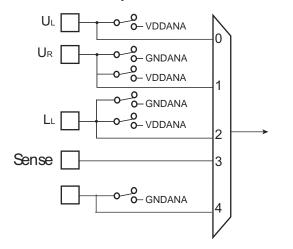

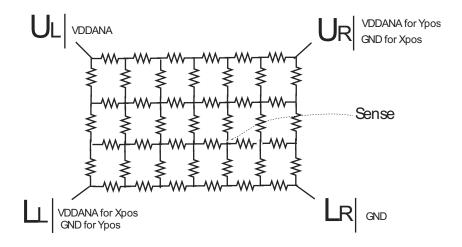

#### 65.6.15.6 5-wire Position Measurement Method

In an application only monitoring clicks, 100 points per second is typically needed. For handwriting or motion detection, the number of measurements to consider is approximately 200 points per second. This must take into account that multiple measurements are included (over sampling, filtering) to compute the correct point.

The 5-wire touchscreen panel works by applying a voltage at the corners of the resistive layer and measuring the vertical or horizontal resistive network with the sense input. The ADC converts the voltage measured at the point the panel is touched.

A measurement of the Y position of the pointing device is made by:

- Connecting Upper left (UL) and upper right (UR) corners to VDDANA

- · Connecting Lower left (LL) and lower right (LR) corners to ground.

The voltage measured is determined by the voltage divider developed at the point of touch (Y position) and the SENSE input is converted by ADC.

A measurement of the X position of the pointing device is made by:

- · Connecting the upper left (UL) and lower left (LL) corners to ground

- Connecting the upper right and lower right corners to VDDANA.

The voltage measured is determined by the voltage divider developed at the point of touch (X position) and the SENSE input is converted by ADC.

#### Figure 65-18: Touchscreen Switches Implementation

#### 66.5.6 Low-power Consumption Versus Modes

The low-power consumption values are measured under the following operating conditions:

- Parts are from typical process

- V<sub>DDIOPx</sub> = 3.3V

- V<sub>DDSDMMC0</sub> and V<sub>DDSDMMC1</sub> = 1.8V to 3.3V (high frequency)

- V<sub>DDCORE</sub> = 1.2V +/-2%

- V<sub>DDBU</sub> = 1.6V to 3.6V

- T<sub>A</sub> = as specified in Table 66-12, Table 66-13, Table 66-14

- There is no consumption on the device's I/Os.

- All peripheral clocks are disabled.

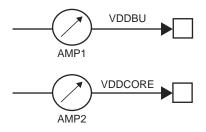

#### Figure 66-2: Measurement Schematics

In order to maximize performances, each Peripheral Clock has been timed to H32MX clock frequency. The peripheral frequency can be reduced with the help of a divider in PMC\_PCR.

#### Table 66-12: Typical Power Consumption in Idle Mode: AMP2

| Conditions                                                                                                                                                                                                                                                                                                                                                            |                     | Consumption         |                     |                      |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|----------------------|------|

| Conditions                                                                                                                                                                                                                                                                                                                                                            | Τ <sub>A</sub> 25°C | T <sub>A</sub> 70°C | T <sub>A</sub> 85°C | T <sub>A</sub> 105°C | Unit |

| <ul> <li>PLL clock is 1000 MHz, ARM Core clock is 500 MHz, MCK is 166 MHz.</li> <li>– Core clock is stopped</li> <li>– Peripheral clocks, including the DDR Controller clock, can be enabled</li> <li>– Mode is entered via Wait for Interrupt (WFI) instruction and PCK disabling</li> <li>– Measure IDDCORE + IDDBU</li> <li>– Peripheral clock disabled</li> </ul> | 28.2                | 29.6                | 30.8                | 33.4                 | mA   |

#### Table 66-13: VDDCORE Power Consumption in Ultra Low-power Mode: AMP2

| Mode             | Conditions                                    |                     | Consumption (mA)                                                                 |     |     | Wakeup |

|------------------|-----------------------------------------------|---------------------|----------------------------------------------------------------------------------|-----|-----|--------|

|                  | Conditions                                    | T <sub>A</sub> 25°C | T <sub>A</sub> 25°C T <sub>A</sub> 70°C T <sub>A</sub> 85°C T <sub>A</sub> 105°C |     |     |        |

| ULP1 Fast Wakeup | ARM Core clock is disabled. MCK is 0.         | 0.3                 | 1.4                                                                              | 2.4 | 4.6 | 15     |

| ULP0 12 MHz      | ARM Core clock is disabled. MCK is 12 MHz.    | 3.2                 | 4.2                                                                              | 5.3 | 7.7 | 13     |

| ULP0 750 kHz     | ARM Core clock is disabled. MCK is 750 kHz.   | 1.6                 | 2.6                                                                              | 3.7 | 6.1 | 205    |

| ULP0 187 kHz     | ARM Core clock is disabled. MCK is 187.5 kHz. | 1.5                 | 2.5                                                                              | 3.6 | 6.0 | 820    |

| ULP0 32 kHz      | ARM Core clock is disabled. MCK is 32 kHz.    | 0.3                 | 1.5                                                                              | 2.6 | 5.0 | 4690   |