#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

EXF

| Product Status                     | Obsolete                                                                                          |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A5                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 500MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ MPE                                                                             |

| RAM Controllers                    | LPDDR1, LPDDR2, LPDDR3, DDR2, DDR3, DDR3L, QSPI                                                   |

| Graphics Acceleration              | Yes                                                                                               |

| Display & Interface<br>Controllers | Keyboard, LCD, Touchscreen                                                                        |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 + HSIC                                                                                    |

| Voltage - I/O                      | 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 105°C (TA)                                                                                |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 196-TFBGA, CSBGA                                                                                  |

| Supplier Device Package            | 196-TFBGA (11x11)                                                                                 |

| Purchase URL                       | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d23b-cn                          |

|                                    |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

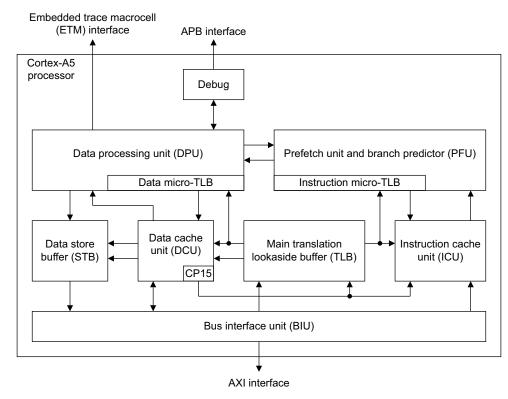

### 13.2 Embedded Characteristics

- In-order pipeline with dynamic branch prediction

- ARM, Thumb, and ThumbEE instruction set support

- TrustZone security extensions

- Harvard level 1 memory system with a Memory Management Unit (MMU)

- 32 Kbytes Data Cache

- 32 Kbytes Instruction Cache

- 64-bit AXI master interface

- ARM v7 debug architecture

- Trace support through an Embedded Trace Macrocell (ETM) interface

- Media Processing Engine (MPE) with NEON technology

- Jazelle hardware acceleration

# 13.3 Block Diagram

#### Figure 13-1: Cortex-A5 Processor Top-level Diagram

# 26.6.15 RTC Valid Entry Register

| Name: | RTC_VER |

|-------|---------|

|       |         |

Address: 0xF80480DC

#### Access: Read-only

| 31 | 30 | 29 | 28 | 27       | 26       | 25    | 24    |

|----|----|----|----|----------|----------|-------|-------|

| _  | _  | _  | _  | _        | _        | _     | _     |

| 23 | 22 | 21 | 20 | 19       | 18       | 17    | 16    |

| _  | _  | -  | -  | —        | -        | -     | -     |

| 15 | 14 | 13 | 12 | 11       | 10       | 9     | 8     |

| -  | _  | -  | -  | -        | -        | _     | -     |

| 7  | 6  | 5  | 4  | 3        | 2        | 1     | 0     |

| _  | _  | _  | -  | NVCALALR | NVTIMALR | NVCAL | NVTIM |

If the RTC is configured in UTC mode, the values returned by this register are not relevant.

#### NVTIM: Non-valid Time

0: No invalid data has been detected in RTC\_TIMR (Time Register).

1: RTC\_TIMR has contained invalid data since it was last programmed.

#### NVCAL: Non-valid Calendar

0: No invalid data has been detected in RTC\_CALR (Calendar Register).

1: RTC\_CALR has contained invalid data since it was last programmed.

#### NVTIMALR: Non-valid Time Alarm

0: No invalid data has been detected in RTC\_TIMALR (Time Alarm Register).

1: RTC\_TIMALR has contained invalid data since it was last programmed.

#### NVCALALR: Non-valid Calendar Alarm

0: No invalid data has been detected in RTC\_CALALR (Calendar Alarm Register).

1: RTC\_CALALR has contained invalid data since it was last programmed.

# 33.22.11 PMC Master Clock Register

| Name: P    | MC_MCKR    |              |    |    |    |      |          |

|------------|------------|--------------|----|----|----|------|----------|

| Address: 0 | xF0014030  |              |    |    |    |      |          |

| Access: R  | Read/Write |              |    |    |    |      |          |

| 31         | 30         | 29           | 28 | 27 | 26 | 25   | 24       |

| _          | -          | —            | —  | —  | —  | —    | H32MXDIV |

| 23         | 22         | 21           | 20 | 19 | 18 | 17   | 16       |

| _          | -          | —            | —  | —  | —  | _    | -        |

| 15         | 14         | 13           | 12 | 11 | 10 | 9    | 8        |

| —          | -          | – – PLLADIV2 |    | -  | -  | MDIV |          |

| 7          | 6          | 5            | 4  | 3  | 2  | 1    | 0        |

| _          |            | PRES         |    | _  | _  | C    | SS       |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

#### CSS: Master/Processor Clock Source Selection

| Value | Name     | Description            |

|-------|----------|------------------------|

| 0     | SLOW_CLK | Slow clock is selected |

| 1     | MAIN_CLK | Main clock is selected |

| 2     | PLLA_CLK | PLLACK is selected     |

| 3     | UPLL_CLK | UPLL Clock is selected |

#### PRES: Master/Processor Clock Prescaler

| Value | Name        | Description                  |

|-------|-------------|------------------------------|

| 0     | CLOCK       | Selected clock               |

| 1     | CLOCK_DIV2  | Selected clock divided by 2  |

| 2     | CLOCK_DIV4  | Selected clock divided by 4  |

| 3     | CLOCK_DIV8  | Selected clock divided by 8  |

| 4     | CLOCK_DIV16 | Selected clock divided by 16 |

| 5     | CLOCK_DIV32 | Selected clock divided by 32 |

| 6     | CLOCK_DIV64 | Selected clock divided by 64 |

| 7     | -           | Reserved                     |

### **MDIV: Master Clock Division**

| Value | Name     | Description                                                                 |

|-------|----------|-----------------------------------------------------------------------------|

| 0     | EQ PCK   | Master Clock is Prescaler Output Clock divided by 1.                        |

| 0     |          | Warning: DDRCK is not available.                                            |

| 1     | PCK_DIV2 | Master Clock is Prescaler Output Clock divided by 2. DDRCK is equal to MCK. |

| 2     | PCK_DIV4 | Master Clock is Prescaler Output Clock divided by 4. DDRCK is equal to MCK. |

| 3     | PCK_DIV3 | Master Clock is Prescaler Output Clock divided by 3. DDRCK is equal to MCK. |

| 31 | 30   | 29 | 28 | 27 | 26 | 25   | 24 |  |

|----|------|----|----|----|----|------|----|--|

| _  | _    | —  | _  | —  | _  | —    | -  |  |

| 23 | 22   | 21 | 20 | 19 | 18 | 17   | 16 |  |

| _  | -    | -  | -  | -  | -  | RZQI |    |  |

| 15 | 14   | 13 | 12 | 11 | 10 | 9    | 8  |  |

| _  | _    | _  | _  | _  | -  | _    | -  |  |

| 7  | 6    | 5  | 4  | 3  | 2  | 1    | 0  |  |

|    | ZQCS |    |    |    |    |      |    |  |

### Access: Read/Write

#### **ZQCS: ZQ Calibration Short**

Reset value is 6 DDRCK<sup>(1)</sup> clock cycles.

This field defines the delay between the ZQ Calibration command and any valid command in number of DDRCK<sup>(1)</sup> clock cycles.

The number of cycles is between 0 and 255. This field applies to LPDDR2, LPDDR3 and DDR3 devices.

#### RZQI: Built-in Self-Test for RZQ Information (read-only)

Reset value is 0.

This field indicates whether the device has detected a resistor connection to the ZQ pin.

This mode is unique to low-power DDR3-SDRAM devices.

| Value | Name              | Description                                              |  |  |  |

|-------|-------------------|----------------------------------------------------------|--|--|--|

| 0     | RZQ_NOT_SUPPORTED | RZQ self test not supported                              |  |  |  |

| 1     | ZQ_VDDCA_FLOAT    | T The ZQ pin can be connected to VDDCA or left floating. |  |  |  |

| 2     | ZQ_SHORTED_GROUND | The ZQ pin can be shorted to ground.                     |  |  |  |

| 3     | ZQ_SELF_TEST_OK   | ZQ pin self test complete; no error condition detected   |  |  |  |

Note 1: DDRCK is the clock that drives the SDRAM device.

1: Number of requests or words is provided by software, see "NRQ\_NWD\_BDW\_Px: Number of Requests, Number of Words or Bandwidth Allocation from Port 0-1-2-3".

DMA Controller 1 manages transfers between peripherals and memory, and receives the triggers from the peripherals listed in Table 38-3.

| Instance Name | Channel T/R | Interface Number | XDMAC_CCx.CSIZE Required Value   |  |

|---------------|-------------|------------------|----------------------------------|--|

| TWIHS0        | Transmit    | 0                | 2                                |  |

| TWIHS0        | Receive     | 1                | 0                                |  |

| TWIHS1        | Transmit    | 2                | 2                                |  |

| TWIHS1        | Receive     | 3                | 0                                |  |

| QSPI0         | Transmit    | 4                | 2                                |  |

| QSPI0         | Receive     | 5                | 0                                |  |

| SPI0          | Transmit    | 6                | 0                                |  |

| SPI0          | Receive     | 7                | 0                                |  |

| SPI1          | Transmit    | 8                |                                  |  |

| SPI1          | Receive     | 9                | 0                                |  |

| PWM           | Transmit    | 10               | 0                                |  |

| FLEXCOM0      | Transmit    | 11               | 2                                |  |

| FLEXCOM0      | Receive     | 12               | 0                                |  |

| FLEXCOM1      | Transmit    | 13               | 0                                |  |

| FLEXCOM1      | Receive     | 14               | 0                                |  |

| FLEXCOM2      | Transmit    | 15               |                                  |  |

| FLEXCOM2      | Receive     | 16               | 0                                |  |

| FLEXCOM3      | Transmit    | 17               |                                  |  |

| FLEXCOM3      | Receive     | 18               | 0                                |  |

| FLEXCOM4      | Transmit    | 19               |                                  |  |

| FLEXCOM4      | Receive     | 20               | 0                                |  |

| SSC0          | Transmit    | 21               | 0                                |  |

| SSC0          | Receive     | 22               | 0                                |  |

| SSC1          | Transmit    | 23               | 0                                |  |

| SSC1          | Receive     | 24               | 0                                |  |

| ADC           | Receive     | 25               | 0                                |  |

| AES           | Transmit    | 26               | 0 or 2 (see AES Section 60.4.4.3 |  |

| AES           | Receive     | 27               | "DMA Mode")                      |  |

| TDES          | Transmit    | 28               |                                  |  |

| TDES          | Receive     | 29               | - 0                              |  |

| SHA           | Transmit    | 30               | 4                                |  |

| I2SC0         | Transmit    | 31               | 0                                |  |

| I2SC0         | Receive     | 32               | 0                                |  |

| I2SC1         | Transmit    | 33               |                                  |  |

| I2SC1         | Receive     | 34               | 0                                |  |

Table 38-3:

DMA Channels Definition (XDMAC1)

| 39.7.120 | High-End Overlay | high-End Overlay Configuration Register 25 |        |        |    |    |    |  |  |  |

|----------|------------------|--------------------------------------------|--------|--------|----|----|----|--|--|--|

| Name:    | LCDC_HEOCFG25    |                                            |        |        |    |    |    |  |  |  |

| Address: | 0xF00003F0       |                                            |        |        |    |    |    |  |  |  |

| Access:  | Read/Write       |                                            |        |        |    |    |    |  |  |  |

| 31       | 30               | 29                                         | 28     | 27     | 26 | 25 | 24 |  |  |  |

|          |                  |                                            | XPHI4C | OEFF3  |    |    |    |  |  |  |

| 23       | 22               | 21                                         | 20     | 19     | 18 | 17 | 16 |  |  |  |

|          |                  |                                            | XPHI4C | OEFF2  |    |    |    |  |  |  |

| 15       | 14               | 13                                         | 12     | 11     | 10 | 9  | 8  |  |  |  |

|          | XPHI4COEFF1      |                                            |        |        |    |    |    |  |  |  |

| 7        | 6                | 5                                          | 4      | 3      | 2  | 1  | 0  |  |  |  |

|          |                  |                                            | XPHI4C | COEFF0 |    |    |    |  |  |  |

# 7 400 Ulink End Overlay Configuration Deviator 25

#### XPHI4COEFF0: Horizontal Coefficient for phase 4 tap 0

Coefficient format is 1 sign bit and 7 fractional bits.

#### XPHI4COEFF1: Horizontal Coefficient for phase 4 tap 1

Coefficient format is 1 sign bit and 7 fractional bits.

# XPHI4COEFF2: Horizontal Coefficient for phase 4 tap 2

Coefficient format is 1 magnitude bit and 7 fractional bits.

#### XPHI4COEFF3: Horizontal Coefficient for phase 4 tap 3

Coefficient format is 1 sign bit and 7 fractional bits.

- A priority enable vector taken from Transmit PFC Pause register

- 8 Pause Quantum registers

- Fill of 00 to take the frame to minimum frame length

- Valid FCS

The Pause Quantum registers used in the generated frame will depend on the trigger source for the frame as follows:

- If bit 17 of the Network Control register is written with a one, then the priority enable vector of the priority-based pause frame will be set equal to the value stored in the Transmit PFC Pause register [7:0]. For each entry equal to zero in the Transmit PFC Pause register [15:8], the pause quantum field of the pause frame associated with that entry will be taken from the Transmit Pause Quantum register. For each entry equal to one in the Transmit PFC Pause register [15:8], the pause quantum associated with that entry will be zero.

- The Transmit Pause Quantum register resets to a value of 0xFFFF giving maximum pause quantum as default.

After transmission, a pause frame transmitted interrupt will be generated (bit 14 of the Interrupt Status register) and the only statistics register that will be incremented will be the Pause Frames Transmitted register.

PFC Pause frames can also be transmitted by the MAC using normal frame transmission methods.

### 40.8.35 GMAC IPG Stretch Register

| Address: 0xF | IAC_IPGS<br>80080BC<br>ad/Write | -  |    |    |    |    |    |

|--------------|---------------------------------|----|----|----|----|----|----|

| 31           | 30                              | 29 | 28 | 27 | 26 | 25 | 24 |

| _            | -                               | -  | -  | -  | -  | _  | -  |

| 23           | 22                              | 21 | 20 | 19 | 18 | 17 | 16 |

| -            | -                               | _  | _  | _  | _  | -  | -  |

| 15           | 14                              | 13 | 12 | 11 | 10 | 9  | 8  |

|              |                                 |    | F  | Ľ  |    |    |    |

| 7            | 6                               | 5  | 4  | 3  | 2  | 1  | 0  |

|              |                                 |    | F  | L  |    |    |    |

#### FL: Frame Length

Bits 7:0 are multiplied with the previously transmitted frame length (including preamble). Bits 15:8 +1 divide the frame length. If the resulting number is greater than 96 and bit 28 is set in the Network Configuration Register than the resulting number is used for the transmit inter-packet-gap. 1 is added to bits 15:8 to prevent a divide by zero. See Section 40.6.4 "MAC Transmit Block".

| 40.0.00  | SMAC OCIEIS Received high Register |    |    |    |    |    |    |  |  |  |  |

|----------|------------------------------------|----|----|----|----|----|----|--|--|--|--|

| Name:    | GMAC_ORHI                          |    |    |    |    |    |    |  |  |  |  |

| Address: | 0xF8008154                         |    |    |    |    |    |    |  |  |  |  |

| Access:  | Read-only                          |    |    |    |    |    |    |  |  |  |  |

| 31       | 30                                 | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |  |

| _        | -                                  | _  | _  | _  | —  | _  | —  |  |  |  |  |

| 23       | 22                                 | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |  |

| _        | -                                  | —  | —  | —  | -  | —  | —  |  |  |  |  |

| 15       | 14                                 | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |  |

|          | RXO                                |    |    |    |    |    |    |  |  |  |  |

| 7        | 6                                  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |  |

|          | RXO                                |    |    |    |    |    |    |  |  |  |  |

# 40.8.68 GMAC Octets Received High Register

When reading the Octets Transmitted and Octets Received Registers, bits 31:0 should be read prior to bits 47:32 to ensure reliable operation.

#### **RXO: Received Octets**

Received octets in frame without errors [47:32]. The number of octets received in valid frames of any type. This counter is 48-bits and is read through two registers. This count does not include octets from pause frames, and is only incremented if the frame is successfully filtered and copied to memory.

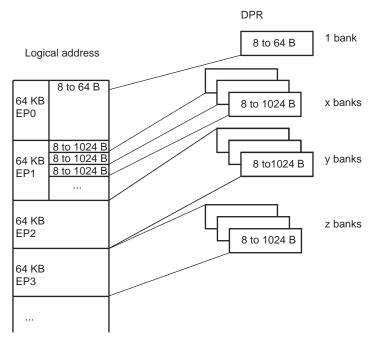

#### Figure 41-5: Logical Address Space for DPR Access

Configuration examples of UDPHS\_EPTCTLx (UDPHS Endpoint Control Disable Register (Isochronous Endpoint)) for Bulk IN endpoint type follow below.

- With DMA

- AUTO\_VALID: Automatically validate the packet and switch to the next bank.

- EPT\_ENABL: Enable endpoint.

- Without DMA:

- TXRDY: An interrupt is generated after each transmission.

- EPT\_ENABL: Enable endpoint.

Configuration examples of Bulk OUT endpoint type follow below.

- With DMA

- AUTO\_VALID: Automatically validate the packet and switch to the next bank.

- EPT\_ENABL: Enable endpoint.

- Without DMA

- RXRDY\_TXKL: An interrupt is sent after a new packet has been stored in the endpoint FIFO.

- EPT\_ENABL: Enable endpoint.

#### 41.6.7 DPRAM Management

Endpoints can only be allocated in ascending order, from the endpoint 0 to the last endpoint to be allocated. The user shall therefore configure them in the same order.

The allocation of an endpoint x starts when the Number of Banks field in the UDPHS Endpoint Configuration Register (UDPHS\_EPTCFGx.BK\_NUMBER) is different from zero. Then, the hardware allocates a memory area in the DPRAM and inserts it between the x-1 and x+1 endpoints. The x+1 endpoint memory window slides up and its data is lost. Note that the following endpoint memory windows (from x+2) do not slide.

Disabling an endpoint, by writing a one to the Endpoint Disable bit in the UDPHS Endpoint Control Disable Register (UDPHS\_EPTCTLDISx.EPT\_DISABL), does not reset its configuration:

- Endpoint Banks (UDPHS\_EPTCFGx.BK\_NUMBER)

- Endpoint Size (UDPHS\_EPTCFGx.EPT\_SIZE)

- Endpoint Direction (UDPHS\_EPTCFGx.EPT\_DIR)

- Endpoint Type (UDPHS\_EPTCFGx.EPT\_TYPE)

To free its memory, the user shall write a zero to the UDPHS\_EPTCFGx.BK\_NUMBER field. The x+1 endpoint memory window then slides down and its data is lost. Note that the following endpoint memory windows (from x+2) do not slide.

| Value | Name | Description                                     |

|-------|------|-------------------------------------------------|

| 0     | 0    | Zero bank, the endpoint is not mapped in memory |

| 1     | 1    | One bank (bank 0)                               |

| 2     | 2    | Double bank (Ping-Pong: bank0/bank1)            |

| 3     | 3    | Triple bank (bank0/bank1/bank2)                 |

Set this field according to the endpoint's number of banks (refer to Section 41.6.6 "Endpoint Configuration").

#### NB\_TRANS: Number Of Transaction per Microframe (cleared upon USB reset)

The Number of transactions per microframe is set by software.

**Note:** Meaningful for high bandwidth isochronous endpoint only.

#### EPT\_MAPD: Endpoint Mapped (cleared upon USB reset)

- 0: The user should reprogram the register with correct values.

- 1: Set by hardware when the endpoint size (EPT\_SIZE) and the number of banks (BK\_NUMBER) are correct regarding:

- The FIFO max capacity (FIFO\_MAX\_SIZE in UDPHS\_IPFEATURES register)

- The number of endpoints/banks already allocated

- The number of allowed banks for this endpoint

Port Enabled Bit and Suspend bit of this register define the port states as follows:

| Bits [Port Enabled, Suspend] | Port State |

|------------------------------|------------|

| 0X                           | Disable    |

| 10                           | Enable     |

| 11                           | Suspend    |

When in suspend state, downstream propagation of data is blocked on this port, except for port reset. The blocking occurs at the end of the current transaction, if a transaction was in progress when this bit was written to 1. In the suspend state, the port is sensitive to resume detection. Note that the bit status does not change until the port is suspended and that there may be a delay in suspending a port if there is a transaction currently in progress on the USB.

A write of 0 to this bit is ignored by the host controller. The host controller will unconditionally set this bit to 0 when:

- Software sets the Force Port Resume bit to 0 (from 1).

- Software sets the Port Reset bit to 1 (from 0).

If host software sets this bit to 1 when the port is not enabled (i.e., Port Enabled bit set to 0), the results are undefined.

This field is 0 if Port Power is set to 0.

#### PR: Port Reset (read/write)

0: Port is not in Reset (default value).

1: Port is in Reset.

When software writes a 1 to this bit (from 0), the bus reset sequence as defined in the USB Specification Revision 2.0 is started. Software writes a 0 to this bit to terminate the bus reset sequence. Software must keep this bit set to 1 long enough to ensure the reset sequence, as specified in the USB Specification Revision 2.0, completes. Note: when software writes this bit to 1, it must also write 0 to the Port Enable bit.

When software writes a 0 to this bit, there may be a delay before the bit status changes to 0. The bit status will not read as 0 until after the reset has completed. If the port is in High-Speed mode after reset is complete, the host controller will automatically enable this port (e.g. set the Port Enable bit to 1). A host controller must terminate the reset and stabilize the state of the port within 2 milliseconds of software transitioning this bit from 1 to 0. For example: if the port detects that the attached device is high-speed during reset, then the host controller must have the port in the enabled state within 2 ms of software writing this bit to 0.

The HCHalted bit in the UHPHS\_USBSTS register should be set to 0 before software attempts to use this bit. The host controller may hold Port Reset asserted to 1 when the HCHalted bit is 1.

This field is 0 if Port Power is 0.

#### LS: Line Status (read-only)

These bits reflect the current logical levels of the D+ (bit 11) and D- (bit 10) signal lines. These bits are used for detection of low-speed USB devices prior to the port reset and enable sequence. This field is valid only when the port enable bit is 0 and the current connect status bit is set to 1.

Bits are encoded as follows:

| Value | USB State | Interpretation                              |

|-------|-----------|---------------------------------------------|

| 00b   | SE0       | Not a low-speed device, perform EHCI reset  |

| 10b   | J-state   | Not a low-speed device, perform EHCI reset  |

| 01b   | K-state   | Low-speed device, release ownership of port |

| 11b   | Undefined | Not a low-speed device, perform EHCI reset  |

This value of this field is undefined if Port Power is 0.

#### PP: Port Power (read/write or read-only)

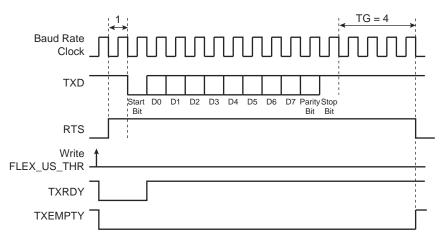

### Figure 47-37: Example of RTS Drive with Timeguard

### 47.7.7 USART Comparison Function on Received Character

The CMP flag in FLEX\_US\_CSR is set when the received character matches the conditions programmed in FLEX\_US\_CMPR. The CMP flag is set as soon as FLEX\_US\_RHR is loaded with the new received character. The CMP flag is cleared by writing a one to FLEX\_US\_CR.RSTSTA.

FLEX\_US\_CMPR (see Section 47.10.34 "USART Comparison Register") can be programmed to provide different comparison methods:

- If VAL1 equals VAL2, then the comparison is performed on a single value and the flag is set to 1 if the received character equals VAL1.

- If VAL1 is strictly lower than VAL2, then any value between VAL1 and VAL2 sets the CMP flag.

- If VAL1 is strictly higher than VAL2, then the flag CMP is set to 1 if any received character equals VAL1 or VAL2.

When the FLEX\_US\_CMPR.CMPMODE bit is set to FLAG\_ONLY (value 0), all received data are loaded in FLEX\_US\_RHR and the CMP flag provides the status of the comparison result.

By programming the START\_CONDITION.CMPMODE bit (value 1), the comparison function result triggers the start of the loading of FLEX\_US\_RHR (see Figure 47-38). The trigger condition exists as soon as the received character value matches the condition defined by the programming of VAL1, VAL2 and CMPPAR in FLEX\_US\_CMPR. The comparison trigger event is restarted by writing a 1 to the FLEX\_US\_CR.REQCLR bit.

The value programmed in the VAL1 and VAL2 fields must not exceed the maximum value of the received character (see CHRL field in USART Mode Register (FLEX\_US\_MR)).

### 47.10.37 USART FIFO Interrupt Enable Register

Name: FLEX\_US\_FIER

Address: 0xF80342A8 (0), 0xF80382A8 (1), 0xFC0102A8 (2), 0xFC0142A8 (3), 0xFC0182A8 (4)

Access: Write-only

| 31      | 30      | 29     | 28    | 27    | 26     | 25      | 24    |

|---------|---------|--------|-------|-------|--------|---------|-------|

| _       | -       | —      | -     | _     | _      | -       | _     |

| 23      | 22      | 21     | 20    | 19    | 18     | 17      | 16    |

| _       | Ι       | —      | Ι     | —     | -      |         | —     |

| 15      | 14      | 13     | 12    | 11    | 10     | 9       | 8     |

| _       | Ι       | —      | Ι     | —     | -      | RXFTHF2 | —     |

| 7       | 6       | 5      | 4     | 3     | 2      | 1       | 0     |

| RXFPTEF | TXFPTEF | RXFTHF | RXFFF | RXFEF | TXFTHF | TXFFF   | TXFEF |

TXFEF: TXFEF Interrupt Enable

**TXFFF: TXFFF Interrupt Enable**

**TXFTHF: TXFTHF Interrupt Enable**

**RXFEF: RXFEF Interrupt Enable**

**RXFFF: RXFFF Interrupt Enable**

**RXFTHF: RXFTHF Interrupt Enable**

**TXFPTEF: TXFPTEF Interrupt Enable**

**RXFPTEF: RXFPTEF Interrupt Enable**

**RXFTHF2: RXFTHF2 Interrupt Enable**

# 49.8 Serial Peripheral Interface (SPI) User Interface

In the "Offset" column of Table 49-5, 'CS\_number' denotes the chip select number.

### Table 49-5: Register Mapping

| Offset                    | Register                         | Name     | Access     | Reset |

|---------------------------|----------------------------------|----------|------------|-------|

| 0x00                      | Control Register                 | SPI_CR   | Write-only | _     |

| 0x04                      | Mode Register                    | SPI_MR   | Read/Write | 0x0   |

| 0x08                      | Receive Data Register            | SPI_RDR  | Read-only  | 0x0   |

| 0x0C                      | Transmit Data Register           | SPI_TDR  | Write-only | _     |

| 0x10                      | Status Register                  | SPI_SR   | Read-only  | 0x0   |

| 0x14                      | Interrupt Enable Register        | SPI_IER  | Write-only | _     |

| 0x18                      | Interrupt Disable Register       | SPI_IDR  | Write-only | _     |

| 0x1C                      | Interrupt Mask Register          | SPI_IMR  | Read-only  | 0x0   |

| 0x20-0x2C                 | Reserved                         | -        | -          | _     |

| 0x30 + (CS_number * 0x04) | Chip Select Register             | SPI_CSR  | Read/Write | 0x0   |

| 0x40                      | FIFO Mode Register               | SPI_FMR  | Read/Write | 0x0   |

| 0x44                      | FIFO Level Register              | SPI_FLR  | Read-only  | 0x0   |

| 0x48                      | Comparison Register              | SPI_CMPR | Read-only  | 0x0   |

| 0x4C-0xE0                 | Reserved                         | -        | -          | _     |

| 0xE4                      | Write Protection Mode Register   | SPI_WPMR | Read/Write | 0x0   |

| 0xE8                      | Write Protection Status Register | SPI_WPSR | Read-only  | 0x0   |

| 0xEC-0xF8                 | Reserved                         | -        | -          | _     |

| 0xFC                      | Reserved                         | _        | -          | _     |

## 49.8.15 SPI Comparison Register

| Name:    | SPI_CMPR                       |    |    |    |    |    |    |  |  |  |

|----------|--------------------------------|----|----|----|----|----|----|--|--|--|

| Address: | 0xF8000048 (0), 0xFC000048 (1) |    |    |    |    |    |    |  |  |  |

| Access:  | Read/Write                     |    |    |    |    |    |    |  |  |  |

| 31       | 30                             | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

|          |                                |    | VA | L2 |    |    |    |  |  |  |

| 23       | 22                             | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

|          |                                |    | VA | L2 |    |    |    |  |  |  |

| 15       | 14                             | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

|          | VAL1                           |    |    |    |    |    |    |  |  |  |

| 7        | 6                              | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

|          |                                |    | VA | L1 |    |    |    |  |  |  |

This register can only be written if the WPEN bit is cleared in the SPI Write Protection Mode Register.

#### VAL1: First Comparison Value for Received Character

0–65535: The received character must be higher or equal to the value of VAL1 and lower or equal to VAL2 to set CMP flag in SPI\_SR. If asynchronous partial wakeup (SleepWalking) is enabled in PMC\_SLPWK\_ER, the SPI requests a system wakeup if the condition is met.

#### VAL2: Second Comparison Value for Received Character

0–65535: The received character must be lower or equal to the value of VAL2 and higher or equal to VAL1 to set CMP flag in SPI\_CSR. If asynchronous partial wakeup (SleepWalking) is enabled in PMC\_SLPWK\_ER, the SPI requests a system wakeup if condition is met.

| Name:   | SDMMC_ASAR |    |     |     |    |    |    |  |  |  |

|---------|------------|----|-----|-----|----|----|----|--|--|--|

| Access: | Read/Write |    |     |     |    |    |    |  |  |  |

| 31      | 30         | 29 | 28  | 27  | 26 | 25 | 24 |  |  |  |

|         |            |    | ADM | ASA |    |    |    |  |  |  |

| 23      | 22         | 21 | 20  | 19  | 18 | 17 | 16 |  |  |  |

|         |            |    | ADM | ASA |    |    |    |  |  |  |

| 15      | 14         | 13 | 12  | 11  | 10 | 9  | 8  |  |  |  |

|         |            |    | ADM | ASA |    |    |    |  |  |  |

| 7       | 6          | 5  | 4   | 3   | 2  | 1  | 0  |  |  |  |

|         | ADMASA     |    |     |     |    |    |    |  |  |  |

|         |            |    |     |     |    |    |    |  |  |  |

### 51.13.40 SDMMC ADMA System Address Register

#### ADMASA: ADMA System Address

This field holds the byte address of the executing command of the descriptor table. The 32-bit address descriptor uses SDMMC\_ASAR. At the start of ADMA, the user must set the start address of the descriptor table. The ADMA increments this register address, which points to the next Descriptor line to be fetched.

When the ADMA Error (ADMA) status flag rises, this field holds a valid descriptor address depending on the ADMA Error State (ERRST). The user must program Descriptor Table on 32-bit boundary and set 32-bit boundary address to this register. ADMA2 ignores the lower 2 bits of this register and assumes it to be 0.

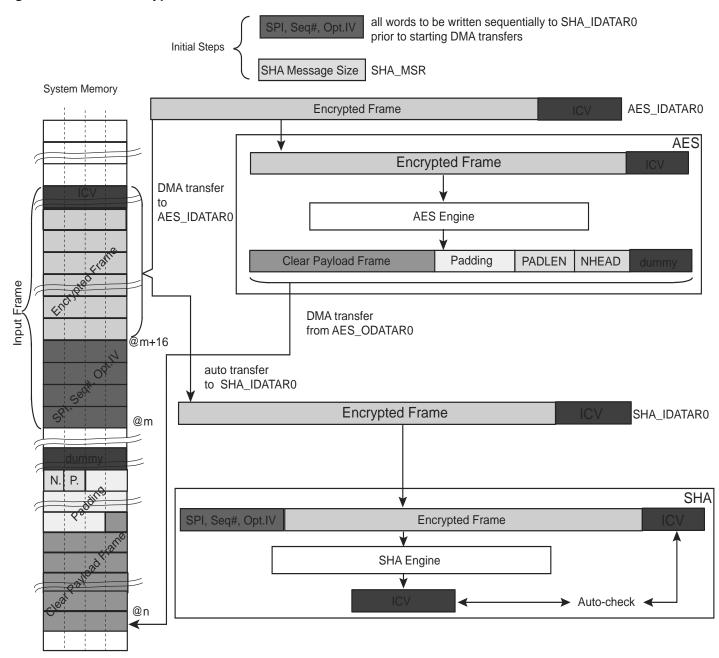

#### Figure 60-14: Decryption of an ESP IP Sec Frame without ESN

#### 62.5.12 TDES Initialization Vector Register x

| Name:<br>Address:<br>Access: | TDES_IVRx<br>0xFC044060<br>Write-only |    |    |    |    |    |    |

|------------------------------|---------------------------------------|----|----|----|----|----|----|

| 31                           | 30                                    | 29 | 28 | 27 | 26 | 25 | 24 |

|                              |                                       |    | N  | V  |    |    |    |

| 23                           | 22                                    | 21 | 20 | 19 | 18 | 17 | 16 |

|                              |                                       |    | N  | V  |    |    |    |

| 15                           | 14                                    | 13 | 12 | 11 | 10 | 9  | 8  |

|                              |                                       |    | N  | V  |    |    |    |

| 7                            | 6                                     | 5  | 4  | 3  | 2  | 1  | 0  |

|                              |                                       |    | N  | V  |    |    |    |

#### **IV: Initialization Vector**

The two 32-bit Initialization Vector registers are used to set the 64-bit initialization vector data block, which is used by some modes of operation as an additional initial input.

IV1 refers to the first word of the Initialization Vector, IV2 to the last one.

These registers are write-only to prevent the Initialization Vector from being read by another application.

**Note:** These registers are not used for the ECB mode and must not be written.