#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                   |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Product Status                     | Obsolete                                                                                          |

| Core Processor                     | ARM® Cortex®-A5                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 500MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ MPE                                                                             |

| RAM Controllers                    | LPDDR1, LPDDR2, LPDDR3, DDR2, DDR3, DDR3L, QSPI                                                   |

| Graphics Acceleration              | Yes                                                                                               |

| Display & Interface<br>Controllers | Keyboard, LCD, Touchscreen                                                                        |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 + HSIC                                                                                    |

| Voltage - I/O                      | 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 85°C (TA)                                                                                 |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 256-TFBGA                                                                                         |

| Supplier Device Package            | 256-TFBGA (8x8)                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d24b-cur                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Block Diagram

Figure 3-1: SAMA5D2 Series Block Diagram

Note: Refer to Section 38. "DMA Controller (XDMAC)" for peripheral connections to DMA.

#### 29.6.2.3 Firmware in SRAM Code Area

The firmware contains all PTC subsystem functionalities, allowing PTC measurement in the different conditions of parameters and configurations. The firmware is a binary file copied to the SRAM code area at the address defined by the memory map. The firmware makes the pPP work properly with some peripherals like the timer, a clock generator and obviously the PTC digital controller and the PTC analog front end. The firmware embeds all QTML (QTouch Modular Library) functionalities. Those modules are not modifiable by the application developer. The QTML functionalities configuration and data are controllable by the mailbox. The host has read and write accesses to the mailbox.

#### 29.6.2.4 Host Interface

The pPP can be controlled by the host processor through an APB interface and the user interface registers. This is referred to as the "host interface". Some configurations are only accessible when the pPP is stopped. The host interface includes pPP flags, which are also called host flags on the firmware, for interprocessor communications. The user interface registers can run, stop and reset the pPP and read the IRQ host flags. Nevertheless, the mailbox remains the main means of communication.

#### Processor Command Registers

The CMD field is part of the host interface and is used to start, stop and reset the pPP. Writing a valid command to this field changes the internal state of the pPP. After a number of cycles, this state change is reflected in the processor state register.

When a START command is issued, the host is no longer able to write to host interface registers which are marked as run-time writelocked. The pPP RAM block is also locked by this command. The host interface registers and RAM block can be unlocked by using the STOP or RESET commands. The lock is released when the processor state register reflects this state.

#### 29.6.3 PTC Digital Controller

The PTC digital controller is a peripheral of the pPP. It is intended for acquiring capacitive touch sensor and capacitive proximity sensor signals under limited firmware control by the controlling processor. The PTC digital controller consists of an Analog Charge Integrator and a 10-bit ADC Controller, 16-bit Digital Accumulator for the ADC results and a State Machine taking care of sensor sampling and digital accumulation sequence.

#### 29.6.3.1 PTC Digital Controller Operations

- Sensing mode (mutual or self)

- Control of the ADC 10-bit SAR state machine single ADC conversion or free run mode (comparator and ADC data/accumulator register)

- Digital gain up to 32 and averaging up to 64 ADC codes

- Selection of the filtering resistance (0, 20, 50 or 100 k?)

- Adjustment of the compensation capacitor up to 30 pF

- Adjustment of the integration capacitor up to 30 pF

- Frequency hopping<sup>(1)</sup> implementation (modification of the sampling rate to avoid synchronous parasitic noise)

- Channel Change Delay Selection CDS<sup>(2)</sup> (settling time)

- Prescaling (1, 1/2, 1/4, 1/8), 4 MHz down to ADC\_CLK

- **Note 1:** A programmable sampling delay can be used to choose (modify) the sampling frequency that is best suited in an application where other periodic noise sources may otherwise disturb the sampling. Frequency hopping can also be modified automatically from one sampling cycle to another, by setting the software driver parameters.

- 2: CDS bits define the delay when changing input channels. The delay allows the analog circuits to settle on a new (Y) channel or channel pair (X-Y). The delay is application-dependent, and therefore this option enables the user to select a suitable delay. The delay is expressed as a number of PTC clock cycles.

#### 29.6.4 PTC Analog Front End (AFE)

The analog front end consists of X-line drivers, a sensor capacitance compensation circuit and a parasitic capacitance insensitive analog Switched Capacitor Charge Integrator (SCCI). The integrator is connected to sensor Y-lines via an analog multiplexer. When the PTC digital controller is enabled, the SCCI output is automatically connected to the ADC input.

The external capacitive touch sensor is typically formed on a PCB and the sensor electrodes are connected to the Analog Charge Integrator of the PTC AFE via MCU I/O port pins. The PTC AFE supports mutual capacitance sensors organized as capacitive touch matrices in different X-Y configurations (QTouch Surface). The PTC AFE requires one pin per X-line and one pin per Y-line. No external components are needed.

The PTC AFE also supports "self-capacitance touch sensors" (QTouch). In Self-capacitance mode, the PTC AFE requires just one Y-line pin per self-capacitance sensor.

| Address: | CKGR_PLLAR<br>0xF0014028<br>Read/Write | J        |           |             |            |          |           |

|----------|----------------------------------------|----------|-----------|-------------|------------|----------|-----------|

| 31       | 30                                     | 29       | 28        | 27          | 26         | 25       | 24        |

| _        | _                                      | ONE      | _         | _           | _          | _        | MULA      |

| 23       | 22                                     | 21<br>ML | 20<br>JLA | 19          | 18         | 17<br>Ol | 16<br>JTA |

| 15       | 14<br>OUTA                             | 13       | 12        | 11<br>PLLAC | 10<br>OUNT | 9        | 8         |

| 7        | 6                                      | 5        | 4         | 3           | 2          | 1        | 0         |

| -        | -                                      | _        | _         | _           | _          | _        | DIVA      |

# 33.22.10 PMC Clock Generator PLLA Register

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

Possible limitations on PLL input frequencies and multiplier factors should be checked before using the PMC.

#### **DIVA: Divider A**

0: PLLA is disabled.

1: Divider is bypassed and the PLL input entry is Main clock (MAINCK).

#### **PLLACOUNT: PLLA Counter**

Specifies the number of Slow clock cycles before the LOCKA bit is set in PMC\_SR after CKGR\_PLLAR is written.

# OUTA: PLLA Clock Frequency Range

To be programmed to 0.

#### **MULA: PLLA Multiplier**

0: The PLLA is disabled.

1–127: The PLLA Clock frequency is the PLLA input frequency multiplied by MULA + 1.

## ONE: Must Be Set to 1

Bit 29 must always be set to 1 when programming CKGR\_PLLAR.

# 36. Multiport DDR-SDRAM Controller (MPDDRC)

# 36.1 Description

The Multiport DDR-SDRAM Controller (MPDDRC) is a multiport memory controller. It comprises eight slave AHB interfaces. All simultaneous accesses (eight independent AHB ports) are interleaved to maximize memory bandwidth and minimize transaction latency due to DDR-SDRAM protocol.

The MPDDRC extends the memory capabilities of a chip by providing the interface to the external 16-bit or 32-bit DDR-SDRAM device. The page size supports ranges from 2048 to 16384 rows and from 256 to 4096 columns. It supports dword (64-bit), word (32-bit), half-word (16-bit), and byte (8-bit) accesses.

The MPDDRC supports a read or write burst length of eight locations. This enables the command and address bus to anticipate the next command, thus reducing latency imposed by the DDR-SDRAM protocol and improving the DDR-SDRAM bandwidth. Moreover, MPDDRC keeps track of the active row in each bank, thus maximizing DDR-SDRAM performance, e.g., the application may be placed in one bank and data in other banks. To optimize performance, avoid accessing different rows in the same bank. The MPDDRC supports a CAS latency of 2, 3, 5 or 6 and optimizes the read access depending on the frequency.

Self-refresh, Powerdown and Deep Powerdown modes minimize the consumption of the DDR-SDRAM device.

OCD (Off-chip Driver) and ODT (On-die Termination) modes are not supported.

The MPDDRC supports DDR3-SDRAM and DDR3L-SDRAM devices with DLL disabled, in DLL Off mode. In this mode, according to JEDEC standard, the maximum clock frequency is 125 MHz. However, check with memory suppliers for higher speed support. DDR3-SDRAM supports high capacity, 1 Gbit and more, and allows to reduce power consumption with a 1.5V supply (DDR3-SDRAM) or a 1.35V supply (DDR3L-SDRAM). The DLL Off mode sets the CAS Read Latency (CRL) and the CAS Write Latency (CWL) to 6. The latency is automatically set by the controller.

# **TFAW: Four Active Windows**

Reset value is 4 DDRCK<sup>(1)</sup> clock cycles.

DDR2 and DDR3 devices with eight banks (1 Gbit or larger) have an additional requirement concerning  $t_{FAW}$  timing. This requires that no more than four Activate commands may be issued in any given  $t_{FAW}$  (MIN) period.

The number of cycles is between 0 and 15.

This field is found only in DDR2-SDRAM and LPDDR2-SDRAM and DDR3-SDRAM and LPDDR3-SDRAM devices.

**Note 1:** DDRCK is the clock that drives the SDRAM device.

| 33.7.33  | Dase Layer Coming | uration Regist |       |       |    |           |    |

|----------|-------------------|----------------|-------|-------|----|-----------|----|

| Name:    | LCDC_BASECFG6     |                |       |       |    |           |    |

| Address: | 0xF0000084        |                |       |       |    |           |    |

| Access:  | Read/Write        |                |       |       |    |           |    |

| 31       | 30                | 29             | 28    | 27    | 26 | 25        | 24 |

| -        | -                 | -              | -     | -     |    | DISCYSIZE |    |

| 23       | 22                | 21             | 20    | 19    | 18 | 17        | 16 |

|          |                   |                | DISCY | YSIZE |    |           |    |

| 15       | 14                | 13             | 12    | 11    | 10 | 9         | 8  |

| -        | -                 | -              | -     |       |    | DISCXSIZE |    |

| 7        | 6                 | 5              | 4     | 3     | 2  | 1         | 0  |

|          |                   |                | DISC> | KSIZE |    |           |    |

# 39.7.33 Base Layer Configuration Register 6

#### **DISCXSIZE:** Discard Area Horizontal Size

Discard Horizontal size in pixels. The Discard size is set to (DISCXSIZE + 1) pixels horizontally.

#### **DISCYSIZE: Discard Area Vertical Size**

Discard Vertical size in pixels. The Discard size is set to (DISCYSIZE + 1) pixels vertically.

# 39.7.104 High-End Overlay Configuration Register 9

| Name:<br>Address:<br>Access: | LCDC_HEC<br>0xF00003B<br>Read/Write |    |    |    |    |    |    |    |

|------------------------------|-------------------------------------|----|----|----|----|----|----|----|

| 31                           |                                     | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

| -                            |                                     | -  | -  | -  | -  | -  | -  | -  |

| 23                           |                                     | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|                              |                                     |    |    | RD | EF |    |    |    |

| 15                           |                                     | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|                              | GDEF                                |    |    |    |    |    |    |    |

| 7                            |                                     | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|                              |                                     |    |    | BD | EF |    |    |    |

#### **RDEF: Red Default**

Default Red color when the High-End Overlay DMA channel is disabled.

#### **GDEF: Green Default**

Default Green color when the High-End Overlay DMA channel is disabled.

#### **BDEF: Blue Default**

Default Blue color when the High-End Overlay DMA channel is disabled.

In the transmit direction, higher priority queues are always serviced before lower priority queues, with Q0 as lowest priority and Q2 as highest priority. This strict priority scheme requires the user to ensure that high priority traffic is constrained so that lower priority traffic will have required bandwidth. The GMAC DMA will determine the next queue to service by initiating a sequence of buffer descriptor reads interrogating the ownership bits of each. The buffer descriptor corresponding to the highest priority queue is read first. As an example, if the ownership bit of this descriptor is set, then the DMA will progress to reading the 2nd highest priority queue's descriptor. If that ownership bit read of this lower priority queue is set, then the DMA will read the 3rd highest priority queue's descriptor. If all the descriptors return an ownership bit set, then a resource error has occurred, an interrupt is generated and transmission is automatically halted. Transmission can only be restarted by setting the START bit in the Network Control register. The GMAC DMA will need to identify the highest available queue to transmit from when the START bit in the Network Control register is written to and the TX is in a halted state, or when the last word of any packet has been fetched from external AHB memory.

The GMAC transmit DMA maximizes the effectiveness of priority queuing by ensuring that high priority traffic be transmitted as early as possible after being fetched from AHB. High priority traffic fetched from AHB will be pushed to the MAC layer, depending on traffic shaping being enabled and the associated credit value for that queue, before any lower priority traffic that may pre-exist in the transmit SRAM-based packet buffer. This is achieved by separating the transmit SRAM-based packet buffer into regions, one region per queue. The size of each region determines the amount of SRAM space allocated per queue.

For each queue, there is an associated Transmit Buffer Queue Base Address register. For the lowest priority queue (or the only queue when only one queue is selected), the Transmit Buffer Queue Base Address is located at address 0x1C. For all other queues, the Transmit Buffer Queue Base Address starting at address 0x40.

In the receive direction each packet is written to AHB data buffers in the order that it is received. For each queue, there is an independent set of receive AHB buffers for each queue. There is therefore a separate Receive Buffer Queue Base Address register for each queue. For the lowest priority queue (or the only queue when only one queue is selected), the Receive Buffer Queue Base Address is located at address 0x18. For all other queues, the Receive Buffer Queue Base Address registers are located at sequential addresses starting at address 0x480. Every received packet will pass through a programmable screening algorithm which will allocate a particular queue to that frame. The user interface to the screeners is through two types of programmable registers:

- Screening Type 1 registers—The module features 4 Screening Type 1 registers. Screening Type 1 registers hold values to match against specific IP and UDP fields of the received frames. The fields matched against are DS (Differentiated Services field of IPv4 frames), TC (Traffic class field of IPv6 frames) and/or the UDP destination port.

- Screening Type 2 registers—The module features 8 Screening Type 2 registers GMAC\_ST2RPQ. Screening Type 2 registers operate independently of Screening Type 1 registers and offer additional match capabilities. Screening Type 2 allows a screen to be configured that is the combination of all or any of the following comparisons:

- 1. An enable bit VLAN priority, VLANE. A VLAN priority match will be performed if the VLAN priority enable is set. The extracted priority field in the VLAN header is compared against VLANP in the GMAC\_ST2RPQ register itself.

- 2. An enable bit EtherType, ETHE. The EtherType field I2ETH inside GMAC\_ST2RPQ maps to one of 4 EtherType match registers, GMAC\_ST2ER. The extracted EtherType is compared against GMAC\_ST2ER designated by this EtherType field.

- An enable bit Compare A, COMPAE. This bit is associated with a Screening Type 2 Compare Word 0/1 register x, GMAC\_ST2CW0/

1.

- An enable bit Compare B, COMPBE. This bit is associated with a Screening Type 2 Compare Word 0/1 register x, GMAC\_ST2CW0/

1.

- 5. An enable bit Compare C, COMPCE. This bit is associated with a Screening Type 2 Compare Word 0/1 register x, GMAC\_ST2CW0/1.

Each screener type has an enable bit, a match pattern and a queue number. If a received frame matches on an enabled Screening register, then the frame will be tagged with the queue value in the associated Screening register, and forwarded onto the DMA and subsequently into the external memory associated with that queue. If two screeners are matched, then the one which resides at the lowest register address will take priority so care must be taken on the selection of the screener location.

When the priority queuing feature is enabled, the number of interrupt outputs from the GMAC core is increased to match the number of supported queues. The number of Interrupt Status registers is increased by the same number. Only DMA related events are reported using the individual interrupt outputs, as the GMAC can relate these events to specific queues. All other events generated within the GMAC are reported in the interrupt associated with the lowest priority queue. For the lowest priority queue (or the only queue when only 1 queue is selected), the Interrupt Status register is located at address 0x24. For all other queues, the Interrupt Status register is located at sequential addresses starting at address 0x400.

**Note:** The address matching is the first level of filtering. If there is a match, the screeners are the next level of filtering for routing the data to the appropriate queue. See Section 40.6.7 "MAC Filtering Block" for more details.

The additional screening done by the functions Compare A, B, and C each have an enable bit and compare register field. COMPA, COMPB and COMPC in GMAC\_ST2RPQ are pointers to a configured offset (OFFSVAL), value (COMPVAL), and mask (MASKVAL). If enabled, the compare is true if the data at the offset into the frame, ANDed with MASKVAL, is equal to the value of COMPVAL ANDed with

#### 40.6.8 Broadcast Address

#### 40.6.9 Hash Addressing

The hash address register is 64 bits long and takes up two locations in the memory map. The least significant bits are stored in Hash Register Bottom and the most significant bits in Hash Register Top.

The unicast hash enable and the multicast hash enable bits in the Network Configuration register enable the reception of hash matched frames. The destination address is reduced to a 6-bit index into the 64-bit Hash register using the following hash function: The hash function is an XOR of every sixth bit of the destination address.

```

hash_index[05] = da[05] ^ da[11] ^ da[17] ^ da[23] ^ da[29] ^ da[35] ^ da[41] ^ da[47]

hash_index[04] = da[04] ^ da[10] ^ da[16] ^ da[22] ^ da[28] ^ da[34] ^ da[40] ^ da[46]

hash_index[03] = da[03] ^ da[09] ^ da[15] ^ da[21] ^ da[27] ^ da[33] ^ da[39] ^ da[45]

hash_index[02] = da[02] ^ da[08] ^ da[14] ^ da[20] ^ da[26] ^ da[32] ^ da[38] ^ da[44]

hash_index[01] = da[01] ^ da[07] ^ da[13] ^ da[19] ^ da[25] ^ da[31] ^ da[37] ^ da[43]

hash_index[00] = da[00] ^ da[06] ^ da[12] ^ da[18] ^ da[24] ^ da[30] ^ da[36] ^ da[42]

```

#### da[0]

represents the least significant bit of the first byte received, that is, the multicast/unicast indicator, and da[47] represents the most significant bit of the last byte received.

If the hash index points to a bit that is set in the Hash register then the frame will be matched according to whether the frame is multicast or unicast.

A multicast match will be signalled if the multicast hash enable bit is set, da[0] is logic 1 and the hash index points to a bit set in the Hash register.

A unicast match will be signalled if the unicast hash enable bit is set, **da[0]** is logic 0 and the hash index points to a bit set in the Hash register.

To receive all multicast frames, the Hash register should be set with all ones and the multicast hash enable bit should be set in the Network Configuration register.

#### 40.6.10 Copy all Frames (Promiscuous Mode)

If the Copy All Frames bit is set in the Network Configuration register then all frames (except those that are too long, too short, have FCS errors or have GRXER asserted during reception) will be copied to memory. Frames with FCS errors will be copied if bit 26 is set in the Network Configuration register.

#### 40.6.11 Disable Copy of Pause Frames

Pause frames can be prevented from being written to memory by setting the disable copying of pause frames control bit 23 in the Network Configuration register. When set, pause frames are not copied to memory regardless of the Copy All Frames bit, whether a hash match is found, a type ID match is identified or if a destination address match is found.

#### 40.6.12 VLAN Support

The following table describes an Ethernet encoded 802.1Q VLAN tag.

#### Table 40-7: 802.1Q VLAN Tag

| TPID (Tag Protocol Identifier) 16 bits | TCI (Tag Control Information) 16 bits                 |  |  |

|----------------------------------------|-------------------------------------------------------|--|--|

| 0x8100                                 | First 3 bits priority, then CFI bit, last 12 bits VID |  |  |

The VLAN tag is inserted at the 13th byte of the frame adding an extra four bytes to the frame. To support these extra four bytes, the GMAC can accept frame lengths up to 1536 bytes by setting bit 8 in the Network Configuration register.

If the VID (VLAN identifier) is null (0x000) this indicates a priority-tagged frame.

The following bits in the receive buffer descriptor status word give information about VLAN tagged frames:-

- Bit 21 set if receive frame is VLAN tagged (i.e., type ID of 0x8100).

- Bit 20 set if receive frame is priority tagged (i.e., type ID of 0x8100 and null VID). (If bit 20 is set, bit 21 will be set also.)

- Bit 19, 18 and 17 set to priority if bit 21 is set.

- Bit 16 set to CFI if bit 21 is set.

# SAMA5D2 SERIES

# 49.8.11 SPI Interrupt Mask Register

Name: SPI\_IMR

Address: 0xF800001C (0), 0xFC00001C (1)

Access: Read-only

| 31      | 30      | 29     | 28    | 27    | 26     | 25      | 24    |

|---------|---------|--------|-------|-------|--------|---------|-------|

| RXFPTEF | TXFPTEF | RXFTHF | RXFFF | RXFEF | TXFTHF | TXFFF   | TXFEF |

| 23      | 22      | 21     | 20    | 19    | 18     | 17      | 16    |

| _       | _       | -      | Ι     | -     | Ι      | Ι       | _     |

| 15      | 14      | 13     | 12    | 11    | 10     | 9       | 8     |

| -       | -       | -      | Ι     | CMP   | UNDES  | TXEMPTY | NSSR  |

| 7       | 6       | 5      | 4     | 3     | 2      | 1       | 0     |

| _       | _       | _      | -     | OVRES | MODF   | TDRE    | RDRF  |

The following configuration values are valid for all listed bit names of this register:

0: The corresponding interrupt is not enabled.

1: The corresponding interrupt is enabled.

**RDRF: Receive Data Register Full Interrupt Mask**

TDRE: SPI Transmit Data Register Empty Interrupt Mask

MODF: Mode Fault Error Interrupt Mask

**OVRES: Overrun Error Interrupt Mask**

**NSSR: NSS Rising Interrupt Mask**

**TXEMPTY: Transmission Registers Empty Mask**

**UNDES: Underrun Error Interrupt Mask**

**CMP: Comparison Interrupt Mask**

**TXFEF: TXFEF Interrupt Mask**

**TXFFF: TXFFF Interrupt Mask**

**TXFTHF: TXFTHF Interrupt Mask**

**RXFEF: RXFEF Interrupt Mask**

**RXFFF: RXFFF Interrupt Mask**

**RXFTHF: RXFTHF Interrupt Mask**

**TXFPTEF: TXFPTEF Interrupt Mask**

**RXFPTEF: RXFPTEF Interrupt Mask**

# 51.13.23 SDMMC Normal Interrupt Status Enable Register (SD\_SDIO)

| Name: | SDMMC_NISTER (SD_SDIO) |  |

|-------|------------------------|--|

|       |                        |  |

#### Access: Read/Write

| 15   | 14   | 13     | 12     | 11     | 10    | 9    | 8    |

|------|------|--------|--------|--------|-------|------|------|

| -    | _    | _      | _      | _      | _     | _    | CINT |

| 7    | 6    | 5      | 4      | 3      | 2     | 1    | 0    |

| CREM | CINS | BRDRDY | BWRRDY | DMAINT | BLKGE | TRFC | CMDC |

### **CMDC: Command Complete Status Enable**

0 (MASKED): The CMDC status flag in SDMMC\_NISTR is masked.1 (ENABLED): The CMDC status flag in SDMMC\_NISTR is enabled.

#### **TRFC: Transfer Complete Status Enable**

0 (MASKED): The TRFC status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The TRFC status flag in SDMMC\_NISTR is enabled.

## **BLKGE: Block Gap Event Status Enable**

0 (MASKED): The BLKGE status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The BLKGE status flag in SDMMC\_NISTR is enabled.

#### **DMAINT: DMA Interrupt Status Enable**

0 (MASKED): The DMAINT status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The DMAINT status flag in SDMMC\_NISTR is enabled.

# **BWRRDY: Buffer Write Ready Status Enable**

0 (MASKED): The BWRRDY status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The BWRRDY status flag in SDMMC\_NISTR is enabled.

#### **BRDRDY: Buffer Read Ready Status Enable**

0 (MASKED): The BRDRDY status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The BRDRDY status flag in SDMMC\_NISTR is enabled.

#### **CINS: Card Insertion Status Enable**

0 (MASKED): The CINS status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The CINS status flag in SDMMC\_NISTR is enabled.

#### **CREM: Card Removal Status Enable**

0 (MASKED): The CREM status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The CREM status flag in SDMMC\_NISTR is enabled.

#### **CINT: Card Interrupt Status Enable**

If this bit is set to 0, the SDMMC clears interrupt requests to the system. The Card Interrupt detection is stopped when this bit is cleared and restarted when this bit is set to 1. The user may clear this bit before servicing the Card Interrupt and may set this bit again after all interrupt requests from the card are cleared to prevent inadvertent interrupts.

0 (MASKED): The CINT status flag in SDMMC\_NISTR is masked.

1 (ENABLED): The CINT status flag in SDMMC\_NISTR is enabled.

# 51.13.41 SDMMC Preset Value Register

| Name:<br>Access: | SDMMC_PVRx [x=0 <sup>-</sup><br>Read/Write | 7] |    |    |         |      |       |

|------------------|--------------------------------------------|----|----|----|---------|------|-------|

| 15               | 14<br>DRVSEL                               | 13 | 12 | 11 |         | 9    | 8     |

|                  | DRVSEL                                     | _  | -  | _  | CLKGSEL | SDCL | KFSEL |

| 7                | 6                                          | 5  | 4  | 3  | 2       | 1    | 0     |

|                  | SDCLKFSEL                                  |    |    |    |         |      |       |

One of the Preset Value Registers is effective based on the selected bus speed mode. Table 51-8 defines the conditions to select one of the SDMMC\_PVRs.

| Selected Bus Speed Mode | VS18EN<br>(SDMMC_HC2R) | HSEN<br>(SDMMC_HC1R) | UHSMS<br>(SDMMC_HC2R) |

|-------------------------|------------------------|----------------------|-----------------------|

| Default Speed           | 0                      | 0                    | don't care            |

| High Speed              | 0                      | 1                    | don't care            |

| SDR12                   | 1                      | don't care           | 0                     |

| SDR25                   | 1                      | don't care           | 1                     |

| SDR50                   | 1                      | don't care           | 2                     |

| SDR104/HS200            | 1                      | don't care           | 3                     |

| DDR50                   | 1                      | don't care           | 4                     |

| Reserved                | 1                      | don't care           | Other values          |

Table 51-9 shows the effective Preset Value Register according to the Selected Bus Speed mode.

| Table 51-9: | Preset Value Registers |

|-------------|------------------------|

|-------------|------------------------|

| SDMMC_PVRx | Selected Bus Speed Mode | Signal Voltage |

|------------|-------------------------|----------------|

| SDMMC_PVR0 | Initialization          | 3.3V or 1.8V   |

| SDMMC_PVR1 | Default Speed           | 3.3V           |

| SDMMC_PVR2 | High Speed              | 3.3V           |

| SDMMC_PVR3 | SDR12                   | 1.8V           |

| SDMMC_PVR4 | SDR25                   | 1.8V           |

| SDMMC_PVR5 | SDR50                   | 1.8V           |

| SDMMC_PVR6 | SDR104/HS200            | 1.8V           |

| SDMMC_PVR7 | DDR50                   | 1.8V           |

When Preset Value Enable (PVALEN) in SDMMC\_HC2R is set to 1, SDCLK Frequency Select (SDLCKFSEL) and Clock Generator Select (CLKGSEL) in SDMMC\_CCR, and Driver Strength Select (DRVSEL) in SDMMC\_HC2R are automatically set based on the Selected Bus Speed mode. This means that the user does not need to set these fields when preset is enabled. A Preset Value Register for Initialization (SDMMC\_PVR0) is not selected by Bus Speed mode. Before starting the initialization sequence, the user needs to set a clock preset value to SDCLKFSEL in SDMMC\_CCR. PVALEN can be set to 1 after the initialization is completed.

**Note:** Preset Values in SDMMC\_PVRx registers are not supposed to be written by the user. However, the user can modify preset values only if Capabilities Write Enable (CAPWREN) is set to 1 in SDMMC\_CACR.

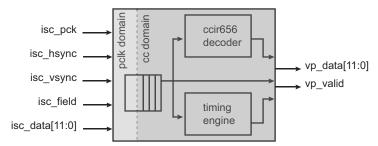

# 52.5.5 Parallel Front End (PFE) Module

## Figure 52-14: PFE Block Diagram

The Parallel Front End module performs data resampling across clock domain boundary. It includes a CCIR656 decoder used to convert a standard ITU-R BT.656 stream to 24-bit digital video. It also generates pixels, syncs flags and valid signals to the main video pipeline. It ouputs field, video and synchronization signals. The PFE can optionally crop and limit the incoming pixel stream to a predefined horizontal and vertical value. By default, the PFE only relies on the cmos sensor horizontal and vertical reference to sample the incoming pixel stream. A pixel is sampled if, and only if, the vertical and horizontal synchronizations are valid and a pixel clock edge is detected. ISC\_PFE\_CFG0.BPS shows the number of bits per sample. The PFE module outputs a 12-bit data on the vp\_data[11:0] bus, and asserts the vp\_valid signal when the data can be sampled.

| PFE VP_DATA<br>Mapping | Raw Bayer<br>12-bit | Raw Bayer<br>10-bit | YUV422<br>8-bit | YUV422<br>10-bit | Mono<br>12-bit |

|------------------------|---------------------|---------------------|-----------------|------------------|----------------|

| VP_DATA[11]            | RGGB[11]            | RGGB[9]             | YC422[7]        | YC422[9]         | Y[11]          |

| VP_DATA[10]            | RGGB[10]            | RGGB[8]             | YC422[6]        | YC422[8]         | Y[10]          |

| VP_DATA[9]             | RGGB[9]             | RGGB[7]             | YC422[5]        | YC422[7]         | Y[9]           |

| VP_DATA[8]             | RGGB[8]             | RGGB[6]             | YC422[4]        | YC422[6]         | Y[8]           |

| VP_DATA[7]             | RGGB[7]             | RGGB[5]             | YC422[3]        | YC422[5]         | Y[7]           |

| VP_DATA[6]             | RGGB[6]             | RGGB[4]             | YC422[2]        | YC422[4]         | Y[6]           |

| VP_DATA[5]             | RGGB[5]             | RGGB[3]             | YC422[1]        | YC422[3]         | Y[5]           |

| VP_DATA[4]             | RGGB[4]             | RGGB[2]             | YC422[0]        | YC422[2]         | Y[4]           |

| VP_DATA[3]             | RGGB[3]             | RGGB[1]             | YC422[7] or 0   | YC422[1]         | Y[3]           |

| VP_DATA[2]             | RGGB[2]             | RGGB[0]             | YC422[6] or 0   | YC422[0]         | Y[2]           |

| VP_DATA[1]             | RGGB[1]             | RGGB[9] or 0        | YC422[5] or 0   | YC422[9] or 0    | Y[1]           |

| VP_DATA[0]             | RGGB[0]             | RGGB[8] or 0        | YC422[4] or 0   | YC422[8] or 0    | Y[0]           |

**Note:** When ISC\_PFE\_CFG0.REP is set, missing VP\_DATA LSBs are replaced with replicated LSBs of the incoming stream, otherwise they are forced to zero.

The PFE module also includes logic to synchronize capture request with the incoming pixel stream. Two operating modes are available: Single Shot and Continuous Acquisition. When the ISC\_PFE\_CFG0.CONT field is cleared, the ISC transfers a single image to memory,

# 53.6.27 MCAN Receive FIFO 0 Configuration

Name: MCAN\_RXF0C Address: 0xF80540A0 (0), 0xFC0500A0 (1)

# Access: Read/Write

| 31   | 30   | 29 | 28 | 27  | 26 | 25 | 24 |

|------|------|----|----|-----|----|----|----|

| F0OM | FOWM |    |    |     |    |    |    |

| 23   | 22   | 21 | 20 | 19  | 18 | 17 | 16 |

| -    |      |    |    | F0S |    |    |    |

| 15   | 14   | 13 | 12 | 11  | 10 | 9  | 8  |

|      | F0SA |    |    |     |    |    |    |

| 7    | 6    | 5  | 4  | 3   | 2  | 1  | 0  |

|      | F0SA |    |    |     |    | _  | —  |

This register can only be written if the bits CCE and INIT are set in MCAN CC Control Register.

## F0SA: Receive FIFO 0 Start Address

Start address of Receive FIFO 0 in Message RAM (32-bit word address, see Figure 53-12).

Write F0SA with the bits [15:2] of the 32-bit address.

#### F0S: Receive FIFO 0 Size

0: No Receive FIFO 0

1-64: Number of Receive FIFO 0 elements.

>64: Values greater than 64 are interpreted as 64.

The Receive FIFO 0 elements are indexed from 0 to F0S-1.

#### F0WM: Receive FIFO 0 Watermark

0: Watermark interrupt disabled.

1-64: Level for Receive FIFO 0 watermark interrupt (MCAN\_IR.RF0W).

>64: Watermark interrupt disabled.

#### F0OM: FIFO 0 Operation Mode

FIFO 0 can be operated in Blocking or in Overwrite mode (see Section 53.5.4.2).

0: FIFO 0 Blocking mode.

1: FIFO 0 Overwrite mode.

# 53.6.44 MCAN Transmit Buffer Cancellation Finished Interrupt Enable

| 31       |      | 30               | 29          | 28 |  |

|----------|------|------------------|-------------|----|--|

| Access:  | Read | I/Write          |             |    |  |

| Address: | 0xF8 | 0540E4 (0), 0xF0 | C0500E4 (1) |    |  |

| Name:    | MCA  | N_TXBCIE         |             |    |  |

| 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CFIE31 | CFIE30 | CFIE29 | CFIE28 | CFIE27 | CFIE26 | CFIE25 | CFIE24 |

| 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

| CFIE23 | CFIE22 | CFIE21 | CFIE20 | CFIE19 | CFIE18 | CFIE17 | CFIE16 |

| 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |

| CFIE15 | CFIE14 | CFIE13 | CFIE12 | CFIE11 | CFIE10 | CFIE9  | CFIE8  |

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| CFIE7  | CFIE6  | CFIE5  | CFIE4  | CFIE3  | CFIE2  | CFIE1  | CFIE0  |

# CFIEx: Cancellation Finished Interrupt Enable for Transmit Buffer x

Each Transmit Buffer has its own Cancellation Finished Interrupt Enable bit.

0: Cancellation finished interrupt disabled.

1: Cancellation finished interrupt enabled.

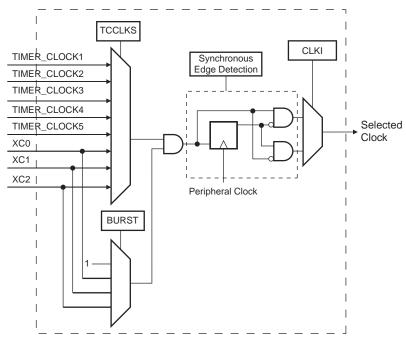

## Figure 54-3: Clock Selection

## 54.6.4 Clock Control

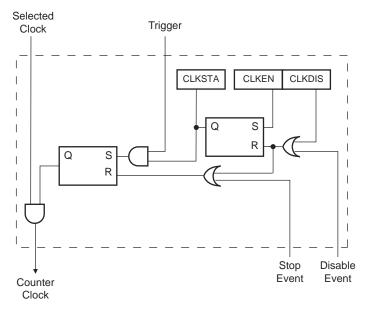

The clock of each counter can be controlled in two different ways: it can be enabled/disabled and started/stopped. See Figure 54-4.

- The clock can be enabled or disabled by the user with the CLKEN and the CLKDIS commands in the Channel Control register (TC\_CCR). In Capture mode it can be disabled by an RB load event if TC\_CMRx.LDBDIS is set to '1'. In Waveform mode, it can be disabled by an RC Compare event if TC\_CMRx.CPCDIS is set to '1'. When disabled, the start or the stop actions have no effect: only a CLKEN command in the TC\_CCR can reenable the clock. When the clock is enabled, TC\_SR.CLKSTA is set.

- The clock can also be started or stopped: a trigger (software, synchro, external or compare) always starts the clock. The clock can

be stopped by an RB load event in Capture mode (TC\_CMRx.LDBSTOP = 1) or an RC compare event in Waveform mode

(TC\_CMRx.CPCSTOP = 1). The start and the stop commands are effective only if the clock is enabled.

#### Figure 54-4: Clock Control

## • Application Example

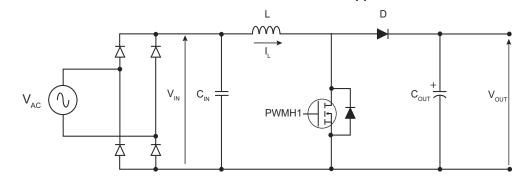

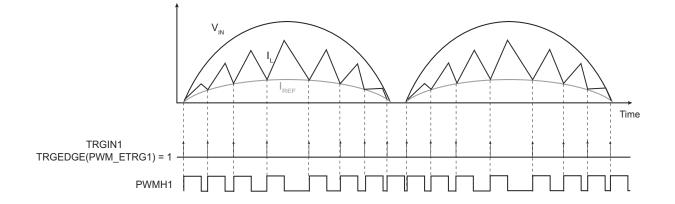

The external PWM Reset mode can be used in power factor correction applications.

In the example below, the external trigger input is the PWMEXTRG1 (therefore the PWM channel used for regulation is the channel 1). The PWM channel 1 period (CPRD in the PWM Channel Period Register of the channel 1) must be programmed so that the TRGIN1 event always triggers before the PWM channel 1 period elapses.

In Figure 56-28, an external circuit (not shown) is required to sense the inductor current  $I_L$ . The internal PWM counter of the channel 1 is cleared when the inductor current falls below a specific threshold ( $I_{REF}$ ). This starts a new PWM period and increases the inductor current.

Figure 56-28: External PWM Reset Mode: Power Factor Correction Application

## 56.6.7 Register Write Protection

To prevent any single software error that may corrupt PWM behavior, the registers listed below can be write-protected by writing the field WPCMD in the PWM Write Protection Control Register (PWM\_WPCR). They are divided into six groups:

- Register group 0:

- PWM Clock Register

- Register group 1:

- PWM Disable Register

- Register group 2:

- PWM Sync Channels Mode Register

- PWM Channel Mode Register

- PWM Stepper Motor Mode Register

- PWM Fault Protection Value Register 2

- PWM Leading-Edge Blanking Register

- PWM Channel Mode Update Register

- Register group 3:

- PWM Spread Spectrum Register

- PWM Spread Spectrum Update Register

- PWM Channel Period Register

- PWM Channel Period Update Register

- Register group 4:

- PWM Channel Dead Time Register

- PWM Channel Dead Time Update Register

- Register group 5:

- PWM Fault Mode Register

- PWM Fault Protection Value Register 1

There are two types of write protection:

- SW write protection—can be enabled or disabled by software

- HW write protection—can be enabled by software but only disabled by a hardware reset of the PWM controller

Both types of write protection can be applied independently to a particular register group by means of the WPCMD and WPRGx fields in PWM\_WPCR. If at least one type of write protection is active, the register group is write-protected. The value of field WPCMD defines the action to be performed:

- 0: Disables SW write protection of the register groups of which the bit WPRGx is at '1'

- 1: Enables SW write protection of the register groups of which the bit WPRGx is at '1'

- 2: Enables HW write protection of the register groups of which the bit WPRGx is at '1'

At any time, the user can determine whether SW or HW write protection is active in a particular register group by the fields WPSWS and WPHWS in the PWM Write Protection Status Register (PWM\_WPSR).

If a write access to a write-protected register is detected, the WPVS flag in PWM\_WPSR is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS and WPVSRC fields are automatically cleared after reading PWM\_WPSR.

Note: The reference voltage pins always remain connected in Normal mode as in Sleep mode.

#### 65.6.9 Comparison Window

The ADC Controller features automatic comparison functions. It compares converted values to a low threshold, a high threshold or both, depending on the value of the CMPMODE field in ADC\_EMR. The comparison can be done on all channels or only on the channel specified in the CMPSEL field of ADC\_EMR. To compare all channels, the CMPALL bit of ADC\_EMR must be set.

If set, the CMPTYPE bit of ADC\_EMR can be used to discard all conversion results that do not match the comparison conditions. Once a conversion result matches the comparison conditions, all the subsequent conversion results are stored in ADC\_LCDR (even if these results do not meet the comparison conditions). Setting the CMPRST bit in ADC\_CR immediately stops the conversion result storage until the next comparison match.

If the CMPTYPE bit in ADC\_EMR is cleared, all conversions are stored in ADC\_LCDR. Only the conversions that match the comparison conditions trigger the COMPE flag in ADC\_ISR.

Moreover, a filtering option can be set by writing the number of consecutive comparison matches needed to raise the flag. This number can be written and read in the CMPFILTER field of ADC\_EMR. The filtering option is dedicated to reinforcing the detection of an analog signal overpassing a predefined threshold. The filter is cleared as soon as ADC\_ISR is read, so this filtering function must be used with peripheral DMA controller and works only when using Interrupt mode (no polling).

The flag can be read on the COMPE bit of the Interrupt Status register (ADC\_ISR) and can trigger an interrupt.

The high threshold and the low threshold can be read/write in the Compare Window register (ADC\_CWR).

Depending on the sign of the conversion, chosen with the SIGNMODE field in the ADC Extended Mode Register, the high threshold and low threshold values must be signed or unsigned to maintain consistency during the comparison. If the conversion is signed, both thresholds must also be signed; if the conversion is unsigned, both thresholds must be unsigned. If comparison occurs on all channels, the SIGN-MODE field must be set to ALL\_UNSIGNED or ALL\_SIGNED and the thresholds must be set accordingly.

#### 65.6.10 Differential and Single-ended Input Modes

#### 65.6.10.1 Input-output Transfer Functions

The ADC can be configured to operate in the following input voltage modes:

- Single-ended—ADC\_COR.DIFFx = 0. This is the default mode after a reset.

- Differential—ADC\_COR.DIFFx = 1 (see Figure 65-7). In Differential mode, the ADC requires differential input signals having a VDD/ 2 common mode voltage (refer to the "Electrical Characteristics" section).

The following equations give the unsigned ADC input-output transfer function in each mode<sup>(1)</sup>. With signed conversions (see field ADC\_EMR.SIGNMODE), subtract 2047 from the ADC\_LCDR.DATA value given below.

Single-ended mode:

$$ADC\_LCDR.LDATA = \frac{ADx - GNDANA}{ADVREF - GNDANA} \times 2^{12}$$

Differential mode:

$$ADC\_LCDR.LDATA = \left(1 + \frac{ADx - ADx+1}{ADVREF - GNDANA}\right) \times 2^{11}$$

Note 1: Equations assume ADC\_EMR.OSR = 1

If the ANACH bit is set in ADC\_MR, the ADC can manage both differential channels and single-ended channels. If the ANACH bit is cleared, the parameters defined in ADC\_COR are applied to all channels.

Table 65-4 gives the internal positive and negative ADC inputs assignment with respect to the programmed mode (ADC\_COR.DIFFx).

For example, if Differential mode is required on channel 0, input pins AD0 and AD1 are used. In this case, only channel 0 must be enabled by writing a 1 to ADC\_CHER.CH0.

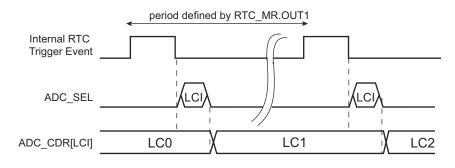

# Figure 65-10: Only Last Channel Measurement Triggered at Low Speed (ADC\_CHSR[LCI] = 0 and ADC\_TRGR.TRGMOD = 0)

#### ADC\_LCTMR.DUALTRIG = 1

Notes: ADC\_SEL: Command to the ADC analog cell LCx: Last channel value LCI: Last channel index

#### 65.6.13 Enhanced Resolution Mode and Digital Averaging Function

#### 65.6.13.1 Enhanced Resolution Mode

The Enhanced Resolution mode is enabled if the OSR field is configured to 1 or 2 in ADC\_EMR. The enhancement is based on a digital averaging function.

There is no averaging on the last index channel if the measure is triggered by an RTC event.

In this mode, the ADC Controller will trade off conversion speed against accuracy by averaging multiple samples, thus providing a digital low-pass filter function.

The selected oversampling ratio applies to all enabled channels when triggered by an RTC event.

$$ADC\_LCDR.LDATA = \frac{1}{M} \times \sum_{k = 0}^{k = N-1} ADC(k)$$

where N and M are given in the table below.

#### Table 65-5: Digital Averaging Function Configuration versus OSR Values

| ADC_EMR.OSR Value | ADC_LCDR.LDATA Length | N Value | M Value | Full Scale Value | Maximum Value |

|-------------------|-----------------------|---------|---------|------------------|---------------|

| 0                 | 12 bits               | 1       | 1       | 4095             | 4095          |

| 1                 | 13 bits               | 4       | 2       | 8191             | 8190          |

| 2                 | 14 bits               | 16      | 4       | 16383            | 16381         |

The average result is valid in ADC\_CDRx (x corresponds to the index of the channel) only if the EOCn flag is set in ADC\_ISR and if the OVREn flag is cleared in ADC\_OVER. The average result for all channels is valid in ADC\_LCDR only if DRDY is set and GOVRE is cleared in ADC\_ISR.

Note that ADC\_CDRs are not buffered. Therefore, when an averaging sequence is ongoing, the value in these registers changes after each averaging sample. However, overrun flags in ADC\_OVER rise as soon as the first sample of an averaging sequence is received. Thus the previous averaged value is not read, even if the new averaged value is not ready.

Consequently, when an overrun flag rises in ADC\_OVER, it means that the previous unread data is lost but it does not mean that this data has been overwritten by the new averaged value as the averaging sequence concerning this channel can still be ongoing.