#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XFI

| Product Status                     | Obsolete                                                                                          |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A5                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 500MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ MPE                                                                             |

| RAM Controllers                    | LPDDR1, LPDDR2, LPDDR3, DDR2, DDR3, DDR3L, QSPI                                                   |

| Graphics Acceleration              | Yes                                                                                               |

| Display & Interface<br>Controllers | Keyboard, LCD, Touchscreen                                                                        |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 + HSIC                                                                                    |

| Voltage - I/O                      | 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 105°C (TA)                                                                                |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 289-LFBGA                                                                                         |

| Supplier Device Package            | 289-LFBGA (14x14)                                                                                 |

| Purchase URL                       | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d26b-cnr                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 6-2: | Pin Description | (Continued) |

|------------|-----------------|-------------|

|------------|-----------------|-------------|

| 289-       | 256- | 196-       |              |           | Primary   |        | Alternate | •        |             | PIO peripheral |           |           | Reset State                                         |     |                |     |      |   |   |        |   |          |                |

|------------|------|------------|--------------|-----------|-----------|--------|-----------|----------|-------------|----------------|-----------|-----------|-----------------------------------------------------|-----|----------------|-----|------|---|---|--------|---|----------|----------------|

| pin<br>BGA | pin  | pin<br>BGA | Power Rail   | I/O Type  | Signal    | Dir    | Signal    | Dir      | Func        | Signal         | Dir       | IO<br>Set | (Signal, Dir, PU,<br>PD, HiZ, ST) <sup>(1)(2)</sup> |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | А           | URXD4          | I         | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | В           | D8             | I/O       | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

| A6         | B6   | B5         | VDDIOP0 GPIO | GPIO      | PB3       | I/O    | -         |          | С           | IRQ            | I         | 3         | PIO, I, PU, ST                                      |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | D           | PWMEXTRG1      | Ι         | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | F           | CLASSD_R2      | 0         | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | А           | UTXD4          | 0         | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

| DC         | 46   |            |              | GPIO      |           | I/O    |           |          | В           | D9             | I/O       | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

| B6         | A6   | A4         | VDDIOP0      | GPIO      | PB4 I     | 1/0    | -         | -        | С           | FIQ            | Ι         | 4         | PIO, I, PU, ST                                      |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           | F        | CLASSD_R3   | 0              | 1         |           |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | А           | TCLK2          | I         | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | В           | D10            | D10 I/O 1 |           |                                                     |     |                |     |      |   |   |        |   |          |                |

| B7         | D7   | D6         | VDDIOP0      | GPIO_QSPI | PB5 I/O – | I/O    | 0         |          |             | -              | С         | PWMH2     | 0                                                   | 1   | PIO, I, PU, ST |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          |             | D              | QSPI1_SCK | 0         | 2                                                   |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        | F         | GTSUCOMP | 0           | 3              |           |           |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | А           | TIOA2          | I/O       | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           | В      | D11       | I/O      | 1           |                |           |           |                                                     |     |                |     |      |   |   |        |   |          |                |

| C7         | B5   | A3         | A3           | VDDIOP0   | GPIO      | PB6 I/ | GPIO PB6  | I/O      | -           | -              | С         | PWML2     | 0                                                   | 1   | PIO, I, PU, ST |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          |             |                |           |           |                                                     |     |                |     |      |   |   |        | D | QSPI1_CS | 0              |

|            |      |            |              |           |           |        |           |          | F           | GTXER          | 0         | 3         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | А           | TIOB2          | I/O       | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           | PB7       |        |           |          |             |                | В         | D12       | I/O                                                 | 1   |                |     |      |   |   |        |   |          |                |

| C6         | A5   | B4         | VDDIOP0      | GPIO_IO   |           | I/O    | -         | _        | С           | PWMH3          | 0         | 1         | PIO, I, PU, ST                                      |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | D           | QSPI1_IO0      | I/O       | 2         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | F           | GRXCK          | I         | 3         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | А           | TCLK3          | I         | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | В           | D13            | I/O       | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

| A5         | E7   | A2         | VDDIOP0      | GPIO_IO   | PB8       | I/O    | _         | -        | С           | PWML3          | 0         | 1         | PIO, I, PU, ST                                      |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | D           | QSPI1_IO1      | I/O       | 2         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | F           | GCRS           | Ι         | 3         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | А           | TIOA3          | I/O       | 1         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           | PB9 I/O - |        |           |          |             | В              | D14       | I/O       | 1                                                   |     |                |     |      |   |   |        |   |          |                |

| A4         | F6   | В3         | VDDIOP0      | GPIO_IO   |           | PB9    | PB9       | D PB9    | O_IO PB9 I/ | О РВ9 І/О      | I/O       | PB9 I/O   | B9 I/O                                              | I/O | I/O            | I/O | ′O – | - | С | PWMFI1 | I | 1        | PIO, I, PU, ST |

|            |      |            |              |           |           |        |           |          | D           | QSPI1_IO2      | I/O       | 2         |                                                     |     |                |     |      |   |   |        |   |          |                |

|            |      |            |              |           |           |        |           |          | F           | GCOL           | 1         | 3         |                                                     |     |                |     |      |   |   |        |   |          |                |

See Section 14.4.1 "Double Linefill Issuing" for details on double linefill functionality.

## 19.3.3 OHCI Interrupt Status Register

| Address: 0xF8 | _OHCIISR<br>8030014<br>d/Write |    |    |    |      |      |      |

|---------------|--------------------------------|----|----|----|------|------|------|

| 31            | 30                             | 29 | 28 | 27 | 26   | 25   | 24   |

| _             | -                              | -  | —  | -  | -    | —    | -    |

| 23            | 22                             | 21 | 20 | 19 | 18   | 17   | 16   |

| _             | -                              | —  | —  | -  | -    | _    | -    |

| 15            | 14                             | 13 | 12 | 11 | 10   | 9    | 8    |

| _             | _                              | _  | _  | -  | _    | _    | -    |

| 7             | 6                              | 5  | 4  | 3  | 2    | 1    | 0    |

| _             | _                              | _  | _  | _  | RIS2 | RIS1 | RIS0 |

## **RISx: OHCI Resume Interrupt Status Port x**

0: OHCI port resume not detected.

1: OHCI port resume detected.

## 38.9.2 XDMAC Global Configuration Register

Name: XDMAC\_GCFG

Address: 0xF0010004 (0), 0xF0004004 (1)

Access: Read/Write

| 31 | 30 | 29 | 28 | 27      | 26        | 25        | 24       |

|----|----|----|----|---------|-----------|-----------|----------|

| -  | -  | —  | -  | -       | -         | -         | —        |

| 23 | 22 | 21 | 20 | 19      | 18        | 17        | 16       |

| _  | -  | -  | -  | -       | -         | —         | —        |

| 15 | 14 | 13 | 12 | 11      | 10        | 9         | 8        |

| -  | -  | -  | -  | -       | -         | -         | BXKBEN   |

| 7  | 6  | 5  | 4  | 3       | 2         | 1         | 0        |

| —  | -  | -  | -  | CGDISIF | CGDISFIFO | CGDISPIPE | CGDISREG |

#### CGDISREG: Configuration Registers Clock Gating Disable

0: The automatic clock gating is enabled for the configuration registers.

1: The automatic clock gating is disabled for the configuration registers.

## CGDISPIPE: Pipeline Clock Gating Disable

- 0: The automatic clock gating is enabled for the main pipeline.

- 1: The automatic clock gating is disabled for the main pipeline.

#### **CGDISFIFO: FIFO Clock Gating Disable**

- 0: The automatic clock gating is enabled for the main FIFO.

- 1: The automatic clock gating is disabled for the main FIFO.

## CGDISIF: Bus Interface Clock Gating Disable

- 0: The automatic clock gating is enabled for the system bus interface.

- 1: The automatic clock gating is disabled for the system bus interface.

## **BXKBEN: Boundary X Kilobyte Enable**

- 0: The 1 Kbyte boundary is used.

- 1: The controller does not meet the AHB specification.

| 30.9.13 A  | CDIVIAC GIODAI Ch   | annel Read Wi | nte Suspend R | egister |       |      |      |  |

|------------|---------------------|---------------|---------------|---------|-------|------|------|--|

| Name: X    | XDMAC_GRWS          |               |               |         |       |      |      |  |

| Address: 0 | xF0010030 (0), 0xF0 | 0004030 (1)   |               |         |       |      |      |  |

| Access: V  | Vrite-only          |               |               |         |       |      |      |  |

| 31         | 30                  | 29            | 28            | 27      | 26    | 25   | 24   |  |

| -          | -                   | _             | _             | _       | _     | —    | —    |  |

| 23         | 22                  | 21            | 20            | 19      | 18    | 17   | 16   |  |

| _          | -                   | _             | -             | _       | _     | _    | -    |  |

| 15         | 14                  | 13            | 12            | 11      | 10    | 9    | 8    |  |

| RWS15      | RWS14               | RWS13         | RWS12         | RWS11   | RWS10 | RWS9 | RWS8 |  |

| 7          | 6                   | 5             | 4             | 3       | 2     | 1    | 0    |  |

| RWS7       | RWS6                | RWS5          | RWS4          | RWS3    | RWS2  | RWS1 | RWS0 |  |

## 38.9.13 XDMAC Global Channel Read Write Suspend Register

## RWSx: XDMAC Channel x Read Write Suspend Bit

0: No effect.

1: Read and write requests are suspended.

## 39.7.8 LCD Controller Enable Register

| Address: 0xF0 | C_LCDEN<br>0000020<br>e-only |    |    |       |        |        |       |

|---------------|------------------------------|----|----|-------|--------|--------|-------|

| 31            | 30                           | 29 | 28 | 27    | 26     | 25     | 24    |

| _             | _                            | _  | —  | _     | _      | _      | -     |

| 23            | 22                           | 21 | 20 | 19    | 18     | 17     | 16    |

| -             | -                            | _  | _  | _     | _      | -      | -     |

| 15            | 14                           | 13 | 12 | 11    | 10     | 9      | 8     |

| -             | -                            | -  | -  | -     | -      | -      | -     |

| 7             | 6                            | 5  | 4  | 3     | 2      | 1      | 0     |

| -             | -                            | _  | _  | PWMEN | DISPEN | SYNCEN | CLKEN |

#### **CLKEN: LCD Controller Pixel Clock Enable**

0: No effect

1: Pixel clock logical unit is activated.

## SYNCEN: LCD Controller Horizontal and Vertical Synchronization Enable

0: No effect

1: Both horizontal and vertical synchronization (LCDVSYNC and LCDHSYNC) signals are generated.

## **DISPEN: LCD Controller DISP Signal Enable**

0: No effect

1: LCDDISP signal is generated.

## **PWMEN: LCD Controller Pulse Width Modulation Enable**

0: No effect

1: PWM is enabled.

| Address: 0xF0 | 000016C<br>d/Write |         |        |    |    |    |      |

|---------------|--------------------|---------|--------|----|----|----|------|

| 31            | 30                 | 29      | 28     | 27 | 26 | 25 | 24   |

| -             | -                  | -       | -      | -  | _  | -  | -    |

| 23            | 22                 | 21      | 20     | 19 | 18 | 17 | 16   |

| —             | -                  | -       | -      | -  | -  | -  | -    |

| 15            | 14                 | 13      | 12     | 11 | 10 | 9  | 8    |

| -             | -                  | LOCKDIS | ROTDIS | —  | _  | -  | DLBO |

| 7             | 6                  | 5       | 4      | 3  | 2  | 1  | 0    |

| _             | -                  | BLE     | EN     | _  | _  | _  | SIF  |

## 39.7.45 Overlay 1 Configuration Register 0

LCDC\_OVR1CEG0

#### SIF: Source Interface

Name:

0: Base Layer data is retrieved through AHB interface 0.

1: Base Layer data is retrieved through AHB interface 1.

#### **BLEN: AHB Burst Length**

| Value | Name            | Description                                                                                                                                                                                                                           |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | AHB_BLEN_SINGLE | AHB Access is started as soon as there is enough space in the FIFO to store one data. SINGLE, INCR, INCR4, INCR8 and INCR16 bursts are used. INCR is used for a burst of 2 and 3 beats.                                               |

| 1     | AHB_BLEN_INCR4  | AHB Access is started as soon as there is enough space in the FIFO to store a total amount of 4 data. An AHB INCR4 Burst is used. SINGLE, INCR and INCR4 bursts are used. INCR is used for a burst of 2 and 3 beats.                  |

| 2     | AHB_BLEN_INCR8  | AHB Access is started as soon as there is enough space in the FIFO to store a total amount of 8 data. An AHB INCR8 Burst is used. SINGLE, INCR, INCR4 and INCR8 bursts are used. INCR is used for a burst of 2 and 3 beats.           |

| 3     | AHB_BLEN_INCR16 | AHB Access is started as soon as there is enough space in the FIFO to store a total amount of 16 data. An AHB INCR16 Burst is used. SINGLE, INCR, INCR4, INCR8 and INCR16 bursts are used. INCR is used for a burst of 2 and 3 beats. |

## DLBO: Defined Length Burst Only for Channel Bus Transaction

0: Undefined length INCR burst is used for a burst of 2 and 3 beats.

1: Only Defined Length burst is used (SINGLE, INCR4, INCR8 and INCR16).

#### **ROTDIS: Hardware Rotation Optimization Disable**

- 0: Rotation optimization is enabled.

- 1: Rotation optimization is disabled.

## LOCKDIS: Hardware Rotation Lock Disable

- 0: AHB lock signal is asserted when a rotation is performed.

- 1: AHB lock signal is cleared when a rotation is performed.

| 40.8.69  | GMAC Frames Received Register |    |    |    |    |    |    |  |

|----------|-------------------------------|----|----|----|----|----|----|--|

| Name:    | GMAC_FR                       |    |    |    |    |    |    |  |

| Address: | 0xF8008158                    |    |    |    |    |    |    |  |

| Access:  | Read-only                     |    |    |    |    |    |    |  |

| 31       | 30                            | 29 | 28 | 27 | 26 | 25 | 24 |  |

|          | FRX                           |    |    |    |    |    |    |  |

| 23       | 22                            | 21 | 20 | 19 | 18 | 17 | 16 |  |

|          |                               |    | FF | RX |    |    |    |  |

| 15       | 14                            | 13 | 12 | 11 | 10 | 9  | 8  |  |

|          |                               |    | FF | RX |    |    |    |  |

| 7        | 6                             | 5  | 4  | 3  | 2  | 1  | 0  |  |

|          |                               |    | FF | RX |    |    |    |  |

## FRX: Frames Received without Error

Frames received without error. This register counts the number of frames successfully received. Excludes pause frames, and is only incremented if the frame is successfully filtered and copied to memory.

## 43.7.10 CLASSD Write Protection Mode Register

| Name:    | CLASSD_WPMR |       |     |     |    |    |      |  |  |

|----------|-------------|-------|-----|-----|----|----|------|--|--|

| Address: | 0xFC0480E4  |       |     |     |    |    |      |  |  |

| Access:  | Read/Write  |       |     |     |    |    |      |  |  |

| 31       | 30          | 29    | 28  | 27  | 26 | 25 | 24   |  |  |

|          |             | WPKEY |     |     |    |    |      |  |  |

| 23       | 22          | 21    | 20  | 19  | 18 | 17 | 16   |  |  |

|          |             |       | WPI | KEY |    |    |      |  |  |

| 15       | 14          | 13    | 12  | 11  | 10 | 9  | 8    |  |  |

|          |             |       | WPI | KEY |    |    |      |  |  |

| 7        | 6           | 5     | 4   | 3   | 2  | 1  | 0    |  |  |

| -        | -           | -     | —   | —   | -  | -  | WPEN |  |  |

## **WPEN: Write Protection Enable**

0: Disables the write protection if WPKEY corresponds to 0x434C44 ("CLD" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x434C44 ("CLD" in ASCII).

See Section 43.6.7 "Register Write Protection" for the list of registers that can be write-protected.

## **WPKEY: Write Protection Key**

| Value           | Name    | Description                                                                       |  |  |  |  |

|-----------------|---------|-----------------------------------------------------------------------------------|--|--|--|--|

| 0x434C44 PASSWD |         | Writing any other value in this field aborts the write operation of the WPEN bit. |  |  |  |  |

| 0,434044        | FASSVID | Always reads as 0.                                                                |  |  |  |  |

## **RXFPTEF: Receive FIFO Pointer Error Flag**

0: No Receive FIFO pointer occurred

1: Receive FIFO pointer error occurred. Receiver must be reset

See Section 47.7.11.9 "FIFO Pointer Error" for details.

## **TXFLOCK: Transmit FIFO Lock**

0: The Transmit FIFO is not locked.

1: The Transmit FIFO is locked.

## RXFTHF2: Receive FIFO Threshold Flag 2 (cleared by writing the FLEX\_US\_CR.RSTSTA bit)

0: Number of unread data in Receive FIFO is above RXFTHRES threshold.

1: Number of unread data in Receive FIFO has reached RXFTHRES2 threshold since the last RSTSTA command was issued.

## 49.8.9 SPI Interrupt Enable Register

Name: SPI\_IER

Address: 0xF8000014 (0), 0xFC000014 (1)

Access: Write-only

| 31      | 30      | 29     | 28    | 27    | 26     | 25      | 24    |

|---------|---------|--------|-------|-------|--------|---------|-------|

| RXFPTEF | TXFPTEF | RXFTHF | RXFFF | RXFEF | TXFTHF | TXFFF   | TXFEF |

| 23      | 22      | 21     | 20    | 19    | 18     | 17      | 16    |

| _       | -       | -      | Ι     | -     | —      | -       | _     |

| 15      | 14      | 13     | 12    | 11    | 10     | 9       | 8     |

| _       | -       | -      | Ι     | CMP   | UNDES  | TXEMPTY | NSSR  |

| 7       | 6       | 5      | 4     | 3     | 2      | 1       | 0     |

| -       | -       | -      | -     | OVRES | MODF   | TDRE    | RDRF  |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Enables the corresponding interrupt.

RDRF: Receive Data Register Full Interrupt Enable

#### **TDRE: SPI Transmit Data Register Empty Interrupt Enable**

MODF: Mode Fault Error Interrupt Enable

**OVRES: Overrun Error Interrupt Enable**

**NSSR: NSS Rising Interrupt Enable**

**TXEMPTY: Transmission Registers Empty Enable**

**UNDES: Underrun Error Interrupt Enable**

**CMP: Comparison Interrupt Enable**

**TXFEF: TXFEF Interrupt Enable**

**TXFFF: TXFFF Interrupt Enable**

**TXFTHF: TXFTHF Interrupt Enable**

**RXFEF: RXFEF Interrupt Enable**

**RXFFF: RXFFF Interrupt Enable**

**RXFTHF: RXFTHF Interrupt Enable**

**TXFPTEF: TXFPTEF Interrupt Enable**

**RXFPTEF: RXFPTEF Interrupt Enable**

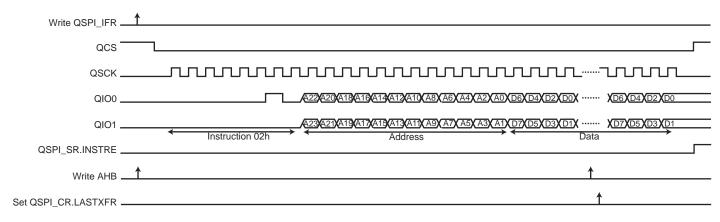

## Example 5:

Instruction in Single-bit SPI, with address in Dual SPI, without option, with data write in Dual SPI.

Command: BYTE/PAGE PROGRAM (02h)

- Write 0x0000\_0002 in QSPI\_ICR.

- Write 0x0000\_30B3 in QSPI\_IFR.

- Read QSPI\_IFR (dummy read) to synchronize system bus accesses.

- Write data in the QSPI system bus memory space (0x9000\_00000-0x9800\_00000/0XD000\_0000-0XD800\_0000). The address of the first system bus write accesss is sent in the instruction frame. The address of the next system bus write accesses is not used.

- Write a '1' to QSPI\_CR.LASTXFR.

- Wait for QSPI\_SR.INSTRE to rise.

#### Figure 50-15: Instruction Transmission Waveform 5

## Table 52-18: Register Mapping (Continued)

| Offset | Register            | Name             | Access    | Reset     |

|--------|---------------------|------------------|-----------|-----------|

| 0x410  | Histogram Entry 0   | ISC_HIS_ENTRY0   | Read-only | 0x0000000 |

|        |                     |                  |           |           |

| 0xBFC  | Histogram Entry 511 | ISC_HIS_ENTRY511 | Read-only | 0x0000000 |

| 52.6.36  | ISC Color Space Conversion YB OY Register |    |     |     |     |       |    |

|----------|-------------------------------------------|----|-----|-----|-----|-------|----|

| Name:    | ISC_CSC_YB_OY                             |    |     |     |     |       |    |

| Address: | 0xF00083A0                                |    |     |     |     |       |    |

| Access:  | Read/Write                                |    |     |     |     |       |    |

| 31       | 30                                        | 29 | 28  | 27  | 26  | 25    | 24 |

| _        | _                                         | _  | _   | _   |     | YOFST |    |

| 23       | 22                                        | 21 | 20  | 19  | 18  | 17    | 16 |

|          |                                           |    | YOI | -ST |     |       |    |

| 15       | 14                                        | 13 | 12  | 11  | 10  | 9     | 8  |

| -        | -                                         | -  | -   |     | YBG | AIN   |    |

| 7        | 6                                         | 5  | 4   | 3   | 2   | 1     | 0  |

|          | YBGAIN                                    |    |     |     |     |       |    |

## YBGAIN: Blue Gain for Luminance Component (12 bits signed 1:3:8)

YOFST: Luminance Offset (11 bits signed 1:10:0)

#### FDOE: CAN FD Operation Enable (read/write, write protection)

0 (DISABLED): FD operation disabled.

1 (ENABLED): FD operation enabled.

#### BRSE: Bit Rate Switching Enable (read/write, write protection)

0 (DISABLED): Bit rate switching for transmissions disabled.

1 (ENABLED): Bit rate switching for transmissions enabled.

#### PXHD: Protocol Exception Event Handling (read/write, write protection)

0: Protocol exception handling enabled.

1: Protocol exception handling disabled.

#### EFBI: Edge Filtering during Bus Integration (read/write, write protection)

0: Edge filtering is disabled.

1: Edge filtering is enabled. Two consecutive dominant tq required to detect an edge for hard synchronization.

#### TXP: Transmit Pause (read/write, write protection)

If this bit is set, the MCAN pauses for two CAN bit times before starting the next transmission after itself has successfully transmitted a frame (see Section 53.5.5).

0: Transmit pause disabled.

1: Transmit pause enabled.

## 53.6.44 MCAN Transmit Buffer Cancellation Finished Interrupt Enable

| 31       |      | 30               | 29          | 28 |  |

|----------|------|------------------|-------------|----|--|

| Access:  | Read | I/Write          |             |    |  |

| Address: | 0xF8 | 0540E4 (0), 0xF0 | C0500E4 (1) |    |  |

| Name:    | MCA  | N_TXBCIE         |             |    |  |

| 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CFIE31 | CFIE30 | CFIE29 | CFIE28 | CFIE27 | CFIE26 | CFIE25 | CFIE24 |

| 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

| CFIE23 | CFIE22 | CFIE21 | CFIE20 | CFIE19 | CFIE18 | CFIE17 | CFIE16 |

| 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |

| CFIE15 | CFIE14 | CFIE13 | CFIE12 | CFIE11 | CFIE10 | CFIE9  | CFIE8  |

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| CFIE7  | CFIE6  | CFIE5  | CFIE4  | CFIE3  | CFIE2  | CFIE1  | CFIE0  |

## CFIEx: Cancellation Finished Interrupt Enable for Transmit Buffer x

Each Transmit Buffer has its own Cancellation Finished Interrupt Enable bit.

0: Cancellation finished interrupt disabled.

1: Cancellation finished interrupt enabled.

| 56.7.10  | PWM DMA Register |          |     |      |    |    |    |  |

|----------|------------------|----------|-----|------|----|----|----|--|

| Name:    | PWM_DMAR         | PWM_DMAR |     |      |    |    |    |  |

| Address: | 0xF802C024       |          |     |      |    |    |    |  |

| Access:  | Write- only      |          |     |      |    |    |    |  |

| 31       | 30               | 29       | 28  | 27   | 26 | 25 | 24 |  |

| -        | -                | -        | -   | -    | -  | —  | -  |  |

| 23       | 22               | 21       | 20  | 19   | 18 | 17 | 16 |  |

|          | DMADUTY          |          |     |      |    |    |    |  |

| 15       | 14               | 13       | 12  | 11   | 10 | 9  | 8  |  |

|          |                  |          | DMA | DUTY |    |    |    |  |

| 7        | 6                | 5        | 4   | 3    | 2  | 1  | 0  |  |

|          | DMADUTY          |          |     |      |    |    |    |  |

Only the first 16 bits (channel counter size) are significant.

#### DMADUTY: Duty-Cycle Holding Register for DMA Access

Each write access to PWM\_DMAR sequentially updates the CDTY field of PWM\_CDTYx with DMADUTY (only for channel configured as synchronous). See "Method 3: Automatic write of duty-cycle values and automatic trigger of the update".

5. Write the data to be encrypted/decrypted in the authorized Input Data Registers (refer to Table 59-2).

|                | 5                             |

|----------------|-------------------------------|

| Operating Mode | Input Data Registers to Write |

| ECB            | All                           |

| CBC            | All                           |

| CTR            | All                           |

Table 59-2:

Authorized Input Data Registers

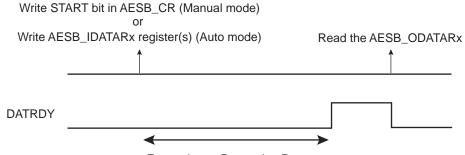

6. Set the START bit in the AESB Control Register (AESB\_CR) to begin the encryption or decryption process.

7. When processing is complete, the DATRDY bit in the AESB Interrupt Status Register (AESB\_ISR) raises. If an interrupt has been enabled by setting the DATRDY bit in AESB\_IER, the interrupt line of the AESB is activated.

8. When the software reads one of the Output Data Registers (AESB\_ODATARx), the AESB\_ISR.DATRDY bit is automatically cleared.

#### 59.3.3.2 Auto Mode

Auto mode is similar to Manual mode, except that in Auto mode, as soon as the correct number of Input Data registers is written, processing starts automatically without any action in the Control Register.

#### 59.3.4 Last Output Data Mode

Last Output Data mode is used to generate cryptographic checksums on data (MAC) by means of a cipher block chaining encryption algorithm (the CBC-MAC algorithm for example).

After each end of encryption/decryption, the output data are available on the output data registers for Manual and Auto modes.

The Last Output Data (LOD) bit in AESB\_MR allows retrieval of only the last data of several encryption/decryption processes.

Those data are only available on the Output Data Registers (AESB\_ODATARx).

#### 59.3.5 Manual and Auto Modes

#### 59.3.5.1 If AESB\_MR.LOD = 0

The AESB\_ISR.DATRDY bit is cleared when at least one of the Output Data Registers is read (refer to Figure 59-1).

## Figure 59-1: Manual and Auto Modes with AESB\_MR.LOD = 0

Encryption or Decryption Process

If the user does not want to read the output data registers between each encryption/decryption, the AESB\_ISR.DATRDY bit will not be cleared. If the AESB\_ISR.DATRDY bit is not cleared, the user cannot know the end of the following encryptions/decryptions.

#### 59.3.5.2 If AESB\_MR.LOD = 1

The AESB\_ISR.DATRDY bit is cleared when at least one Input Data Register is written, so before the start of a new transfer (refer to Figure 59-2). No more Output Data Register reads are necessary between consecutive encryptions/decryptions.

| 60.5.18<br>Name:<br>Address:<br>Access: | AES Byte Counter Register<br>AES_BCNT<br>0xF002C0B4<br>Read/Write |    |    |    |    |    |    |

|-----------------------------------------|-------------------------------------------------------------------|----|----|----|----|----|----|

| 31                                      | 30                                                                | 29 | 28 | 27 | 26 | 25 | 24 |

|                                         | BCNT                                                              |    |    |    |    |    |    |

| 23                                      | 22                                                                | 21 | 20 | 19 | 18 | 17 | 16 |

|                                         |                                                                   |    | BC | NT |    |    |    |

| 15                                      | 14                                                                | 13 | 12 | 11 | 10 | 9  | 8  |

|                                         | BCNT                                                              |    |    |    |    |    |    |

| 7                                       | 6                                                                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                                         |                                                                   |    | BC | NT |    |    |    |

## **BCNT: Auto Padding Byte Counter**

Auto padding byte counter value. BCNT must be greater than 0.

| Signal Name | <b>Recommended Pin Connection</b>                               | Description                                                                          |  |  |  |  |

|-------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| VDDFUSE     | 2.25V to 2.75V                                                  | Powers the fuse box for programming.                                                 |  |  |  |  |

| VDDF03E     | Decoupling capacitor (100 nF) <sup>(1)(2)</sup>                 | VDDFUSE must not be left floating.                                                   |  |  |  |  |

| VDDAUDIOPLL | 3.0V to 3.6V<br>Decoupling capacitor (100 nF) <sup>(1)(2)</sup> | Powers the Audio PLL.                                                                |  |  |  |  |

|             |                                                                 | GNDCORE pins are common to VDDCORE pins.                                             |  |  |  |  |

| GNDCORE     | Core Chip ground                                                | GNDCORE pins should be connected as shortly as possible to the system ground plane.  |  |  |  |  |

|             |                                                                 | GNDPLL pin is provided for VDDPLLA pins.                                             |  |  |  |  |

| GNDPLLA     | PLLA cell ground                                                | GNDPLL pin should be connected as shortly as possible to the system ground plane.    |  |  |  |  |

| GNDIODDR    | DDR2/LPDDR1/LPDDR2/DDR3/LPDDR3<br>interface I/O lines ground    | GNDIODDR pins should be connected as shortly as possible to the system ground plane. |  |  |  |  |

|             |                                                                 | GNDISC pins are common to VDDISC pins.                                               |  |  |  |  |

| GNDISC      | VDDISC ground                                                   | GNDISC pins should be connected as shortly as possible to the system ground plane.   |  |  |  |  |

|             |                                                                 | GNDIOPx pins are common to VDDIOPx pins.                                             |  |  |  |  |

| GNDIOP0,1,2 | Peripherals and ISC I/O lines ground                            | GNDIOP pins should be connected as shortly as possible to the system ground plane.   |  |  |  |  |

|             |                                                                 | GNDBU pin is provided for VDDBU pins.                                                |  |  |  |  |

| GNDBU       | Backup ground                                                   | GNDBU pin should be connected as shortly as possible to the system ground plane.     |  |  |  |  |

|             |                                                                 | GNDUTMIC pins are common to VDDUTMIC and VDDHSIC pins.                               |  |  |  |  |

| GNDUTMIC    | VDDUTMIC and VDDHSIC ground                                     | GNDUTMIC pins should be connected as shortly as possible to the system ground plane. |  |  |  |  |

|             | UDPHS and UHPHS UTMI+ Core and                                  | GNDUTMII pins are common to VDDUTMII and VDDUTMIC pins.                              |  |  |  |  |

| GNDUTMII    | Interface, and PLL UTMI ground                                  | GNDUTMII pins should be connected as shortly as possible to the system ground plane. |  |  |  |  |

|             |                                                                 | GNDOSC pin is provided for VDDOSC pins.                                              |  |  |  |  |

| GNDOSC      | Oscillator ground                                               | GNDOSC pin should be connected as shortly as possible to the system ground plane.    |  |  |  |  |

|             |                                                                 | SDMMC pins are common to VDDSDMMC pins.                                              |  |  |  |  |

| GNDSDMMC    | SDMMC ground                                                    | GNDSDMMC pins should be connected as shortly as possible to the system ground plane. |  |  |  |  |

|             |                                                                 | GNDANA pins are common to VDDANA pins.                                               |  |  |  |  |

| GNDANA      | Analog ground                                                   | GNDANA pins should be connected as shortly as possible to the system ground plane.   |  |  |  |  |

|             |                                                                 | GNDFUSE pins are common to VDDFUSE pins.                                             |  |  |  |  |

| GNDFUSE     | Fuse box ground                                                 | GNDFUSE pins should be connected as shortly as possible to the system ground plane.  |  |  |  |  |

## Table 68-1: Power Supply Connections (Continued)