Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                        |

| Number of I/O              | 140                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | ·                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 201-UFBGA                                                                           |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f427igh7               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Peripherals                   |                                  | STM32F427<br>Vx | STM32F429Vx                 | STM32F427<br>Zx | STM32F429Zx      | STM32F427<br>Ax | STM32F429<br>Ax  | STM32F427<br>Ix              | STM32F429lx      | STM32F429Bx | STM32F429N |

|-------------------------------|----------------------------------|-----------------|-----------------------------|-----------------|------------------|-----------------|------------------|------------------------------|------------------|-------------|------------|

| SPI / I <sup>2</sup> S        |                                  | 4/2 (ful        | l duplex) <sup>(2)</sup>    |                 |                  |                 | 6/2              | (full duplex) <sup>(2)</sup> |                  |             |            |

|                               | l <sup>2</sup> C                 |                 |                             | •               |                  |                 | 3                |                              |                  |             |            |

|                               | USART/<br>UART                   |                 |                             |                 |                  |                 | 4/4              |                              |                  |             |            |

| Communication interfaces      | USB OTG<br>FS                    |                 | Yes                         |                 |                  |                 |                  |                              |                  |             |            |

| Interfaces                    | USB OTG<br>HS                    |                 | Yes                         |                 |                  |                 |                  |                              |                  |             |            |

|                               | CAN                              |                 | 2                           |                 |                  |                 |                  |                              |                  |             |            |

|                               | SAI                              |                 | 1                           |                 |                  |                 |                  |                              |                  |             |            |

|                               | SDIO                             | Yes             |                             |                 |                  |                 |                  |                              |                  |             |            |

| Camera interface              | 9                                |                 |                             |                 |                  |                 | Yes              |                              |                  |             |            |

| LCD-TFT (STM3<br>only)        | 2F429xx                          | No              | Yes                         | No              | Yes              | No              | Yes              | No                           |                  | Yes         |            |

| Chrom-ART Acc                 | elerator™                        |                 |                             |                 |                  |                 | Yes              |                              |                  |             |            |

| GPIOs                         |                                  | 82              |                             | 114             |                  | 130             |                  |                              | 140 168          |             | 58         |

| 12-bit ADC                    |                                  |                 | 3                           |                 |                  |                 |                  |                              |                  |             |            |

| Number of chanr               | nels                             |                 | 16 24                       |                 |                  |                 |                  |                              |                  |             |            |

| 12-bit DAC<br>Number of chanr | 12-bit DAC<br>Number of channels |                 | Yes<br>2                    |                 |                  |                 |                  |                              |                  |             |            |

| Maximum CPU frequency         |                                  | 180 MHz         |                             |                 |                  |                 |                  |                              |                  |             |            |

| Operating voltag              | Operating voltage                |                 | 1.8 to 3.6 V <sup>(3)</sup> |                 |                  |                 |                  |                              |                  |             |            |

| Operating tempe               | raturos                          |                 |                             |                 | Ambient te       | emperatures: -  | 40 to +85 °C /-  | 40 to +105 °C                |                  |             |            |

|                               | aures                            |                 |                             |                 | Ju               | nction tempera  | ture: -40 to + 1 | 125 °C                       |                  |             |            |

| Packages                      |                                  | LQ              | FP100                       |                 | CSP143<br>0FP144 | UFBO            | GA169            |                              | BGA176<br>QFP176 | LQFP208     | TFBGA216   |

#### Table 2. STM32F427xx and STM32F429xx features and peripheral counts (continued)

For the LQFP100 package, only FMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package. For UFBGA169 package, only SDRAM, NAND and multiplexed static memories are supported.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

16/238

3. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

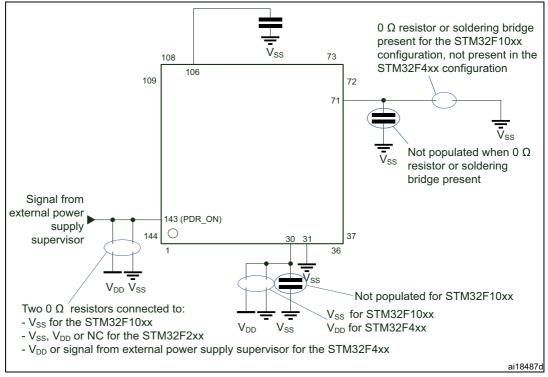

# Figure 2. Compatible board design between STM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package

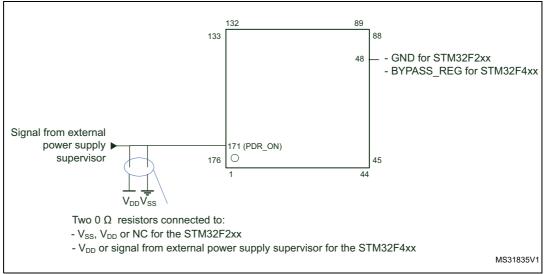

Figure 3. Compatible board design between STM32F2xx and STM32F4xx for LQFP176 and UFBGA176 packages

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

# 3.20 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

## Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

## • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup).

| Voltage regulator<br>configuration      | Main regulator (MR) | Low-power regulator (LPR) |

|-----------------------------------------|---------------------|---------------------------|

| Normal mode                             | MR ON               | LPR ON                    |

| Under-drive mode MR in under-drive mode |                     | LPR in under-drive mode   |

## Table 5. Voltage regulator modes in stop mode

### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

| Symbol                               | Ratings                                                                                 | Max.   | Unit |

|--------------------------------------|-----------------------------------------------------------------------------------------|--------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>            | 270    |      |

| $\Sigma I_{VSS}$                     | SS Total current out of sum of all V <sub>SS_x</sub> ground lines (sink) <sup>(1)</sup> |        |      |

| I <sub>VDD</sub>                     | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>          | 100    |      |

| I <sub>VSS</sub>                     | Maximum current out of each $V_{SS_x}$ ground line (sink) <sup>(1)</sup>                | - 100  |      |

| 1                                    | Output current sunk by any I/O and control pin                                          | 25     |      |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/Os and control pin                                      | - 25   |      |

| ΣI                                   | Total output current sunk by sum of all I/O and control pins <sup>(2)</sup>             | 120    | mA   |

| $\Sigma I_{IO}$                      | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup>         | - 120  |      |

|                                      | Injected current on FT pins <sup>(4)</sup>                                              | 5/10   |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on NRST and BOOT0 pins <sup>(4)</sup>                                  | - 5/+0 |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                             | ±5     |      |

| $\Sigma I_{\rm INJ(PIN)}^{(5)}$      | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                 | ±25    |      |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.21: 12-bit ADC characteristics.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. A positive injection is induced by  $V_{IN} > V_{DDA}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 14* for the values of the maximum allowed input voltage.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 16. Thermal characteristics

| Symbol           | Ratings                      | Value        | Unit |

|------------------|------------------------------|--------------|------|

| T <sub>STG</sub> | Storage temperature range    | – 65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125          | °C   |

|                      |                                                       |                                                               | Typ <sup>(1)</sup> |                              |                            |                           |                           |                            |      |  |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------|--------------------|------------------------------|----------------------------|---------------------------|---------------------------|----------------------------|------|--|

| Symbol               | Parameter                                             | arameter Conditions                                           |                    | tions T <sub>A</sub> = 25 °C |                            | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|                      |                                                       |                                                               |                    | V <sub>DD</sub> =<br>2.4 V   | V <sub>DD</sub> =<br>3.3 V | v                         | <sub>DD</sub> = 3.6       | v                          |      |  |

|                      | Backup SRAM ON, low-speed oscillator (LSE) and RTC ON | 2.80                                                          | 3.00               | 3.60                         | 7.00                       | 19.00                     | 36.00                     |                            |      |  |

| I <sub>DD_STBY</sub> | Supply current                                        | Backup SRAM OFF, low-<br>speed oscillator (LSE) and<br>RTC ON | 2.30               | 2.60                         | 3.10                       | 6.00                      | 16.00                     | 31.00                      | μA   |  |

| mode                 | mode                                                  | Backup SRAM ON, RTC and LSE OFF                               | 2.30               | 2.50                         | 2.90                       | 6.00 <sup>(3)</sup>       | 18.00 <sup>(3)</sup>      | 35.00 <sup>(3)</sup>       |      |  |

|                      |                                                       | Backup SRAM OFF, RTC and LSE OFF                              | 1.70               | 1.90                         | 2.20                       | 5.00 <sup>(3)</sup>       | 15.00 <sup>(3)</sup>      | 30.00 <sup>(3)</sup>       |      |  |

## Table 28. Typical and maximum current consumptions in Standby mode

The typical current consumption values are given with PDR OFF (internal reset OFF). When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2 μA.

2. Based on characterization, not tested in production unless otherwise specified.

3. Based on characterization, tested in production.

## Table 29. Typical and maximum current consumptions in $\mathrm{V}_{\mathrm{BAT}}$ mode

|                                               |                                     |                                                        |      | Тур                         |                                                             |                    | Max <sup>(2)</sup> |      |  |

|-----------------------------------------------|-------------------------------------|--------------------------------------------------------|------|-----------------------------|-------------------------------------------------------------|--------------------|--------------------|------|--|

| Symbol                                        | Parameter Conditions <sup>(1)</sup> |                                                        | т    | a = 25 °                    | 5 °C $T_A = 85 °C \begin{bmatrix} T_A \\ 105 \end{bmatrix}$ |                    |                    | Unit |  |

|                                               |                                     |                                                        |      | V <sub>BAT</sub> =<br>2.4 V | V <sub>BAT</sub> =<br>3.3 V                                 | V <sub>BAT</sub> = | = 3.6 V            |      |  |

|                                               |                                     | Backup SRAM ON, low-speed oscillator (LSE) and RTC ON  | 1.28 | 1.40                        | 1.62                                                        | 6                  | 11                 |      |  |

|                                               | Backup                              | Backup SRAM OFF, low-speed oscillator (LSE) and RTC ON | 0.66 | 0.76                        | 0.97                                                        | 3                  | 5                  | μA   |  |

| I <sub>DD_VBAT</sub> domain supply<br>current | Backup SRAM ON, RTC and LSE OFF     | 0.70                                                   | 0.72 | 0.74                        | 5                                                           | 10                 | μΛ                 |      |  |

|                                               |                                     | Backup SRAM OFF, RTC and LSE OFF                       | 0.10 | 0.10                        | 0.10                                                        | 2                  | 4                  |      |  |

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a  $C_L$  of 6 pF for typical values.

2. Guaranteed by characterization results.

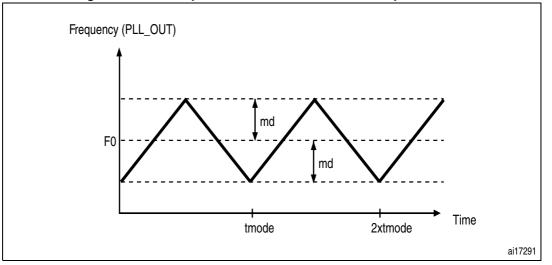

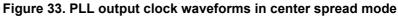

*Figure 33* and *Figure 34* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

$T_{mode}$  is the modulation period.

md is the modulation depth.

Figure 34. PLL output clock waveforms in down spread mode

# 6.3.16 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

## Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of – 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 55.

|                  |                                                                                                              | Functional s       |                    |      |

|------------------|--------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                  | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                |                    | NA                 |      |

|                  | Injected current on NRST pin                                                                                 | - 0                | NA                 |      |

| I <sub>INJ</sub> | Injected current on PA0, PA1, PA2, PA3, PA6, PA7, PB0, PC0, PC1, PC2, PC3, PC4, PC5, PH1, PH2, PH3, PH4, PH5 | - 0                | NA                 | mA   |

|                  | Injected current on TTa pins: PA4 and PA5                                                                    | - 0                | +5                 |      |

|                  | Injected current on any other FT pin                                                                         | - 5                | NA                 |      |

# Table 55. I/O current injection susceptibility<sup>(1)</sup>

1. NA = not applicable.

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

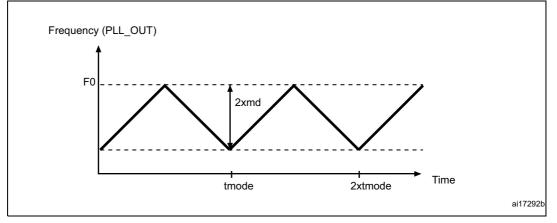

Figure 35. FT I/O input characteristics

# **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14, PC15 and PI8 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 and PI8 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15*).

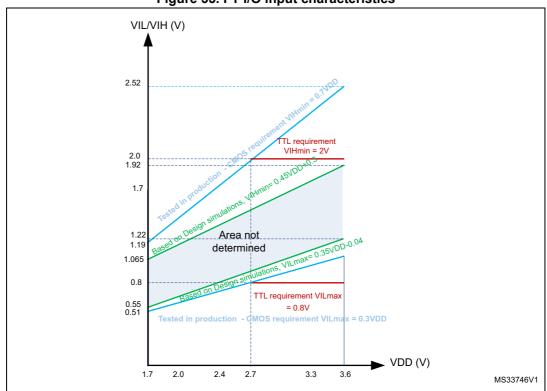

#### 6.3.18 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 56: I/O static characteristics).

Unless otherwise specified, the parameters given in Table 59 are derived from tests performed under the ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 17.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       |                         | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 59. NRST pin characteristics

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order). 1

#### 2. Guaranteed by design.

#### Figure 37. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

- 2. The external capacitor must be placed as close as possible to the device.

- 3. The user must ensure that the level on the NRST pin can go below the VIL(NRST) max level specified in Table 59. Otherwise the reset is not taken into account by the device.

ai14132c

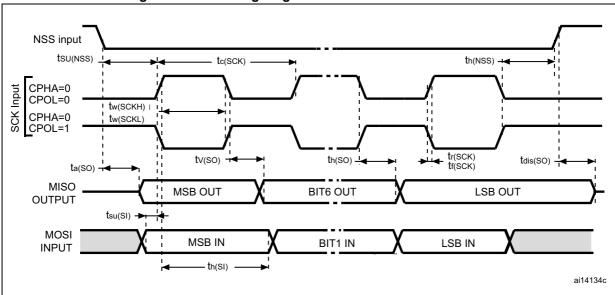

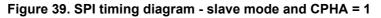

Figure 38. SPI timing diagram - slave mode and CPHA = 0

# **SAI characteristics**

Unless otherwise specified, the parameters given in *Table 64* for SAI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and VDD supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C=30 pF

- Measurement points are performed at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (SCK,SD,WS).

| Symbol                                         | Parameter                      | Conditions                             | Min      | Мах                   | Unit  |

|------------------------------------------------|--------------------------------|----------------------------------------|----------|-----------------------|-------|

| f <sub>MCKL</sub>                              | SAI Main clock output          | -                                      | 256 x 8K | 256xFs <sup>(2)</sup> | MHz   |

| E                                              | SAL clock frequency            | Master data: 32 bits                   | -        | 64xFs                 | MHz   |

| F <sub>SCK</sub>                               | SAI clock frequency            | Slave data: 32 bits                    | -        | 64xFs                 | IVITZ |

| D <sub>SCK</sub>                               | SAI clock frequency duty cycle | Slave receiver                         | 30       | 70                    | %     |

| t <sub>v(FS)</sub>                             | FS valid time                  | Master mode                            | 8        | 22                    |       |

| t <sub>su(FS)</sub>                            | FS setup time                  | Slave mode                             | 2        | -                     |       |

| 4                                              | FS hold time                   | Master mode                            | 8        | -                     |       |

| t <sub>h(FS)</sub>                             | FS hold little                 | Slave mode                             | 0        | -                     |       |

| t <sub>su(SD_MR)</sub>                         | Data innut actus tima          | Master receiver                        | 5        | -                     |       |

| t <sub>su(SD_SR)</sub>                         | Data input setup time          | Slave receiver                         | 3        | -                     |       |

| t <sub>h(SD_MR)</sub>                          | Data input hold time           | Master receiver                        | 0        | -                     | ns    |

| t <sub>h(SD_SR)</sub>                          | Data input hold time           | Slave receiver                         | 0        | -                     |       |

| t <sub>v(SD_ST)</sub><br>t <sub>h(SD_ST)</sub> | Data output valid time         | Slave transmitter (after enable edge)  | -        | 22                    |       |

| t <sub>v(SD_MT)</sub>                          |                                | Master transmitter (after enable edge) | -        | 20                    |       |

| t <sub>h(SD_MT)</sub>                          | Data output hold time          | Master transmitter (after enable edge) | 8        | -                     |       |

| Table 64 | I. SAI | characteristics <sup>(1)</sup> |

|----------|--------|--------------------------------|

|----------|--------|--------------------------------|

1. Guaranteed by characterization results.

2. 256xFs maximum corresponds to 45 MHz (APB2 xaximum frequency)

|                             | (0011010                                 |                        |     |      |

|-----------------------------|------------------------------------------|------------------------|-----|------|

| Symbol                      | Parameter Min                            |                        | Max | Unit |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | 0                      | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                      | 0   | ns   |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                      | 2.5 | ns   |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | 0                      | -   | ns   |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 4                      |     |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 0                      |     |      |

## Table 97. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

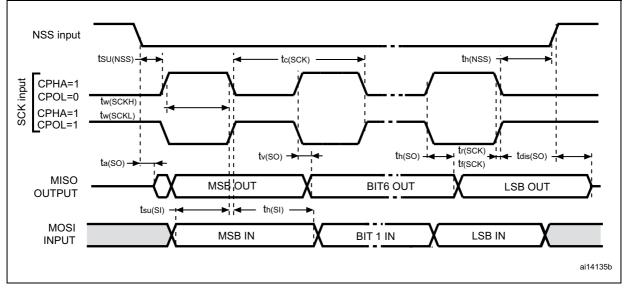

## PC Card/CompactFlash controller waveforms and timings

*Figure 63* through *Figure 68* represent synchronous waveforms, and *Table 98* and *Table 99* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x04;

- COM.FMC\_WaitSetupTime = 0x07;

- COM.FMC\_HoldSetupTime = 0x04;

- COM.FMC\_HiZSetupTime = 0x00;

- ATT.FMC\_SetupTime = 0x04;

- ATT.FMC\_WaitSetupTime = 0x07;

- ATT.FMC\_HoldSetupTime = 0x04;

- ATT.FMC\_HiZSetupTime = 0x00;

- IO.FMC\_SetupTime = 0x04;

- IO.FMC WaitSetupTime = 0x07;

- IO.FMC\_HoldSetupTime = 0x04;

- IO.FMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period.

Figure 68. PC Card/CompactFlash controller waveforms for I/O space write access

Table 98. Switching characteristics for PC Card/CF read and write cycles in attribute/common space  $^{(1)(2)}$

| Symbol                    | Parameter                                  | Min                       | Мах                      | Unit |

|---------------------------|--------------------------------------------|---------------------------|--------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FMC_Ncex low to FMC_Ay valid               | -                         | 0                        | ns   |

| t <sub>h(NCEx_AI)</sub>   | FMC_NCEx high to FMC_Ax invalid            | 0                         | -                        | ns   |

| t <sub>d(NREG-NCEx)</sub> | FMC_NCEx low to FMC_NREG valid             | -                         | 1                        | ns   |

| t <sub>h(NCEx-NREG)</sub> | FMC_NCEx high to FMC_NREG invalid          | T <sub>HCLK</sub> – 2     | -                        | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FMC_NCEx low to FMC_NWE low                | -                         | 5T <sub>HCLK</sub>       | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low width                          | 8T <sub>HCLK</sub> – 0.5  | 8T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>d(NWE_NCEx)</sub>  | FMC_NWE high to FMC_NCEx high              | 5T <sub>HCLK</sub> +1     | -                        | ns   |

| t <sub>V(NWE-D)</sub>     | FMC_NWE low to FMC_D[15:0] valid           | -                         | 0                        | ns   |

| t <sub>h(NWE-D)</sub>     | FMC_NWE high to FMC_D[15:0] invalid        | 9T <sub>HCLK</sub> – 0.5  | -                        | ns   |

| t <sub>d(D-NWE)</sub>     | FMC_D[15:0] valid before FMC_NWE high      | 13T <sub>HCLK</sub> – 3   |                          | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FMC_NCEx low to FMC_NOE low                | -                         | 5T <sub>HCLK</sub>       | ns   |

| t <sub>w(NOE)</sub>       | FMC_NOE low width                          | 8 T <sub>HCLK</sub> – 0.5 | 8 T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FMC_NOE high to FMC_NCEx high              | 5T <sub>HCLK</sub> – 1    | -                        | ns   |

| t <sub>su (D-NOE)</sub>   | FMC_D[15:0] valid data before FMC_NOE high | T <sub>HCLK</sub>         | -                        | ns   |

| t <sub>h(NOE-D)</sub>     | FMC_NOE high to FMC_D[15:0] invalid        | 0                         | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

| Table 99. Switching characteristics for PC Card/CF read and write cycles |  |

|--------------------------------------------------------------------------|--|

| in I/O space <sup>(1)(2)</sup>                                           |  |

| Symbol           | Parameter                               | Min                      | Мах                     | Unit |

|------------------|-----------------------------------------|--------------------------|-------------------------|------|

| tw(NIOWR)        | FMC_NIOWR low width                     | 8T <sub>HCLK</sub> – 0.5 | -                       | ns   |

| tv(NIOWR-D)      | FMC_NIOWR low to FMC_D[15:0] valid      | -                        | 0                       | ns   |

| th(NIOWR-D)      | FMC_NIOWR high to FMC_D[15:0] invalid   | 9T <sub>HCLK</sub> – 2   | -                       | ns   |

| td(NCE4_1-NIOWR) | FMC_NCE4_1 low to FMC_NIOWR valid       | -                        | 5T <sub>HCLK</sub>      | ns   |

| th(NCEx-NIOWR)   | FMC_NCEx high to FMC_NIOWR invalid      | 5T <sub>HCLK</sub>       | -                       | ns   |

| td(NIORD-NCEx)   | FMC_NCEx low to FMC_NIORD valid         | -                        | 5T <sub>HCLK</sub>      | ns   |

| th(NCEx-NIORD)   | FMC_NCEx high to FMC_NIORD) valid       | 6T <sub>HCLK</sub> +2    | -                       | ns   |

| tw(NIORD)        | FMC_NIORD low width                     | 8T <sub>HCLK</sub> – 0.5 | 8T <sub>HCLK</sub> +0.5 | ns   |

| tsu(D-NIORD)     | FMC_D[15:0] valid before FMC_NIORD high | T <sub>HCLK</sub>        | -                       | ns   |

| td(NIORD-D)      | FMC_D[15:0] valid after FMC_NIORD high  | 0                        | _                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

## NAND controller waveforms and timings

*Figure 69* through *Figure 72* represent synchronous waveforms, and *Table 100* and *Table 101* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC\_HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC\_WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |  |  |

|-------------------------------|------------------------|--------------------------|-------------------------|------|--|--|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |  |  |

| t <sub>d(SDCLKL_Data</sub> )  | Data output valid time | -                        | 3.5                     |      |  |  |

| t <sub>h(SDCLKL</sub> _Data)  | Data output hold time  | 0                        | -                       |      |  |  |

| $t_{d(SDCLKL_Add)}$           | Address valid time     | -                        | 1.5                     |      |  |  |

| t <sub>d(SDCLKL_SDNWE)</sub>  | SDNWE valid time       | -                        | 1                       |      |  |  |

| t <sub>h(SDCLKL_SDNWE)</sub>  | SDNWE hold time        | 0                        | -                       |      |  |  |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 0.5                     | ns   |  |  |

| t <sub>h(SDCLKLSDNE)</sub>    | Chip select hold time  | 0                        | -                       | 115  |  |  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 2                       |      |  |  |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                       |      |  |  |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 0.5                     |      |  |  |

| td(SDCLKL_SDNCAS)             | SDNCAS hold time       | 0                        | -                       |      |  |  |

| t <sub>d(SDCLKL_NBL)</sub>    | NBL valid time         | -                        | 0.5                     |      |  |  |

| t <sub>h(SDCLKL_NBL)</sub>    | NBLoutput time         | 0                        | -                       |      |  |  |

# Table 104. SDRAM write timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

# Table 105. LPSDR SDRAM write timings<sup>(1)(2)</sup>

| Symbol                                         | Parameter              | Min                      | Мах                     | Unit |

|------------------------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>                          | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL_Data</sub> )                   | Data output valid time | -                        | 5                       |      |

| t <sub>h(SDCLKL</sub> _Data)                   | Data output hold time  | 2                        | -                       |      |

| t <sub>d(SDCLKL_Add)</sub>                     | Address valid time     | -                        | 2.8                     |      |

| t <sub>d(SDCLKL-SDNWE)</sub>                   | SDNWE valid time       | -                        | 2                       |      |

| t <sub>h(SDCLKL-SDNWE)</sub>                   | SDNWE hold time        | 1                        | -                       |      |

| t <sub>d(SDCLKL</sub> - SDNE)                  | Chip select valid time | -                        | 1.5                     |      |

| t <sub>h(SDCLKL</sub> - SDNE)                  | Chip select hold time  | 1                        | -                       | ns   |

| td(SDCLKL-SDNRAS)                              | SDNRAS valid time      | -                        | 1.5                     |      |

| t <sub>h(SDCLKL-SDNRAS)</sub>                  | SDNRAS hold time       | 1.5                      | -                       |      |

| td(SDCLKL-SDNCAS)                              | SDNCAS valid time      | -                        | 1.5                     |      |

| t <sub>d(SDCLKL-SDNCAS)</sub> SDNCAS hold time |                        | 1.5                      | -                       |      |

| $t_{d(SDCLKL_NBL)}$                            | NBL valid time         | -                        | 1.5                     | ]    |

| t <sub>h(SDCLKL-NBL)</sub>                     | NBL output time        | 1.5                      | -                       |      |

1. CL = 10 pF.

2. Guaranteed by characterization results.

| Symbol            |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |

|-------------------|-------|-------------|-------|--------|-----------------------|--------|--|--|

| Symbol            | Min   | Тур         | Max   | Min    | Тур                   | Max    |  |  |

| A                 | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.0230 |  |  |

| A1                | 0.155 | 0.175       | 0.195 | -      | 0.0069                | -      |  |  |

| A2                | -     | 0.380       | -     | -      | 0.0150                | -      |  |  |

| A3 <sup>(2)</sup> | -     | 0.025       | -     | -      | 0.0010                | -      |  |  |

| b <sup>(3)</sup>  | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |  |  |

| D                 | 4.486 | 4.521       | 4.556 | 0.1766 | 0.1780                | 0.1794 |  |  |

| E                 | 5.512 | 5.547       | 5.582 | 0.2170 | 0.2184                | 0.2198 |  |  |

| е                 | -     | 0.400       | -     | -      | 0.0157                | -      |  |  |

| e1                | -     | 4.000       | -     | -      | 0.1575                | -      |  |  |

| e2                | -     | 4.800       | -     | -      | 0.1890                | -      |  |  |

| F                 | -     | 0.2605      | -     | -      | 0.0103                | -      |  |  |

| G                 | -     | 0.3735      | -     | -      | 0.0147                | -      |  |  |

| aaa               | -     | -           | 0.100 | -      | -                     | 0.0039 |  |  |

| bbb               | -     | -           | 0.100 | -      | -                     | 0.0039 |  |  |

| CCC               | -     | -           | 0.100 | -      | -                     | 0.0039 |  |  |

| ddd               | -     | -           | 0.050 | -      | -                     | 0.0020 |  |  |

| eee               | -     | -           | 0.050 | -      | -                     | 0.0020 |  |  |

# Table 111. WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

# Figure 84. WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale recommended footprint

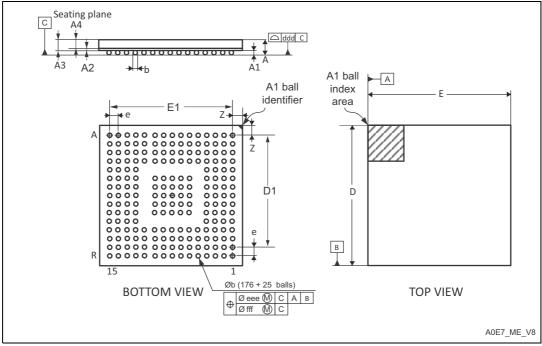

# 7.7 UFBGA176+25 package information

Figure 98. UFBGA176+25 - ball 10 x 10 mm, 0.65 mm pitch ultra thin fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 118. UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch, |

|-----------------------------------------------------------|

| ultra fine pitch ball grid array package mechanical data  |

| Gumbal | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | Min.        | Тур.   | Max.   | Min.                  | Тур.   | Max.   |  |

| А      | -           | -      | 0.600  | -                     | -      | 0.0236 |  |

| A1     | -           | -      | 0.110  | -                     | -      | 0.0043 |  |

| A2     | -           | 0.130  | -      | -                     | 0.0051 | -      |  |

| A3     | -           | 0.450  | -      | -                     | 0.0177 | -      |  |

| A4     | -           | 0.320  | -      | -                     | 0.0126 | -      |  |

| b      | 0.240       | 0.290  | 0.340  | 0.0094                | 0.0114 | 0.0134 |  |

| D      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| D1     | -           | 9.100  | -      | -                     | 0.3583 | -      |  |

| E      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| E1     | -           | 9.100  | -      | -                     | 0.3583 | -      |  |

| е      | -           | 0.650  | -      | -                     | 0.0256 | -      |  |

| Z      | -           | 0.450  | -      | -                     | 0.0177 | -      |  |

| ddd    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

# 8 Part numbering

| Table 122. Ordering inform                                              | mation sc | heme |         |   |       |

|-------------------------------------------------------------------------|-----------|------|---------|---|-------|

| Example:                                                                | STM32     | F    | 429 V I | Т | 6 xxx |

| Device family                                                           |           |      |         |   |       |

| STM32 = ARM-based 32-bit microcontroller                                |           |      |         |   |       |

| Product type                                                            |           |      |         |   |       |

| F = general-purpose                                                     |           |      |         |   |       |

| Device subfamily                                                        |           |      |         |   |       |

| 427= STM32F427xx, USB OTG FS/HS, camera interface, Ethernet             |           |      |         |   |       |

| 429= STM32F429xx, USB OTG FS/HS, camera interface,<br>Ethernet, LCD-TFT |           |      |         |   |       |

| Pin count                                                               |           |      |         |   |       |

| V = 100 pins                                                            |           |      |         |   |       |

| Z = 143 and 144 pins                                                    |           |      |         |   |       |

| A = 169 pins                                                            |           |      |         |   |       |

| I = 176 pins                                                            |           |      |         |   |       |

| B = 208 pins                                                            |           |      |         |   |       |

| N = 216 pins                                                            |           |      |         |   |       |

| Flash memory size                                                       |           |      |         |   |       |

| E = 512 Kbytes of Flash memory                                          |           |      |         |   |       |

| G = 1024 Kbytes of Flash memory                                         |           |      |         |   |       |

| I = 2048 Kbytes of Flash memory                                         |           |      |         |   |       |

| Package                                                                 |           |      |         |   |       |

| T = LQFP                                                                |           |      |         |   |       |

| H = BGA                                                                 |           |      |         |   |       |

| Y = WLCSP                                                               |           |      |         |   |       |

| Temperature range                                                       |           |      |         |   |       |

| 6 = Industrial temperature range, -40 to 85 °C.                         |           |      |         |   | _     |

| 7 = Industrial temperature range, -40 to 105 °C.                        |           |      |         |   |       |

| Options                                                                 |           |      |         |   |       |

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID024030 Rev 9

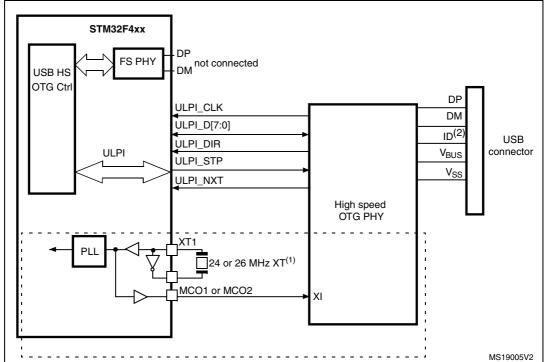

# B.2 USB OTG high speed (HS) interface solutions

Figure 106. USB controller configured as peripheral, host, or dual-mode and used in high speed mode

It is possible to use MCO1 or MCO2 to save a crystal. It is however not mandatory to clock the STM32F42x with a 24 or 26 MHz crystal when using USB HS. The above figure only shows an example of a possible connection.

<sup>2.</sup> The ID pin is required in dual role only.

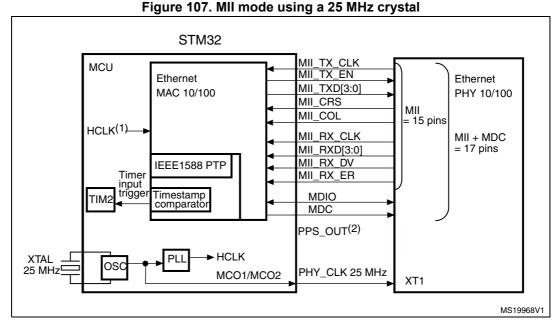

# **B.3** Ethernet interface solutions

1.  $f_{HCLK}$  must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

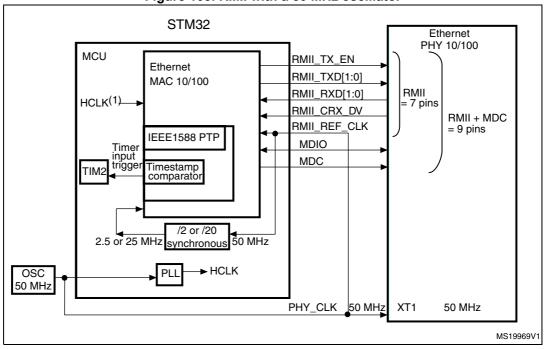

#### Figure 108. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.