## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                        |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f427vgt7               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 90.  | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint    | . 210 |

|-------------|------------------------------------------------------------------------------|-------|

| Figure 91.  | LQFP176 marking (package top view)                                           | . 211 |

| Figure 92.  | LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package outline          | . 212 |

| Figure 93.  | LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package                  |       |

| 0           | recommended footprint.                                                       | . 214 |

| Figure 94.  | LQFP208 marking example (package top view)                                   |       |

| Figure 95.  | UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid array |       |

|             | package outline                                                              | . 216 |

| Figure 96.  | UFBGA169 - 169-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch               |       |

| U           | ball grid array recommended footprint                                        | . 217 |

| Figure 97.  | UFBGA169 marking example (package top view)                                  |       |

| Figure 98.  | UFBGA176+25 - ball 10 x 10 mm, 0.65 mm pitch ultra thin fine pitch           |       |

| -           | ball grid array package outline                                              | . 219 |

| Figure 99.  | UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch                |       |

|             | ball grid array package recommended footprint                                | . 220 |

| Figure 100. | UFBGA176+25 marking example (package top view)                               |       |

| Figure 101. | TFBGA216 - 216 ball 13 × 13 mm 0.8 mm pitch thin fine pitch                  |       |

| -           | ball grid array package outline                                              | . 222 |

| Figure 102. | TFBGA176 marking example (package top view)                                  |       |

| Figure 103. | USB controller configured as peripheral-only and used                        |       |

|             | in Full speed mode                                                           | . 227 |

| Figure 104. | USB controller configured as host-only and used in full speed mode           | . 227 |

| Figure 105. | USB controller configured in dual mode and used in full speed mode           | . 228 |

| Figure 106. | USB controller configured as peripheral, host, or dual-mode                  |       |

| -           | and used in high speed mode                                                  | . 229 |

| Figure 107. | MII mode using a 25 MHz crystal                                              | . 230 |

|             | RMII with a 50 MHz oscillator                                                |       |

|             | RMII with a 25 MHz crystal and PHY with PLL                                  |       |

## 1 Introduction

This datasheet provides the description of the STM32F427xx and STM32F429xx line of microcontrollers. For more details on the whole STMicroelectronics STM32 family, please refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F427xx and STM32F429xx datasheet should be read in conjunction with the STM32F4xx reference manual.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214), available from *www.st.com*.

## 2.1 Full compatibility throughout the family

The STM32F427xx and STM32F429xx devices are part of the STM32F4 family. They are fully pin-to-pin, software and feature compatible with the STM32F2xx devices, allowing the user to try different memory densities, peripherals, and performances (FPU, higher frequency) for a greater degree of freedom during the development cycle.

The STM32F427xx and STM32F429xx devices maintain a close compatibility with the whole STM32F10xx family. All functional pins are pin-to-pin compatible. The STM32F427xx and STM32F429xx, however, are not drop-in replacements for the STM32F10xx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xx to the STM32F42x family remains simple as only a few pins are impacted.

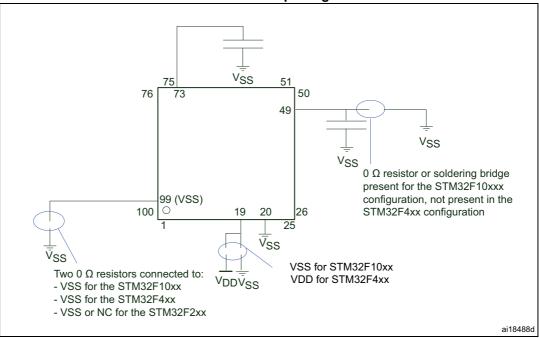

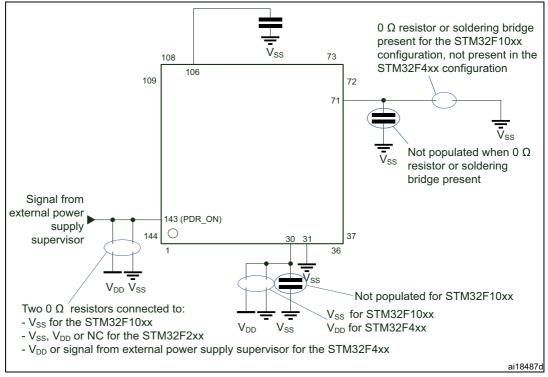

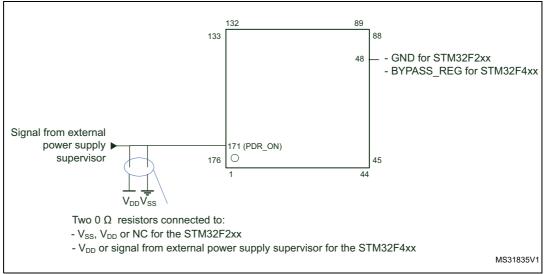

*Figure 1*, *Figure 2*, and *Figure 3*, give compatible board designs between the STM32F4xx, STM32F2xx, and STM32F10xx families.

Figure 1. Compatible board design STM32F10xx/STM32F2xx/STM32F4xx for LQFP100 package

## Figure 2. Compatible board design between STM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package

Figure 3. Compatible board design between STM32F2xx and STM32F4xx for LQFP176 and UFBGA176 packages

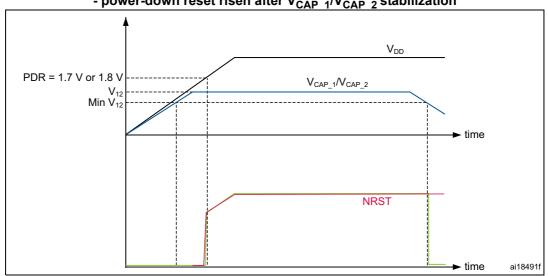

Figure 9. Startup in regulator OFF: slow  $V_{DD}$  slope - power-down reset risen after  $V_{CAP}$   $_1/V_{CAP}$   $_2$  stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

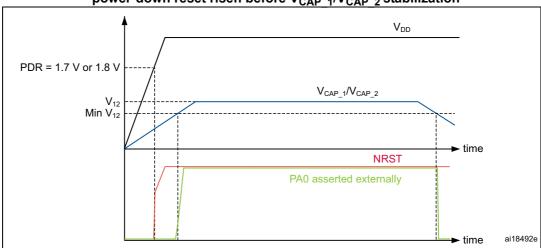

Figure 10. Startup in regulator OFF mode: fast V<sub>DD</sub> slope - power-down reset risen before  $V_{CAP_1}/V_{CAP_2}$  stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

## 3.22.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

## 3.22.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.22.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

## 3.23 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the standard (up to 100 KHz), and fast (up to 400 KHz) modes. They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see *Table 7*).

|                                     | Analog filter | Digital filter                                            |

|-------------------------------------|---------------|-----------------------------------------------------------|

| Pulse width of<br>suppressed spikes | 2 30 08       | Programmable length from 1 to 15<br>I2C peripheral clocks |

### Table 7. Comparison of I2C analog and digital filters

# 3.24 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and four universal asynchronous receiver transmitters (UART4, UART5, UART7, and UART8).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to

## 3.26 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available. They can be operated in master or slave mode, in full duplex and simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

Note: For I2S2 full-duplex mode, I2S2\_CK and I2S2\_WS signals can be used only on GPIO Port B and GPIO Port D.

## 3.27 Serial Audio interface (SAI1)

The serial audio interface (SAI1) is based on two independent audio sub-blocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both sub-blocks can be configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

SAI1 can be served by the DMA controller.

## 3.28 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S/SAI flow with an external PLL (or Codec output).

## 3.29 Audio and LCD PLL(PLLSAI)

An additional PLL dedicated to audio and LCD-TFT is used for SAI1 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the LCD-TFT clock.

|         |         |           | Pin nı   |         |          |         |          |                                                      |          |                 |       |                                                                               |                         |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                           | Additional<br>functions |

| -       | 10      | F2        | E2       | 16      | F11      | 16      | D2       | PF0                                                  | I/O      | FT              | -     | I2C2_SDA, FMC_A0,<br>EVENTOUT                                                 | -                       |

| -       | 11      | F3        | H3       | 17      | E9       | 17      | E2       | PF1                                                  | I/O      | FT              | -     | I2C2_SCL, FMC_A1,<br>EVENTOUT                                                 | -                       |

| -       | 12      | G5        | H2       | 18      | F10      | 18      | G2       | PF2                                                  | I/O      | FT              | -     | I2C2_SMBA, FMC_A2,<br>EVENTOUT                                                | -                       |

| -       | -       | -         | -        | -       | -        | 19      | E3       | PI12                                                 | I/O      | FT              | -     | LCD_HSYNC,<br>EVENTOUT                                                        | -                       |

| -       | -       | -         | -        | -       | -        | 20      | G3       | PI13                                                 | I/O      | FT              | -     | LCD_VSYNC,<br>EVENTOUT                                                        | -                       |

| -       | -       | -         | -        | -       | -        | 21      | H3       | PI14                                                 | I/O      | FT              |       | LCD_CLK, EVENTOUT                                                             | -                       |

| -       | 13      | G4        | J2       | 19      | G11      | 22      | H2       | PF3                                                  | I/O      | FT              | (5)   | FMC_A3, EVENTOUT                                                              | ADC3_IN9                |

| -       | 14      | G3        | J3       | 20      | F9       | 23      | J2       | PF4                                                  | I/O      | FT              | (5)   | FMC_A4, EVENTOUT                                                              | ADC3_<br>IN14           |

| -       | 15      | H3        | K3       | 21      | F8       | 24      | K3       | PF5                                                  | I/O      | FT              | (5)   | FMC_A5, EVENTOUT                                                              | ADC3_<br>IN15           |

| 10      | 16      | G7        | G2       | 22      | H7       | 25      | H6       | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                             | -                       |

| 11      | 17      | G8        | G3       | 23      | -        | 26      | H5       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                             | -                       |

| -       | 18      | NC<br>(2) | K2       | 24      | G10      | 27      | K2       | PF6                                                  | I/O      | FT              | (5)   | TIM10_CH1,<br>SPI5_NSS,<br>SAI1_SD_B,<br>UART7_Rx,<br>FMC_NIORD,<br>EVENTOUT  | ADC3_IN4                |

| -       | 19      | NC<br>(2) | K1       | 25      | F7       | 28      | K1       | PF7                                                  | I/O      | FT              | (5)   | TIM11_CH1,<br>SPI5_SCK,<br>SAI1_MCLK_B,<br>UART7_Tx,<br>FMC_NREG,<br>EVENTOUT | ADC3_IN5                |

| -       | 20      | NC<br>(2) | L3       | 26      | H11      | 29      | L3       | PF8                                                  | I/O      | FT              | (5)   | SPI5_MISO,<br>SAI1_SCK_B,<br>TIM13_CH1,<br>FMC_NIOWR,<br>EVENTOUT             | ADC3_IN6                |

| Table 10. STM32F427xx and STM32F429xx pin an | nd ball definitions (con | tinued) |

|----------------------------------------------|--------------------------|---------|

|----------------------------------------------|--------------------------|---------|

|         | Pin number |          |          |         |          |         |          |                                                      |          | ,               |       |                                                                                                                     |                             |

|---------|------------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|

| LQFP100 | LQFP144    | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                                 | Additional<br>functions     |

| -       | -          | M1       | L4       | 48      | N11      | -       | L5       | BYPASS_<br>REG                                       | Ι        | FT              | -     | -                                                                                                                   | -                           |

| 28      | 39         | J11      | K4       | 49      | J8       | 52      | K5       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| 29      | 40         | N2       | N4       | 50      | M10      | 53      | N4       | PA4                                                  | I/O      | ТТа             | (5)   | SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK,<br>OTG_HS_SOF,<br>DCMI_HSYNC,<br>LCD_VSYNC,<br>EVENTOUT                | ADC12_<br>IN4 /DAC_<br>OUT1 |

| 30      | 41         | М3       | P4       | 51      | M9       | 54      | P4       | PA5                                                  | I/O      | ТТа             | (5)   | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK,<br>OTG_HS_ULPI_CK,<br>EVENTOUT                                        | ADC12_<br>IN5/DAC_<br>OUT2  |

| 31      | 42         | N3       | P3       | 52      | N10      | 55      | P3       | PA6                                                  | I/O      | FT              | (5)   | TIM1_BKIN,<br>TIM3_CH1,<br>TIM8_BKIN,<br>SPI1_MISO,<br>TIM13_CH1,<br>DCMI_PIXCLK,<br>LCD_G2, EVENTOUT               | ADC12_<br>IN6               |

| 32      | 43         | K4       | R3       | 53      | L8       | 56      | R3       | PA7                                                  | I/O      | FT              | (5)   | TIM1_CH1N,<br>TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI,<br>TIM14_CH1,<br>ETH_MII_RX_DV/ETH_<br>RMII_CRS_DV,<br>EVENTOUT | ADC12_<br>IN7               |

| 33      | 44         | L4       | N5       | 54      | M8       | 57      | N5       | PC4                                                  | I/O      | FT              | (5)   | ETH_MII_RXD0/ETH_<br>RMII_RXD0,<br>EVENTOUT                                                                         | ADC12_<br>IN14              |

| 34      | 45         | M4       | P5       | 55      | N9       | 58      | P5       | PC5                                                  | I/O      | FT              | (5)   | ETH_MII_RXD1/ETH_<br>RMII_RXD1,<br>EVENTOUT                                                                         | ADC12_<br>IN15              |

| -       | -          | -        | -        | -       | J7       | 59      | L7       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| -       | -          | -        | -        | -       | -        | 60      | L6       | VSS                                                  | S        | -               | -     | -                                                                                                                   | -                           |

| Table 10. | STM32F427xx and | STM32F429xx pir | n and ball de | efinitions (continued) | ) |

|-----------|-----------------|-----------------|---------------|------------------------|---|

|           |                 |                 |               |                        | £ |

#### Pinouts and pin description

- 4. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F4xx reference manual, available from the STMicroelectronics website: www.st.com.

- 5. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- If the device is delivered in an WLCSP143, UFBGA169, UFBGA176, LQFP176 or TFBGA216 package, and the BYPASS\_REG pin is set to V<sub>DD</sub> (Regulator OFF/internal reset ON mode), then PA0 is used as an internal Reset (active low).

- 7. PI0 and PI1 cannot be used for I2S2 full-duplex mode.

- 8. The DCMI\_VSYNC alternate function on PG9 is only available on silicon revision 3.

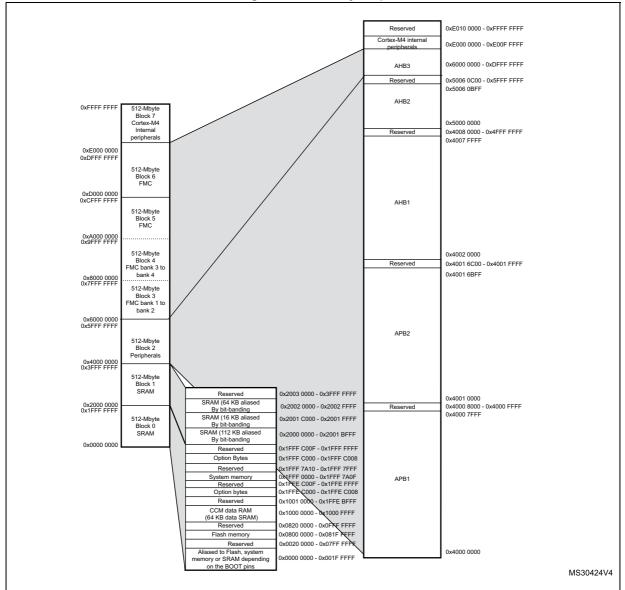

## 5 Memory mapping

The memory map is shown in *Figure 19*.

Figure 19. Memory map

| Bus       | Boundary address          | Peripheral                     |

|-----------|---------------------------|--------------------------------|

|           | 0xE00F FFFF - 0xFFFF FFFF | Reserved                       |

| Cortex-M4 | 0xE000 0000 - 0xE00F FFFF | Cortex-M4 internal peripherals |

|           | 0xD000 0000 - 0xDFFF FFFF | FMC bank 6                     |

|           | 0xC000 0000 - 0xCFFF FFFF | FMC bank 5                     |

|           | 0xA000 1000 - 0xBFFF FFFF | Reserved                       |

| AHB3      | 0xA000 0000- 0xA000 0FFF  | FMC control register           |

| АПЬЗ      | 0x9000 0000 - 0x9FFF FFFF | FMC bank 4                     |

|           | 0x8000 0000 - 0x8FFF FFFF | FMC bank 3                     |

|           | 0x7000 0000 - 0x7FFF FFFF | FMC bank 2                     |

|           | 0x6000 0000 - 0x6FFF FFFF | FMC bank 1                     |

|           | 0x5006 0C00- 0x5FFF FFFF  | Reserved                       |

|           | 0x5006 0800 - 0X5006 0BFF | RNG                            |

|           | 0x5005 0400 - X5006 07FF  | Reserved                       |

| AHB2      | 0x5005 0000 - 0X5005 03FF | DCMI                           |

|           | 0x5004 0000- 0x5004 FFFF  | Reserved                       |

|           | 0x5000 0000 - 0X5003 FFFF | USB OTG FS                     |

Table 13. STM32F427xx and STM32F429xx register boundary addresses

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

|      | 0x4008 0000- 0x4FFF FFFF  | Reserved                 |

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 BC00- 0x4003 FFFF  | Reserved                 |

|      | 0x4002 B000 - 0x4002 BBFF | DMA2D                    |

|      | 0x4002 9400 - 0x4002 AFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0X4002 5000 - 0X4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| АПВТ | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0X4002 3400 - 0X4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2C00 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2800 - 0x4002 2BFF | GPIOK                    |

|      | 0x4002 2400 - 0x4002 27FF | GPIOJ                    |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0X4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

## Table 13. STM32F427xx and STM32F429xx register boundary addresses (continued)

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 56: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 35: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DD</sub> is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

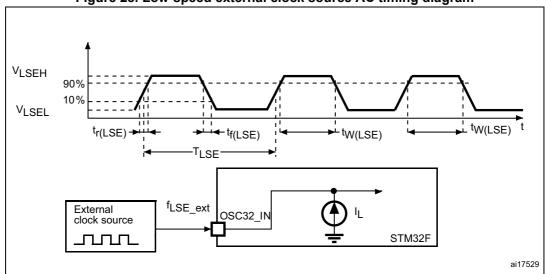

Figure 28. Low-speed external clock source AC timing diagram

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                             | Parameter                               | Conditions                                                            | Min   | Тур | Max | Unit |

|------------------------------------|-----------------------------------------|-----------------------------------------------------------------------|-------|-----|-----|------|

| f <sub>OSC_IN</sub>                | Oscillator frequency                    |                                                                       | 4     | -   | 26  | MHz  |

| R <sub>F</sub>                     | Feedback resistor                       |                                                                       | -     | 200 | -   | kΩ   |

| I                                  | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -     | 450 | -   | μA   |

| I <sub>DD</sub>                    | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -     | 530 | -   | μΑ   |

| ACC <sub>HSE</sub> <sup>(2)</sup>  | HSE accuracy                            |                                                                       | - 500 | -   | 500 | ppm  |

| G <sub>m</sub> _crit_max           | Maximum critical crystal g <sub>m</sub> | Startup                                                               | -     | -   | 1   | mA/V |

| t <sub>SU(HSE</sub> <sup>(3)</sup> | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -     | 2   | -   | ms   |

| Table 39. HSE 4-2 | 6 MHz oscillator | characteristics <sup>(1)</sup> |

|-------------------|------------------|--------------------------------|

|                   |                  | onaraotoriotioo                |

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. The minimum and maximum values must be respected to comply with USB standard specifications.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

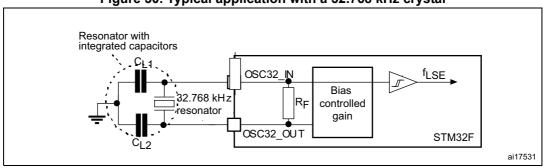

Figure 30. Typical application with a 32.768 kHz crystal

## 6.3.10 Internal clock source characteristics

The parameters given in *Table 41* and *Table 42* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                           | Conditions                           | Min | Тур | Max | Unit |  |  |

|-------------------------------------|-------------------------------------|--------------------------------------|-----|-----|-----|------|--|--|

| f <sub>HSI</sub>                    | Frequency                           | -                                    | -   | 16  | -   | MHz  |  |  |

|                                     | HSI user-trimming step (2)          | -                                    | -   | -   | 1   | %    |  |  |

|                                     | Accuracy of the HSI oscillator      | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |  |  |

| ACC <sub>HSI</sub>                  |                                     | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |  |  |

|                                     |                                     | $T_A = 25 \ ^{\circ}C^{(4)}$         | - 1 | -   | 1   | %    |  |  |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time         | -                                    | -   | 2.2 | 4   | μs   |  |  |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power<br>consumption | -                                    | -   | 60  | 80  | μA   |  |  |

Table 41. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

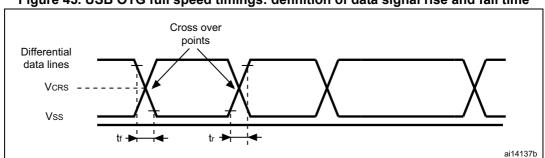

#### Figure 45. USB OTG full speed timings: definition of data signal rise and fall time

### Table 67. USB OTG full speed electrical characteristics<sup>(1)</sup>

| Driver characteristics |                                        |                                |                                      |     |      |  |  |

|------------------------|----------------------------------------|--------------------------------|--------------------------------------|-----|------|--|--|

| Symbol                 | Parameter                              | Conditions                     | Min                                  | Max | Unit |  |  |

| t <sub>r</sub>         | Rise time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4                                    | 20  | ns   |  |  |

| t <sub>f</sub>         | Fall time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4                                    | 20  | ns   |  |  |

| t <sub>rfm</sub>       | Rise/ fall time matching               | t <sub>r</sub> /t <sub>f</sub> | t <sub>r</sub> /t <sub>f</sub> 90 11 |     | %    |  |  |

| V <sub>CRS</sub>       | Output signal crossover voltage        |                                | 1.3                                  | 2.0 | V    |  |  |

| Z <sub>DRV</sub>       | Output driver impedance <sup>(3)</sup> | Driving high or<br>low         | 28                                   | 44  | Ω    |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on DP (D+) and DM (D-) pins since the matching impedance is included in the embedded driver.

## USB high speed (HS) characteristics

Unless otherwise specified, the parameters given in *Table 70* for ULPI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 69* and  $V_{DD}$  supply voltage conditions summarized in *Table 68*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10, unless otherwise specified

- Capacitive load C = 30 pF, unless otherwise specified

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

| Symbol      |                 | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |  |

|-------------|-----------------|------------------------------|---------------------|---------------------|------|--|--|

| Input level | V <sub>DD</sub> | USB OTG HS operating voltage | 1.7                 | 3.6                 | V    |  |  |

Table 68. USB HS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

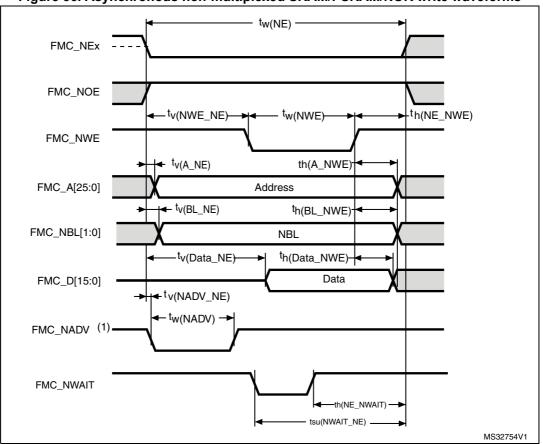

Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

|                          |                                       | · J-                          |                         |      |  |  |

|--------------------------|---------------------------------------|-------------------------------|-------------------------|------|--|--|

| Symbol                   | Parameter Min                         |                               | Max                     | Unit |  |  |

| t <sub>w(NE)</sub>       | FMC_NE low time                       | 3T <sub>HCLK</sub>            | 3T <sub>HCLK</sub> +1   | ns   |  |  |

| t <sub>v(NWE_NE)</sub>   | FMC_NEx low to FMC_NWE low            | E low T <sub>HCLK</sub> – 0.5 |                         | ns   |  |  |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                      | T <sub>HCLK</sub>             | T <sub>HCLK</sub> + 0.5 | ns   |  |  |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> +1.5        | -                       | ns   |  |  |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid            | -                             | 0                       | ns   |  |  |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> +0.5        | -                       | ns   |  |  |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid           | -                             | 1.5                     | ns   |  |  |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> +0.5        | -                       | ns   |  |  |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid     | -                             | T <sub>HCLK</sub> + 2   | ns   |  |  |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5        | -                       | ns   |  |  |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low           | -                             | 0.5                     | ns   |  |  |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                     | -                             | T <sub>HCLK</sub> + 0.5 | ns   |  |  |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

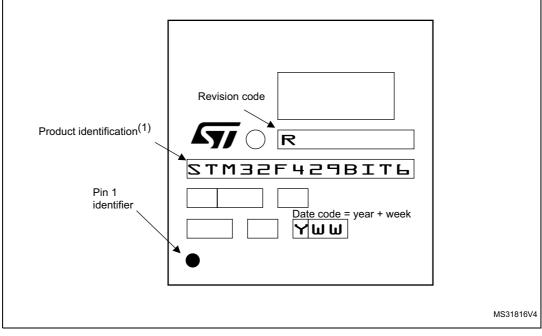

#### **Device marking for LQFP208**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID024030 Rev 9