#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                        |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | ·                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 144-LQFP                                                                            |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f427zgt6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction                                                          | 3 |

|---|-------|------------------------------------------------------------------|---|

| 2 | Desc  | ription                                                          | 4 |

|   | 2.1   | Full compatibility throughout the family1                        | 7 |

| 3 | Func  | tional overview                                                  | 0 |

|   | 3.1   | ARM <sup>®</sup> Cortex®-M4 with FPU and embedded Flash and SRAM | 0 |

|   | 3.2   | Adaptive real-time memory accelerator (ART Accelerator™) 20      | 0 |

|   | 3.3   | Memory protection unit 20                                        | 0 |

|   | 3.4   | Embedded Flash memory 2                                          | 1 |

|   | 3.5   | CRC (cyclic redundancy check) calculation unit                   | 1 |

|   | 3.6   | Embedded SRAM                                                    | 1 |

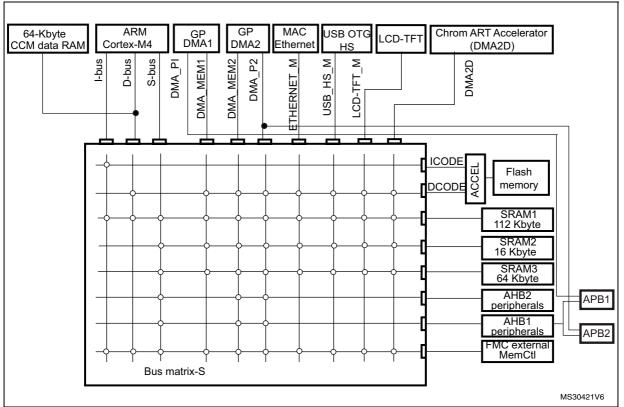

|   | 3.7   | Multi-AHB bus matrix                                             | 1 |

|   | 3.8   | DMA controller (DMA) 22                                          | 2 |

|   | 3.9   | Flexible memory controller (FMC) 23                              | 3 |

|   | 3.10  | LCD-TFT controller (available only on STM32F429xx)               | 3 |

|   | 3.11  | Chrom-ART Accelerator™ (DMA2D) 24                                | 4 |

|   | 3.12  | Nested vectored interrupt controller (NVIC) 24                   | 4 |

|   | 3.13  | External interrupt/event controller (EXTI) 24                    | 4 |

|   | 3.14  | Clocks and startup                                               | 4 |

|   | 3.15  | Boot modes                                                       | 5 |

|   | 3.16  | Power supply schemes                                             | 5 |

|   | 3.17  | Power supply supervisor                                          | 5 |

|   |       | 3.17.1 Internal reset ON                                         | 5 |

|   |       | 3.17.2 Internal reset OFF                                        | 6 |

|   | 3.18  | Voltage regulator                                                | 7 |

|   |       | 3.18.1 Regulator ON                                              |   |

|   |       | 3.18.2 Regulator OFF                                             |   |

|   |       | 3.18.3 Regulator ON/OFF and internal reset ON/OFF availability   |   |

|   | 3.19  | Real-time clock (RTC), backup SRAM and backup registers 3        | 1 |

|   | 3.20  | Low-power modes                                                  |   |

|   | 3.21  | V <sub>BAT</sub> operation                                       | 3 |

Figure 5. STM32F427xx and STM32F429xx Multi-AHB matrix

# 3.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDIO

- Camera interface (DCMI)

- ADC

- SAI1.

# **3.9** Flexible memory controller (FMC)

All devices embed an FMC. It has four Chip Select outputs supporting the following modes: PCCard/Compact Flash, SDRAM/LPSDR SDRAM, SRAM, PSRAM, NOR Flash and NAND Flash.

Functionality overview:

- 8-,16-, 32-bit data bus width

- Read FIFO for SDRAM controller

- Write FIFO

- Maximum FMC\_CLK/FMC\_SDCLK frequency for synchronous accesses is 90 MHz.

## LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

# 3.10 LCD-TFT controller (available only on STM32F429xx)

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 displays layers with dedicated FIFO (64x32-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 Input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events.

# 3.21 V<sub>BAT</sub> operation

The V<sub>BAT</sub> pin allows to power the device V<sub>BAT</sub> domain from an external battery, an external supercapacitor, or from V<sub>DD</sub> when no external battery and an external supercapacitor are present.

$V_{\text{BAT}}$  operation is activated when  $V_{\text{DD}}$  is not present.

The V<sub>BAT</sub> pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When PDR\_ON pin is not connected to  $V_{DD}$  (Internal Reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to VDD.

# 3.22 Timers and watchdogs

The devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

Table 6 compares the features of the advanced-control, general-purpose and basic timers.

## 3.22.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

## 3.22.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F42x devices (see *Table 6* for differences).

### • TIM2, TIM3, TIM4, TIM5

The STM32F42x include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

## 3.22.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

DocID024030 Rev 9

|         |         |           | Pin nu   | ımbei   | r        |         |          |                                                      |          |                 |            |                                                                                          |                              |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|------------|------------------------------------------------------------------------------------------|------------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes      | Alternate functions                                                                      | Additional<br>functions      |

| 4       | 4       | D1        | B2       | 4       | D9       | 4       | B1       | PE5                                                  | I/O      | FT              | -          | TRACED2, TIM9_CH1,<br>SPI4_MISO,<br>SAI1_SCK_A,<br>FMC_A21, DCMI_D6,<br>LCD_G0, EVENTOUT | -                            |

| 5       | 5       | D2        | В3       | 5       | E8       | 5       | B2       | PE6                                                  | I/O      | FT              | -          | TRACED3, TIM9_CH2,<br>SPI4_MOSI,<br>SAI1_SD_A, FMC_A22,<br>DCMI_D7, LCD_G1,<br>EVENTOUT  | -                            |

| -       | -       | -         | -        | -       | -        | -       | G6       | V <sub>SS</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | -         | -        | -       | -        | -       | F5       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| 6       | 6       | E5        | C1       | 6       | C11      | 6       | C1       | V <sub>BAT</sub>                                     | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | NC<br>(2) | D2       | 7       | -        | 7       | C2       | PI8                                                  | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | TAMP_2                       |

| 7       | 7       | E4        | D1       | 8       | D10      | 8       | D1       | PC13                                                 | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | TAMP_1                       |

| 8       | 8       | E1        | E1       | 9       | D11      | 9       | E1       | PC14-<br>OSC32_IN<br>(PC14)                          | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | OSC32_IN                     |

| 9       | 9       | F1        | F1       | 10      | E11      | 10      | F1       | PC15-<br>OSC32_OUT<br>(PC15)                         | I/O      | FT              | (3)<br>(4) | EVENTOUT                                                                                 | OSC32_<br>OUT <sup>(5)</sup> |

| -       | -       | -         | -        | -       | -        | -       | G5       | V <sub>DD</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | E2        | D3       | 11      | -        | 11      | E4       | PI9                                                  | I/O      | FT              | -          | CAN1_RX, FMC_D30,<br>LCD_VSYNC,<br>EVENTOUT                                              | -                            |

| -       | -       | E3        | E3       | 12      | -        | 12      | D5       | PI10                                                 | I/O      | FT              | -          | ETH_MII_RX_ER,<br>FMC_D31,<br>LCD_HSYNC,<br>EVENTOUT                                     | -                            |

| -       | -       | NC<br>(2) | E4       | 13      | -        | 13      | F3       | PI11                                                 | I/O      | FT              | -          | OTG_HS_ULPI_DIR,<br>EVENTOUT                                                             | -                            |

| -       | -       | F6        | F2       | 14      | E7       | 14      | F2       | V <sub>SS</sub>                                      | S        | -               | -          | -                                                                                        | -                            |

| -       | -       | F4        | F3       | 15      | E10      | 15      | F4       | $V_{DD}$                                             | S        | -               | -          | -                                                                                        | -                            |

| Table 10. | STM32F427xx and | STM32F429xx | pin and ball | definitions | (continued) |

|-----------|-----------------|-------------|--------------|-------------|-------------|

|           |                 |             |              |             |             |

| Pin name | CF  | Table 11. FMC<br>NOR/PSRAM/<br>SRAM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |

|----------|-----|-------------------------------------|------------------|--------|-------|

| PF0      | A0  | A0                                  |                  |        | A0    |

| PF1      | A1  | A1                                  |                  |        | A1    |

| PF2      | A2  | A2                                  |                  |        | A2    |

| PF3      | A3  | A3                                  |                  |        | A3    |

| PF4      | A4  | A4                                  |                  |        | A4    |

| PF5      | A5  | A5                                  |                  |        | A5    |

| PF12     | A6  | A6                                  |                  |        | A6    |

| PF13     | A7  | A7                                  |                  |        | A7    |

| PF14     | A8  | A8                                  |                  |        | A8    |

| PF15     | A9  | A9                                  |                  |        | A9    |

| PG0      | A10 | A10                                 |                  |        | A10   |

| PG1      |     | A11                                 |                  |        | A11   |

| PG2      |     | A12                                 |                  |        | A12   |

| PG3      |     | A13                                 |                  |        |       |

| PG4      |     | A14                                 |                  |        | BA0   |

| PG5      |     | A15                                 |                  |        | BA1   |

| PD11     |     | A16                                 | A16              | CLE    |       |

| PD12     |     | A17                                 | A17              | ALE    |       |

| PD13     |     | A18                                 | A18              |        |       |

| PE3      |     | A19                                 | A19              |        |       |

| PE4      |     | A20                                 | A20              |        |       |

| PE5      |     | A21                                 | A21              |        |       |

| PE6      |     | A22                                 | A22              |        |       |

| PE2      |     | A23                                 | A23              |        |       |

| PG13     |     | A24                                 | A24              |        |       |

| PG14     |     | A25                                 | A25              |        |       |

| PD14     | D0  | D0                                  | DA0              | D0     | D0    |

| PD15     | D1  | D1                                  | DA1              | D1     | D1    |

| PD0      | D2  | D2                                  | DA2              | D2     | D2    |

| PD1      | D3  | D3                                  | DA3              | D3     | D3    |

| PE7      | D4  | D4                                  | DA4              | D4     | D4    |

| PE8      | D5  | D5                                  | DA5              | D5     | D5    |

| PE9      | D6  | D6                                  | DA6              | D6     | D6    |

| PE10     | D7  | D7                                  | DA7              | D7     | D7    |

### Table 11. FMC pin definition

| Symbol                               | Ratings                                                                         | Max.   | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|--------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>    | 270    |      |

| $\Sigma I_{VSS}$                     | Total current out of sum of all $V_{SS_x}$ ground lines $(sink)^{(1)}$          | - 270  |      |

| I <sub>VDD</sub>                     | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>  | 100    |      |

| I <sub>VSS</sub>                     | Maximum current out of each $V_{SS_x}$ ground line (sink) <sup>(1)</sup>        | - 100  |      |

| 1                                    | Output current sunk by any I/O and control pin                                  | 25     |      |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/Os and control pin                              | - 25   |      |

| ΣI                                   | Total output current sunk by sum of all I/O and control pins <sup>(2)</sup>     | 120    | mA   |

| $\Sigma I_{IO}$                      | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | - 120  |      |

|                                      | Injected current on FT pins <sup>(4)</sup>                                      | 5/10   |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on NRST and BOOT0 pins <sup>(4)</sup>                          | - 5/+0 |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ±5     |      |

| $\Sigma I_{\rm INJ(PIN)}^{(5)}$      | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ±25    |      |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.21: 12-bit ADC characteristics.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. A positive injection is induced by  $V_{IN} > V_{DDA}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 14* for the values of the maximum allowed input voltage.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

### Table 16. Thermal characteristics

| Symbol           | Ratings                      | Value        | Unit |

|------------------|------------------------------|--------------|------|

| T <sub>STG</sub> | Storage temperature range    | – 65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125          | °C   |

|                 |                   |                                              |                         |     |              | Max <sup>(1)</sup> |           | Unit |

|-----------------|-------------------|----------------------------------------------|-------------------------|-----|--------------|--------------------|-----------|------|

| Symbol          | Parameter         | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур | TA=<br>25 °C | TA=85 °C           | TA=105 °C |      |

|                 |                   |                                              | 180                     | 103 | 112          | 140                | 151       |      |

|                 |                   |                                              | 168                     | 98  | 107          | 126                | 144       |      |

|                 |                   |                                              | 150                     | 87  | 95           | 112                | 128       |      |

|                 |                   |                                              | 144                     | 85  | 92           | 108                | 124       |      |

|                 |                   |                                              | 120                     | 66  | 71           | 85                 | 99        |      |

|                 |                   |                                              | 90                      | 54  | 58           | 69                 | 80        |      |

|                 |                   | All Peripherals<br>enabled <sup>(2)(3)</sup> | 60                      | 37  | 39           | 47                 | 55        |      |

|                 |                   |                                              | 30                      | 20  | 24           | 39                 | 51        |      |

|                 |                   |                                              | 25                      | 17  | 21           | 35                 | 48        | - mA |

|                 |                   |                                              | 16                      | 12  | 16           | 30                 | 42        |      |

|                 |                   |                                              | 8                       | 7   | 11           | 24                 | 37        |      |

|                 |                   |                                              | 4                       | 5   | 8            | 22                 | 35        |      |

|                 | Supply current in |                                              | 2                       | 3   | 7            | 21                 | 34        |      |

| I <sub>DD</sub> | RUN mode          |                                              | 180                     | 57  | 62           | 87                 | 106       |      |

|                 |                   |                                              | 168                     | 50  | 54           | 76                 | 93        |      |

|                 |                   |                                              | 150                     | 46  | 50           | 70                 | 86        |      |

|                 |                   |                                              | 144                     | 45  | 49           | 68                 | 84        |      |

|                 |                   |                                              | 120                     | 36  | 41           | 56                 | 69        |      |

|                 |                   |                                              | 90                      | 29  | 34           | 46                 | 57        |      |

|                 |                   | All Peripherals<br>disabled <sup>(3)</sup>   | 60                      | 21  | 24           | 33                 | 41        |      |

|                 |                   |                                              | 30                      | 13  | 17           | 31                 | 44        |      |

|                 |                   |                                              | 25                      | 11  | 15           | 28                 | 41        |      |

|                 |                   |                                              | 16                      | 8   | 12           | 25                 | 38        |      |

|                 |                   |                                              | 8                       | 5   | 9            | 23                 | 35        |      |

|                 |                   |                                              | 4                       | 4   | 7            | 21                 | 34        |      |

|                 |                   |                                              | 2                       | 3   | 6.5          | 20                 | 33        |      |

# Table 25. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

# 6.3.13 Memory characteristics

## Flash memory

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter | Conditions                                  | Min | Тур | Max | Unit |

|-----------------|-----------|---------------------------------------------|-----|-----|-----|------|

|                 |           | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 5   | -   |      |

| I <sub>DD</sub> |           | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                 |           | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

| t <sub>prog</sub>       |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

|                         | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |

| t <sub>ERASE128KB</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |

| t <sub>erase128kb</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 16   | 32                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 11   | 22                 | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |

### Table 48. Flash memory programming

## 6.3.19 TIM timer characteristics

The parameters given in Table 60 are guaranteed by design.

Refer to Section 6.3.17: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                       | Conditions <sup>(3)</sup>                                            | Min | Max                     | Unit                 |

|------------------------|-------------------------------------------------|----------------------------------------------------------------------|-----|-------------------------|----------------------|

| t <sub>res(TIM)</sub>  | Timer resolution time                           | AHB/APBx prescaler=1<br>or 2 or 4, f <sub>TIMxCLK</sub> =<br>180 MHz | 1   | -                       | t <sub>TIMxCLK</sub> |

| ,                      |                                                 | AHB/APBx prescaler>4,<br>f <sub>TIMxCLK</sub> = 90 MHz               | 1   | -                       | t <sub>TIMxCLK</sub> |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 180 MHz                                       | 0   | f <sub>TIMxCLK</sub> /2 | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                |                                                                      | -   | 16/32                   | bit                  |

| t <sub>MAX_COUNT</sub> | Maximum possible count with 32-bit counter      |                                                                      | -   | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |

| Table 60 | TIMx | characteristics <sup>(1)(2)</sup> |

|----------|------|-----------------------------------|

|----------|------|-----------------------------------|

1. TIMx is used as a general term to refer to the TIM1 to TIM12 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 or APB2 is up to 180 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK = 4x PCLKx.

## 6.3.20 Communications interfaces

# I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0090 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 6.3.17: I/O port characteristics for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

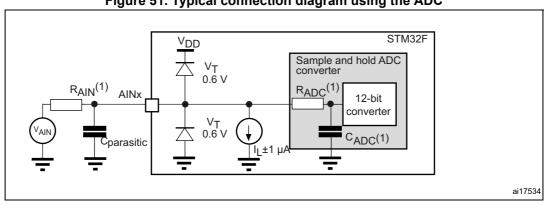

Figure 51. Typical connection diagram using the ADC

1. Refer to Table 74 for the values of  $\mathsf{R}_{\mathsf{AIN}},\,\mathsf{R}_{\mathsf{ADC}}\,\mathsf{and}\,\mathsf{C}_{\mathsf{ADC}}.$

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

| Symbol                                                    | Parameter                                               | Min                      | Max                     | Unit |

|-----------------------------------------------------------|---------------------------------------------------------|--------------------------|-------------------------|------|

| t <sub>w(NE)</sub>                                        | FMC_NE low time                                         | 3T <sub>HCLK</sub> – 1   | 3T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>v(NOE_NE)</sub>                                    | FMC_NEx low to FMC_NOE low                              | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub>      | ns   |

| t <sub>tw(NOE)</sub>                                      | FMC_NOE low time                                        | T <sub>HCLK</sub> – 1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>                                    | FMC_NOE high to FMC_NE high hold time                   | 1                        | -                       | ns   |

| t <sub>v(A_NE)</sub>                                      | FMC_NEx low to FMC_A valid                              | -                        | 2                       | ns   |

| t <sub>v(NADV_NE)</sub>                                   | FMC_NEx low to FMC_NADV low                             | 0                        | 2                       | ns   |

| t <sub>w(NADV)</sub>                                      | FMC_NADV low time                                       | T <sub>HCLK</sub> – 0.5  | T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>h(AD_NADV)</sub>                                   | FMC_AD(address) valid hold time after<br>FMC_NADV high) | 0                        | -                       | ns   |

| t <sub>h(A_NOE)</sub>                                     | Address hold time after FMC_NOE high                    | T <sub>HCLK</sub> – 0.5  | -                       | ns   |

| t <sub>h(BL_NOE)</sub>                                    | FMC_BL time after FMC_NOE high                          | 0                        | -                       | ns   |

| t <sub>v(BL_NE)</sub>                                     | FMC_NEx low to FMC_BL valid                             | -                        | 2                       | ns   |

| t <sub>su(Data_NE)</sub>                                  | Data to FMC_NEx high setup time                         | T <sub>HCLK</sub> +1.5   | -                       | ns   |

| t <sub>su(Data_NOE)</sub> Data to FMC_NOE high setup time |                                                         | T <sub>HCLK</sub> +1     | -                       | ns   |

| t <sub>h(Data_NE)</sub> Data hold time after FMC_NEx high |                                                         | 0                        | -                       | ns   |

| t <sub>h(Data_NOE)</sub>                                  | Data hold time after FMC_NOE high                       | 0                        | -                       | ns   |

Table 90. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

|                           |                                           | 0                       | -                       |      |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> +0.5 | 8T <sub>HCLK</sub> +2   | ns   |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> – 1  | 5T <sub>HCLK</sub> +1.5 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> +1.5 | -                       | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   |                         | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

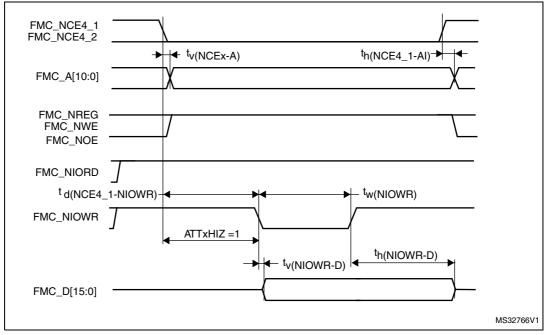

Figure 68. PC Card/CompactFlash controller waveforms for I/O space write access

Table 98. Switching characteristics for PC Card/CF read and write cycles in attribute/common space  $^{(1)(2)}$

| Symbol                    | Parameter                                  | Min                       | Мах                      | Unit |

|---------------------------|--------------------------------------------|---------------------------|--------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FMC_Ncex low to FMC_Ay valid               | -                         | 0                        | ns   |

| t <sub>h(NCEx_AI)</sub>   | FMC_NCEx high to FMC_Ax invalid            | 0                         | -                        | ns   |

| t <sub>d(NREG-NCEx)</sub> | FMC_NCEx low to FMC_NREG valid             | -                         | 1                        | ns   |

| t <sub>h(NCEx-NREG)</sub> | FMC_NCEx high to FMC_NREG invalid          | T <sub>HCLK</sub> – 2     | -                        | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FMC_NCEx low to FMC_NWE low                | -                         | 5T <sub>HCLK</sub>       | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low width                          | 8T <sub>HCLK</sub> – 0.5  | 8T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>d(NWE_NCEx)</sub>  | FMC_NWE high to FMC_NCEx high              | 5T <sub>HCLK</sub> +1     | -                        | ns   |

| t <sub>V(NWE-D)</sub>     | FMC_NWE low to FMC_D[15:0] valid           | -                         | 0                        | ns   |

| t <sub>h(NWE-D)</sub>     | FMC_NWE high to FMC_D[15:0] invalid        | 9T <sub>HCLK</sub> – 0.5  | -                        | ns   |

| t <sub>d(D-NWE)</sub>     | FMC_D[15:0] valid before FMC_NWE high      | 13T <sub>HCLK</sub> – 3   |                          | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FMC_NCEx low to FMC_NOE low                | -                         | 5T <sub>HCLK</sub>       | ns   |

| t <sub>w(NOE)</sub>       | FMC_NOE low width                          | 8 T <sub>HCLK</sub> – 0.5 | 8 T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FMC_NOE high to FMC_NCEx high              | 5T <sub>HCLK</sub> – 1    | -                        | ns   |

| t <sub>su (D-NOE)</sub>   | FMC_D[15:0] valid data before FMC_NOE high | T <sub>HCLK</sub>         | -                        | ns   |

| t <sub>h(NOE-D)</sub>     | FMC_NOE high to FMC_D[15:0] invalid        | 0                         | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

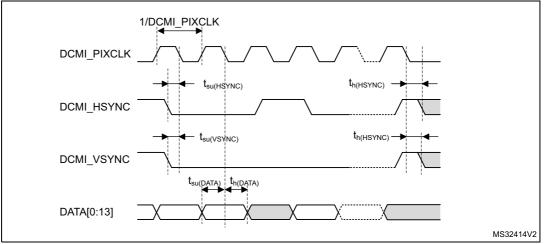

# 6.3.27 Camera interface (DCMI) timing specifications

Unless otherwise specified, the parameters given in *Table 106* for DCMI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 17*, with the following configuration:

- DCMI\_PIXCLK polarity: falling

- DCMI\_VSYNC and DCMI\_HSYNC polarity: high

- Data formats: 14 bits

| Symbol Parameter                                 |                                               | Min | Max | Unit |

|--------------------------------------------------|-----------------------------------------------|-----|-----|------|

|                                                  | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | -   | 0.4 |      |

| DCMI_PIXCLK                                      | Pixel clock input                             | -   | 54  | MHz  |

| D <sub>Pixel</sub>                               | Pixel clock input duty cycle                  | 30  | 70  | %    |

| t <sub>su(DATA)</sub>                            | Data input setup time                         | 2   | -   |      |

| t <sub>h(DATA)</sub>                             | Data input hold time                          | 2.5 | -   |      |

| t <sub>su(HSYNC)</sub><br>t <sub>su(VSYNC)</sub> | DCMI_HSYNC/DCMI_VSYNC input setup time        | 0.5 | -   | ns   |

| t <sub>h(HSYNC)</sub><br>t <sub>h(VSYNC)</sub>   | DCMI_HSYNC/DCMI_VSYNC input hold time         | 1   | -   |      |

### Table 106. DCMI characteristics

### Figure 75. DCMI timing diagram

| Symbol              | Parameter                               | Conditions  | Min | Тур | Max | Unit |  |

|---------------------|-----------------------------------------|-------------|-----|-----|-----|------|--|

| f <sub>PP</sub>     | Clock frequency in data transfer mode   |             | 0   |     | 48  | MHz  |  |

| -                   | SDIO_CK/fPCLK2 frequency ratio          |             | -   | -   | 8/3 | -    |  |

| t <sub>W(CKL)</sub> | Clock low time                          | fpp =48 MHz | 8.5 | 9   | -   |      |  |

| t <sub>W(CKH)</sub> | Clock high time                         | fpp =48 MHz | 8.3 | 10  | -   | – ns |  |

| CMD, D inp          | outs (referenced to CK) in MMC and SE   | O HS mode   |     |     |     |      |  |

| t <sub>ISU</sub>    | Input setup time HS                     | fpp =48 MHz | 3.5 | -   | -   |      |  |

| t <sub>IH</sub>     | Input hold time HS                      | fpp =48 MHz | 0   | -   | -   | ns   |  |

| CMD, D ou           | tputs (referenced to CK) in MMC and S   | SD HS mode  |     | •   | •   |      |  |

| t <sub>OV</sub>     | Output valid time HS                    | fpp =48 MHz | -   | 4.5 | 7   |      |  |

| t <sub>OH</sub>     | Output hold time HS                     | fpp =48 MHz | 3   | -   | -   | ns   |  |

| CMD, D inp          | outs (referenced to CK) in SD default m | node        |     |     |     |      |  |

| tISUD               | Input setup time SD                     | fpp =24 MHz | 1.5 | -   | -   |      |  |

| tIHD                | Input hold time SD                      | fpp =24 MHz | 0.5 | -   | -   | ns . |  |

| CMD, D ou           | tputs (referenced to CK) in SD default  | mode        |     |     |     |      |  |

| tOVD                | Output valid default time SD            | fpp =24 MHz | -   | 4.5 | 6.5 |      |  |

| tOHD                |                                         | fpp =24 MHz | 3.5 |     |     | ns   |  |

1. Guaranteed by characterization results.

2.  $V_{DD}$  = 2.7 to 3.6 V.

## 6.3.30 RTC characteristics

### Table 109. RTC characteristics

| Symbol | Parameter                                  | Conditions                                          | Min | Max |

|--------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

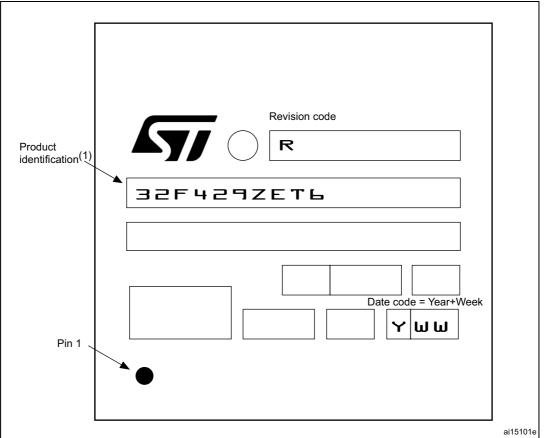

### **Device marking for LQFP144**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

### Figure 88. LQFP144 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

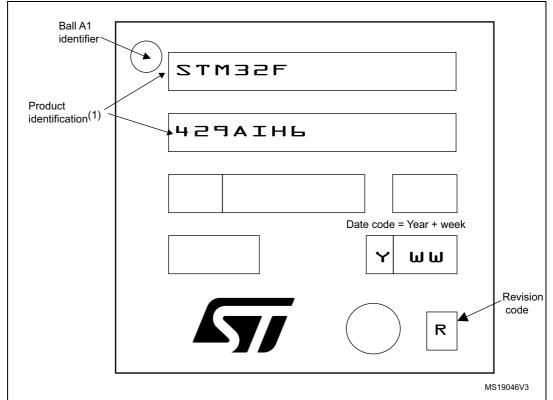

### **Device marking for UFBGA169**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

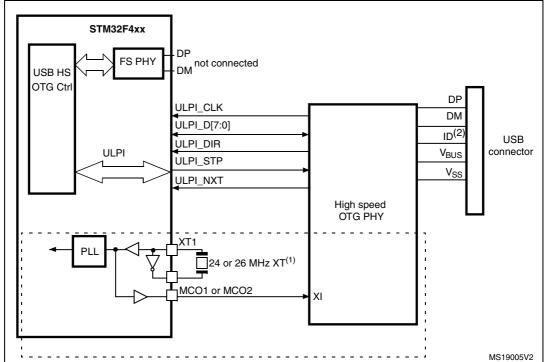

# B.2 USB OTG high speed (HS) interface solutions

Figure 106. USB controller configured as peripheral, host, or dual-mode and used in high speed mode

It is possible to use MCO1 or MCO2 to save a crystal. It is however not mandatory to clock the STM32F42x with a 24 or 26 MHz crystal when using USB HS. The above figure only shows an example of a possible connection.

<sup>2.</sup> The ID pin is required in dual role only.

| []          | Table 124. Document revision history |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                             | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 17-Sep-2015 | 6                                    | Updated notes related to the minimum and maximum values<br>guaranteed by design, characterization or test in production.<br>Updated I <sub>DD_STOP_UDM</sub> in <i>Table 27: Typical and maximum current</i><br><i>consumptions in Stop mode</i> .<br>Removed note related to tests in production in <i>Table 24: Typical and</i><br><i>maximum current consumption in Run mode, code with data</i><br><i>processing running from Flash memory (ART accelerator enabled</i><br><i>except prefetch) or RAM</i> and <i>Table 26: Typical and maximum current</i><br><i>consumption in Sleep mode</i> .<br>Updated <i>Table 41: HSI oscillator characteristics. Figure 31</i> renamed<br><i>ACCHSI accuracy versus temperature</i> and updated.<br>Updated <i>Figure 38: SPI timing diagram - slave mode and CPHA = 0.</i><br>Updated <i>Section : Ethernet characteristics.</i><br>Updated <i>Table 43: Main PLL characteristics.</i><br>Updated <i>Table 57: ADC static accuracy at fADC = 18 MHz,</i><br><i>Table 76: ADC static accuracy at fADC = 30 MHz</i> and <i>Table 77: ADC</i><br><i>static accuracy at fADC = 36 MHz.</i><br>Updated t <sub>d(SDCLKL_Data)</sub> and t <sub>h(SDCLKL_Data)</sub> in <i>Table 104: SDRAM</i><br><i>write timings.</i><br>Added <i>Figure 96: UFBGA169 - 169-ball, 7 x 7 mm, 0.50 mm pitch, ultra</i><br><i>fine pitch ball grid array recommended footprint</i> and <i>Table 117:</i><br><i>UFBGA169 recommended PCB design rules (0.5 mm pitch, gal).</i><br>Added <i>Figure 99: UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch,</i><br><i>ultra fine pitch ball grid array package recommended footprint</i> and<br><i>Table 119: UFBGA176+25 recommended PCB design rules (0.65 mm</i><br><i>pitch BGA).</i> |  |  |  |

| 30-Nov-2015 | 7                                    | Updated $ V_{SSX} - V_{SS} $ in Table 14: Voltage characteristics to add $V_{REF}$ .<br>Updated $t_{d(TXEN)}$ and $t_{d(TXD)}$ minimum value in Table 72: Dynamics characteristics: Ethernet MAC signals for RMII and Table 73: Dynamics characteristics: Ethernet MAC signals for MII.<br>Added $V_{REF}$ in Table 74: ADC characteristics.<br>Added A1 minimum and maximum values in Table 111: WLCSP143 - 143-ball, 4.521x 5.547 mm, 0.4 mm pitch wafer level chip scale package mechanical data. Updated Figure 86: LQFP144-144-pin, 20 x 20 mm low-profile quad flat package outline.<br>Updated Figure 98: UFBGA176+25 - ball 10 x 10 mm, 0.65 mm pitch ultra thin fine pitch ball grid array package outline and Table 118: UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline and Table 118: UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline and Table 120: TFBGA216 - 216 ball 13 × 13 mm 0.8 mm pitch thin fine pitch ball grid array package mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Table 124. Documer | t revision history |

|--------------------|--------------------|

|--------------------|--------------------|