### STMicroelectronics - STM32F427ZIT7TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                        |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K × 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 144-LQFP                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f427zit7tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2 Description

The STM32F427xx and STM32F429xx devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 180 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F427xx and STM32F429xx devices incorporate high-speed embedded memories (Flash memory up to 2 Mbyte, up to 256 kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Six SPIs, two I<sup>2</sup>Ss full duplex. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus four UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- One SAI serial audio interface

- An SDIO/MMC interface

- Ethernet and camera interface

- LCD-TFT display controller

- Chrom-ART Accelerator™.

Advanced peripherals include an SDIO, a flexible memory control (FMC) interface, a camera interface for CMOS sensors. Refer to *Table 2: STM32F427xx and STM32F429xx features and peripheral counts* for the list of peripherals available on each part number.

The STM32F427xx and STM32F429xx devices operates in the -40 to +105 °C temperature range from a 1.7 to 3.6 V power supply.

The supply voltage can drop to 1.7 V with the use of an external power supply supervisor (refer to *Section 3.17.2: Internal reset OFF*). A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F427xx and STM32F429xx devices offer devices in 8 packages ranging from 100 pins to 216 pins. The set of included peripherals changes with the device chosen.

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

## 3.20 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

### • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

### Table 5. Voltage regulator modes in stop mode

### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

### 3.39 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

## 3.40 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 10-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

## 3.41 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

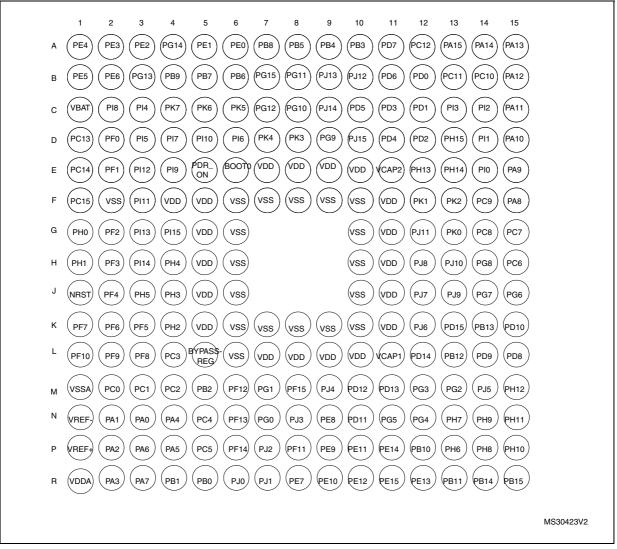

### Figure 18. STM32F42x TFBGA216 ballout

1. The above figure shows the package top view.

|         |         |          | Pin nu   |         |          |         |          |                                                      |          |                 |       |                                                                                                                     | ,                           |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                                 | Additional<br>functions     |

| -       | -       | M1       | L4       | 48      | N11      | -       | L5       | BYPASS_<br>REG                                       | Ι        | FT              | -     | -                                                                                                                   | -                           |

| 28      | 39      | J11      | K4       | 49      | J8       | 52      | K5       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| 29      | 40      | N2       | N4       | 50      | M10      | 53      | N4       | PA4                                                  | I/O      | ТТа             | (5)   | SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK,<br>OTG_HS_SOF,<br>DCMI_HSYNC,<br>LCD_VSYNC,<br>EVENTOUT                | ADC12_<br>IN4 /DAC_<br>OUT1 |

| 30      | 41      | М3       | P4       | 51      | M9       | 54      | P4       | PA5                                                  | I/O      | ТТа             | (5)   | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK,<br>OTG_HS_ULPI_CK,<br>EVENTOUT                                        | ADC12_<br>IN5/DAC_<br>OUT2  |

| 31      | 42      | N3       | P3       | 52      | N10      | 55      | P3       | PA6                                                  | I/O      | FT              | (5)   | TIM1_BKIN,<br>TIM3_CH1,<br>TIM8_BKIN,<br>SPI1_MISO,<br>TIM13_CH1,<br>DCMI_PIXCLK,<br>LCD_G2, EVENTOUT               | ADC12_<br>IN6               |

| 32      | 43      | K4       | R3       | 53      | L8       | 56      | R3       | PA7                                                  | I/O      | FT              | (5)   | TIM1_CH1N,<br>TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI,<br>TIM14_CH1,<br>ETH_MII_RX_DV/ETH_<br>RMII_CRS_DV,<br>EVENTOUT | ADC12_<br>IN7               |

| 33      | 44      | L4       | N5       | 54      | M8       | 57      | N5       | PC4                                                  | I/O      | FT              | (5)   | ETH_MII_RXD0/ETH_<br>RMII_RXD0,<br>EVENTOUT                                                                         | ADC12_<br>IN14              |

| 34      | 45      | M4       | P5       | 55      | N9       | 58      | P5       | PC5                                                  | I/O      | FT              | (5)   | ETH_MII_RXD1/ETH_<br>RMII_RXD1,<br>EVENTOUT                                                                         | ADC12_<br>IN15              |

| -       | -       | -        | -        | -       | J7       | 59      | L7       | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                                   | -                           |

| -       | -       | -        | -        | -       | -        | 60      | L6       | VSS                                                  | S        | -               | -     | -                                                                                                                   | -                           |

| Table 10. | STM32F427xx and | STM32F429xx pir | n and ball de | efinitions (continued) | ) |

|-----------|-----------------|-----------------|---------------|------------------------|---|

|           |                 |                 |               |                        | £ |

|         |         |           | Pin nu   | ımber   | •        |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 82      | 115     | C9        | C12      | 143     | C4       | 165     | C12      | PD1                                                  | I/O      | FT              | -     | CAN1_TX, FMC_D3,<br>EVENTOUT                                                                  | -                       |

| 83      | 116     | В9        | D12      | 144     | A3       | 166     | D12      | PD2                                                  | I/O      | FT              | -     | TIM3_ETR,<br>UART5_RX,<br>SDIO_CMD,<br>DCMI_D11,<br>EVENTOUT                                  | -                       |

| 84      | 117     | A9        | D11      | 145     | B4       | 167     | C11      | PD3                                                  | I/O      | FT              | -     | SPI2_SCK/I2S2_CK,<br>USART2_CTS,<br>FMC_CLK, DCMI_D5,<br>LCD_G7, EVENTOUT                     | -                       |

| 85      | 118     | D8        | D10      | 146     | B5       | 168     | D11      | PD4                                                  | I/O      | FT              | -     | USART2_RTS,<br>FMC_NOE,<br>EVENTOUT                                                           | -                       |

| 86      | 119     | C8        | C11      | 147     | A4       | 169     | C10      | PD5                                                  | I/O      | FT              | -     | USART2_TX,<br>FMC_NWE,<br>EVENTOUT                                                            | -                       |

| -       | 120     | -         | D8       | 148     | -        | 170     | F8       | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 121     | D6        | C8       | 149     | C5       | 171     | E9       | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| 87      | 122     | B8        | B11      | 150     | F4       | 172     | B11      | PD6                                                  | I/O      | FT              | -     | SPI3_MOSI/I2S3_SD,<br>SAI1_SD_A,<br>USART2_RX,<br>FMC_NWAIT,<br>DCMI_D10, LCD_B2,<br>EVENTOUT | -                       |

| 88      | 123     | A8        | A11      | 151     | A5       | 173     | A11      | PD7                                                  | I/O      | FT              | -     | USART2_CK,<br>FMC_NE1/FMC_NCE2,<br>EVENTOUT                                                   | -                       |

| -       | -       | -         | -        | -       | -        | 174     | B10      | PJ12                                                 | I/O      | FT              | -     | LCD_B0, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 175     | B9       | PJ13                                                 | I/O      | FT              | -     | LCD_B1, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 176     | C9       | PJ14                                                 | I/O      | FT              | -     | LCD_B2, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 177     | D10      | PJ15                                                 | I/O      | FT              | -     | LCD_B3, EVENTOUT                                                                              | -                       |

| -       | 124     | NC<br>(2) | C10      | 152     | E5       | 178     | D9       | PG9                                                  | I/O      | FT              | -     | USART6_RX,<br>FMC_NE2/FMC_NCE3,<br>DCMI_VSYNC <sup>(8)</sup> ,<br>EVENTOUT                    | -                       |

Table 10. STM32F427xx and STM32F429xx pin and ball definitions (continued)

DocID024030 Rev 9

#### Pinouts and pin description

- 4. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F4xx reference manual, available from the STMicroelectronics website: www.st.com.

- 5. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- If the device is delivered in an WLCSP143, UFBGA169, UFBGA176, LQFP176 or TFBGA216 package, and the BYPASS\_REG pin is set to V<sub>DD</sub> (Regulator OFF/internal reset ON mode), then PA0 is used as an internal Reset (active low).

- 7. PI0 and PI1 cannot be used for I2S2 full-duplex mode.

- 8. The DCMI\_VSYNC alternate function on PG9 is only available on silicon revision 3.

| Operating<br>power supply<br>range                | ADC operation                     | Maximum Flash<br>memory access<br>frequency with<br>no wait states<br>(f <sub>Flashmax</sub> ) | Maximum HCLK<br>frequency vs Flash<br>memory wait states<br>(1)(2) | I/O operation          | Possible Flash<br>memory<br>operations        |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup>   | Conversion time<br>up to 1.2 Msps | 20 MHz <sup>(4)</sup>                                                                          | 168 MHz with 8 wait<br>states and over-drive<br>OFF                | No I/O<br>compensation | 8-bit erase and<br>program<br>operations only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                 | Conversion time<br>up to 1.2 Msps | 22 MHz                                                                                         | 180 MHz with 8 wait<br>states and over-drive<br>ON                 | No I/O<br>compensation | 16-bit erase and<br>program<br>operations     |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                 | Conversion time<br>up to 2.4 Msps | 24 MHz                                                                                         | 180 MHz with 7 wait<br>states and over-drive<br>ON                 | I/O compensation works | 16-bit erase and<br>program<br>operations     |

| $V_{DD} = 2.7 \text{ to}$<br>3.6 V <sup>(5)</sup> | Conversion time<br>up to 2.4 Msps | 30 MHz                                                                                         | 180 MHz with 5 wait<br>states and over-drive<br>ON                 | I/O compensation works | 32-bit erase and program operations           |

Table 18. Limitations depending on the operating power supply range

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

- 4. Prefetch is not available.

- 5. The voltage range for USB full speed PHYs can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

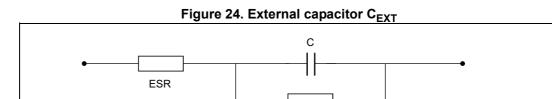

### 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{EXT}$  to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 19*.

1. Legend: ESR is the equivalent series resistance.

#### Table 19. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

R <sub>Leak</sub>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu$ F V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

MS19044V2

### 6.3.7 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 23: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- Regulator ON

- The voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \leq 120 \text{ MHz}$

- Scale 2 for 120 MHz < f<sub>HCLK</sub> ≤144 MHz

- Scale 1 for 144 MHz < f<sub>HCLK</sub> ≤180 MHz. The over-drive is only ON at 180 MHz.

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- External clock frequency is 4 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and a maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

| Table 24. Typical and maximum current consumption in Run mode, code with data processing  |  |

|-------------------------------------------------------------------------------------------|--|

| running from Flash memory (ART accelerator enabled except prefetch) or RAM <sup>(1)</sup> |  |

|                 |                   |                           |                         |     |                           | Max <sup>(2)</sup>        |                            |                   |    |  |  |   |   |   |    |    |  |

|-----------------|-------------------|---------------------------|-------------------------|-----|---------------------------|---------------------------|----------------------------|-------------------|----|--|--|---|---|---|----|----|--|

| Symbol          | Parameter         | Conditions                | f <sub>HCLK</sub> (MHz) | Тур | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit              |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 180                     | 98  | 104 <sup>(5)</sup>        | 123                       | 141 <sup>(5)</sup>         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 168                     | 89  | 98 <sup>(5)</sup>         | 116                       | 133 <sup>(5)</sup>         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 150                     | 75  | 84                        | 100                       | 115                        |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 144                     | 72  | 81                        | 96                        | 112                        |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 120                     | 54  | 58                        | 72                        | 85                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   | All                       | 90                      | 43  | 45                        | 56                        | 66                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   | Peripherals               | 60                      | 29  | 30                        | 38                        | 45                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   | enabled <sup>(3)(4)</sup> | 30                      | 16  | 20                        | 34                        | 46                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 25                      | 13  | 16                        | 30                        | 43                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 16                      | 11  | 13                        | 27                        | 39                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           |                         |     |                           |                           |                            |                   |    |  |  | 8 | 5 | 9 | 23 | 36 |  |

|                 |                   |                           |                         |     | 4                         | 4                         | 8                          | 21                | 34 |  |  |   |   |   |    |    |  |

| 1               | Supply current in |                           | 2                       | 2   | 7                         | 20                        | 33                         |                   |    |  |  |   |   |   |    |    |  |

| I <sub>DD</sub> | RUN mode          | •                         |                         | 180 | 44                        | 47 <sup>(5)</sup>         | 69                         | 87 <sup>(5)</sup> | mA |  |  |   |   |   |    |    |  |

|                 |                   |                           |                         | 168 | 41                        | 45 <sup>(5)</sup>         | 66                         | 83 <sup>(5)</sup> |    |  |  |   |   |   |    |    |  |

|                 |                   |                           |                         | 150 | 36                        | 39                        | 57                         | 73                |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 144                     | 33  | 37                        | 56                        | 72                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 120                     | 25  | 29                        | 43                        | 56                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   | All                       | 90                      | 20  | 21                        | 32                        | 41                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   | Peripherals               | 60                      | 14  | 15                        | 22                        | 28                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   | disabled <sup>(3)</sup>   | 30                      | 8   | 8                         | 12                        | 26                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 25                      | 7   | 7                         | 10                        | 24                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 16                      | 7   | 9                         | 22                        | 35                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 8                       | 3   | 7                         | 21                        | 34                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 4                       | 3   | 6                         | 20                        | 33                         |                   |    |  |  |   |   |   |    |    |  |

|                 |                   |                           | 2                       | 2   | 6                         | 20                        | 33                         |                   |    |  |  |   |   |   |    |    |  |

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed by characterization.

3. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. Guaranteed by test in production.

DocID024030 Rev 9

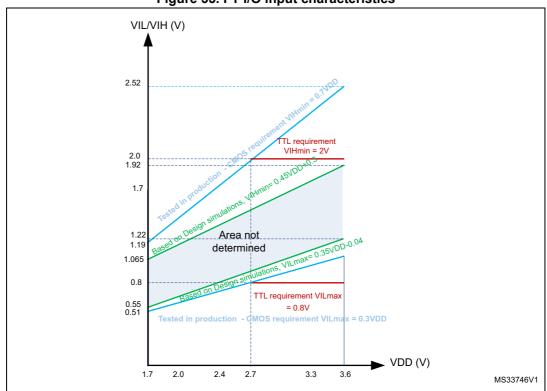

Figure 35. FT I/O input characteristics

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14, PC15 and PI8 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 and PI8 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15*).

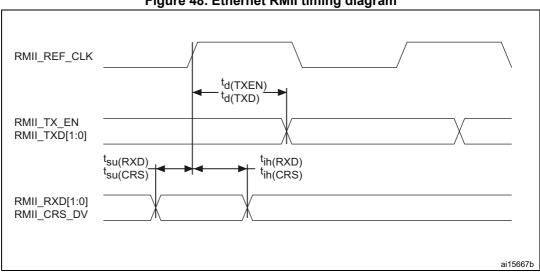

*Table 72* gives the list of Ethernet MAC signals for the RMII and *Figure 48* shows the corresponding timing diagram.

Figure 48. Ethernet RMII timing diagram

| Table 72. Dynamics characteristics: Ethernet MAC signals for RMII <sup>(1)</sup> | ) |

|----------------------------------------------------------------------------------|---|

|----------------------------------------------------------------------------------|---|

| Symbol               | Parameter                                           | Condition                        | Min | Тур  | Мах  | Unit |

|----------------------|-----------------------------------------------------|----------------------------------|-----|------|------|------|

| t <sub>su(RXD)</sub> | Receive data setup time                             |                                  | 1.5 | -    | -    |      |

| t <sub>ih(RXD)</sub> | Receive data hold time                              | 1.71 V < V <sub>DD</sub> < 3.6 V | 0   | -    | -    |      |

| t <sub>su(CRS)</sub> | Carrier sense setup time<br>Carrier sense hold time | 1.71 V < V <sub>DD</sub> < 3.0 V | 1   | -    | -    |      |

| t <sub>ih(CRS)</sub> | Carrier sense hold time                             |                                  | 1   | -    | -    |      |

| +                    | Transmit enable valid delay                         | 2.7 V < V <sub>DD</sub> < 3.6 V  | 8   | 10.5 | 12   | ns   |

| t <sub>d(TXEN)</sub> | time                                                | 1.71 V < V <sub>DD</sub> < 3.6 V | 8   | 10.5 | 14   |      |

| +                    | Transmit data valid dalav tima                      | 2.7 V < V <sub>DD</sub> < 3.6 V  | 8   | 11   | 12.5 |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time                      | 1.71 V < V <sub>DD</sub> < 3.6 V | 8   | 11   | 14.5 |      |

1. Guaranteed by characterization results.

*Table 73* gives the list of Ethernet MAC signals for MII and *Figure 48* shows the corresponding timing diagram.

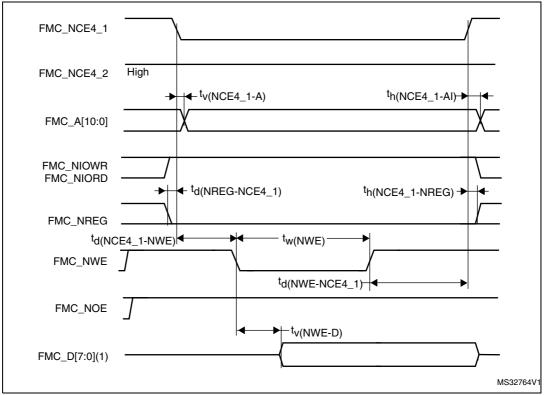

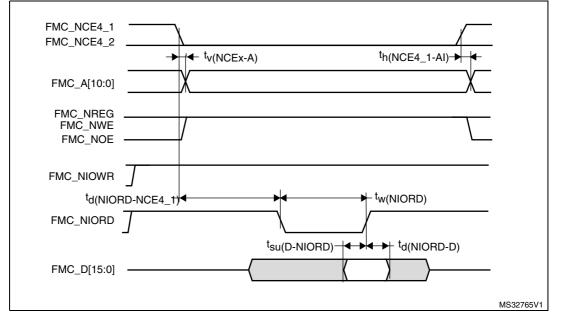

### 6.3.26 FMC characteristics

Unless otherwise specified, the parameters given in *Table 86* to *Table 101* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10 except at V<sub>DD</sub> range 1.7 to 2.1V where OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

### Asynchronous waveforms and timings

*Figure 55* through *Figure 58* represent asynchronous waveforms and *Table 86* through *Table 93* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode , DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

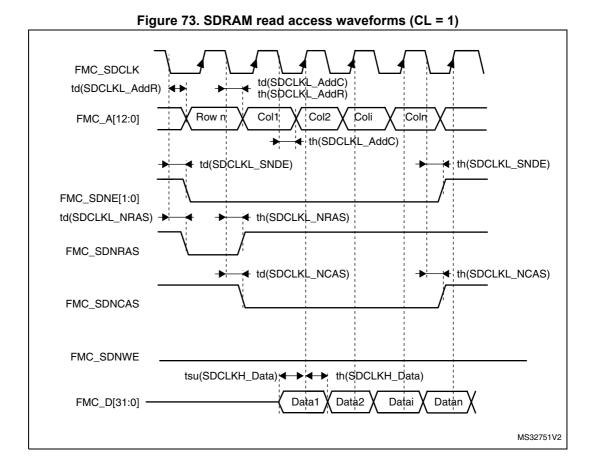

- For SDRAM memories,  $V_{DD}$  ranges from 2.7 to 3.6 V and maximum frequency FMC\_SDCLK = 90 MHz

- For Mobile LPSDR SDRAM memories, V<sub>DD</sub> ranges from 1.7 to 1.95 V and maximum frequency FMC\_SDCLK = 84 MHz

|                           |                                           |                         | <u> </u>                |      |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 9T <sub>HCLK</sub>      | 9T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 7T <sub>HCLK</sub>      | 7T <sub>HCLK</sub> +2   | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                       | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> –1   | -                       | ns   |

Table 93. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

### Synchronous waveforms and timings

*Figure 59* through *Figure 62* represent synchronous waveforms and *Table 94* through *Table 97* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F4xx reference manual : RM0090)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period (with maximum FMC\_CLK = 90 MHz).

| Symbol                      | Parameter                                  | Min                    | Max | Unit |

|-----------------------------|--------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period, VDD range= 2.7 to 3.6 V    | 2T <sub>HCLK</sub> – 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                      | 1.5 | ns   |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub>      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -                      | 0   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 0                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -                      | 0   | ns   |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>      | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -                      | 0   | ns   |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high               | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -                      | 3   | ns   |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0                      | -   | ns   |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -                      | 3   | ns   |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | 0                      | -   | ns   |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 4                      | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 0                      | -   | ns   |

Table 95. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

Figure 66. PC Card/CompactFlash controller waveforms for attribute memory write access

1. Only data bits 0...7 are driven (bits 8...15 remains Hi-Z).

#### Figure 67. PC Card/CompactFlash controller waveforms for I/O space read access

| <u> </u>                |                                       |                        |                         |      |

|-------------------------|---------------------------------------|------------------------|-------------------------|------|

| Symbol                  | Parameter                             | Min                    | Max                     | Unit |

| t <sub>w(NWE)</sub>     | FMC_NWE low width                     | 4T <sub>HCLK</sub>     | 4T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NWE-D)</sub>   | FMC_NWE low to FMC_D[15-0] valid      | 0                      | -                       | ns   |

| t <sub>h(NWE-D)</sub>   | FMC_NWE high to FMC_D[15-0] invalid   | 3T <sub>HCLK</sub> – 1 | -                       | ns   |

| t <sub>d(D-NWE)</sub>   | FMC_D[15-0] valid before FMC_NWE high | 5T <sub>HCLK</sub> – 3 | -                       | ns   |

| t <sub>d(ALE-NWE)</sub> | FMC_ALE valid before FMC_NWE low      | -                      | 3T <sub>HCLK</sub> -0.5 | ns   |

| t <sub>h(NWE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid       | 3T <sub>HCLK</sub> – 1 | -                       | ns   |

| 4 0 00 F                |                                       |                        |                         |      |

Table 101. Switching characteristics for NAND Flash write cycles<sup>(1)</sup>

1. C<sub>L</sub> = 30 pF.

### **SDRAM** waveforms and timings

57

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

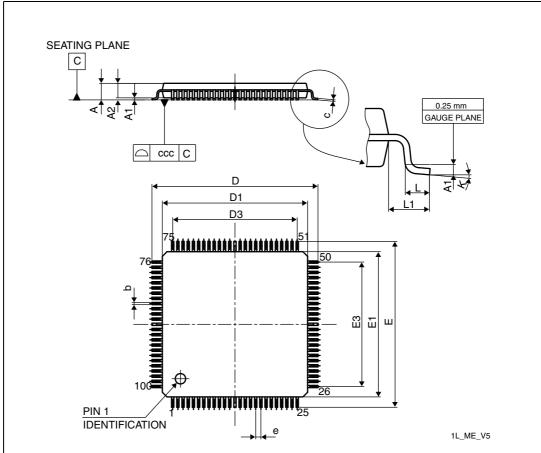

## 7.1 LQFP100 package information

Figure 80. LQFP100 -100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

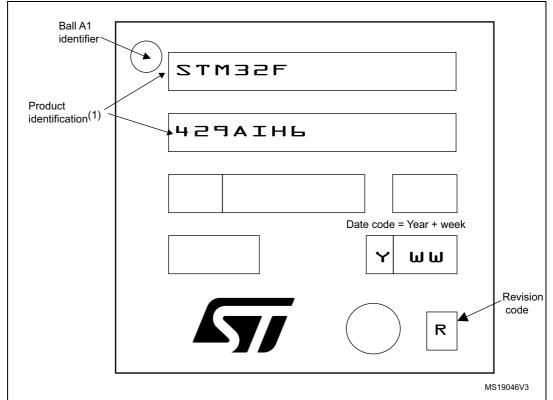

### **Device marking for UFBGA169**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

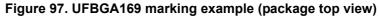

## B.2 USB OTG high speed (HS) interface solutions

Figure 106. USB controller configured as peripheral, host, or dual-mode and used in high speed mode

It is possible to use MCO1 or MCO2 to save a crystal. It is however not mandatory to clock the STM32F42x with a 24 or 26 MHz crystal when using USB HS. The above figure only shows an example of a possible connection.

<sup>2.</sup> The ID pin is required in dual role only.