# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 130                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 169-UFBGA                                                                           |

| Supplier Device Package    | 169-UFBGA (7x7)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f429agh6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

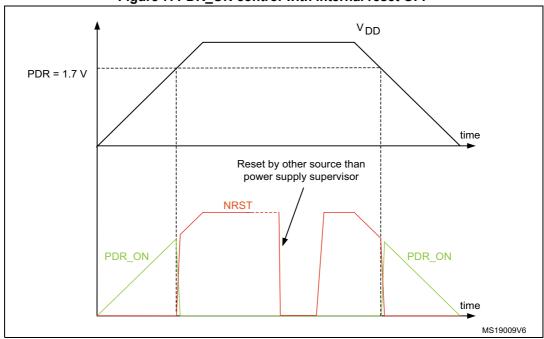

Figure 7. PDR ON control with internal reset OFF

## 3.18 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

#### 3.18.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR mode used in Run/sleep modes or in Stop modes

- In Run/Sleep mode

The MR mode is used either in the normal mode (default mode) or the over-drive mode (enabled by software). Different voltages scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

| Timer<br>type        | Timer               | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz)<br>(1) |

|----------------------|---------------------|-----------------------|-------------------------|---------------------------------------------|------------------------------|---------------------------------|-------------------------|------------------------------------|---------------------------------------|

| Advanced<br>-control | TIM1,<br>TIM8       | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | Yes                     | 90                                 | 180                                   |

|                      | TIM2,<br>TIM5       | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                      | 45                                 | 90/180                                |

|                      | TIM3,<br>TIM4       | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                      | 45                                 | 90/180                                |

| General              | TIM9                | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                      | 90                                 | 180                                   |

| purpose              | TIM10<br>,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                      | 90                                 | 180                                   |

|                      | TIM12               | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                      | 45                                 | 90/180                                |

|                      | TIM13<br>,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                      | 45                                 | 90/180                                |

| Basic                | TIM6,<br>TIM7       | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 0                               | No                      | 45                                 | 90/180                                |

Table 6. Timer feature comparison

1. The maximum timer clock is either 90 or 180 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

communicate at speeds of up to 11.25 Mbit/s. The other available interfaces communicate at up to 5.62 bit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

| USART<br>name | Standard<br>features | Modem<br>(RTS/CTS) | LIN | SPI<br>master | irDA | Smartcard<br>(ISO 7816) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 16) | Max. baud<br>rate in Mbit/s<br>(oversampling<br>by 8) | APB<br>mapping           |

|---------------|----------------------|--------------------|-----|---------------|------|-------------------------|--------------------------------------------------------|-------------------------------------------------------|--------------------------|

| USART1        | х                    | х                  | х   | х             | х    | х                       | 5.62                                                   | 11.25                                                 | APB2<br>(max.<br>90 MHz) |

| USART2        | х                    | х                  | х   | х             | х    | х                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |

| USART3        | х                    | х                  | х   | х             | х    | х                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |

| UART4         | х                    | -                  | х   | -             | х    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |

| UART5         | х                    | -                  | x   | -             | x    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |

| USART6        | х                    | х                  | x   | х             | х    | х                       | 5.62                                                   | 11.25                                                 | APB2<br>(max.<br>90 MHz) |

| UART7         | х                    | -                  | x   | -             | x    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |

| UART8         | х                    | -                  | х   | -             | х    | -                       | 2.81                                                   | 5.62                                                  | APB1<br>(max.<br>45 MHz) |

| Table 8. | USART | feature | comp | arison <sup>(1)</sup> |

|----------|-------|---------|------|-----------------------|

|----------|-------|---------|------|-----------------------|

1. X = feature supported.

## 3.25 Serial peripheral interface (SPI)

The devices feature up to six SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, SPI4, SPI5, and SPI6 can communicate at up to 45 Mbits/s, SPI2 and SPI3 can communicate at up to 22.5 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

DocID024030 Rev 9

| Table 10. STM32F427xx and STM32F429xx pin an Pin number |         |          |    |         | /        | anu S   | ι ινισζρ429XX μ |                                                      |          |                 |       | )                                                                                                     |                            |

|---------------------------------------------------------|---------|----------|----|---------|----------|---------|-----------------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------------------------------|----------------------------|

| LQFP100                                                 | LQFP144 | UFBGA169 |    | LQFP176 | WLCSP143 | LQFP208 | TFBGA216        | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                   | Additional<br>functions    |

| 22                                                      | 33      | J4       | R1 | 39      | L10      | 42      | R1              | V <sub>DDA</sub>                                     | S        | -               | -     | -                                                                                                     | -                          |

| 23                                                      | 34      | J5       | N3 | 40      | K9       | 43      | N3              | PA0-WKUP<br>(PA0)                                    | I/O      | FT              | (6)   | TIM2_CH1/TIM2_ETR,<br>TIM5_CH1, TIM8_ETR,<br>USART2_CTS,<br>UART4_TX,<br>ETH_MII_CRS,<br>EVENTOUT     | ADC123_<br>IN0/WKUP<br>(5) |

| 24                                                      | 35      | K1       | N2 | 41      | K8       | 44      | N2              | PA1                                                  | I/O      | FT              | (5)   | TIM2_CH2, TIM5_CH2,<br>USART2_RTS,<br>UART4_RX,<br>ETH_MII_RX_CLK/ETH<br>_RMII_REF_CLK,<br>EVENTOUT   | ADC123_<br>IN1             |

| 25                                                      | 36      | K2       | P2 | 42      | L9       | 45      | P2              | PA2                                                  | I/O      | FT              | (5)   | TIM2_CH3, TIM5_CH3,<br>TIM9_CH1,<br>USART2_TX,<br>ETH_MDIO,<br>EVENTOUT                               | ADC123_<br>IN2             |

| -                                                       | -       | L2       | F4 | 43      | -        | 46      | K4              | PH2                                                  | I/O      | FT              | -     | ETH_MII_CRS,<br>FMC_SDCKE0,<br>LCD_R0, EVENTOUT                                                       | -                          |

| -                                                       | _       | L1       | G4 | 44      | -        | 47      | J4              | PH3                                                  | I/O      | FT              | -     | ETH_MII_COL,<br>FMC_SDNE0, LCD_R1,<br>EVENTOUT                                                        | -                          |

| -                                                       | _       | M2       | H4 | 45      | -        | 48      | H4              | PH4                                                  | I/O      | FT              | -     | I2C2_SCL,<br>OTG_HS_ULPI_NXT,<br>EVENTOUT                                                             | -                          |

| -                                                       | -       | L3       | J4 | 46      | -        | 49      | J3              | PH5                                                  | I/O      | FT              | -     | I2C2_SDA, SPI5_NSS,<br>FMC_SDNWE,<br>EVENTOUT                                                         | -                          |

| 26                                                      | 37      | КЗ       | R2 | 47      | M11      | 50      | R2              | PA3                                                  | I/O      | FT              | (5)   | TIM2_CH4, TIM5_CH4,<br>TIM9_CH2,<br>USART2_RX,<br>OTG_HS_ULPI_D0,<br>ETH_MII_COL,<br>LCD_B5, EVENTOUT | ADC123_<br>IN3             |

| 27                                                      | 38      | -        | -  |         | -        | 51      | K6              | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                                                     | -                          |

## Table 10. STM32F427xx and STM32F429xx pin and ball definitions (continued)

|         |         |          | Pin nu   |         |          |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| -       | 91      | G11      | J15      | 110     | G4       | 133     | J15      | PG6                                                  | I/O      | FT              | -     | FMC_INT2, DCMI_D12,<br>LCD_R7, EVENTOUT                                                       | -                       |

| -       | 92      | G12      | J14      | 111     | H1       | 134     | J14      | PG7                                                  | I/O      | FT              | -     | USART6_CK,<br>FMC_INT3, DCMI_D13,<br>LCD_CLK, EVENTOUT                                        | -                       |

| -       | 93      | F13      | H14      | 112     | G2       | 135     | H14      | PG8                                                  | I/O      | FT              | -     | SPI6_NSS,<br>USART6_RTS,<br>ETH_PPS_OUT,<br>FMC_SDCLK,<br>EVENTOUT                            | -                       |

| -       | 94      | J7       | G12      | 113     | D2       | 136     | G10      | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 95      | E6       | H13      | 114     | G1       | 137     | G11      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| 63      | 96      | F9       | H15      | 115     | F2       | 138     | H15      | PC6                                                  | I/O      | FT              | -     | TIM3_CH1, TIM8_CH1,<br>I2S2_MCK,<br>USART6_TX,<br>SDIO_D6, DCMI_D0,<br>LCD_HSYNC,<br>EVENTOUT | -                       |

| 64      | 97      | F10      | G15      | 116     | F3       | 139     | G15      | PC7                                                  | I/O      | FT              | -     | TIM3_CH2, TIM8_CH2,<br>I2S3_MCK,<br>USART6_RX,<br>SDIO_D7, DCMI_D1,<br>LCD_G6, EVENTOUT       | -                       |

| 65      | 98      | F11      | G14      | 117     | E4       | 140     | G14      | PC8                                                  | I/O      | FT              | _     | TIM3_CH3, TIM8_CH3,<br>USART6_CK,<br>SDIO_D0, DCMI_D2,<br>EVENTOUT                            | -                       |

| 66      | 99      | F12      | F14      | 118     | E3       | 141     | F14      | PC9                                                  | I/O      | FT              | 1     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, SDIO_D1,<br>DCMI_D3, EVENTOUT             | -                       |

| 67      | 100     | E13      | F15      | 119     | F1       | 142     | F15      | PA8                                                  | I/O      | FT              | -     | MCO1, TIM1_CH1,<br>I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF,<br>LCD_R6, EVENTOUT                 | -                       |

Table 10. STM32F427xx and STM32F429xx pin and ball definitions (continued)

| Operating<br>power supply<br>range                | ADC operation                     | Maximum Flash<br>memory access<br>frequency with<br>no wait states<br>(f <sub>Flashmax</sub> ) | Maximum HCLK<br>frequency vs Flash<br>memory wait states<br>(1)(2) | I/O operation          | Possible Flash<br>memory<br>operations        |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup>   | Conversion time<br>up to 1.2 Msps | 20 MHz <sup>(4)</sup>                                                                          | 168 MHz with 8 wait<br>states and over-drive<br>OFF                | No I/O<br>compensation | 8-bit erase and<br>program<br>operations only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                 | Conversion time<br>up to 1.2 Msps | 22 MHz                                                                                         | 180 MHz with 8 wait<br>states and over-drive<br>ON                 | No I/O<br>compensation | 16-bit erase and<br>program<br>operations     |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                 | Conversion time<br>up to 2.4 Msps | 24 MHz                                                                                         | 180 MHz with 7 wait<br>states and over-drive<br>ON                 | I/O compensation works | 16-bit erase and<br>program<br>operations     |

| $V_{DD} = 2.7 \text{ to}$<br>3.6 V <sup>(5)</sup> | Conversion time<br>up to 2.4 Msps | 30 MHz                                                                                         | 180 MHz with 5 wait<br>states and over-drive<br>ON                 | I/O compensation works | 32-bit erase and program operations           |

Table 18. Limitations depending on the operating power supply range

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

- 4. Prefetch is not available.

- 5. The voltage range for USB full speed PHYs can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

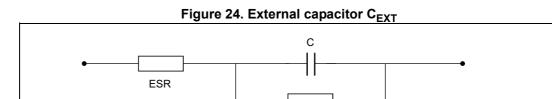

## 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{EXT}$  to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 19*.

1. Legend: ESR is the equivalent series resistance.

#### Table 19. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

R <sub>Leak</sub>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu$ F V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

MS19044V2

|                 |                   |                                              |                         |     |              | Max <sup>(1)</sup> |           |      |

|-----------------|-------------------|----------------------------------------------|-------------------------|-----|--------------|--------------------|-----------|------|

| Symbol          | Parameter         | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур | TA=<br>25 °C | TA=85 °C           | TA=105 °C | Unit |

|                 |                   |                                              | 180                     | 103 | 112          | 140                | 151       |      |

|                 |                   |                                              | 168                     | 98  | 107          | 126                | 144       |      |

|                 |                   |                                              | 150                     | 87  | 95           | 112                | 128       |      |

|                 |                   |                                              | 144                     | 85  | 92           | 108                | 124       |      |

|                 |                   |                                              | 120                     | 66  | 71           | 85                 | 99        |      |

|                 |                   |                                              | 90                      | 54  | 58           | 69                 | 80        |      |

|                 |                   | All Peripherals<br>enabled <sup>(2)(3)</sup> | 60                      | 37  | 39           | 47                 | 55        |      |

|                 |                   |                                              | 30                      | 20  | 24           | 39                 | 51        |      |

|                 |                   |                                              | 25                      | 17  | 21           | 35                 | 48        |      |

|                 |                   |                                              | 16                      | 12  | 16           | 30                 | 42        | • mA |

|                 |                   |                                              | 8                       | 7   | 11           | 24                 | 37        |      |

|                 |                   |                                              | 4                       | 5   | 8            | 22                 | 35        |      |

|                 | Supply current in |                                              | 2                       | 3   | 7            | 21                 | 34        |      |

| I <sub>DD</sub> | RUN mode          |                                              | 180                     | 57  | 62           | 87                 | 106       |      |

|                 |                   |                                              | 168                     | 50  | 54           | 76                 | 93        |      |

|                 |                   |                                              | 150                     | 46  | 50           | 70                 | 86        |      |

|                 |                   |                                              | 144                     | 45  | 49           | 68                 | 84        |      |

|                 |                   |                                              | 120                     | 36  | 41           | 56                 | 69        |      |

|                 |                   |                                              | 90                      | 29  | 34           | 46                 | 57        |      |

|                 |                   | All Peripherals<br>disabled <sup>(3)</sup>   | 60                      | 21  | 24           | 33                 | 41        |      |

|                 |                   |                                              | 30                      | 13  | 17           | 31                 | 44        |      |

|                 |                   |                                              | 25                      | 11  | 15           | 28                 | 41        |      |

|                 |                   |                                              | 16                      | 8   | 12           | 25                 | 38        |      |

|                 |                   |                                              | 8                       | 5   | 9            | 23                 | 35        |      |

|                 |                   |                                              | 4                       | 4   | 7            | 21                 | 34        |      |

|                 |                   |                                              | 2                       | 3   | 6.5          | 20                 | 33        |      |

## Table 25. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

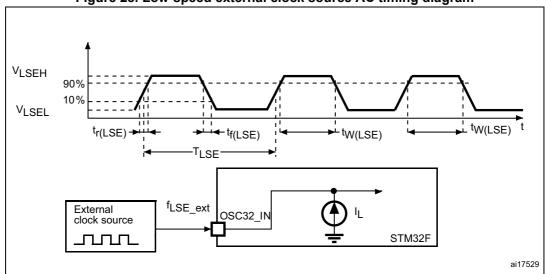

Figure 28. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                            | Parameter                               | Conditions                                                            | Min   | Тур | Max | Unit |

|-----------------------------------|-----------------------------------------|-----------------------------------------------------------------------|-------|-----|-----|------|

| f <sub>OSC_IN</sub>               | Oscillator frequency                    |                                                                       | 4     | -   | 26  | MHz  |

| R <sub>F</sub>                    | Feedback resistor                       |                                                                       | -     | 200 | -   | kΩ   |

|                                   | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -     |     |     | μA   |

| IDD                               |                                         | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -     | 530 | -   | μΑ   |

| ACC <sub>HSE</sub> <sup>(2)</sup> | HSE accuracy                            |                                                                       | - 500 | -   | 500 | ppm  |

| G <sub>m</sub> _crit_max          | Maximum critical crystal g <sub>m</sub> | Startup                                                               | -     | -   | 1   | mA/V |

| $t_{SU(HSE}^{(3)}$                | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -     | 2   | -   | ms   |

| Table 39. HSE 4-2 | 6 MHz oscillator | characteristics <sup>(1)</sup> |

|-------------------|------------------|--------------------------------|

|                   |                  | onaraotoriotioo                |

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. The minimum and maximum values must be respected to comply with USB standard specifications.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

### 6.3.15 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/ESDA/JEDEC JS-001 and ANSI/ESD S5.3.1 standards.

| Symbol                | Ratings                                            | Conditions                                                                                                        | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model) | T <sub>A</sub> = +25 °C conforming to<br>ANSI/ESDA/JEDEC JS-001                                                   | 2     | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device     | $T_A$ = +25 °C conforming to ANSI/ESD S5.3.1,<br>LQFP100/144/176, UFBGA169/176,<br>TFBGA176 and WLCSP143 packages | C3    | 250                             | V    |

| . ()                  | model)                                             | $T_A = +25$ °C conforming to ANSI/ESD S5.3.1,<br>LQFP208 package                                                  | C3    | 250                             |      |

#### Table 53. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

|   | Symbol         Parameter           LU         Static latch-up class |  | Conditions                                    | Class      |  |

|---|---------------------------------------------------------------------|--|-----------------------------------------------|------------|--|

| Ī |                                                                     |  | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |  |

#### Table 54. Electrical sensitivities

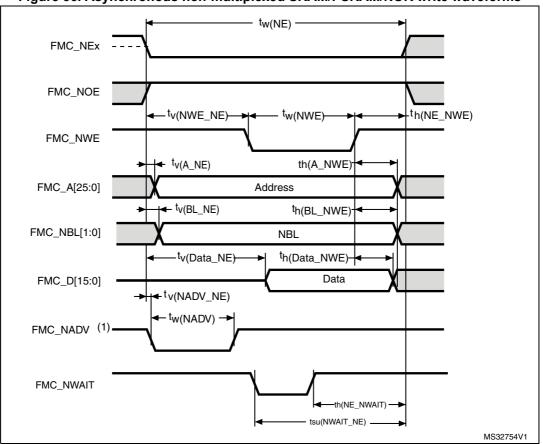

Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

|                          |                                       |                         | •                       |      |

|--------------------------|---------------------------------------|-------------------------|-------------------------|------|

| Symbol                   | Parameter                             | Min                     | Max                     | Unit |

| t <sub>w(NE)</sub>       | FMC_NE low time                       | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NWE_NE)</sub>   | FMC_NEx low to FMC_NWE low            | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                      | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> +1.5  | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid            | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid           | -                       | 1.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid     | -                       | T <sub>HCLK</sub> + 2   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low           | -                       | 0.5                     | ns   |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                     | -                       | T <sub>HCLK</sub> + 0.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

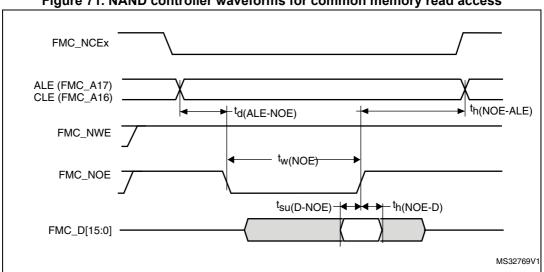

Figure 71. NAND controller waveforms for common memory read access

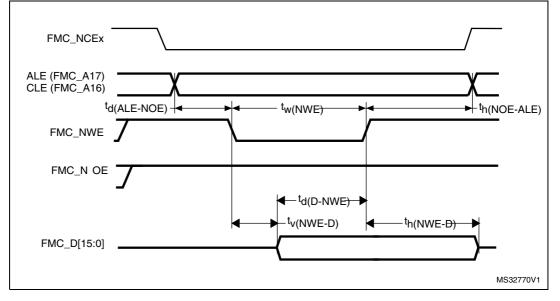

Figure 72. NAND controller waveforms for common memory write access

Table 100. Switching characteristics for NAND Flash read cycles<sup>(1)</sup>

| Symbol                  | Parameter                                  | Min                      | Max                      | Unit |

|-------------------------|--------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> – 0.5 | 4T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 9                        | -                        | ns   |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 0                        | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                        | 3T <sub>HCLK</sub> – 0.5 | ns   |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> – 2   | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

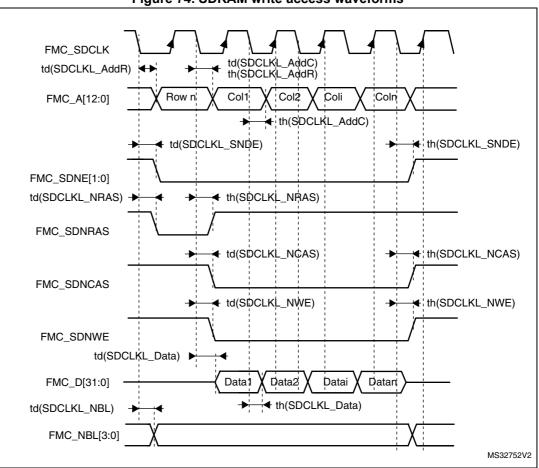

Figure 74. SDRAM write access waveforms

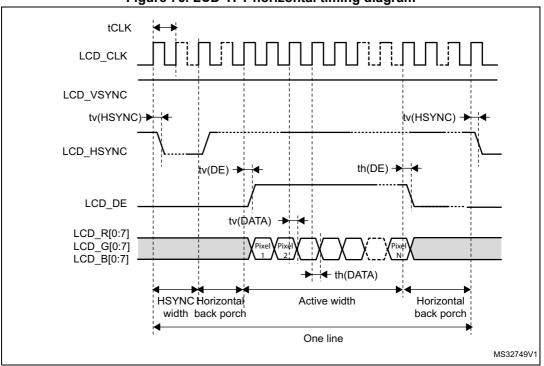

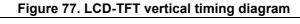

Figure 76. LCD-TFT horizontal timing diagram

| Symbol                              | Parameter                               | Conditions  | Min | Тур | Max | Unit |

|-------------------------------------|-----------------------------------------|-------------|-----|-----|-----|------|

| f <sub>PP</sub>                     | Clock frequency in data transfer mode   |             | 0   |     | 48  | MHz  |

| -                                   | SDIO_CK/fPCLK2 frequency ratio          |             | -   | -   | 8/3 | -    |

| t <sub>W(CKL)</sub>                 | Clock low time                          | fpp =48 MHz | 8.5 | 9   | -   | ns   |

| t <sub>W(CKH)</sub>                 | Clock high time                         | fpp =48 MHz | 8.3 | 10  | -   | 115  |

| CMD, D inp                          | outs (referenced to CK) in MMC and SE   | ) HS mode   |     |     |     |      |

| t <sub>ISU</sub>                    | Input setup time HS                     | fpp =48 MHz | 3.5 | -   | -   |      |

| t <sub>IH</sub>                     | Input hold time HS                      | fpp =48 MHz | 0   | -   | -   | – ns |

| CMD, D ou                           | tputs (referenced to CK) in MMC and S   | D HS mode   |     | •   | •   |      |

| t <sub>OV</sub>                     | Output valid time HS                    | fpp =48 MHz | -   | 4.5 | 7   |      |

| t <sub>OH</sub> Output hold time HS |                                         | fpp =48 MHz | 3   | -   | -   | - ns |

| CMD, D inp                          | outs (referenced to CK) in SD default m | node        |     |     |     |      |

| tISUD                               | Input setup time SD                     | fpp =24 MHz | 1.5 | -   | -   |      |

| tIHD                                | tIHD Input hold time SD                 |             | 0.5 | -   | -   | ns   |

| CMD, D ou                           | tputs (referenced to CK) in SD default  | mode        |     |     |     |      |

| tOVD Output valid default time SD   |                                         | fpp =24 MHz | -   | 4.5 | 6.5 |      |

| tOHD Output hold default time SD    |                                         | fpp =24 MHz | 3.5 |     |     | ns   |

1. Guaranteed by characterization results.

2.  $V_{DD}$  = 2.7 to 3.6 V.

## 6.3.30 RTC characteristics

#### Table 109. RTC characteristics

| Symbol Parameter |                                            | Conditions                                          | Min | Max |

|------------------|--------------------------------------------|-----------------------------------------------------|-----|-----|

| -                | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4   | -   |

| Dimension      | Recommended values                             |  |  |  |  |

|----------------|------------------------------------------------|--|--|--|--|

| Pitch          | 0.4                                            |  |  |  |  |

| Dpad           | 260 µm max. (circular)                         |  |  |  |  |

| ppau           | 220 µm recommended                             |  |  |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |  |  |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |  |  |  |

Table 112. WLCSP143 recommended PCB design rules (0.4 mm pitch)

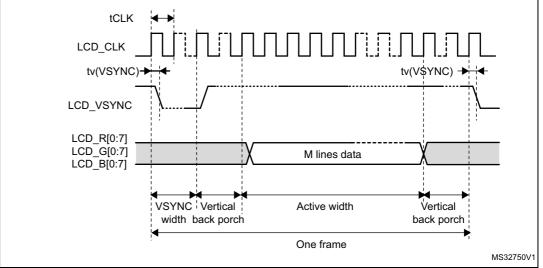

#### **Device marking for WLCSP143**

The following figure gives an example of topside marking orientation versus ball A 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Figure 85. WLCSP143 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Max    | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.874  |

| D1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -           | 17.500 | -      | -                     | 0.689  | -      |

| E      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -           | 17.500 | -      | -                     | 0.6890 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

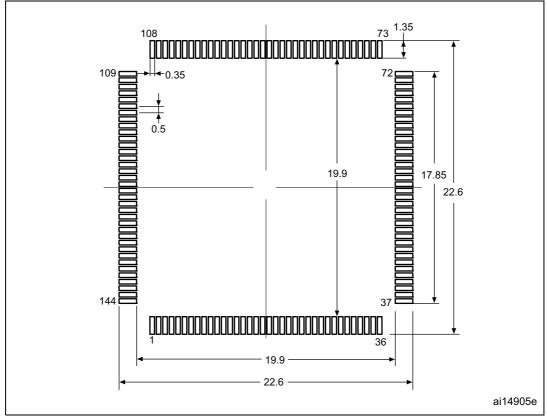

# Table 113. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 87. LQPF144- 144-pin,20 x 20 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

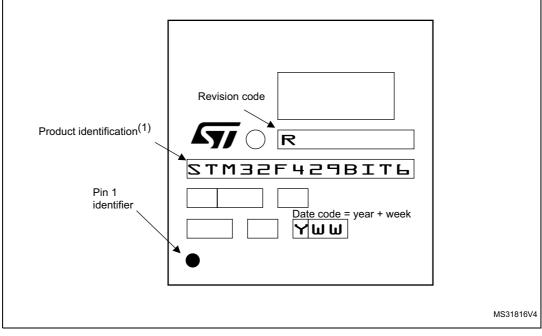

#### **Device marking for LQFP208**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

## Appendix A Recommendations when using internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

- The over-drive mode is not supported.

## A.1 Operating conditions

#### Table 123. Limitations depending on the operating power supply range

| Operating<br>power<br>supply<br>range           | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                           | Possible Flash<br>memory<br>operations        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup> | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(4)</sup>                                                                                   | 168 MHz with 8<br>wait states and<br>over-drive OFF                               | <ul> <li>No I/O compensation</li> </ul> | 8-bit erase and<br>program<br>operations only |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 3.17.1: Internal reset ON).

4. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

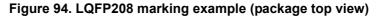

Figure 105. USB controller configured in dual mode and used in full speed mode

- 1. External voltage regulator only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

- 4. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.