Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 168                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 208-LQFP                                                                            |

| Supplier Device Package    | 208-LQFP (28x28)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f429bit7               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.               | Compatible board design STM32F10xx/STM32F2xx/STM32F4xx                               |              |

|-------------------------|--------------------------------------------------------------------------------------|--------------|

|                         | for LQFP100 package                                                                  | 17           |

| Figure 2.               | Compatible board design between STM32F10xx/STM32F2xx/STM32F4xx                       |              |

|                         | for LQFP144 package                                                                  | 18           |

| Figure 3.               | Compatible board design between STM32F2xx and STM32F4xx                              |              |

|                         | for LQFP176 and UFBGA176 packages                                                    | 18           |

| Figure 4.               | STM32F427xx and STM32F429xx block diagram                                            | 19           |

| Figure 5.               | STM32F427xx and STM32F429xx Multi-AHB matrix                                         | 22           |

| Figure 6.               | Power supply supervisor interconnection with internal reset OFF                      | 26           |

| Figure 7.               | PDR_ON control with internal reset OFF                                               | 27           |

| Figure 8.               | Regulator OFF                                                                        | 29           |

| Figure 9.               | Startup in regulator OFF: slow V <sub>DD</sub> slope                                 |              |

| -                       | - power-down reset risen after V <sub>CAP 1</sub> /V <sub>CAP 2</sub> stabilization  | 30           |

| Figure 10.              | Startup in regulator OFF mode: fast V <sub>DD</sub> slope                            |              |

| -                       | - power-down reset risen before V <sub>CAP 1</sub> /V <sub>CAP 2</sub> stabilization | 30           |

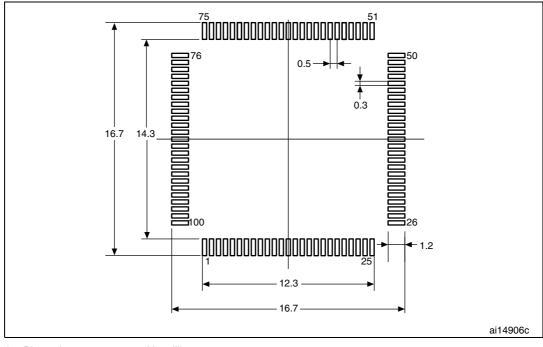

| Figure 11.              | STM32F42x LQFP100 pinout                                                             | 44           |

| Figure 12.              | STM32F42x WLCSP143 ballout                                                           |              |

| Figure 13.              | STM32F42x LQFP144 pinout                                                             | 46           |

| Figure 14.              | STM32F42x LQFP176 pinout                                                             |              |

| Figure 15.              | STM32F42x LQFP208 pinout                                                             |              |

| Figure 16.              | STM32F42x UFBGA169 ballout                                                           |              |

| Figure 17.              | STM32F42x UFBGA176 ballout                                                           |              |

| Figure 18.              | STM32F42x TFBGA216 ballout                                                           |              |

| Figure 19.              | Memory map                                                                           |              |

| Figure 20.              | Pin loading conditions                                                               |              |

| Figure 21.              | Pin input voltage                                                                    |              |

| Figure 22.              | Power supply scheme                                                                  |              |

| Figure 23.              | Current consumption measurement scheme                                               |              |

| Figure 24.              | External capacitor C <sub>FXT</sub>                                                  |              |

| Figure 25.              | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/backup RAM OFF)         |              |

| Figure 26.              | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/backup RAM ON)          |              |

| Figure 27.              | High-speed external clock source AC timing diagram                                   |              |

| Figure 28.              | Low-speed external clock source AC timing diagram                                    |              |

| Figure 29.              | Typical application with an 8 MHz crystal                                            |              |

| Figure 30.              | Typical application with a 32.768 kHz crystal                                        |              |

| Figure 31.              | ACCHSI accuracy versus temperature                                                   |              |

| Figure 32.              | ACC <sub>I SI</sub> versus temperature                                               |              |

| Figure 33.              | PLL output clock waveforms in center spread mode                                     |              |

| Figure 34.              | PLL output clock waveforms in down spread mode                                       |              |

| Figure 35.              | FT I/O input characteristics.                                                        |              |

| Figure 36.              | I/O AC characteristics definition                                                    |              |

| Figure 37.              | Recommended NRST pin protection                                                      |              |

| Figure 38.              | SPI timing diagram - slave mode and CPHA = 0                                         |              |

| Figure 39.              | SPI timing diagram - slave mode and CPHA = 1                                         |              |

| Figure 40.              |                                                                                      |              |

| Figure 41.              | SPI timing diagram - master mode                                                     | 1 <u>4</u> 6 |

| Figure 42.              | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>             | 146          |

| Figure 43.              | SAI master timing waveforms                                                          |              |

| i iguie <del>1</del> 0. |                                                                                      |              |

| Peripher                      | als                      | STM32F427<br>Vx             | STM32F429Vx              | STM32F427<br>Zx | STM32F429Zx               | STM32F427<br>Ax | STM32F429<br>Ax  | STM32F427<br>Ix              | STM32F429lx | STM32F429Bx | STM32F429N |  |  |

|-------------------------------|--------------------------|-----------------------------|--------------------------|-----------------|---------------------------|-----------------|------------------|------------------------------|-------------|-------------|------------|--|--|

|                               | SPI / I <sup>2</sup> S   | 4/2 (ful                    | l duplex) <sup>(2)</sup> |                 |                           |                 | 6/2              | (full duplex) <sup>(2)</sup> |             |             |            |  |  |

|                               | l <sup>2</sup> C         |                             |                          | •               |                           |                 | 3                |                              |             |             |            |  |  |

|                               | USART/<br>UART           |                             |                          |                 |                           |                 | 4/4              |                              |             |             |            |  |  |

| Communication interfaces      | USB OTG<br>FS            |                             |                          |                 |                           |                 | Yes              |                              |             |             |            |  |  |

| Interfaces                    | USB OTG<br>HS            |                             |                          |                 |                           |                 | Yes              |                              |             |             |            |  |  |

|                               | CAN                      |                             | 2                        |                 |                           |                 |                  |                              |             |             |            |  |  |

|                               | SAI                      |                             | 1                        |                 |                           |                 |                  |                              |             |             |            |  |  |

|                               | SDIO                     |                             |                          |                 |                           |                 | Yes              |                              |             |             |            |  |  |

| Camera interface              | 9                        |                             | Yes                      |                 |                           |                 |                  |                              |             |             |            |  |  |

| LCD-TFT (STM3<br>only)        | D-TFT (STM32F429xx<br>/) |                             | Yes                      | No              | Yes                       | No              | Yes              | No                           |             | Yes         |            |  |  |

| Chrom-ART Acc                 | elerator™                |                             |                          | Yes             |                           |                 |                  |                              |             |             |            |  |  |

| GPIOs                         |                          |                             | 82                       |                 | 114                       | 130             |                  |                              | 140 168     |             | 58         |  |  |

| 12-bit ADC                    |                          |                             |                          |                 |                           |                 | 3                |                              |             |             |            |  |  |

| Number of chanr               | nels                     | 16 24                       |                          |                 |                           |                 |                  |                              |             |             |            |  |  |

| 12-bit DAC<br>Number of chanr | nels                     |                             |                          |                 |                           | Yes<br>2        |                  |                              |             |             |            |  |  |

| Maximum CPU f                 | requency                 | 180 MHz                     |                          |                 |                           |                 |                  |                              |             |             |            |  |  |

| Operating voltag              | e                        | 1.8 to 3.6 V <sup>(3)</sup> |                          |                 |                           |                 |                  |                              |             |             |            |  |  |

| Operating tempe               | raturos                  |                             |                          |                 | Ambient te                | emperatures: -  | 40 to +85 °C /-  | 40 to +105 °C                |             |             |            |  |  |

|                               | aures                    |                             |                          |                 | Ju                        | nction tempera  | ture: -40 to + 1 | 125 °C                       |             |             |            |  |  |

| Packages                      |                          | LQ                          | FP100                    |                 | WLCSP143 UF<br>LQFP144 UF |                 |                  | BGA169 UFBGA176<br>LQFP176   |             | LQFP208     | TFBGA216   |  |  |

#### Table 2. STM32F427xx and STM32F429xx features and peripheral counts (continued)

For the LQFP100 package, only FMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package. For UFBGA169 package, only SDRAM, NAND and multiplexed static memories are supported.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

16/238

3. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

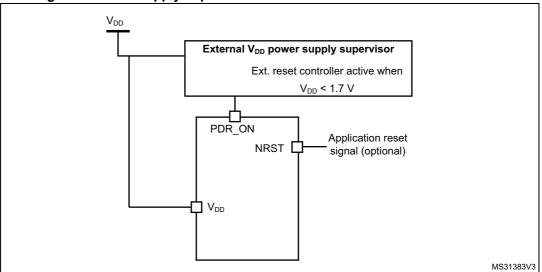

# 3.17.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to this external power supply supervisor. Refer to *Figure 6: Power supply supervisor interconnection with internal reset OFF*.

Figure 6. Power supply supervisor interconnection with internal reset OFF

The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.7 V (see *Figure 7*).

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry must be disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>.

All packages, except for the LQFP100, allow to disable the internal reset through the PDR\_ON signal.

The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode: MR operates in normal mode (default mode of MR in stop mode) MR operates in under-drive mode (reduced leakage mode).

LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to *Table 3* for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 22: Power supply scheme* and *Table 19: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. C means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

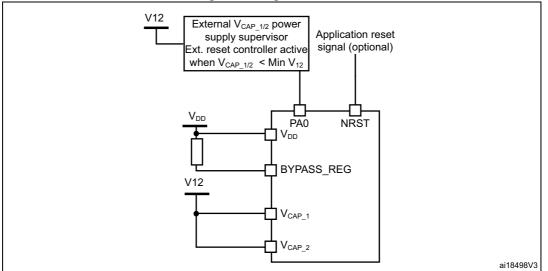

# 3.18.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 17: General operating conditions*. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 22: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below V<sub>12</sub> minimum value and V<sub>DD</sub> is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of  $V_{12}$  depends on the maximum frequency targeted in the application (see Table 17: General operating conditions).

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

# 3.20 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

## Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

## • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

## Table 5. Voltage regulator modes in stop mode

## • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

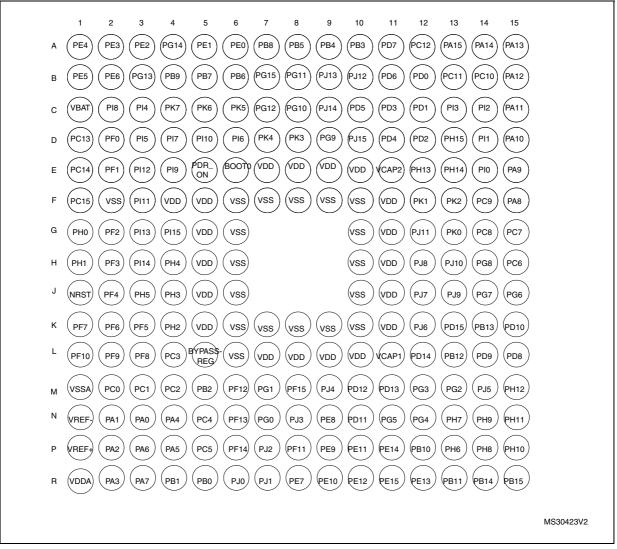

## Figure 18. STM32F42x TFBGA216 ballout

1. The above figure shows the package top view.

|         |         |           | Pin nu   | ımber   | •        |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 82      | 115     | C9        | C12      | 143     | C4       | 165     | C12      | PD1                                                  | I/O      | FT              | -     | CAN1_TX, FMC_D3,<br>EVENTOUT                                                                  | -                       |

| 83      | 116     | В9        | D12      | 144     | A3       | 166     | D12      | PD2                                                  | I/O      | FT              | -     | TIM3_ETR,<br>UART5_RX,<br>SDIO_CMD,<br>DCMI_D11,<br>EVENTOUT                                  | -                       |

| 84      | 117     | A9        | D11      | 145     | B4       | 167     | C11      | PD3                                                  | I/O      | FT              | -     | SPI2_SCK/I2S2_CK,<br>USART2_CTS,<br>FMC_CLK, DCMI_D5,<br>LCD_G7, EVENTOUT                     | -                       |

| 85      | 118     | D8        | D10      | 146     | B5       | 168     | D11      | PD4                                                  | I/O      | FT              | -     | USART2_RTS,<br>FMC_NOE,<br>EVENTOUT                                                           | -                       |

| 86      | 119     | C8        | C11      | 147     | A4       | 169     | C10      | PD5                                                  | I/O      | FT              | -     | USART2_TX,<br>FMC_NWE,<br>EVENTOUT                                                            | -                       |

| -       | 120     | -         | D8       | 148     | -        | 170     | F8       | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 121     | D6        | C8       | 149     | C5       | 171     | E9       | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| 87      | 122     | B8        | B11      | 150     | F4       | 172     | B11      | PD6                                                  | I/O      | FT              | -     | SPI3_MOSI/I2S3_SD,<br>SAI1_SD_A,<br>USART2_RX,<br>FMC_NWAIT,<br>DCMI_D10, LCD_B2,<br>EVENTOUT | -                       |

| 88      | 123     | A8        | A11      | 151     | A5       | 173     | A11      | PD7                                                  | I/O      | FT              | -     | USART2_CK,<br>FMC_NE1/FMC_NCE2,<br>EVENTOUT                                                   | -                       |

| -       | -       | -         | -        | -       | -        | 174     | B10      | PJ12                                                 | I/O      | FT              | -     | LCD_B0, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 175     | B9       | PJ13                                                 | I/O      | FT              | -     | LCD_B1, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 176     | C9       | PJ14                                                 | I/O      | FT              | -     | LCD_B2, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 177     | D10      | PJ15                                                 | I/O      | FT              | -     | LCD_B3, EVENTOUT                                                                              | -                       |

| -       | 124     | NC<br>(2) | C10      | 152     | E5       | 178     | D9       | PG9                                                  | I/O      | FT              | -     | USART6_RX,<br>FMC_NE2/FMC_NCE3,<br>DCMI_VSYNC <sup>(8)</sup> ,<br>EVENTOUT                    | -                       |

Table 10. STM32F427xx and STM32F429xx pin and ball definitions (continued)

DocID024030 Rev 9

| Symbol                             | Deremeter                                            | Conditions                  | £ (MIL)                   | VDD:              | =3.3 V          | VDD               | =1.7 V          | Unit |

|------------------------------------|------------------------------------------------------|-----------------------------|---------------------------|-------------------|-----------------|-------------------|-----------------|------|

| Symbol                             | Parameter                                            | Conditions                  | f <sub>HCLK</sub> (MHz) - | I <sub>DD12</sub> | I <sub>DD</sub> | I <sub>DD12</sub> | I <sub>DD</sub> |      |

|                                    |                                                      |                             | 180                       | 61.5              | 1.4             | -                 | -               |      |

|                                    |                                                      |                             | 168                       | 59.4              | 1.3             | 59.4              | 1.0             |      |

|                                    |                                                      |                             | 150                       | 53.9              | 1.3             | 53.9              | 1.0             |      |

|                                    |                                                      |                             | 144                       | 49.0              | 1.3             | 49.0              | 1.0             |      |

|                                    |                                                      | All Peripherals<br>enabled  | 120                       | 38.0              | 1.2             | 38.0              | 0.9             |      |

|                                    | Supply current<br>in Sleep mode<br>from $V_{12}$ and | enabled                     | 90                        | 29.3              | 1.4             | 29.3              | 1.1             |      |

|                                    |                                                      |                             | 60                        | 20.2              | 1.2             | 20.2              | 0.9             | - mA |

|                                    |                                                      |                             | 30                        | 11.9              | 1.2             | 11.9              | 0.9             |      |

| 1 /1                               |                                                      |                             | 25                        | 10.4              | 1.2             | 10.4              | 0.9             |      |

| I <sub>DD12</sub> /I <sub>DD</sub> |                                                      |                             | 180                       | 14.9              | 1.4             | -                 | -               |      |

|                                    | $V_{DD}$ supply                                      |                             | 168                       | 14.0              | 1.3             | 14.0              | 1.0             |      |

|                                    |                                                      |                             | 150                       | 12.6              | 1.3             | 12.6              | 1.0             |      |

|                                    |                                                      |                             | 144                       | 11.5              | 1.3             | 11.5              | 1.0             |      |

|                                    |                                                      | All Peripherals<br>disabled | 120                       | 8.7               | 1.2             | 8.7               | 0.9             |      |

|                                    |                                                      |                             | 90                        | 7.1               | 1.4             | 7.1               | 1.1             | -    |

|                                    |                                                      |                             | 60                        | 5.0               | 1.2             | 5.0               | 0.9             |      |

|                                    |                                                      |                             | 30                        | 3.1               | 1.2             | 3.1               | 0.9             |      |

|                                    |                                                      |                             | 25                        | 2.8               | 1.2             | 2.8               | 0.9             |      |

| Table 33. Tyical of | urrent consumption in Sleep mode, regulator OFF <sup>(1)</sup> | ) |

|---------------------|----------------------------------------------------------------|---|

|                     |                                                                |   |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC, or DAC) is not included.

|                                         |                                       |                                          |              | ,   |              |      |

|-----------------------------------------|---------------------------------------|------------------------------------------|--------------|-----|--------------|------|

| Symbol                                  | Parameter                             | Conditions                               | Min          | Тур | Мах          | Unit |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$  | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DDA}$ | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 | mA   |

### Table 44. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

## Table 45. PLLISAI (audio and LCD-TFT PLL) characteristics

| Symbol                                  | Parameter                             | Conditions                                                              |                    | Min                 | Тур                                                    | Max          | Unit |

|-----------------------------------------|---------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|--------------------------------------------------------|--------------|------|

| f <sub>PLLSAI_IN</sub>                  | PLLSAI input clock <sup>(1)</sup>     |                                                                         |                    | 0.95 <sup>(2)</sup> | 1                                                      | 2.10         | MHz  |

| f <sub>PLLSAI_OUT</sub>                 | PLLSAI multiplier output clock        |                                                                         |                    | -                   | -                                                      | 216          | MHz  |

| f <sub>VCO_OUT</sub>                    | PLLSAI VCO output                     |                                                                         |                    | 100                 | -                                                      | 432          | MHz  |

| +                                       | PLLSAI lock time                      | VCO freq = 100 MHz                                                      | 2                  | 75                  | -                                                      | 200          |      |

| t <sub>LOCK</sub>                       |                                       | VCO freq = 432 MHz                                                      | 2                  | 100                 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 300          | μs   |

|                                         |                                       | Cycle to cycle at                                                       | RMS                | -                   | 90                                                     | -            |      |

|                                         | Main SAI clock jitter                 | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                            | peak<br>to<br>peak | -                   | ±280                                                   | -            | ps   |

| Jitter <sup>(3)</sup>                   |                                       | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | -                  | 90                  | -                                                      | ps           |      |

|                                         | FS clock jitter                       | Cycle to cycle at 48 on 1000 samples                                    | KHz                | -                   | 400                                                    | -            | ps   |

| I <sub>DD(PLLSAI)</sub> <sup>(4)</sup>  | PLLSAI power consumption on $V_{DD}$  | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.15<br>0.45        | -                                                      | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLSAI)</sub> <sup>(4)</sup> | PLLSAI power consumption on $V_{DDA}$ | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -                                                      | 0.40<br>0.85 | mA   |

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

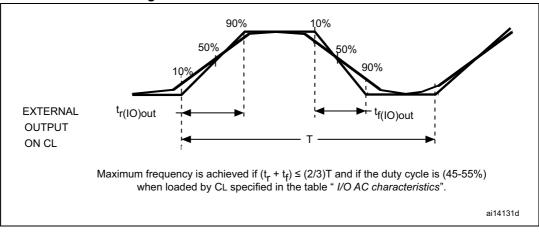

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                      | Min                    | Тур | Мах                | Unit |

|-----------------------------------------------|-------------------------|-----------------------------------------------------------------|-------------------------------------------------|------------------------|-----|--------------------|------|

|                                               |                         |                                                                 | $C_L = 30 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$ | -                      | -   | 100 <sup>(4)</sup> |      |

|                                               |                         | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.8 V | -                      | -   | 50                 |      |

|                                               | f                       |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V | -                      | -   | 42.5               | MHz  |

|                                               | f <sub>max(IO)out</sub> |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                      | -   | 180 <sup>(4)</sup> |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -                      | -   | 100                |      |

| 11                                            |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -                      | -   | 72.5               |      |

|                                               |                         | Output high to low level fall                                   | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -                      | -   | 4                  | - ns |

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.8 V  | -                      | -   | 6                  |      |

|                                               | t <sub>f(IO)out</sub> / |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.7 V  | -                      | -   | 7                  |      |

|                                               | t <sub>r(IO)out</sub>   | time and output low to high level rise time                     | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -                      | -   | 2.5                |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.8 V  | -                      | -   | 3.5                |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.7 V  | V <sub>DD</sub> ≥1.7 V |     | 4                  |      |

| -                                             | tEXTIpw                 | Pulse width of external signals detected by the EXTI controller | -                                               | 10                     | -   | -                  | ns   |

Table 58. I/O AC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by design.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

3. The maximum frequency is defined in *Figure 36*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

## Figure 36. I/O AC characteristics definition

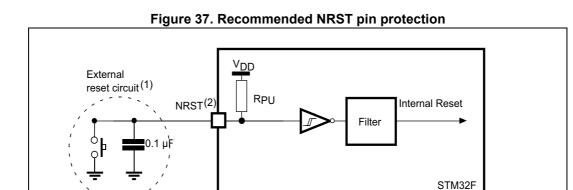

# 6.3.18 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 56: I/O static characteristics*).

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       |                         | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 59. NRST pin characteristics

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

#### 2. Guaranteed by design.

1. The reset network protects the device against parasitic resets.

- 2. The external capacitor must be placed as close as possible to the device.

- 3. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 59*. Otherwise the reset is not taken into account by the device.

ai14132c

# 6.3.19 TIM timer characteristics

The parameters given in Table 60 are guaranteed by design.

Refer to Section 6.3.17: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                       | Conditions <sup>(3)</sup>                                            | Min | Max                     | Unit                 |  |

|------------------------|-------------------------------------------------|----------------------------------------------------------------------|-----|-------------------------|----------------------|--|

|                        |                                                 | AHB/APBx prescaler=1<br>or 2 or 4, f <sub>TIMxCLK</sub> =<br>180 MHz | 1   | -                       | t <sub>TIMxCLK</sub> |  |

| ,                      |                                                 | AHB/APBx prescaler>4,<br>f <sub>TIMxCLK</sub> = 90 MHz               | 1   | -                       | t <sub>TIMxCLK</sub> |  |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 180 MHz                                       | 0   | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| Res <sub>TIM</sub>     | Timer resolution                                |                                                                      | -   | 16/32                   | bit                  |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count with 32-bit counter      |                                                                      | -   | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |  |

| Table 60 | TIMx | characteristics <sup>(1)(2)</sup> |

|----------|------|-----------------------------------|

|----------|------|-----------------------------------|

1. TIMx is used as a general term to refer to the TIM1 to TIM12 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 or APB2 is up to 180 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCKL, otherwise TIMxCLK = 4x PCLKx.

# 6.3.20 Communications interfaces

# I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0090 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 6.3.17: I/O port characteristics for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| r |                 |                                                                                           |     |                    |      |  |  |

|---|-----------------|-------------------------------------------------------------------------------------------|-----|--------------------|------|--|--|

|   | Symbol          | Parameter                                                                                 | Min | Мах                | Unit |  |  |

|   | t <sub>AF</sub> | t <sub>AF</sub> Maximum pulse width of spikes that<br>are suppressed by the analog filter |     | 260 <sup>(3)</sup> | ns   |  |  |

Table 61. I2C analog filter characteristics<sup>(1)</sup>

- 1. Guaranteed by design.

- 2. Spikes with widths below  $t_{AF(min)}$  are filtered.

- 3. Spikes with widths above  $t_{AF(max)}$  are not filtered

# SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 62* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                    | Parameter                            | Conditions                                                   |                             | Min | Тур | Max               | Unit |

|-------------------------------------------|--------------------------------------|--------------------------------------------------------------|-----------------------------|-----|-----|-------------------|------|

|                                           |                                      | Master mode, SPI1/4/5/6,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V     |                             |     |     | 45                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> |                                      | Slave mode,                                                  | Receiver                    | -   | -   | 45                | MHz  |

|                                           | SPI clock frequency                  | SPI1/4/5/6,<br>2.7 V≤V <sub>DD</sub> ≤3.6 V                  | Transmitter/<br>full-duplex |     |     | 38 <sup>(2)</sup> |      |

| "C(SCK)                                   |                                      | Master mode, SPI1/2/3/4/5/6,<br>1.7 V≤V <sub>DD</sub> ≤3.6 V |                             |     |     | 22.5              |      |

|                                           |                                      | Slave mode, SPI1/2/3/4/5/6,<br>1.7 V≤V <sub>DD</sub> ≤3.6 V  |                             | -   | -   | 22.5              |      |

| Duty(SCK)                                 | Duty cycle of SPI clock<br>frequency | Slave mode                                                   |                             | 30  | 50  | 70                | %    |

Table 62. SPI dynamic characteristics<sup>(1)</sup>

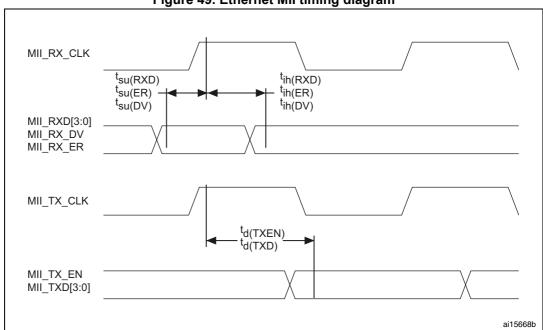

Figure 49. Ethernet MII timing diagram

| Table 73. Dynamics characteristics: Ethernet MAC signals for MII <sup>(1)</sup> |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Symbol               | Parameter                          | Condition                        | Min | Тур | Max | Unit |

|----------------------|------------------------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time            |                                  | 9   | -   | -   |      |

| t <sub>ih(RXD)</sub> | Receive data hold time             |                                  | 10  | -   | -   |      |

| t <sub>su(DV)</sub>  | Data valid setup time              | 1.71 V < V <sub>DD</sub> < 3.6 V | 9   | -   | -   |      |

| t <sub>ih(DV)</sub>  | Data valid hold time               | 1.71 V < V <sub>DD</sub> < 3.0 V | 8   | -   | -   |      |

| t <sub>su(ER)</sub>  | Error setup time                   |                                  | 6   | -   | -   |      |

| t <sub>ih(ER)</sub>  | Error hold time                    |                                  | 8   | -   | -   | ns   |

| +                    | Transmit an able welled delay time | 2.7 V < V <sub>DD</sub> < 3.6 V  | 8   | 10  | 14  |      |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time   | 1.71 V < V <sub>DD</sub> < 3.6 V | 8   | 10  | 16  |      |

| +                    | Transmit data valid delay time     | 2.7 V < V <sub>DD</sub> < 3.6 V  | 7.5 | 10  | 15  |      |

| t <sub>d(TXD)</sub>  | Transmit uata valiu uelay time     | 1.71 V < V <sub>DD</sub> < 3.6 V | 7.5 | 10  | 17  |      |

1. Guaranteed by characterization results.

# CAN (controller area network) interface

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (CANx\_TX and CANx\_RX).

| Symbol                      | Parameter                                | Min                    | Max | Unit |  |  |

|-----------------------------|------------------------------------------|------------------------|-----|------|--|--|

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | 0                      | -   | ns   |  |  |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                      | 0   | ns   |  |  |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> -0.5 | -   | ns   |  |  |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                      | 2.5 | ns   |  |  |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | 0                      | -   | ns   |  |  |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> -0.5 | -   | ns   |  |  |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 4                      |     |      |  |  |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 0                      |     |      |  |  |

## Table 97. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

## PC Card/CompactFlash controller waveforms and timings

*Figure 63* through *Figure 68* represent synchronous waveforms, and *Table 98* and *Table 99* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x04;

- COM.FMC\_WaitSetupTime = 0x07;

- COM.FMC\_HoldSetupTime = 0x04;

- COM.FMC\_HiZSetupTime = 0x00;

- ATT.FMC\_SetupTime = 0x04;

- ATT.FMC\_WaitSetupTime = 0x07;

- ATT.FMC\_HoldSetupTime = 0x04;

- ATT.FMC\_HiZSetupTime = 0x00;

- IO.FMC\_SetupTime = 0x04;

- IO.FMC WaitSetupTime = 0x07;

- IO.FMC\_HoldSetupTime = 0x04;

- IO.FMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period.

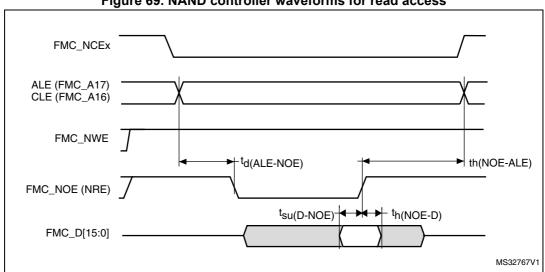

Figure 69. NAND controller waveforms for read access

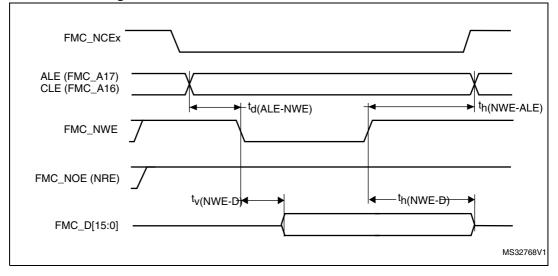

Figure 70. NAND controller waveforms for write access

# Figure 81. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

# 7.6 UFBGA169 package information

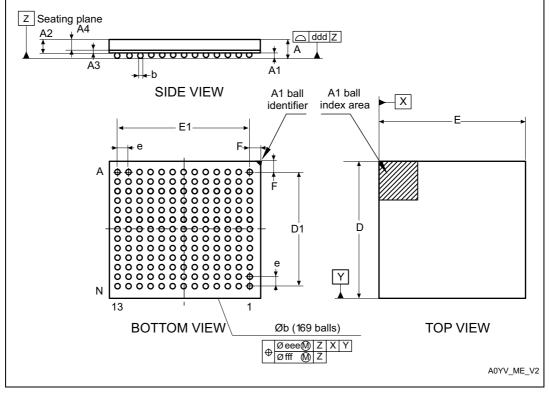

Figure 95. UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 116. UFBGA169 - 169-ball 7 x 7 mm 0.50 mm pitch, ultra fine pitch ball grid arraypackage mechanical data

| Symbol |       | millimeters | ters  |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Мах    |  |

| А      | 0.460 | 0.530       | 0.600 | 0.0181 | 0.0209                | 0.0236 |  |

| A1     | 0.050 | 0.080       | 0.110 | 0.0020 | 0.0031                | 0.0043 |  |

| A2     | 0.400 | 0.450       | 0.500 | 0.0157 | 0.0177                | 0.0197 |  |

| A3     | -     | 0.130       | -     | -      | 0.0051                | -      |  |

| A4     | 0.270 | 0.320       | 0.370 | 0.0106 | 0.0126                | 0.0146 |  |

| b      | 0.230 | 0.280       | 0.330 | 0.0091 | 0.0110                | 0.0130 |  |

| D      | 6.950 | 7.000       | 7.050 | 0.2736 | 0.2756                | 0.2776 |  |

| D1     | 5.950 | 6.000       | 6.050 | 0.2343 | 0.2362                | 0.2382 |  |

| E      | 6.950 | 7.000       | 7.050 | 0.2736 | 0.2756                | 0.2776 |  |

| E1     | 5.950 | 6.000       | 6.050 | 0.2343 | 0.2362                | 0.2382 |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| ultra fine pitch ball grid array package mechanical data (continued) |             |      |       |                       |      |        |  |  |

|----------------------------------------------------------------------|-------------|------|-------|-----------------------|------|--------|--|--|

| Symbol                                                               | millimeters |      |       | inches <sup>(1)</sup> |      |        |  |  |

| Symbol                                                               | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |  |  |

| eee                                                                  | -           | -    | 0.150 | -                     | -    | 0.0059 |  |  |

| fff                                                                  | -           | -    | 0.050 | -                     | -    | 0.0020 |  |  |

# Table 118. UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch,

Values in inches are converted from mm and rounded to 4 decimal digits. 1.

## Figure 99. UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package recommended footprint

| 000000000000000000000000000000000000 |            |

|--------------------------------------|------------|

|                                      | A0E7_FP_V1 |

## Table 119. UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.65 mm                                                          |

| Dpad              | 0.300 mm                                                         |

| Dsm               | 0.400 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.300 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |