#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 168                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 216-TFBGA                                                                           |

| Supplier Device Package    | 216-TFBGA (13x13)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f429ngh6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the description of the STM32F427xx and STM32F429xx line of microcontrollers. For more details on the whole STMicroelectronics STM32 family, please refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F427xx and STM32F429xx datasheet should be read in conjunction with the STM32F4xx reference manual.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214), available from *www.st.com*.

reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

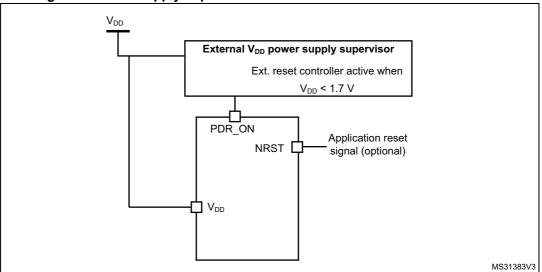

## 3.17.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to this external power supply supervisor. Refer to *Figure 6: Power supply supervisor interconnection with internal reset OFF*.

Figure 6. Power supply supervisor interconnection with internal reset OFF

The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.7 V (see *Figure 7*).

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry must be disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>.

All packages, except for the LQFP100, allow to disable the internal reset through the PDR\_ON signal.

|         |         |           | Pin nu   | ımber   | •        |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|-----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169  | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 82      | 115     | C9        | C12      | 143     | C4       | 165     | C12      | PD1                                                  | I/O      | FT              | -     | CAN1_TX, FMC_D3,<br>EVENTOUT                                                                  | -                       |

| 83      | 116     | В9        | D12      | 144     | A3       | 166     | D12      | PD2                                                  | I/O      | FT              | -     | TIM3_ETR,<br>UART5_RX,<br>SDIO_CMD,<br>DCMI_D11,<br>EVENTOUT                                  | -                       |

| 84      | 117     | A9        | D11      | 145     | B4       | 167     | C11      | PD3                                                  | I/O      | FT              | -     | SPI2_SCK/I2S2_CK,<br>USART2_CTS,<br>FMC_CLK, DCMI_D5,<br>LCD_G7, EVENTOUT                     | -                       |

| 85      | 118     | D8        | D10      | 146     | B5       | 168     | D11      | PD4                                                  | I/O      | FT              | -     | USART2_RTS,<br>FMC_NOE,<br>EVENTOUT                                                           | -                       |

| 86      | 119     | C8        | C11      | 147     | A4       | 169     | C10      | PD5                                                  | I/O      | FT              | -     | USART2_TX,<br>FMC_NWE,<br>EVENTOUT                                                            | -                       |

| -       | 120     | -         | D8       | 148     | -        | 170     | F8       | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 121     | D6        | C8       | 149     | C5       | 171     | E9       | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| 87      | 122     | B8        | B11      | 150     | F4       | 172     | B11      | PD6                                                  | I/O      | FT              | -     | SPI3_MOSI/I2S3_SD,<br>SAI1_SD_A,<br>USART2_RX,<br>FMC_NWAIT,<br>DCMI_D10, LCD_B2,<br>EVENTOUT | -                       |

| 88      | 123     | A8        | A11      | 151     | A5       | 173     | A11      | PD7                                                  | I/O      | FT              | -     | USART2_CK,<br>FMC_NE1/FMC_NCE2,<br>EVENTOUT                                                   | -                       |

| -       | -       | -         | -        | -       | -        | 174     | B10      | PJ12                                                 | I/O      | FT              | -     | LCD_B0, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 175     | B9       | PJ13                                                 | I/O      | FT              | -     | LCD_B1, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 176     | C9       | PJ14                                                 | I/O      | FT              | -     | LCD_B2, EVENTOUT                                                                              | -                       |

| -       | -       | -         | -        | -       | -        | 177     | D10      | PJ15                                                 | I/O      | FT              | -     | LCD_B3, EVENTOUT                                                                              | -                       |

| -       | 124     | NC<br>(2) | C10      | 152     | E5       | 178     | D9       | PG9                                                  | I/O      | FT              | -     | USART6_RX,<br>FMC_NE2/FMC_NCE3,<br>DCMI_VSYNC <sup>(8)</sup> ,<br>EVENTOUT                    | -                       |

Table 10. STM32F427xx and STM32F429xx pin and ball definitions (continued)

DocID024030 Rev 9

## Pinouts and pin description

- 4. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F4xx reference manual, available from the STMicroelectronics website: www.st.com.

- 5. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- If the device is delivered in an WLCSP143, UFBGA169, UFBGA176, LQFP176 or TFBGA216 package, and the BYPASS\_REG pin is set to V<sub>DD</sub> (Regulator OFF/internal reset ON mode), then PA0 is used as an internal Reset (active low).

- 7. PI0 and PI1 cannot be used for I2S2 full-duplex mode.

- 8. The DCMI\_VSYNC alternate function on PG9 is only available on silicon revision 3.

| ~        |  |

|----------|--|

| õ        |  |

| Ñ        |  |

| ω        |  |

| $\infty$ |  |

DocID024030 Rev 9

577

|           |      | AF0           | AF1           | AF2          | AF3              | AF4           | AF5                       | AF6             | AF7                     | AF8                        | AF9                            | AF10                    | AF11                                     | AF12                 | AF13        | AF14          | AF15         |

|-----------|------|---------------|---------------|--------------|------------------|---------------|---------------------------|-----------------|-------------------------|----------------------------|--------------------------------|-------------------------|------------------------------------------|----------------------|-------------|---------------|--------------|

| Р         | ort  | SYS           | TIM1/2        | TIM3/4/5     | TIM8/9/<br>10/11 | l2C1/<br>2/3  | SPI1/2/<br>3/4/5/6        | SPI2/3/<br>SAI1 | SPI3/<br>USART1/<br>2/3 | USART6/<br>UART4/5/7<br>/8 | CAN1/2/<br>TIM12/13/14<br>/LCD | OTG2_HS<br>/OTG1_<br>FS | ЕТН                                      | FMC/SDIO<br>/OTG2_FS | DCMI        | LCD           | SYS          |

|           | PB11 | -             | TIM2_<br>CH4  | -            | -                | I2C2_<br>SDA  | -                         | -               | USART3_<br>RX           | -                          | -                              | OTG_HS_<br>ULPI_D4      | ETH_MII_<br>TX_EN/<br>ETH_RMII<br>_TX_EN | -                    | -           | LCD_G5        | EVEN<br>TOUT |

|           | PB12 | -             | TIM1_<br>BKIN | -            | -                | I2C2_<br>SMBA | SPI2_<br>NSS/I2<br>S2_WS  | -               | USART3_<br>CK           | -                          | CAN2_RX                        | OTG_HS_<br>ULPI_D5      | ETH_MII_<br>TXD0/ETH<br>_RMII_<br>TXD0   | OTG_HS_<br>ID        | -           | -             | EVEN<br>TOUT |

| Port B    | PB13 | -             | TIM1_<br>CH1N | -            | -                | -             | SPI2_<br>SCK/I2<br>S2_CK  | -               | USART3_<br>CTS          | -                          | CAN2_TX                        | OTG_HS_<br>ULPI_D6      | ETH_MII_<br>TXD1/ETH<br>_RMII_TX<br>D1   | -                    | -           | -             | EVEN<br>TOUT |

|           | PB14 | -             | TIM1_<br>CH2N | -            | TIM8_<br>CH2N    | -             | SPI2_<br>MISO             | I2S2ext_<br>SD  | USART3_<br>RTS          | -                          | TIM12_CH1                      | -                       | -                                        | OTG_HS_<br>DM        | -           | -             | EVEN<br>TOUT |

|           | PB15 | RTC_<br>REFIN | TIM1_<br>CH3N | -            | TIM8_<br>CH3N    | -             | SPI2_<br>MOSI/I2<br>S2_SD | -               | -                       | -                          | TIM12_CH2                      | -                       | -                                        | OTG_HS_<br>DP        | -           | -             | EVEN<br>TOUT |

|           | PC0  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | OTG_HS_<br>ULPI_STP     | -                                        | FMC_SDN<br>WE        | -           | -             | EVEN<br>TOUT |

|           | PC1  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | ETH_MDC                                  | -                    | -           | -             | EVEN<br>TOUT |

|           | PC2  | -             | -             | -            | -                | -             | SPI2_<br>MISO             | I2S2ext_<br>SD  | -                       | -                          | -                              | OTG_HS_<br>ULPI_DIR     | ETH_MII_<br>TXD2                         | FMC_<br>SDNE0        | -           | -             | EVEN<br>TOUT |

|           | PC3  | -             | -             | -            | -                | -             | SPI2_<br>MOSI/I2<br>S2_SD | -               | -                       | -                          | -                              | OTG_HS_<br>ULPI_NXT     | ETH_MII_<br>TX_CLK                       | FMC_<br>SDCKE0       | -           | -             | EVEN<br>TOUT |

| Port<br>C | PC4  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>RXD0/ETH<br>_RMII_<br>RXD0   | -                    | -           | -             | EVEN<br>TOUT |

|           | PC5  | -             | -             | -            | -                | -             | -                         | -               | -                       | -                          | -                              | -                       | ETH_MII_<br>RXD1/ETH<br>_RMII_<br>RXD1   | -                    | -           | -             | EVEN<br>TOUT |

|           | PC6  | -             | -             | TIM3_<br>CH1 | TIM8_<br>CH1     | -             | I2S2_<br>MCK              | -               | -                       | USART6_<br>TX              | -                              | -                       | -                                        | SDIO_D6              | DCMI_<br>D0 | LCD_<br>HSYNC | EVEN<br>TOUT |

|           | PC7  | -             | -             | TIM3_<br>CH2 | TIM8_<br>CH2     | -             | -                         | I2S3_<br>MCK    | -                       | USART6_<br>RX              | -                              | -                       | -                                        | SDIO_D7              | DCMI_<br>D1 | LCD_G6        | EVEN<br>TOUT |

# Table 12. STM32F427xx and STM32F429xx alternate function mapping (continued)

|--|

AF0

SYS

-

Port

PJ8

AF1

TIM1/2

\_

DocID024030 Rev 9

84/238

|   |        | PJ9  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_G2 |

|---|--------|------|---|---|---|---|---|---|---|---|---|---|---|---|---|--------|--------|

|   |        | PJ10 | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_G3 |

|   | Port J | PJ11 | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_G4 |

|   | FUILJ  | PJ12 | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_B0 |

|   | PJ13   | -    | - | - | - | - | - | - | - | - | - | - | - | - | - | LCD_B1 |        |

|   |        | PJ14 | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_B2 |

|   |        | PJ15 | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_B3 |

|   |        | PK0  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_G5 |

|   |        | PK1  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_G6 |

|   |        | PK2  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_G7 |

|   | Port K | PK3  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_B4 |

| ſ |        | PK4  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_B5 |

|   |        | PK5  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_B6 |

|   |        | PK6  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_B7 |

|   |        | PK7  | - | - | - | - | - | - | - | - | - | - | - | - | - | -      | LCD_DE |

Table 12. STM32F427xx and STM32F429xx alternate function mapping (continued)

AF7

SPI3/

USART1/

2/3

-

AF8

USART6/

UART4/5/7

/8

-

AF9

CAN1/2/

TIM12/13/14

/LCD

.

AF6

SPI2/3/

SAI1

.

AF11

ETH

-

AF13

DCMI

\_

AF12

FMC/SDIO

/OTG2\_FS

\_

AF14

LCD

LCD\_G1

AF15

SYS

EVEN TOUT

EVEN TOUT

EVEN

TOUT EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN

TOUT EVEN TOUT

EVEN TOUT

EVEN TOUT

AF10

OTG2\_HS /OTG1\_

FS

-

1. The DCMI\_VSYNC alternate function on PG9 is only available on silicon revision 3.

AF3

TIM8/9/

10/11

-

AF2

TIM3/4/5

\_

AF4

I2C1/

2/3

-

AF5

SPI1/2/

3/4/5/6

-

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 8000- 0x4000 FFFF  | Reserved            |

|      | 0x4000 7C00 - 0x4000 7FFF | UART8               |

|      | 0x4000 7800 - 0x4000 7BFF | UART7               |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | Reserved            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | I2C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | Reserved            |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 13. STM32F427xx and STM32F429xx register boundary addresses (continued)

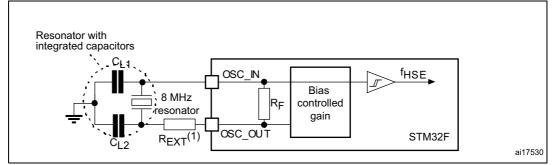

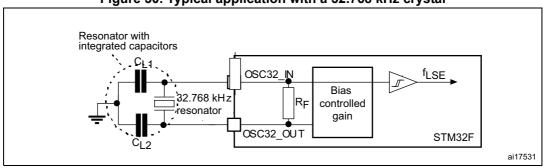

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 29*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                    | Min   | Тур  | Max  | Unit |

|-------------------------------------|-----------------------------------------|-------------------------------|-------|------|------|------|

| R <sub>F</sub>                      | Feedback resistor                       |                               | -     | 18.4 | -    | MΩ   |

| I <sub>DD</sub>                     | LSE current consumption                 |                               | -     | -    | 1    | μA   |

| ACC <sub>LSE</sub> <sup>(2)</sup>   | LSE accuracy                            |                               | - 500 | -    | 500  | ppm  |

| G <sub>m</sub> _crit_max            | Maximum critical crystal g <sub>m</sub> | Startup                       | -     | -    | 0.56 | μA/V |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | startup time                            | V <sub>DD</sub> is stabilized | -     | 2    | -    | s    |

Table 40. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. Refer to application note AN2867.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 30. Typical application with a 32.768 kHz crystal

## 6.3.10 Internal clock source characteristics

The parameters given in *Table 41* and *Table 42* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

## High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                           | Conditions                                   | Min | Тур | Max | Unit |  |  |

|-------------------------------------|-------------------------------------|----------------------------------------------|-----|-----|-----|------|--|--|

| f <sub>HSI</sub>                    | Frequency                           | -                                            | -   | 16  | -   | MHz  |  |  |

| 100                                 | HSI user-trimming step (2)          | -                                            | -   | -   | 1   | %    |  |  |

|                                     |                                     | $T_A = -40$ to 105 °C <sup>(3)</sup>         | - 8 | -   | 4.5 | %    |  |  |

| ACC <sub>HSI</sub>                  | Accuracy of the HSI oscillator      | $T_A = -10 \text{ to } 85 \ ^{\circ}C^{(3)}$ | - 4 | -   | 4   | %    |  |  |

|                                     |                                     | $T_A = 25 \ ^{\circ}C^{(4)}$                 | - 1 | -   | 1   | %    |  |  |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time         | -                                            | -   | 2.2 | 4   | μs   |  |  |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power<br>consumption | -                                            | -   | 60  | 80  | μA   |  |  |

Table 41. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

| Symbol            | Parameter           | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|---------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>BE</sub>   |                     | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 16  | 32                 |      |

|                   | Bank erase time     | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 11  | 22                 | s    |

|                   |                     | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 8   | 16                 |      |

|                   |                     | 32-bit program operation                    | 2.7                | -   | 3.6                | V    |

| V <sub>prog</sub> | Programming voltage | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |

|                   |                     | 8-bit program operation                     | 1.7                | -   | 3.6                | V    |

Table 48. Flash memory programming (continued)

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 100K erase operations.

| Symbol                          | Parameter                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |  |  |  |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|--|--|--|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |  |  |  |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |  |  |  |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |  |  |  |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |  |  |  |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | s    |  |  |  |

| t <sub>BE</sub>                 | Bank erase time                                  |                              | -                  | 6.9 | -                  | s    |  |  |  |

| V <sub>prog</sub>               | Programming voltage                              |                              | 2.7                | -   | 3.6                | V    |  |  |  |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    |                              | 7                  | -   | 9                  | V    |  |  |  |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     |                              | 10                 | -   | -                  | mA   |  |  |  |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied |                              | -                  | -   | 1                  | hour |  |  |  |

| Table 49. Flash memory | programming with | V <sub>PP</sub> |

|------------------------|------------------|-----------------|

|------------------------|------------------|-----------------|

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC<sup>?</sup> code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                     | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Unit |      |

|------------------|------------|--------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|--------------------------------------------------|------|------|

|                  |            |                                                                                | nequency band               | 25/168 MHz                                       | 25/180 MHz                                       |      |      |

|                  |            | V = 3.3 V T = 25 °C + 0 EP 176                                                 | 0.1 to 30 MHz               | 16                                               | 19                                               |      |      |

|                  |            | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C, LQFP176<br>package, conforming to SAE J1752/3 | 30 to 130 MHz               | 23                                               | 23                                               | dBµV |      |

|                  |            | EEMBC, ART ON, all peripheral clocks enabled, clock dithering                  |                             | 130 MHz to<br>1GHz                               | 25                                               | 22   |      |

| S                | Peak level |                                                                                | SAE EMI Level               | 4                                                | 4                                                | dBµV |      |

| S <sub>EMI</sub> |            | $V_{-} = 2.2 V_{-} T_{-} = 25 \circ C_{-} L_{0} = 0.0176$                      | 0.1 to 30 MHz               | 17                                               | 16                                               |      |      |

|                  |            | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C, LQFP176 package, conforming to SAE J1752/3    | 88 11                       | 30 to 130 MHz                                    | 8                                                | 10   | dBµV |

|                  |            | EEMBC, ART ON, all peripheral<br>clocks enabled, clock dithering<br>enabled    | 130 MHz to<br>1GHz          | 11                                               | 16                                               |      |      |

|                  |            |                                                                                | SAE EMI level               | 3.5                                              | 3.5                                              | -    |      |

### Table 52. EMI characteristics

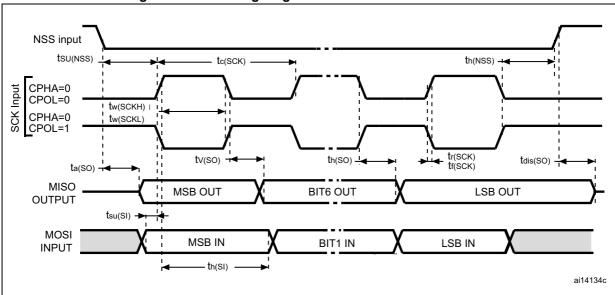

Figure 38. SPI timing diagram - slave mode and CPHA = 0

| Symbol                  | Parameter                                                                          | Min        | Тур    | Max | Unit   |     |

|-------------------------|------------------------------------------------------------------------------------|------------|--------|-----|--------|-----|

|                         | f <sub>HCLK</sub> value to guarantee proper operation of USB HS interface          |            | 30     | -   | -      | MHz |

| F <sub>START_8BIT</sub> | Frequency (first transition)                                                       | 8-bit ±10% | 54     | 60  | 66     | MHz |

| F <sub>STEADY</sub>     | Frequency (steady state) ±500 ppm                                                  |            | 59.97  | 60  | 60.03  | MHz |

| D <sub>START_8BIT</sub> | Duty cycle (first transition) 8-bit ±10%                                           |            | 40     | 50  | 60     | %   |

| D <sub>STEADY</sub>     | Duty cycle (steady state) ±500 ppm                                                 |            | 49.975 | 50  | 50.025 | %   |

| t <sub>STEADY</sub>     | Time to reach the steady state frequency and duty cycle after the first transition |            | -      | -   | 1.4    | ms  |

| t <sub>START_DEV</sub>  | Clock startup time after the                                                       | Peripheral | -      | -   | 5.6    | ma  |

| t <sub>START_HOST</sub> | de-assertion of SuspendM                                                           | Host       | -      | -   | -      | ms  |

| t <sub>PREP</sub>       | PHY preparation time after the first transition of the input clock                 |            | -      | -   | -      | μs  |

| Table 69. USB HS | clock timina | parameters <sup>(1)</sup> |

|------------------|--------------|---------------------------|

|------------------|--------------|---------------------------|

1. Guaranteed by design.

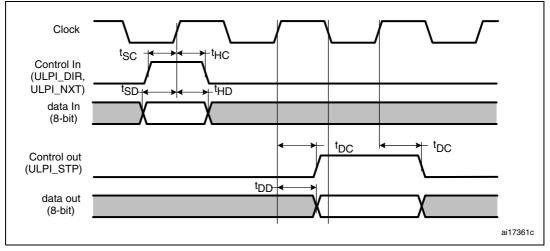

## Figure 46. ULPI timing diagram

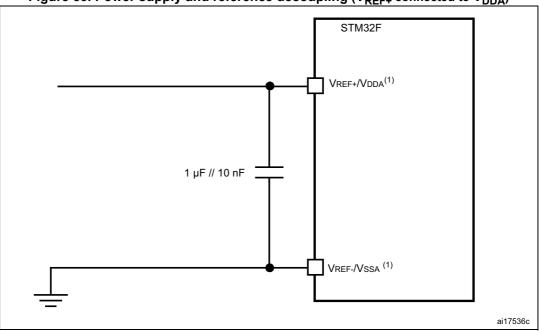

Figure 53. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA176.  $V_{REF+}$  is also available on LQFP100, LQFP144, and LQFP176. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

## 6.3.22 Temperature sensor characteristics

| Table 80. Temperature sensor characteristics | 6   |   |

|----------------------------------------------|-----|---|

| Parameter                                    | Min | т |

| Symbol                             | Parameter                                                      | Min | Тур  | Max | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | ±2  | °C    |

| Avg_Slope <sup>(1</sup>            | Average slope                                                  | -   | 2.5  |     | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 |     | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -   | 6    | 10  | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -   | μs    |

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Symbol  | Parameter                                                            | Memory address            |

|---------|----------------------------------------------------------------------|---------------------------|

| TS_CAL1 | TS ADC raw data acquired at temperature of 30 °C, $V_{DDA}$ = 3.3 V  | 0x1FFF 7A2C - 0x1FFF 7A2D |

| TS_CAL2 | TS ADC raw data acquired at temperature of 110 °C, $V_{DDA}$ = 3.3 V | 0x1FFF 7A2E - 0x1FFF 7A2F |

## Table 81. Temperature sensor calibration values

| Symbol                      | Parameter                                  | Min                    | Max | Unit |

|-----------------------------|--------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period, VDD range= 2.7 to 3.6 V    | 2T <sub>HCLK</sub> – 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                      | 1.5 | ns   |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub>      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -                      | 0   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 0                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -                      | 0   | ns   |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>      | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -                      | 0   | ns   |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high               | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -                      | 3   | ns   |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0                      | -   | ns   |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -                      | 3   | ns   |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | 0                      | -   | ns   |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | T <sub>HCLK</sub> -0.5 | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 4                      | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 0                      | -   | ns   |

Table 95. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

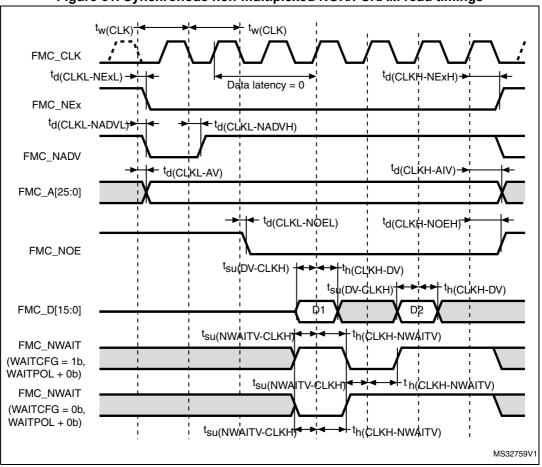

Figure 61. Synchronous non-multiplexed NOR/PSRAM read timings

| Table 96. Synchronous non-multiplexed NOR/PSRAM read timings | 1)(2) |

|--------------------------------------------------------------|-------|

|--------------------------------------------------------------|-------|

| Symbol                         | Parameter                                  | Min                     | Max                  | Unit |

|--------------------------------|--------------------------------------------|-------------------------|----------------------|------|

| t <sub>w(CLK)</sub>            | FMC_CLK period                             | 2T <sub>HCLK</sub> – 1  | -                    | ns   |

| t <sub>(CLKL-NExL)</sub>       | FMC_CLK low to FMC_NEx low (x=02)          | -                       | 0.5                  | ns   |

| t <sub>d(CLKH-</sub><br>NExH)  | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub>       | -                    | ns   |

| t <sub>d(CLKL-</sub><br>NADVL) | FMC_CLK low to FMC_NADV low                | -                       | 0                    | ns   |

| t <sub>d(CLKL-</sub><br>NADVH) | FMC_CLK low to FMC_NADV high               | 0                       | -                    | ns   |

| t <sub>d(CLKL-AV)</sub>        | FMC_CLK low to FMC_Ax valid (x=1625)       | -                       | 0                    | ns   |

| t <sub>d(CLKH-AIV)</sub>       | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub> – 0.5 | -                    | ns   |

| t <sub>d(CLKL-NOEL)</sub>      | FMC_CLK low to FMC_NOE low                 | -                       | T <sub>HCLK</sub> +2 | ns   |

| t <sub>d(CLKH-</sub><br>NOEH)  | FMC_CLK high to FMC_NOE high               | T <sub>HCLK</sub> – 0.5 | -                    | ns   |

| t <sub>su(DV-CLKH)</sub>       | FMC_D[15:0] valid data before FMC_CLK high | 5                       | -                    | ns   |

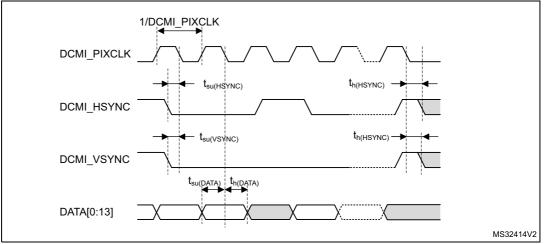

# 6.3.27 Camera interface (DCMI) timing specifications

Unless otherwise specified, the parameters given in *Table 106* for DCMI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 17*, with the following configuration:

- DCMI\_PIXCLK polarity: falling

- DCMI\_VSYNC and DCMI\_HSYNC polarity: high

- Data formats: 14 bits

| Symbol                                           | Symbol Parameter                              |     | Max | Unit |  |  |

|--------------------------------------------------|-----------------------------------------------|-----|-----|------|--|--|

|                                                  | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | -   | 0.4 |      |  |  |

| DCMI_PIXCLK                                      | Pixel clock input                             | -   | 54  | MHz  |  |  |

| D <sub>Pixel</sub>                               | Pixel clock input duty cycle                  | 30  | 70  | %    |  |  |

| t <sub>su(DATA)</sub>                            | Data input setup time                         | 2   | -   |      |  |  |

| t <sub>h(DATA)</sub>                             | Data input hold time                          | 2.5 | -   |      |  |  |

| t <sub>su(HSYNC)</sub><br>t <sub>su(VSYNC)</sub> | DCMI_HSYNC/DCMI_VSYNC input setup time        | 0.5 | -   | ns   |  |  |

| t <sub>h(HSYNC)</sub><br>t <sub>h(VSYNC)</sub>   | DCMI_HSYNC/DCMI_VSYNC input hold time         | 1   | -   |      |  |  |

## Table 106. DCMI characteristics

## Figure 75. DCMI timing diagram

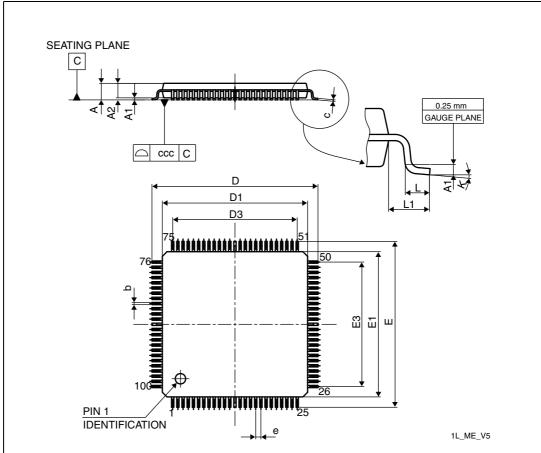

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 7.1 LQFP100 package information

Figure 80. LQFP100 -100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| ult    | ultra fine pitch ball grid array package mechanical data (continued) |             |       |      |                       |        |  |

|--------|----------------------------------------------------------------------|-------------|-------|------|-----------------------|--------|--|

| Symbol |                                                                      | millimeters |       |      | inches <sup>(1)</sup> |        |  |

| Symbol | Min.                                                                 | Тур.        | Max.  | Min. | Тур.                  | Max.   |  |

| eee    | -                                                                    | -           | 0.150 | -    | -                     | 0.0059 |  |

| fff    | -                                                                    | -           | 0.050 | -    | -                     | 0.0020 |  |

# Table 118. UFBGA176+25 - ball, 10 x 10 mm, 0.65 mm pitch,

Values in inches are converted from mm and rounded to 4 decimal digits. 1.

## Figure 99. UFBGA176+25-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package recommended footprint

| 000000000000000000000000000000000000 |            |

|--------------------------------------|------------|

|                                      | A0E7_FP_V1 |

## Table 119. UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.65 mm                                                          |

| Dpad              | 0.300 mm                                                         |

| Dsm               | 0.400 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.300 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

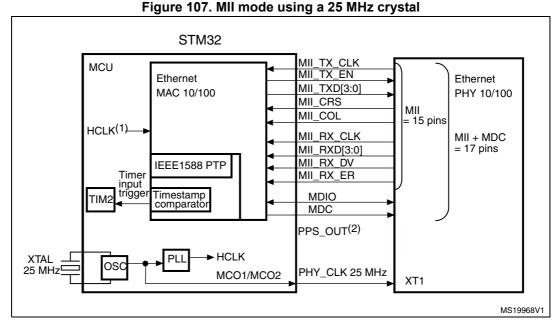

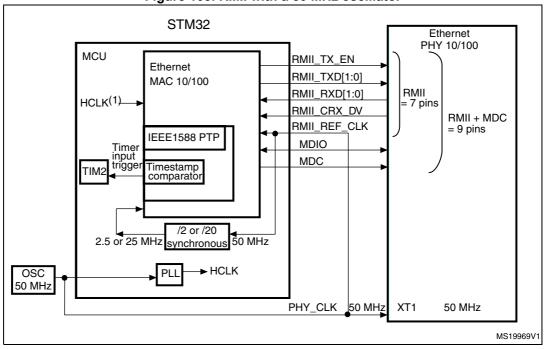

# **B.3** Ethernet interface solutions

1.  $f_{HCLK}$  must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

## Figure 108. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.