# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| υ | e | τ | a | IS |

|---|---|---|---|----|

|   |   |   |   |    |

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f429vit6               |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Introduction

This datasheet provides the description of the STM32F427xx and STM32F429xx line of microcontrollers. For more details on the whole STMicroelectronics STM32 family, please refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F427xx and STM32F429xx datasheet should be read in conjunction with the STM32F4xx reference manual.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214), available from *www.st.com*.

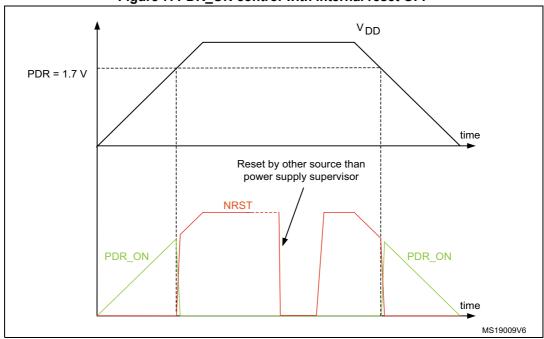

Figure 7. PDR ON control with internal reset OFF

## 3.18 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

## 3.18.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR mode used in Run/sleep modes or in Stop modes

- In Run/Sleep mode

The MR mode is used either in the normal mode (default mode) or the over-drive mode (enabled by software). Different voltages scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

| Timer<br>type        | Timer               | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz)<br>(1) |

|----------------------|---------------------|-----------------------|-------------------------|---------------------------------------------|------------------------------|---------------------------------|-------------------------|------------------------------------|---------------------------------------|

| Advanced<br>-control | TIM1,<br>TIM8       | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | Yes                     | 90                                 | 180                                   |

|                      | TIM2,<br>TIM5       | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                      | 45                                 | 90/180                                |

|                      | TIM3,<br>TIM4       | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 4                               | No                      | 45                                 | 90/180                                |

| General              | TIM9                | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                      | 90                                 | 180                                   |

| purpose              | TIM10<br>,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                      | 90                                 | 180                                   |

|                      | TIM12               | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 2                               | No                      | 45                                 | 90/180                                |

|                      | TIM13<br>,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | No                           | 1                               | No                      | 45                                 | 90/180                                |

| Basic                | TIM6,<br>TIM7       | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and<br>65536 | Yes                          | 0                               | No                      | 45                                 | 90/180                                |

Table 6. Timer feature comparison

1. The maximum timer clock is either 90 or 180 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

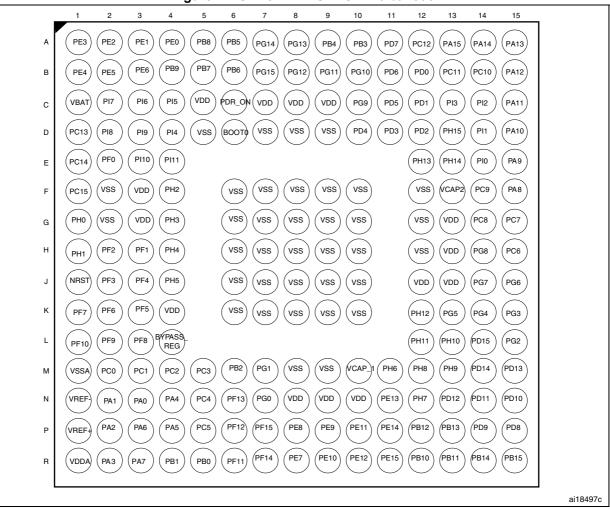

Figure 17. STM32F42x UFBGA176 ballout

1. The above figure shows the package top view.

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 1.7 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

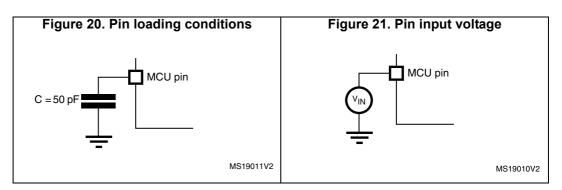

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 20*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 21*.

|                       |                                                                                                             |                                                                                                                                                                                                                                 | Тур                       |                           |                           |                                          |      |

|-----------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|------------------------------------------|------|

| Symbol                | Parameter                                                                                                   | Conditions                                                                                                                                                                                                                      | тур                       | V <sub>DD</sub> = 3.6 V   |                           |                                          | Unit |

|                       |                                                                                                             |                                                                                                                                                                                                                                 | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C               |      |

| UD_STOP_NM            | Supply current in Stop mode with voltage                                                                    | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                                                                                                                   | 0.40                      | 1.50                      | 14.00                     | 25.00                                    |      |

|                       | regulator in main<br>regulator mode                                                                         | Flash memory in Deep power<br>down mode, all oscillators OFF, no<br>independent watchdog                                                                                                                                        | 0.35                      | 1.50                      | 14.00                     | 25.00                                    |      |

| (normal mode)         | Supply current in Stop<br>mode with voltage                                                                 | Flash memory in Stop mode, all<br>oscillators OFF, no independent<br>watchdog                                                                                                                                                   | 0.29                      | 1.10                      | 10.00                     | 00 18.00                                 |      |

|                       | regulator in Low Power<br>regulator mode                                                                    | ply current in Stop<br>le with voltage<br>ilator in Low Power<br>ilator modeoscillators OFF, no independent<br>watchdog0.291.10Flash memory in Deep power<br>down mode, all oscillators OFF, no<br>independent watchdog0.231.10 | 1.10                      | 10.00                     | 18.00                     | mA                                       |      |

| IDD_STOP_UDM          | Supply current in Stop<br>mode with voltage<br>regulator in main<br>regulator and under-<br>drive mode      | Flash memory in Deep power<br>down mode, main regulator in<br>under-drive mode, all oscillators<br>OFF, no independent watchdog                                                                                                 | 0.19                      | 0.50                      | 6.00                      | 9.00                                     |      |

| (under-drive<br>mode) | Supply current in Stop<br>mode with voltage<br>regulator in Low Power<br>regulator and under-<br>drive mode | Flash memory in Deep power<br>down mode, Low Power regulator<br>in under-drive mode, all oscillators<br>OFF, no independent watchdog                                                                                            | 0.10                      | 0.40                      | 4.00                      | $T_{A} = 105 °C$ 25.00 25.00 18.00 18.00 |      |

| Table 27. Typical and maximum current consumptions in Stop mo |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

1. Data based on characterization, tested in production.

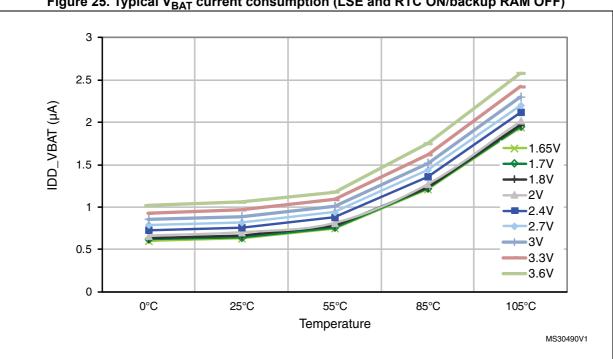

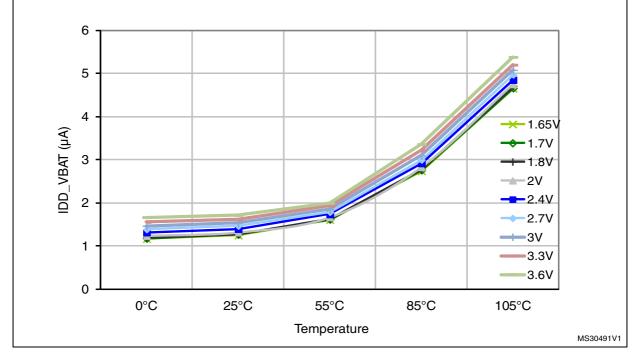

Figure 25. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/backup RAM OFF)

Figure 26. Typical  $V_{BAT}$  current consumption (LSE and RTC ON/backup RAM ON)

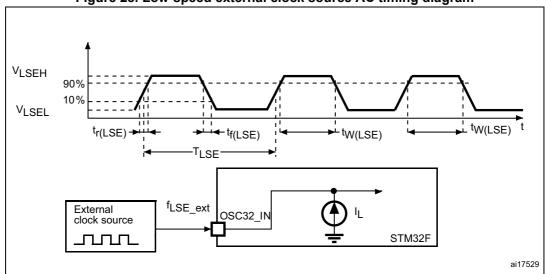

Figure 28. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                            | Parameter                               | Conditions                                                            | Min   | Тур | Max | Unit |

|-----------------------------------|-----------------------------------------|-----------------------------------------------------------------------|-------|-----|-----|------|

| f <sub>OSC_IN</sub>               | Oscillator frequency                    |                                                                       | 4     | -   | 26  | MHz  |

| R <sub>F</sub>                    | Feedback resistor                       |                                                                       | -     | 200 | -   | kΩ   |

|                                   | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -     | 450 | -   | μA   |

| IDD                               |                                         | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -     | 530 | -   | μΑ   |

| ACC <sub>HSE</sub> <sup>(2)</sup> | HSE accuracy                            |                                                                       | - 500 | -   | 500 | ppm  |

| G <sub>m</sub> _crit_max          | Maximum critical crystal g <sub>m</sub> | Startup                                                               | -     | -   | 1   | mA/V |

| $t_{SU(HSE}^{(3)}$                | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -     | 2   | -   | ms   |

| Table 39. HSE 4-2 | 6 MHz oscillator | characteristics <sup>(1)</sup> |

|-------------------|------------------|--------------------------------|

|                   |                  | onaraotoriotioo                |

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. The minimum and maximum values must be respected to comply with USB standard specifications.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

## 6.3.12 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 52: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup>  | Unit |

|-------------------|-----------------------|------|-----|---------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                  | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                   | %    |

| MODEPER * INCSTEP |                       | -    | -   | 2 <sup>15</sup> – 1 | -    |

| Table 46. SSCO | parameters constraint |

|----------------|-----------------------|

|----------------|-----------------------|

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL IN} / (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15}-1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$md_{guantized} \% = (250 \times 126 \times 100 \times 5) / ((2^{15} - 1) \times 240) = 2.002\%$ (peak)

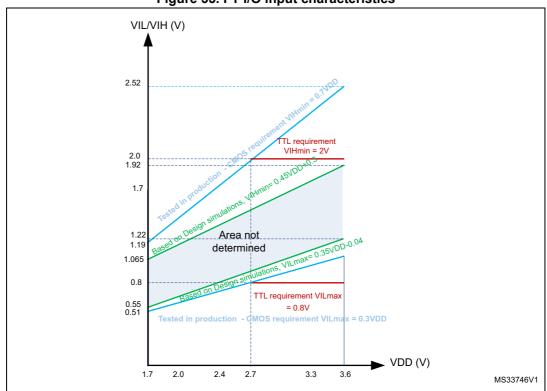

Figure 35. FT I/O input characteristics

## **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14, PC15 and PI8 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 and PI8 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15*).

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                                       | Conditions                                      | Min | Тур | Мах                | Unit |

|-----------------------------------------------|-------------------------|---------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|--------------------|------|

|                                               |                         |                                                                                 | $C_L = 30 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$ | -   | -   | 100 <sup>(4)</sup> |      |

|                                               | 6                       |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 50                 |      |

|                                               |                         | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 42.5               | MHz  |

|                                               | f <sub>max(IO)out</sub> |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 180 <sup>(4)</sup> | MHZ  |

|                                               |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 100                |      |

| 11                                            |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 72.5               |      |

|                                               |                         | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V                                 | -                                               | -   | 4   |                    |      |

|                                               |                         | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 6                  | - ns |

|                                               | t <sub>f(IO)out</sub> / |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 7                  |      |

|                                               | t <sub>r(IO)out</sub>   |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 2.5                |      |

|                                               |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 3.5                |      |

|                                               |                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 4                  |      |

| -                                             | tEXTIpw                 | Pulse width of external signals detected by the EXTI controller                 | -                                               | 10  | -   | -                  | ns   |

Table 58. I/O AC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by design.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

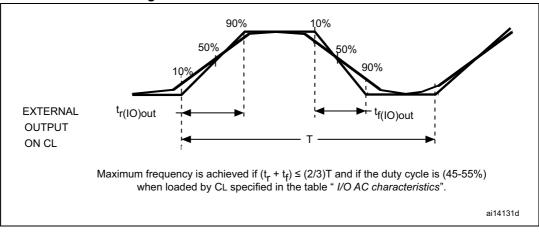

3. The maximum frequency is defined in *Figure 36*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

## Figure 36. I/O AC characteristics definition

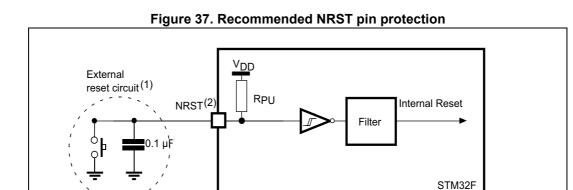

## 6.3.18 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 56: I/O static characteristics*).

Unless otherwise specified, the parameters given in *Table 59* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       |                         | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 59. NRST pin characteristics

1. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

#### 2. Guaranteed by design.

1. The reset network protects the device against parasitic resets.

- 2. The external capacitor must be placed as close as possible to the device.

- 3. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 59*. Otherwise the reset is not taken into account by the device.

ai14132c

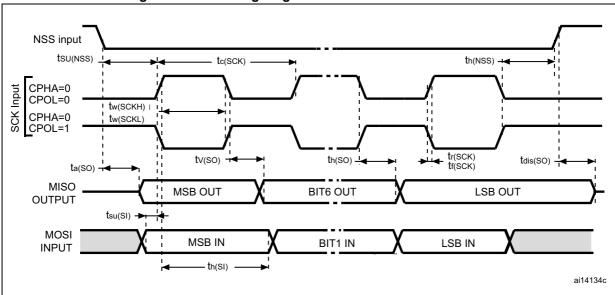

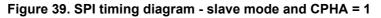

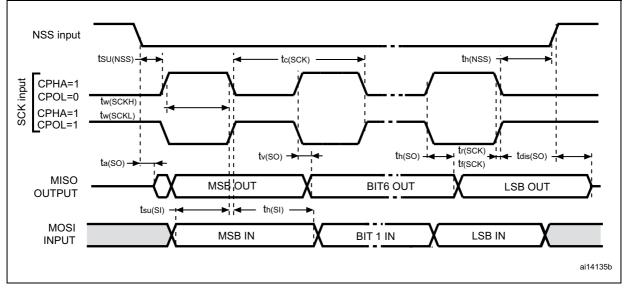

Figure 38. SPI timing diagram - slave mode and CPHA = 0

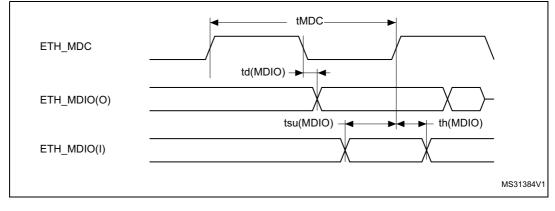

#### **Ethernet characteristics**

Unless otherwise specified, the parameters given in *Table 71*, *Table 72* and *Table 73* for SMI, RMII and MII are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 17* with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF for  $2.7 \text{ V} < \text{V}_{\text{DD}} < 3.6 \text{ V}$

- Capacitive load C = 20 pF for  $1.71 \text{ V} < \text{V}_{\text{DD}} < 3.6 \text{ V}$

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

*Table 71* gives the list of Ethernet MAC signals for the SMI (station management interface) and *Figure 47* shows the corresponding timing diagram.

| Symbol                | Parameter                | Min | Тур | Мах | Unit |

|-----------------------|--------------------------|-----|-----|-----|------|

| t <sub>MDC</sub>      | MDC cycle time(2.38 MHz) | 411 | 420 | 425 |      |

| T <sub>d(MDIO)</sub>  | Write data valid time    | 6   | 10  | 13  | ns   |

| t <sub>su(MDIO)</sub> | Read data setup time     | 12  | -   | -   | 115  |

| t <sub>h(MDIO)</sub>  | Read data hold time      | 0   | -   | -   |      |

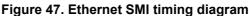

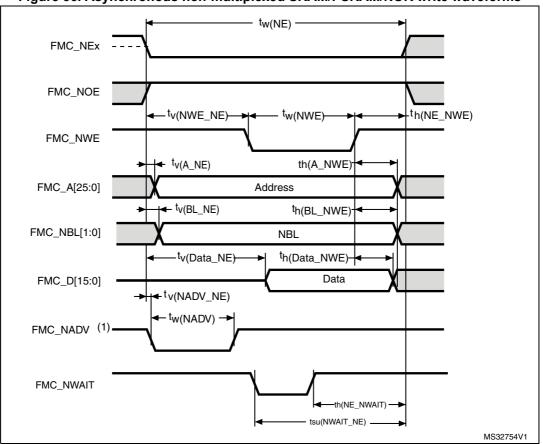

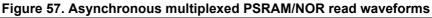

Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

|                          |                                       |                         | •                       |      |

|--------------------------|---------------------------------------|-------------------------|-------------------------|------|

| Symbol                   | Parameter                             | Min                     | Max                     | Unit |

| t <sub>w(NE)</sub>       | FMC_NE low time                       | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NWE_NE)</sub>   | FMC_NEx low to FMC_NWE low            | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                      | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> +1.5  | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid            | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid           | -                       | 1.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid     | -                       | T <sub>HCLK</sub> + 2   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low           | -                       | 0.5                     | ns   |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                     | -                       | T <sub>HCLK</sub> + 0.5 | ns   |

1. C<sub>L</sub> = 30 pF.

| NWAIT timings('//²/       |                                           |                         |                       |      |

|---------------------------|-------------------------------------------|-------------------------|-----------------------|------|

| Symbol                    | Parameter                                 | Min                     | Max                   | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> +1   | 8T <sub>HCLK</sub> +2 | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> – 1  | 6T <sub>HCLK</sub> +2 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                     | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   |                       | ns   |

Table 89. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings^{(1)(2)}

1. C<sub>L</sub> = 30 pF.

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 2                        | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                        | 1.5                     |      |

| t <sub>d</sub> (SDCLKL- SDNE) | Chip select valid time | -                        | 0.5                     | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                       |      |

## Table 102. SDRAM read timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

## Table 103. LPSDR SDRAM read timings<sup>(1)(2)</sup>

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |  |

|-------------------------------|------------------------|--------------------------|-------------------------|------|--|

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |  |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time  | 2.5                      | -                       |      |  |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |  |

| t <sub>d</sub> (SDCLKL_Add)   | Address valid time     | -                        | 1                       |      |  |

| t <sub>d</sub> (SDCLKL_SDNE)  | Chip select valid time | -                        | 1                       | ns   |  |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 1                        | -                       | 115  |  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time      | -                        | 1                       |      |  |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 1                        | -                       |      |  |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 1                       |      |  |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 1                        | -                       |      |  |

1. CL = 10 pF.

## 6.3.29 SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 108* for the SDIO/MMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

#### Figure 78. SDIO high-speed mode

Figure 79. SD default mode

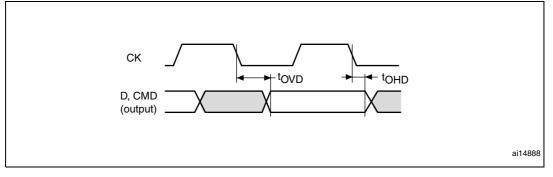

#### **Device marking for LQFP176**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Figure 91. LQFP176 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

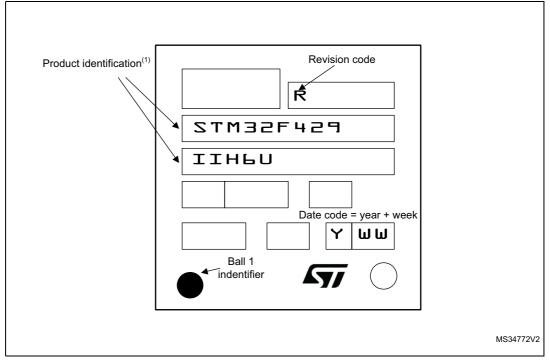

#### **Device marking for UFBGA176+25**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.