# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| υ | e | C | а | IS |

|---|---|---|---|----|

|   |   |   |   |    |

| 2000                       |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Active                                                                              |

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 82                                                                                  |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-LQFP                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f429vit6tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the description of the STM32F427xx and STM32F429xx line of microcontrollers. For more details on the whole STMicroelectronics STM32 family, please refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F427xx and STM32F429xx datasheet should be read in conjunction with the STM32F4xx reference manual.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214), available from *www.st.com*.

| Peripher                      | als                      | STM32F427<br>Vx | STM32F429Vx              | STM32F427<br>Zx | STM32F429Zx      | STM32F427<br>Ax | STM32F429<br>Ax        | STM32F427<br>Ix                  | STM32F429lx      | STM32F429Bx | STM32F429N |  |  |

|-------------------------------|--------------------------|-----------------|--------------------------|-----------------|------------------|-----------------|------------------------|----------------------------------|------------------|-------------|------------|--|--|

|                               | SPI / I <sup>2</sup> S   | 4/2 (ful        | l duplex) <sup>(2)</sup> |                 |                  |                 | 6/2                    | 6/2 (full duplex) <sup>(2)</sup> |                  |             |            |  |  |

|                               | l <sup>2</sup> C         |                 |                          | •               |                  |                 | 3                      |                                  |                  |             |            |  |  |

|                               | USART/<br>UART           |                 |                          |                 |                  |                 | 4/4                    |                                  |                  |             |            |  |  |

| Communication interfaces      | USB OTG<br>FS            |                 |                          |                 |                  |                 | Yes                    |                                  |                  |             |            |  |  |

| Interfaces                    | USB OTG<br>HS            |                 |                          |                 |                  |                 | Yes                    |                                  |                  |             |            |  |  |

|                               | CAN                      |                 |                          |                 |                  |                 | 2                      |                                  |                  |             |            |  |  |

|                               | SAI                      |                 | 1                        |                 |                  |                 |                        |                                  |                  |             |            |  |  |

|                               | SDIO                     |                 |                          |                 |                  |                 | Yes                    |                                  |                  |             |            |  |  |

| Camera interface              | mera interface           |                 | Yes                      |                 |                  |                 |                        |                                  |                  |             |            |  |  |

| LCD-TFT (STM3<br>only)        | D-TFT (STM32F429xx<br>/) |                 | Yes                      | No              | Yes              | No              | Yes                    | No                               | Yes              |             |            |  |  |

| Chrom-ART Acc                 | elerator™                |                 |                          |                 |                  |                 | Yes                    |                                  |                  |             |            |  |  |

| GPIOs                         |                          | 82              |                          |                 | 114              | 130             |                        | 140                              |                  | 168         |            |  |  |

| 12-bit ADC                    |                          |                 | 3                        |                 |                  |                 |                        |                                  |                  |             |            |  |  |

| Number of chanr               | nels                     |                 | 16                       |                 | 24               |                 |                        |                                  |                  |             |            |  |  |

| 12-bit DAC<br>Number of chanr | nels                     |                 |                          |                 |                  |                 | Yes<br>2               |                                  |                  |             |            |  |  |

| Maximum CPU f                 | requency                 |                 |                          |                 |                  | 18              | 0 MHz                  |                                  |                  |             |            |  |  |

| Operating voltag              | e                        |                 |                          |                 |                  | 1.8 to          | o 3.6 V <sup>(3)</sup> |                                  |                  |             |            |  |  |

| Operating tempe               | raturos                  |                 |                          |                 | Ambient te       | emperatures: -  | 40 to +85 °C /-        | 40 to +105 °C                    |                  |             |            |  |  |

|                               | aures                    |                 |                          |                 | Ju               | nction tempera  | ture: -40 to + 1       | 125 °C                           |                  |             |            |  |  |

| Packages                      |                          | LQ              | FP100                    |                 | CSP143<br>0FP144 | UFBO            | GA169                  |                                  | BGA176<br>QFP176 | LQFP208     | TFBGA216   |  |  |

#### Table 2. STM32F427xx and STM32F429xx features and peripheral counts (continued)

For the LQFP100 package, only FMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package. For UFBGA169 package, only SDRAM, NAND and multiplexed static memories are supported.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

16/238

3. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section 3.17.2: Internal reset OFF).

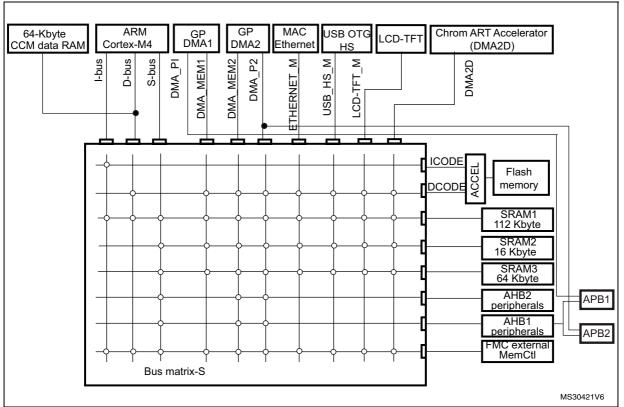

Figure 5. STM32F427xx and STM32F429xx Multi-AHB matrix

# 3.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

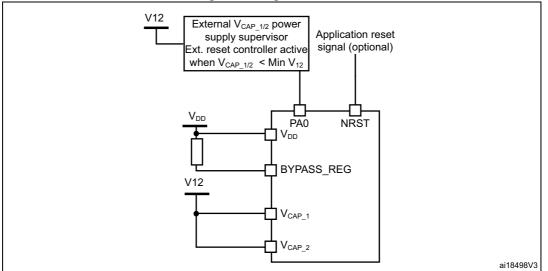

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below V<sub>12</sub> minimum value and V<sub>DD</sub> is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of  $V_{12}$  depends on the maximum frequency targeted in the application (see Table 17: General operating conditions).

### 3.18.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table                                                       | Table 4. Regulator ON/OFF and Internal reset ON/OFF availability |                                             |                                         |                                                                  |  |  |  |  |  |  |  |

|-------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|------------------------------------------------------------------|--|--|--|--|--|--|--|

| Package                                                     | Regulator ON                                                     | Regulator OFF                               | Internal reset ON                       | Internal reset OFF                                               |  |  |  |  |  |  |  |

| LQFP100                                                     | Yes                                                              | No                                          | Yes                                     | No                                                               |  |  |  |  |  |  |  |

| LQFP144,<br>LQFP208                                         | Tes                                                              | NO                                          |                                         | Yes                                                              |  |  |  |  |  |  |  |

| WLCSP143,<br>LQFP176,<br>UFBGA169,<br>UFBGA176,<br>TFBGA216 | Yes<br>BYPASS_REG set<br>to V <sub>SS</sub>                      | Yes<br>BYPASS_REG set<br>to V <sub>DD</sub> | Yes<br>PDR_ON set to<br>V <sub>DD</sub> | PDR_ON<br>connected to an<br>external power<br>supply supervisor |  |  |  |  |  |  |  |

#### Table 4. Regulator ON/OFF and internal reset ON/OFF availability

## 3.19 Real-time clock (RTC), backup SRAM and backup registers

The backup domain includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are performed automatically. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes. The sub-seconds value is also available in binary format.

It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

The 4-Kbyte backup SRAM is an EEPROM-like memory area. It can be used to store data which need to be retained in VBAT and standby mode. This memory area is disabled by default to minimize power consumption (see *Section 3.20: Low-power modes*). It can be enabled by software.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.20: Low-power modes).

DocID024030 Rev 9

### 3.39 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

# 3.40 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 10-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

## 3.41 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

|         |         |          | Pin nu   |         |          |         |          |                                                      |          |                 |       |                                                                                               |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| -       | 91      | G11      | J15      | 110     | G4       | 133     | J15      | PG6                                                  | I/O      | FT              | -     | FMC_INT2, DCMI_D12,<br>LCD_R7, EVENTOUT                                                       | -                       |

| -       | 92      | G12      | J14      | 111     | H1       | 134     | J14      | PG7                                                  | I/O      | FT              | -     | USART6_CK,<br>FMC_INT3, DCMI_D13,<br>LCD_CLK, EVENTOUT                                        | -                       |

| -       | 93      | F13      | H14      | 112     | G2       | 135     | H14      | PG8                                                  | I/O      | FT              | -     | SPI6_NSS,<br>USART6_RTS,<br>ETH_PPS_OUT,<br>FMC_SDCLK,<br>EVENTOUT                            | -                       |

| -       | 94      | J7       | G12      | 113     | D2       | 136     | G10      | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| -       | 95      | E6       | H13      | 114     | G1       | 137     | G11      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                             | -                       |

| 63      | 96      | F9       | H15      | 115     | F2       | 138     | H15      | PC6                                                  | I/O      | FT              | -     | TIM3_CH1, TIM8_CH1,<br>I2S2_MCK,<br>USART6_TX,<br>SDIO_D6, DCMI_D0,<br>LCD_HSYNC,<br>EVENTOUT | -                       |

| 64      | 97      | F10      | G15      | 116     | F3       | 139     | G15      | PC7                                                  | I/O      | FT              | -     | TIM3_CH2, TIM8_CH2,<br>I2S3_MCK,<br>USART6_RX,<br>SDIO_D7, DCMI_D1,<br>LCD_G6, EVENTOUT       | -                       |

| 65      | 98      | F11      | G14      | 117     | E4       | 140     | G14      | PC8                                                  | I/O      | FT              | _     | TIM3_CH3, TIM8_CH3,<br>USART6_CK,<br>SDIO_D0, DCMI_D2,<br>EVENTOUT                            | -                       |

| 66      | 99      | F12      | F14      | 118     | E3       | 141     | F14      | PC9                                                  | I/O      | FT              | 1     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, SDIO_D1,<br>DCMI_D3, EVENTOUT             | -                       |

| 67      | 100     | E13      | F15      | 119     | F1       | 142     | F15      | PA8                                                  | I/O      | FT              | -     | MCO1, TIM1_CH1,<br>I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF,<br>LCD_R6, EVENTOUT                 | -                       |

Table 10. STM32F427xx and STM32F429xx pin and ball definitions (continued)

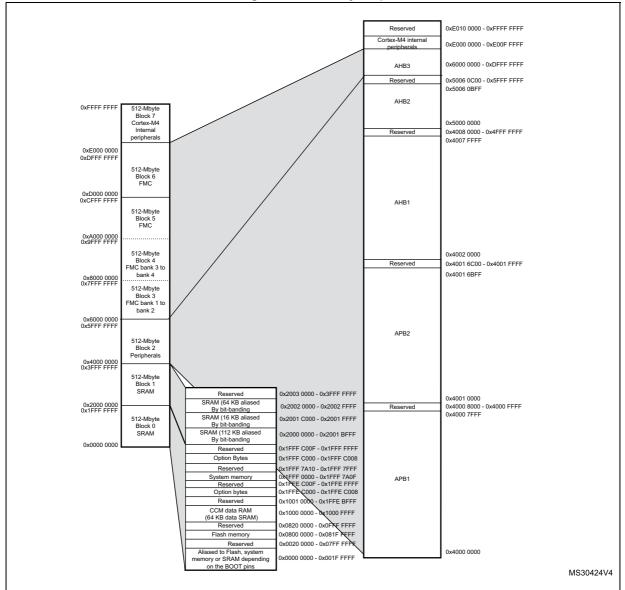

# 5 Memory mapping

The memory map is shown in *Figure 19*.

Figure 19. Memory map

| Bus       | Boundary address          | Peripheral                     |

|-----------|---------------------------|--------------------------------|

|           | 0xE00F FFFF - 0xFFFF FFFF | Reserved                       |

| Cortex-M4 | 0xE000 0000 - 0xE00F FFFF | Cortex-M4 internal peripherals |

|           | 0xD000 0000 - 0xDFFF FFFF | FMC bank 6                     |

|           | 0xC000 0000 - 0xCFFF FFFF | FMC bank 5                     |

|           | 0xA000 1000 - 0xBFFF FFFF | Reserved                       |

| AHB3      | 0xA000 0000- 0xA000 0FFF  | FMC control register           |

| АПЬЗ      | 0x9000 0000 - 0x9FFF FFFF | FMC bank 4                     |

|           | 0x8000 0000 - 0x8FFF FFFF | FMC bank 3                     |

|           | 0x7000 0000 - 0x7FFF FFFF | FMC bank 2                     |

|           | 0x6000 0000 - 0x6FFF FFFF | FMC bank 1                     |

|           | 0x5006 0C00- 0x5FFF FFFF  | Reserved                       |

|           | 0x5006 0800 - 0X5006 0BFF | RNG                            |

|           | 0x5005 0400 - X5006 07FF  | Reserved                       |

| AHB2      | 0x5005 0000 - 0X5005 03FF | DCMI                           |

|           | 0x5004 0000- 0x5004 FFFF  | Reserved                       |

|           | 0x5000 0000 - 0X5003 FFFF | USB OTG FS                     |

Table 13. STM32F427xx and STM32F429xx register boundary addresses

# 6 Electrical characteristics

### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 1.7 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

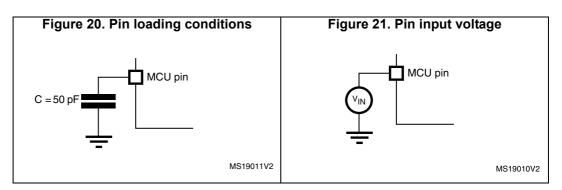

The loading conditions used for pin parameter measurement are shown in *Figure 20*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 21*.

| Symbol                           | Parameter                                                                           | Conditions                                                                                | Min | Тур | Max | Unit |  |  |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|--|

| I <sub>RUSH</sub> <sup>(1)</sup> | InRush current on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby) |                                                                                           | -   | 160 | 200 | mA   |  |  |  |  |  |

| E <sub>RUSH</sub> <sup>(1)</sup> | InRush energy on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -   | -   | 5.4 | μC   |  |  |  |  |  |

Table 22. reset and power control block characteristics (continued)

1. Guaranteed by design.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

#### 6.3.6 Over-drive switching characteristics

When the over-drive mode switches from enabled to disabled or disabled to enabled, the system clock is stalled during the internal voltage set-up.

The over-drive switching characteristics are given in *Table 23*. They are sbject to general operating conditions for  $T_A$ .

| Symbol    | Parameter                        | Conditions                              | Min | Тур | Мах | Unit |

|-----------|----------------------------------|-----------------------------------------|-----|-----|-----|------|

| Tod_swen  |                                  | HSI                                     | -   | 45  | -   |      |

|           | Over_drive switch<br>enable time | HSE max for 4 MHz<br>and min for 26 MHz | 45  | -   | 100 |      |

|           |                                  | External HSE<br>50 MHz                  | -   | 40  | -   | 116  |

|           |                                  | HSI                                     | -   | 20  | -   | μs   |

| Tod_swdis | Over_drive switch disable time   | HSE max for 4 MHz and min for 26 MHz.   | 20  | -   | 80  |      |

|           |                                  | External HSE<br>50 MHz                  | -   | 15  | -   |      |

Table 23. Over-drive switching characteristics<sup>(1)</sup>

1. Guaranteed by design.

|        |           |                                                               |                            | Typ <sup>(1)</sup>         |                            |                           |                           |                            |      |  |

|--------|-----------|---------------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------|----------------------------|------|--|

| Symbol | Parameter | Conditions                                                    | т                          | A = 25 °(                  | C                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|        |           |                                                               | V <sub>DD</sub> =<br>1.7 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> = 3.6 V   |                           |                            |      |  |

|        |           | Backup SRAM ON, low-speed oscillator (LSE) and RTC ON         | 2.80                       | 3.00                       | 3.60                       | 7.00                      | 19.00                     | 36.00                      |      |  |

|        |           | Backup SRAM OFF, low-<br>speed oscillator (LSE) and<br>RTC ON | 2.30                       | 2.60                       | 3.10                       | 6.00                      | 16.00                     | 31.00                      | μA   |  |

| _      |           | Backup SRAM ON, RTC and LSE OFF                               | 2.30                       | 2.50                       | 2.90                       | 6.00 <sup>(3)</sup>       | 18.00 <sup>(3)</sup>      | 35.00 <sup>(3)</sup>       |      |  |

|        |           | Backup SRAM OFF, RTC and LSE OFF                              | 1.70                       | 1.90                       | 2.20                       | 5.00 <sup>(3)</sup>       | 15.00 <sup>(3)</sup>      | 30.00 <sup>(3)</sup>       |      |  |

#### Table 28. Typical and maximum current consumptions in Standby mode

The typical current consumption values are given with PDR OFF (internal reset OFF). When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2 μA.

2. Based on characterization, not tested in production unless otherwise specified.

3. Based on characterization, tested in production.

#### Table 29. Typical and maximum current consumptions in $\mathrm{V}_{\mathrm{BAT}}$ mode

|        |                                    |                                                       |                             | Тур                         |                             | Ма                               |         |      |    |

|--------|------------------------------------|-------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------------|---------|------|----|

| Symbol | Parameter                          | Conditions <sup>(1)</sup>                             | т                           | a = 25 °                    | С                           | T <sub>A</sub> = 85 °C<br>105 °C |         | Unit |    |

|        |                                    |                                                       | V <sub>BAT</sub> =<br>1.7 V | V <sub>BAT</sub> =<br>2.4 V | V <sub>BAT</sub> =<br>3.3 V | V <sub>BAT</sub> =               | = 3.6 V |      |    |

|        | Backup<br>domain supply<br>current | Backup SRAM ON, low-speed oscillator (LSE) and RTC ON | 1.28                        | 1.40                        | 1.62                        | 6                                | 11      |      |    |

|        |                                    |                                                       |                             | 0.66                        | 0.76                        | 0.97                             | 3       | 5    | μA |

|        |                                    | Backup SRAM ON, RTC and LSE OFF                       | 0.70                        | 0.72                        | 0.74                        | 5                                | 10      | μΛ   |    |

|        |                                    | Backup SRAM OFF, RTC and<br>LSE OFF                   |                             | 0.10                        | 0.10                        | 0.10                             | 2       | 4    |    |

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a  $C_L$  of 6 pF for typical values.

2. Guaranteed by characterization results.

#### **On-chip peripheral current consumption**

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- I/O compensation cell enabled.

- The ART accelerator is ON.

- Scale 1 mode selected, internal digital voltage V12 = 1.32 V.

- HCLK is the system clock. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- $f_{HCLK}$  = 180 MHz (Scale1 + over-drive ON),  $f_{HCLK}$  = 144 MHz (Scale 2),  $f_{HCLK}$  = 120 MHz (Scale 3)"

- Ambient operating temperature is 25 °C and  $V_{DD}$ =3.3 V.

| E                  | Peripheral                                         |         | I <sub>DD</sub> ( Тур) <sup>(1)</sup> |         | Unit   |  |  |  |  |  |  |  |

|--------------------|----------------------------------------------------|---------|---------------------------------------|---------|--------|--|--|--|--|--|--|--|

|                    | enpheral                                           | Scale 1 | Scale 2                               | Scale 3 |        |  |  |  |  |  |  |  |

|                    | GPIOA                                              | 2.50    | 2.36                                  | 2.08    |        |  |  |  |  |  |  |  |

|                    | GPIOB                                              | 2.56    | 2.36                                  | 2.08    |        |  |  |  |  |  |  |  |

|                    | GPIOC<br>GPIOD                                     | 2.44    | 2.29                                  | 2.00    |        |  |  |  |  |  |  |  |

|                    |                                                    | 2.50    | 2.36                                  | 2.08    |        |  |  |  |  |  |  |  |

|                    | GPIOE                                              | 2.44    | 2.29                                  | 2.00    |        |  |  |  |  |  |  |  |

|                    | GPIOF                                              | 2.44    | 2.29                                  | 2.00    |        |  |  |  |  |  |  |  |

|                    | GPIOG                                              | 2.39    | 2.22                                  | 2.00    |        |  |  |  |  |  |  |  |

|                    | GPIOH                                              | 2.33    | 2.15                                  | 1.92    |        |  |  |  |  |  |  |  |

|                    | GPIOI                                              | 2.39    | 2.22                                  | 2.00    |        |  |  |  |  |  |  |  |

| AHB1               | GPIOJ                                              | 2.33    | 2.15                                  | 1.92    | 1      |  |  |  |  |  |  |  |

| (up to<br>180 MHz) | GPIOK                                              | 2.33    | 2.15                                  | 1.92    | µA/MHz |  |  |  |  |  |  |  |

| 100 101 12)        | OTG_HS+ULPI                                        | 27.00   | 24.86                                 | 21.92   |        |  |  |  |  |  |  |  |

|                    | CRC                                                | 0.44    | 0.42                                  | 0.33    |        |  |  |  |  |  |  |  |

|                    | BKPSRAM                                            | 0.78    | 0.69                                  | 0.58    |        |  |  |  |  |  |  |  |

|                    | DMA1                                               | 25.33   | 23.26                                 | 20.50   |        |  |  |  |  |  |  |  |

|                    | DMA2                                               | 24.72   | 22.71                                 | 20.00   |        |  |  |  |  |  |  |  |

|                    | DMA2D                                              | 28.50   | 26.32                                 | 23.33   | 1      |  |  |  |  |  |  |  |

|                    | ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 21.56   | 20.07                                 | 17.75   |        |  |  |  |  |  |  |  |

#### Table 35. Peripheral current consumption

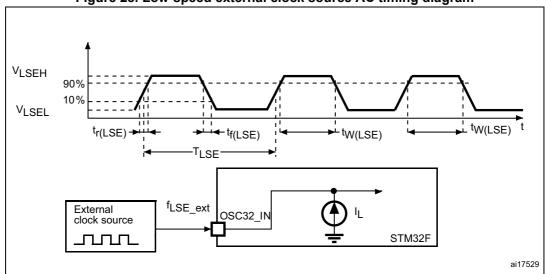

Figure 28. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                             | Parameter                               | Conditions                                                            | Min   | Тур | Max | Unit |  |

|------------------------------------|-----------------------------------------|-----------------------------------------------------------------------|-------|-----|-----|------|--|

| f <sub>OSC_IN</sub>                | Oscillator frequency                    |                                                                       | 4     | -   | 26  | MHz  |  |

| R <sub>F</sub>                     | Feedback resistor                       |                                                                       | -     | 200 | -   | kΩ   |  |

| I                                  |                                         | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -     | 450 | -   |      |  |

| IDD                                | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -     | 530 | -   | μA   |  |

| ACC <sub>HSE</sub> <sup>(2)</sup>  | HSE accuracy                            |                                                                       | - 500 | -   | 500 | ppm  |  |

| G <sub>m</sub> _crit_max           | Maximum critical crystal g <sub>m</sub> | Startup                                                               | -     | -   | 1   | mA/V |  |

| t <sub>SU(HSE</sub> <sup>(3)</sup> | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -     | 2   | -   | ms   |  |

| Table 39. HSE 4- | 26 MHz oscillator | characteristics <sup>(1)</sup> |

|------------------|-------------------|--------------------------------|

|                  |                   | onaraotoriotioo                |

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. The minimum and maximum values must be respected to comply with USB standard specifications.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

| Symbol                                  | Parameter                                    | Conditions                               | Min          | Тур | Мах          | Unit |  |  |

|-----------------------------------------|----------------------------------------------|------------------------------------------|--------------|-----|--------------|------|--|--|

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |  |  |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{\text{DDA}}$ | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 | mA   |  |  |

#### Table 44. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

#### Table 45. PLLISAI (audio and LCD-TFT PLL) characteristics

| Symbol                                  | Parameter                             | Conditions                                                              |                    | Min                 | Тур  | Max          | Unit |

|-----------------------------------------|---------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLLSAI_IN</sub>                  | PLLSAI input clock <sup>(1)</sup>     |                                                                         |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         | MHz  |

| f <sub>PLLSAI_OUT</sub>                 | PLLSAI multiplier output clock        |                                                                         |                    | -                   | -    | 216          | MHz  |

| f <sub>VCO_OUT</sub>                    | PLLSAI VCO output                     |                                                                         |                    | 100                 | -    | 432          | MHz  |

| +                                       | PLLSAI lock time                      | VCO freq = 100 MHz                                                      |                    | 75                  | -    | 200          |      |

| t <sub>LOCK</sub>                       |                                       | VCO freq = 432 MHz                                                      |                    | 100                 | -    | 300          | μs   |

| Jitter <sup>(3)</sup>                   |                                       | Cycle to cycle at                                                       | RMS                | -                   | 90   | -            |      |

|                                         | Main SAI clock jitter                 | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                            | peak<br>to<br>peak | -                   | ±280 | -            | ps   |

|                                         |                                       | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples |                    | -                   | 90   | -            | ps   |

|                                         | FS clock jitter                       | Cycle to cycle at 48 KHz on 1000 samples                                |                    | -                   | 400  | -            | ps   |

| I <sub>DD(PLLSAI)</sub> <sup>(4)</sup>  | PLLSAI power consumption on $V_{DD}$  | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLSAI)</sub> <sup>(4)</sup> | PLLSAI power consumption on $V_{DDA}$ | VCO freq = 100 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 | mA   |

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

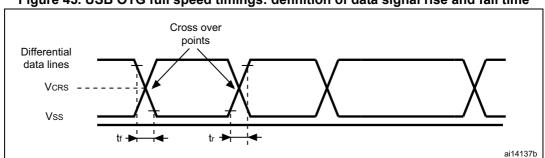

#### Figure 45. USB OTG full speed timings: definition of data signal rise and fall time

#### Table 67. USB OTG full speed electrical characteristics<sup>(1)</sup>

|                  | Driver characteristics                 |                                |     |     |      |  |  |  |  |  |

|------------------|----------------------------------------|--------------------------------|-----|-----|------|--|--|--|--|--|

| Symbol           | Parameter                              | Conditions                     | Min | Max | Unit |  |  |  |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching               | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |  |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage        |                                | 1.3 | 2.0 | V    |  |  |  |  |  |

| Z <sub>DRV</sub> | Output driver impedance <sup>(3)</sup> | Driving high or<br>low         | 28  | 44  | Ω    |  |  |  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on DP (D+) and DM (D-) pins since the matching impedance is included in the embedded driver.

#### USB high speed (HS) characteristics

Unless otherwise specified, the parameters given in *Table 70* for ULPI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 69* and  $V_{DD}$  supply voltage conditions summarized in *Table 68*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10, unless otherwise specified

- Capacitive load C = 30 pF, unless otherwise specified

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

| Symb        | ol              | Parameter                    | r Min. <sup>(1)</sup> Max. <sup>(1)</sup> |     | Unit |

|-------------|-----------------|------------------------------|-------------------------------------------|-----|------|

| Input level | V <sub>DD</sub> | USB OTG HS operating voltage | 1.7                                       | 3.6 | V    |

Table 68. USB HS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(1)</sup> | Unit |  |  |  |  |  |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|--|--|--|--|--|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |  |  |  |  |  |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±1.5 | ±2.5               |      |  |  |  |  |  |

| EG     | Gain error                   | $V_{DDA} = 2.4$ to 3.6 V,                                                      | ±1.5 | ±3                 | LSB  |  |  |  |  |  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |  |  |  |  |  |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |  |  |  |  |  |

#### Table 76. ADC static accuracy at f<sub>ADC</sub> = 30 MHz

1. Guaranteed by characterization results.

|        | Table 11. Abo static accuracy at TADC – 50 Milz |                                                                     |     |                    |      |  |  |  |  |

|--------|-------------------------------------------------|---------------------------------------------------------------------|-----|--------------------|------|--|--|--|--|

| Symbol | Parameter                                       | Test conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |  |  |  |  |

| ET     | Total unadjusted error                          |                                                                     | ±4  | ±7                 |      |  |  |  |  |

| EO     | Offset error                                    | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |  |  |  |  |

| EG     | Gain error                                      | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |  |  |  |  |

| ED     | Differential linearity error                    | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |  |  |  |  |

| EL     | Integral linearity error                        |                                                                     | ±3  | ±6                 |      |  |  |  |  |

### Table 77. ADC static accuracy at $f_{ADC}$ = 36 MHz

1. Guaranteed by characterization results.

# Table 78. ADC dynamic accuracy at $f_{ADC}$ = 18 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz     | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

## Table 79. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz     | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

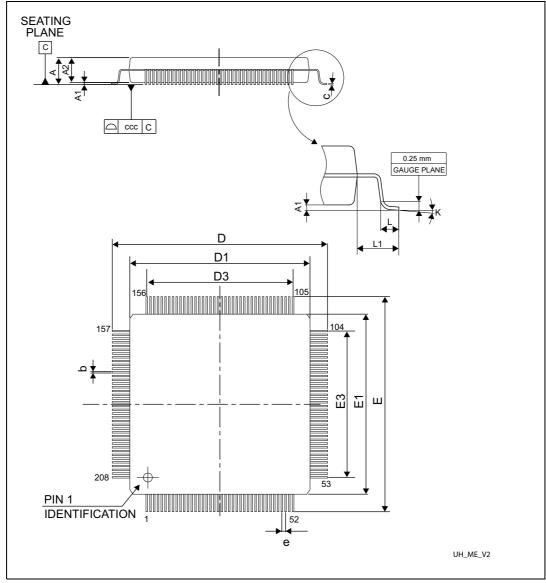

| mechanical data (continued) |        |             |        |        |                       |        |  |  |  |

|-----------------------------|--------|-------------|--------|--------|-----------------------|--------|--|--|--|

| Symbol                      |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |  |  |

| Symbol                      | Min    | Тур         | Мах    | Min    | Тур                   | Мах    |  |  |  |

| ZD                          | -      | 1.250       | -      | -      | 0.0492                | -      |  |  |  |

| Е                           | 23.900 | -           | 24.100 | 0.9409 | -                     | 0.9488 |  |  |  |

| HE                          | 25.900 | -           | 26.100 | 1.0197 | -                     | 1.0276 |  |  |  |

| ZE                          | -      | 1.250       | -      | -      | 0.0492                | -      |  |  |  |

| е                           | -      | 0.500       | -      | -      | 0.0197                | -      |  |  |  |

| L <sup>(2)</sup>            | 0.450  | -           | 0.750  | 0.0177 | -                     | 0.0295 |  |  |  |

| L1                          | -      | 1.000       | -      | -      | 0.0394                | -      |  |  |  |

| k                           | 0°     | -           | 7°     | 0°     | -                     | 7°     |  |  |  |

| CCC                         | -      | -           | 0.080  | -      | -                     | 0.0031 |  |  |  |

# Table 114. LQFP176 - 176-pin, 24 x 24 mm low-profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. L dimension is measured at gauge plane at 0.25 mm above the seating plane.

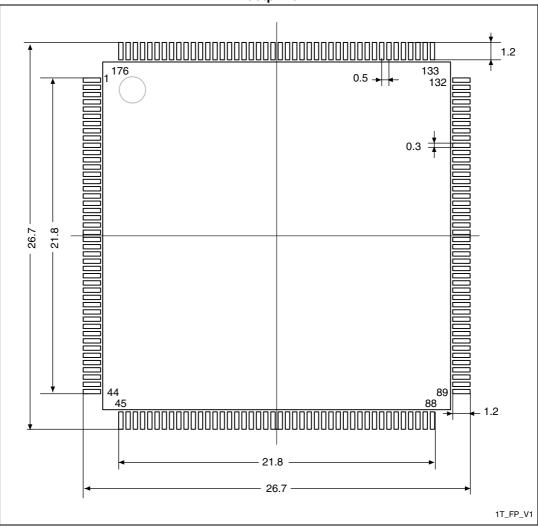

Figure 90. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

# 7.5 LQFP208 package information

Figure 92. LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat package outline

1. Drawing is not to scale.