## STMicroelectronics - STM32F429ZIT6TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 180MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                   |

| Number of I/O              | 114                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                |                                                                                     |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 144-LQFP                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f429zit6tr             |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.1 Full compatibility throughout the family

The STM32F427xx and STM32F429xx devices are part of the STM32F4 family. They are fully pin-to-pin, software and feature compatible with the STM32F2xx devices, allowing the user to try different memory densities, peripherals, and performances (FPU, higher frequency) for a greater degree of freedom during the development cycle.

The STM32F427xx and STM32F429xx devices maintain a close compatibility with the whole STM32F10xx family. All functional pins are pin-to-pin compatible. The STM32F427xx and STM32F429xx, however, are not drop-in replacements for the STM32F10xx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xx to the STM32F42x family remains simple as only a few pins are impacted.

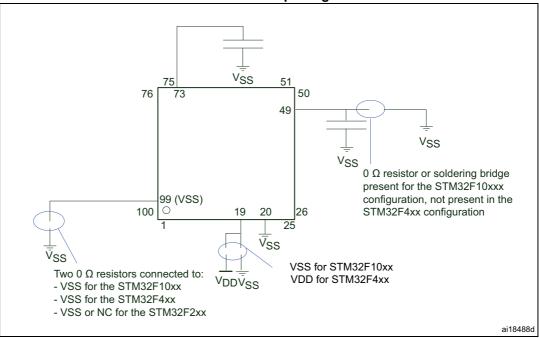

*Figure 1*, *Figure 2*, and *Figure 3*, give compatible board designs between the STM32F4xx, STM32F2xx, and STM32F10xx families.

Figure 1. Compatible board design STM32F10xx/STM32F2xx/STM32F4xx for LQFP100 package

# 3 Functional overview

# 3.1 **ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU and embedded Flash and SRAM**

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core is a 32-bit RISC processor that features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F42x family is compatible with all ARM tools and software.

*Figure 4* shows the general block diagram of the STM32F42x family.

Note: Cortex-M4 with FPU core is binary compatible with the Cortex-M3 core.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 225 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART Accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 180 MHz.

# 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

## 3.4 Embedded Flash memory

The devices embed a Flash memory of up to 2 Mbytes available for storing programs and data.

# 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.6 Embedded SRAM

All devices embed:

- Up to 256Kbytes of system SRAM including 64 Kbytes of CCM (core coupled memory) data RAM

- RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

- 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM, FMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

# 3.11 Chrom-ART Accelerator<sup>™</sup> (DMA2D)

The Chrom-Art Accelerator <sup>™</sup> (DMA2D) is a graphic accelerator which offers advanced bit blitting, row data copy and pixel format conversion. It supports the following functions:

- Rectangle filling with a fixed color

- Rectangle copy

- Rectangle copy with pixel format conversion

- Rectangle composition with blending and pixel format conversion.

Various image format coding are supported, from indirect 4bpp color mode up to 32bpp direct color. It embeds dedicated memory to store color lookup tables.

An interrupt can be generated when an operation is complete or at a programmed watermark.

All the operations are fully automatized and are running independently from the CPU or the DMAs.

# 3.12 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 91 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\$}$ -M4 with FPU core.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

# 3.13 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 168 GPIOs can be connected to the 16 external interrupt lines.

## 3.14 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy over the full temperature range. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is

DocID024030 Rev 9

| ſ | 11             | 10    | 9      | 8     | 7      | 6      | 5      | 4      | 3      | 2          | 1          |

|---|----------------|-------|--------|-------|--------|--------|--------|--------|--------|------------|------------|

| A |                | (PE1) | (PB8)  | (PB6) | PG15   | PG12   | (PD7)  | PD5    | PD2    | PC10       | VDD        |

| в | (PE4)          | PEO   | (PB9)  | (PB7) | (PB3)  | (PG11) | (PD4)  | (PD3)  | PD0    | PC11       | PA14       |

| с | VBAT           | (PE3) |        | PB5   | (PB4)  | PG10   | VDD    | (PD1)  | PC12   | (PA15)     | VDD        |

| D | PC14           | PC13  | PE5    | (PE2) | VDD    | PG13   | (PA10) | (PA11) | (PA13) | vss        | VCAP<br>_2 |

| E | PC15           | VDD   | (PF1)  | PE6   | vss    | VDD    | PG9    | PC8    | PC9    | (PA9)      | (PA12)     |

| F | PF0            | (PF2) | (PF4)  | PF5   | (PF7)  | PG14   | VSS    | PD6    | PC7    | PC6        | PA8        |

| G | PF3            | PF6   | (PF10) | PF9   | VDD    | PG5    | PG4    | PG6    | PG3    | PG8        | VDD        |

| н | PF8            | (PH1) | NRST   | PC0   | vss    | (PD12) | (PD13) | PD10   | vss    | vss        | PG7        |

| J | (PH0)          | PC2   | PC3    | VDD   | VDD    | VDD    | VDD    | PE10   | PB15   | (PD14)     | PG2        |

| к | PC1            | VSSA  | PA0    | (PA1) | (PB1)  | (PF13) | (PG1)  | (PE11) | (PB14) | (PD11)     | PD15       |

| L | VREF<br>+      | VDDA  | (PA2)  | (PA7) | (PB2)  | (PF14) | (PE7)  | PE12   | PE15   | PD8        | VDD        |

| м | (PA3)          | (PA4) | PA5    | PC4   | (PF11) | (PF15) | PE8    | PE14   | (PB10) | (PB12)     | (PD9)      |

| N | BYPASS_<br>REG | (PA6) | PC5    | РВО   | (PF12) | PG0    | PE9    | PE13   | (PB11) | VCAP<br>_1 | PB13       |

| l |                |       |        |       |        |        |        |        |        |            | N          |

Figure 12. STM32F42x WLCSP143 ballout

1. The above figure shows the package bump view.

|         |         |          | Pin nu   |         |          |         |          |                                                      |          |                 |       |                                                                                                                 |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                             | Additional<br>functions |

| 38      | 58      | N7       | R8       | 68      | L5       | 79      | R8       | PE7                                                  | I/O      | FT              | -     | TIM1_ETR, UART7_Rx,<br>FMC_D4, EVENTOUT                                                                         | -                       |

| 39      | 59      | J8       | P8       | 69      | M5       | 80      | N9       | PE8                                                  | I/O      | FT              | -     | TIM1_CH1N,<br>UART7_Tx, FMC_D5,<br>EVENTOUT                                                                     | -                       |

| 40      | 60      | K8       | P9       | 70      | N5       | 81      | P9       | PE9                                                  | I/O      | FT              | -     | TIM1_CH1, FMC_D6,<br>EVENTOUT                                                                                   | -                       |

| -       | 61      | J6       | M9       | 71      | H3       | 82      | K8       | V <sub>SS</sub>                                      | S        |                 | -     |                                                                                                                 | -                       |

| -       | 62      | G10      | N9       | 72      | J5       | 83      | L9       | V <sub>DD</sub>                                      | S        |                 | -     |                                                                                                                 | -                       |

| 41      | 63      | L8       | R9       | 73      | J4       | 84      | R9       | PE10                                                 | I/O      | FT              | -     | TIM1_CH2N, FMC_D7,<br>EVENTOUT                                                                                  | -                       |

| 42      | 64      | M8       | P10      | 74      | K4       | 85      | P10      | PE11                                                 | I/O      | FT              | -     | TIM1_CH2, SPI4_NSS,<br>FMC_D8, LCD_G3,<br>EVENTOUT                                                              | -                       |

| 43      | 65      | N8       | R10      | 75      | L4       | 86      | R10      | PE12                                                 | I/O      | FT              | -     | TIM1_CH3N,<br>SPI4_SCK, FMC_D9,<br>LCD_B4, EVENTOUT                                                             | -                       |

| 44      | 66      | H9       | N11      | 76      | N4       | 87      | R12      | PE13                                                 | I/O      | FT              | -     | TIM1_CH3,<br>SPI4_MISO, FMC_D10,<br>LCD_DE, EVENTOUT                                                            | -                       |

| 45      | 67      | 19       | P11      | 77      | M4       | 88      | P11      | PE14                                                 | I/O      | FT              | -     | TIM1_CH4,<br>SPI4_MOSI, FMC_D11,<br>LCD_CLK, EVENTOUT                                                           | -                       |

| 46      | 68      | K9       | R11      | 78      | L3       | 89      | R11      | PE15                                                 | I/O      | FT              | -     | TIM1_BKIN, FMC_D12,<br>LCD_R7, EVENTOUT                                                                         | -                       |

| 47      | 69      | L9       | R12      | 79      | М3       | 90      | P12      | PB10                                                 | I/O      | FT              | -     | TIM2_CH3, I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>USART3_TX,<br>OTG_HS_ULPI_D3,<br>ETH_MII_RX_ER,<br>LCD_G4, EVENTOUT | -                       |

| 48      | 70      | M9       | R13      | 80      | N3       | 91      | R13      | PB11                                                 | I/O      | FT              | -     | TIM2_CH4, I2C2_SDA,<br>USART3_RX,<br>OTG_HS_ULPI_D4,<br>ETH_MII_TX_EN/ETH_<br>RMII_TX_EN, LCD_G5,<br>EVENTOUT   | -                       |

| Table 10. | STM32F427xx and | STM32F429xx pin | and ball definition | ons (continued) |

|-----------|-----------------|-----------------|---------------------|-----------------|

|           |                 |                 |                     |                 |

|         |         |          | Pin nı   | ımber   | •        |         |          |                                                      |          |                 |       |                                                                                       |                         |

|---------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | UFBGA176 | LQFP176 | WLCSP143 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| -       | -       | C11      | D14      | 132     | -        | 155     | D14      | PI1                                                  | I/O      | FT              | -     | SPI2_SCK/I2S2_CK <sup>(7)</sup> ,<br>FMC_D25, DCMI_D8,<br>LCD_G6, EVENTOUT            | -                       |

| -       | I       | B12      | C14      | 133     | -        | 156     | C14      | PI2                                                  | I/O      | FT              | -     | TIM8_CH4,<br>SPI2_MISO,<br>I2S2ext_SD, FMC_D26,<br>DCMI_D9, LCD_G7,<br>EVENTOUT       | -                       |

| -       | -       | A12      | C13      | 134     | -        | 157     | C13      | PI3                                                  | I/O      | FT              | -     | TIM8_ETR,<br>SPI2_MOSI/I2S2_SD,<br>FMC_D27, DCMI_D10,<br>EVENTOUT                     | -                       |

| -       | -       | D11      | D9       | 135     | F5       | -       | F9       | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                     | -                       |

| -       | -       | D3       | C9       | 136     | A1       | 158     | E10      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                     | -                       |

| 76      | 109     | A11      | A14      | 137     | B1       | 159     | A14      | PA14<br>(JTCK-<br>SWCLK)                             | I/O      | FT              | -     | JTCK-SWCLK/<br>EVENTOUT                                                               | -                       |

| 77      | 110     | B11      | A13      | 138     | C2       | 160     | A13      | PA15<br>(JTDI)                                       | I/O      | FT              | -     | JTDI,<br>TIM2_CH1/TIM2_ETR,<br>SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>EVENTOUT             | -                       |

| 78      | 111     | C10      | B14      | 139     | A2       | 161     | B14      | PC10                                                 | I/O      | FT              | -     | SPI3_SCK/I2S3_CK,<br>USART3_TX,<br>UART4_TX, SDI0_D2,<br>DCMI_D8, LCD_R2,<br>EVENTOUT | -                       |

| 79      | 112     | B10      | B13      | 140     | B2       | 162     | B13      | PC11                                                 | I/O      | FT              | -     | I2S3ext_SD,<br>SPI3_MISO,<br>USART3_RX,<br>UART4_RX, SDIO_D3,<br>DCMI_D4, EVENTOUT    | -                       |

| 80      | 113     | A10      | A12      | 141     | C3       | 163     | A12      | PC12                                                 | I/O      | FT              | -     | SPI3_MOSI/I2S3_SD,<br>USART3_CK,<br>UART5_TX, SDIO_CK,<br>DCMI_D9, EVENTOUT           | -                       |

| 81      | 114     | D9       | B12      | 142     | B3       | 164     | B12      | PD0                                                  | I/O      | FT              | -     | CAN1_RX, FMC_D2,<br>EVENTOUT                                                          | -                       |

| Table 10. | STM32F427xx and | STM32F429xx | pin and ball | definitions | (continued) |  |

|-----------|-----------------|-------------|--------------|-------------|-------------|--|

|           |                 |             |              |             |             |  |

| Symbol                               | Ratings                                                                         | Max.   | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|--------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>    | 270    |      |

| $\Sigma I_{VSS}$                     | Total current out of sum of all $V_{SS_x}$ ground lines $(sink)^{(1)}$          | - 270  |      |

| I <sub>VDD</sub>                     | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>  | 100    |      |

| I <sub>VSS</sub>                     | Maximum current out of each $V_{SS_x}$ ground line (sink) <sup>(1)</sup>        | - 100  |      |

| 1                                    | Output current sunk by any I/O and control pin                                  | 25     |      |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/Os and control pin                              | - 25   |      |

| ΣI                                   | Total output current sunk by sum of all I/O and control pins <sup>(2)</sup>     | 120    | mA   |

| $\Sigma I_{IO}$                      | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | - 120  |      |

|                                      | Injected current on FT pins <sup>(4)</sup>                                      | 5/10   |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on NRST and BOOT0 pins <sup>(4)</sup>                          | - 5/+0 |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ±5     |      |

| $\Sigma I_{\rm INJ(PIN)}^{(5)}$      | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ±25    |      |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.21: 12-bit ADC characteristics.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. A positive injection is induced by  $V_{IN} > V_{DDA}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 14* for the values of the maximum allowed input voltage.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 16. Thermal characteristics

| Symbol           | Ratings                      | Value        | Unit |

|------------------|------------------------------|--------------|------|

| T <sub>STG</sub> | Storage temperature range    | – 65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125          | °C   |

## 6.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for  $\mathsf{T}_{\mathsf{A}}.$

| Symbol           | Parameter                      | Min | Мах | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| t                | V <sub>DD</sub> rise time rate | 20  | ∞   | us/V  |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate | 20  | ∞   | μ5/ V |

#### Table 20. Operating conditions at power-up / power-down (regulator ON)

## 6.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for  $T_A$ .

#### Table 21. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit  |

|-------------------|----------------------------------------------|------------|-----|-----|-------|

| +                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | 8   |       |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   | μs/V  |

| t                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | 8   | μ5/ ν |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | 8   |       |

1. To reset the internal logic at power-down, a reset must be applied on pin PA0 when V<sub>DD</sub> reach below 1.08 V.

#### Additional current consumption

The MCU is placed under the following conditions:

- All I/O pins are configured in analog mode.

- The Flash memory access time is adjusted to fHCLK frequency.

- The voltage scaling is adjusted to fHCLK frequency as follows:

- Scale 3 for  $f_{HCLK} \le 120$  MHz,

- Scale 2 for 120 MHz <  $f_{HCLK} \le 144$  MHz

- Scale 1 for 144 MHz <  $f_{HCLK} \le$  180 MHz. The over-drive is only ON at 180 MHz.

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- HSE crystal clock frequency is 25 MHz.

- When the regulator is OFF, V12 is provided externally as described in *Table 17: General operating conditions*

- T<sub>A</sub>= 25 °C .

# Table 30. Typical current consumption in Run mode, code with data processing running from Flash memory or RAM, regulator ON (ART accelerator enabled except prefetch), $V_{DD}=1.7 V^{(1)}$

| Symbol          | Parameter                       | Conditions     | f <sub>HCLK</sub> (MHz) | Тур  | Unit |

|-----------------|---------------------------------|----------------|-------------------------|------|------|

|                 |                                 |                | 168                     | 88.2 |      |

|                 |                                 |                | 150                     | 74.3 |      |

|                 |                                 |                | 144                     | 71.3 |      |

|                 |                                 | All Peripheral | 120                     | 52.9 |      |

|                 |                                 | enabled        | 90                      | 42.6 |      |

|                 |                                 |                | 60                      | 28.6 | - mA |

|                 | Supply current in RUN mode from |                | 30                      | 15.7 |      |

|                 |                                 |                | 25                      | 12.3 |      |

| I <sub>DD</sub> | V <sub>DD</sub> supply          |                | 168                     | 40.6 |      |

|                 |                                 |                | 150                     | 30.6 |      |

|                 |                                 |                | 144                     | 32.6 |      |

|                 |                                 | All Peripheral | 120                     | 24.7 |      |

|                 |                                 | disabled       | 90                      | 19.7 |      |

|                 |                                 |                | 60                      | 13.6 |      |

|                 |                                 |                | 30                      | 7.7  |      |

|                 |                                 |                | 25                      | 6.7  |      |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherls (such as ADC, or DAC) is not included.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

Table 50. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

## 6.3.14 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                         | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2                                            | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP176}, \text{T}_{\text{A}} = +25 \text{ °C}, \text{f}_{\text{HCLK}} = 168 \text{ MHz}, \text{ conforms to} \text{IEC 61000-4-2}$ | 4A              |

#### Table 51. EMS characteristics

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, PH2, PH3, PH4, PH5, PA3, PA4, PA5, PA6, PA7, PC4, and PC5.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

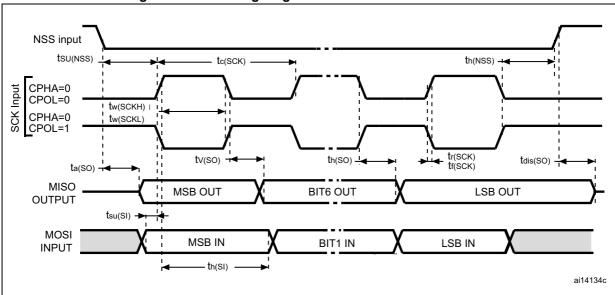

Figure 38. SPI timing diagram - slave mode and CPHA = 0

## 6.3.25 DAC electrical characteristics

| Symbol                            | Parameter                                      | Cond       | itions                                                | Min                | Тур | Мах                            | Unit | Comments                                                                                                                |

|-----------------------------------|------------------------------------------------|------------|-------------------------------------------------------|--------------------|-----|--------------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                  | Analog supply voltage                          |            | _                                                     | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    | -                                                                                                                       |

| V <sub>REF+</sub>                 | Reference supply voltage                       |            | -                                                     | 1.7 <sup>(1)</sup> | -   | 3.6                            | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                     |

| V <sub>SSA</sub>                  | Ground                                         |            | -                                                     | 0                  | -   | 0                              | V    | -                                                                                                                       |

| RLOAD <sup>(2)</sup>              | Resistive load                                 | DAC output | R <sub>LOAD</sub><br>connected<br>to V <sub>SSA</sub> | 5                  | -   | -                              | kΩ   | -                                                                                                                       |

| "LOAD                             |                                                | buffer ON  | R <sub>LOAD</sub><br>connected<br>to V <sub>DDA</sub> | 25                 |     |                                | 1132 | -                                                                                                                       |

| R <sub>O</sub> <sup>(2)</sup>     | Impedance output with<br>buffer OFF            |            | -                                                     | -                  | -   | 15                             | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                |            | -                                                     | -                  | -   | 50                             | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_O<br>UT<br>min <sup>(2)</sup> | Lower DAC_OUT voltage with buffer ON           |            | -                                                     | 0.2                | -   | -                              | v    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input                                  |

| DAC_O<br>UT<br>max <sup>(2)</sup> | Higher DAC_OUT voltage with buffer ON          |            | -                                                     | -                  | -   | V <sub>DDA</sub><br>- 0.2      | v    | code (0x0E0) to (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V and (0x1C7) to<br>(0xE38) at V <sub>REF+</sub> = 1.7 V          |

| DAC_O<br>UT<br>min <sup>(2)</sup> | Lower DAC_OUT<br>voltage with buffer<br>OFF    |            | -                                                     | -                  | 0.5 | -                              | mV   | It gives the maximum output                                                                                             |

| DAC_O<br>UT<br>max <sup>(2)</sup> | Higher DAC_OUT<br>voltage with buffer<br>OFF   |            | -                                                     | -                  | -   | V <sub>REF+</sub><br>-<br>1LSB | v    | excursion of the DAC.                                                                                                   |

| (4)                               | DAC DC V <sub>REF</sub> current consumption in |            | -                                                     | -                  | 170 | 240                            | μA   | With no load, worst code<br>(0x800) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs         |

| I <sub>VREF+</sub> <sup>(4)</sup> | quiescent mode<br>(Standby mode)               |            | -                                                     | -                  | 50  | 75                             | μΑ   | With no load, worst code<br>(0xF1C) at V <sub>REF+</sub> = 3.6 V in<br>terms of DC consumption on<br>the inputs         |

#### Table 85. DAC characteristics

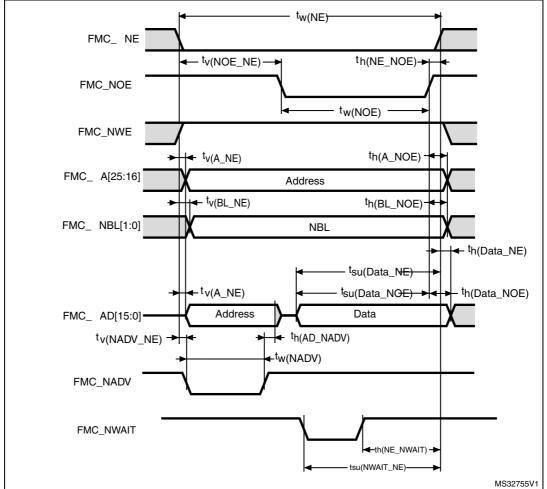

## 6.3.26 FMC characteristics

Unless otherwise specified, the parameters given in *Table 86* to *Table 101* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10 except at V<sub>DD</sub> range 1.7 to 2.1V where OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.17: I/O port characteristics for more details on the input/output characteristics.

#### Asynchronous waveforms and timings

*Figure 55* through *Figure 58* represent asynchronous waveforms and *Table 86* through *Table 93* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode , DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

- For SDRAM memories,  $V_{DD}$  ranges from 2.7 to 3.6 V and maximum frequency FMC\_SDCLK = 90 MHz

- For Mobile LPSDR SDRAM memories, V<sub>DD</sub> ranges from 1.7 to 1.95 V and maximum frequency FMC\_SDCLK = 84 MHz

|                           | NWAIT timings <sup>(1)(2)</sup>           |                         |                       |      |

|---------------------------|-------------------------------------------|-------------------------|-----------------------|------|

| Symbol                    | Parameter                                 | Min                     | Max                   | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> +1   | 8T <sub>HCLK</sub> +2 | ns   |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> – 1  | 6T <sub>HCLK</sub> +2 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                     | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   |                       | ns   |

Table 89. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings^{(1)(2)}

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results.

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 2                        | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                        | 1.5                     |      |

| t <sub>d</sub> (SDCLKL- SDNE) | Chip select valid time | -                        | 0.5                     | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 0.5                     |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                        | -                       |      |

## Table 102. SDRAM read timings<sup>(1)(2)</sup>

1. CL = 30 pF on data and address lines. CL=15pF on FMC\_SDCLK.

2. Guaranteed by characterization results.

## Table 103. LPSDR SDRAM read timings<sup>(1)(2)</sup>

|                               |                        | J                        |                         |      |

|-------------------------------|------------------------|--------------------------|-------------------------|------|

| Symbol                        | Parameter              | Min                      | Мах                     | Unit |

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time  | 2.5                      | -                       |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 0                        | -                       |      |

| t <sub>d</sub> (SDCLKL_Add)   | Address valid time     | -                        | 1                       |      |

| t <sub>d</sub> (SDCLKL_SDNE)  | Chip select valid time | -                        | 1                       | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 1                        | -                       | 115  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time      | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 1                        | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 1                       |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 1                        | -                       |      |

1. CL = 10 pF.

2. Guaranteed by characterization results.

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min    | Тур         | Max    | Min    | Тур                   | Max    |

| А      | -      | -           | 1.600  |        | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 29.800 | 30.000      | 30.200 | 1.1732 | 1.1811                | 1.1890 |

| D1     | 27.800 | 28.000      | 28.200 | 1.0945 | 1.1024                | 1.1102 |

| D3     | -      | 25.500      | -      | -      | 1.0039                | -      |

| E      | 29.800 | 30.000      | 30.200 | 1.1732 | 1.1811                | 1.1890 |

| E1     | 27.800 | 28.000      | 28.200 | 1.0945 | 1.1024                | 1.1102 |

| E3     | -      | 25.500      | -      | -      | 1.0039                | -      |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |

| k      | 0°     | 3.5°        | 7.0°   | 0°     | 3.5°                  | 7.0°   |

| CCC    | -      | -           | 0.080  | -      | -                     | 0.0031 |

# Table 115. LQFP208 - 208-pin, 28 x 28 mm low-profile quad flat packagemechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

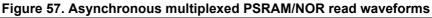

Figure 105. USB controller configured in dual mode and used in full speed mode

- 1. External voltage regulator only needed when building a  $\mathrm{V}_{\mathrm{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

- 4. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

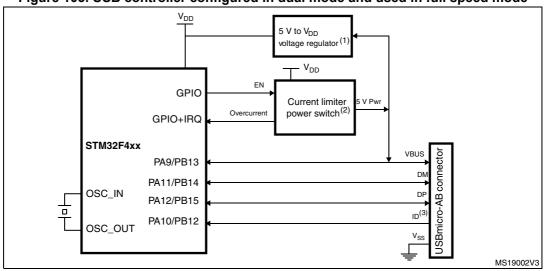

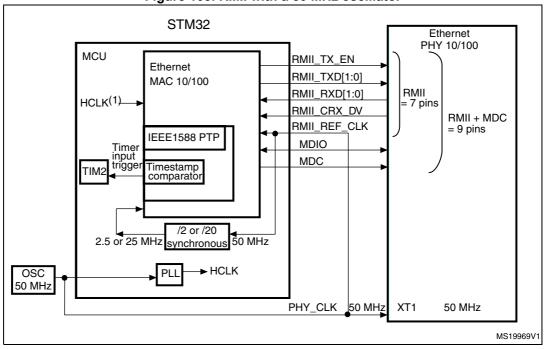

# **B.3** Ethernet interface solutions

1.  $f_{HCLK}$  must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

#### Figure 108. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.

#### STM32F427xx STM32F429xx

| Date        | Revision   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dale        | 1/64191011 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 24-Jan-2014 | 3          | Added STM32F429xE part numbers featuring 512 Mbytes of Flash<br>memory and UFBGA169 package.<br>Added LPSDR SDRAM.<br>Changed INTN into INTR in <i>Figure 4: STM32F427xx and</i><br><i>STM32F429xx block diagram</i> .<br>Added note 4 in Table 2: <i>STM32F427xx and STM32F429xx features</i><br><i>and peripheral counts</i> .<br>Updated Section 3.15: Boot modes.<br>Updated for PA4 and PA5 in Table 10: <i>STM32F427xx and</i><br><i>STM32F429xx pin and ball definitions</i> .<br>Added V <sub>IN</sub> for BOOT0 pins in <i>Table 14: Voltage characteristics</i> .<br>Updated Note 6., added Note 1.,and updated maximum V <sub>IN</sub> for B pins<br>in <i>Table 17: General operating conditions</i> .<br>Updated maximum Flash memory access frequency with wait states<br>for V <sub>DD</sub> = 1.8 to 2.1 V in <i>Table 18: Limitations depending on the</i><br><i>operating power supply range</i> .<br>Updated <i>Table 24: Typical and maximum current consumption in Run</i><br><i>mode</i> , code with data processing running from Flash memory (ART<br>accelerator enabled except prefetch) or RAM and Table 25: Typical<br><i>and maximum current consumption in Run mode</i> , code<br>with data processing running from Flash memory or RAM, regulator<br>ON (ART accelerator enabled except prefetch), VDD=1.7 V, Table 31:<br>Typical current consumption in Run mode, code<br>with data processing running from Flash memory or RAM, regulator<br>ON (ART accelerator enabled except prefetch), VDD=1.7 V, Table 31:<br>Typical current consumption in Run mode, code<br>with data processing running from Flash memory or RAM, regulator<br>ON (ART accelerator enabled except prefetch), VDD=1.7 V,<br>Updated Table 57: Output voltage characteristics.<br>Updated Table 57: Dynamic characteristics uSB ULPI.<br>Updated Table 70: Dynamic characteristics conditions. Updated<br>Figure 73: SDRAM read access waveforms (CL = 1) and Figure 74:<br>SDRAM write access waveforms. Added Table 103: LPSDR SDRAM<br>read timings and Table 105: LPSDR SDRAM write timings<br>and added note 2. Table 108: Dynamic characteristics: SD / MMC<br>characteris |

| Table 124. Document revision history |

|--------------------------------------|

|--------------------------------------|