Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | SH-3                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 133MHz                                                                            |

| Connectivity               | EBI/EMI, FIFO, IrDA, SCI, SmartCard                                               |

| Peripherals                | DMA, POR, WDT                                                                     |

| Number of I/O              | 96                                                                                |

| Program Memory Size        | -                                                                                 |

| Program Memory Type        | ROMIess                                                                           |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2.05V                                                                     |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                               |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 240-LFBGA                                                                         |

| Supplier Device Package    | 240-LFBGA (13x13)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d6417709sbp133bv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family/SH7700 Series

# SH7709S Group

# Hardware Manual

REJ09B0081-0500O

| Section                                                | Page | Description                                                                                                                                                                                                                                                     |

|--------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.2.13 MCS0 Control                                   | 258  | Description added                                                                                                                                                                                                                                               |

| Register (MCSCR0)                                      |      | Bit 6—CS2/CS0 Select (CS2/0)<br>Only 0 should be used for the CS2/0 bit in MCSCR0. Either 0 or 1<br>may be used for MCSCR1 to MCSCR7.                                                                                                                           |

| 10.3.4 Synchronous                                     | 290  | Bank Active description added                                                                                                                                                                                                                                   |

| DRAM Interface                                         |      | In bank active mode, too, all banks become inactive after a refresh cycle or after the bus is released as the result of bus arbitration.<br>The bank active mode should not be used unless the bus width for all areas is 32 bits.                              |

| 10.3.6 PCMCIA<br>Interface                             | 310  | Figure amended                                                                                                                                                                                                                                                  |

| Figure 10.32 Basic                                     |      | D15 to D0                                                                                                                                                                                                                                                       |

| Timing for PCMCIA<br>Memory Card Interface             |      | (Write)                                                                                                                                                                                                                                                         |

| 10.3.7 Waits between Access Cycles                     | 320  | Figure amended                                                                                                                                                                                                                                                  |

| Figure 10.40 Waits<br>between Access Cycles            |      | CKIO<br>A25 to A0                                                                                                                                                                                                                                               |

| 10.3.10 MCS[0] to                                      | 323  | Description amended                                                                                                                                                                                                                                             |

| MCS[7] Pin Control                                     |      | This enables 32-, 64-, 128-, or 256-Mbit memory to be connected to area 0 or area 2. However, only $CS2/0 = 0$ (area 0) should be used for MCSCR0. Table 10.15 shows MCSCR0–MCSCR7 settings and $\overline{MCS[0]}$ – $\overline{MCS[7]}$ assertion conditions. |

| 11.6 Usage Notes                                       | 387  | Description added                                                                                                                                                                                                                                               |

|                                                        |      | <ol> <li>DMAC transfers should not be performed in the sleep mode<br/>under conditions other than when the clock ratio of lφ (on-<br/>chip clock) to Bφ (bus clock) is 1:1.</li> </ol>                                                                          |

|                                                        |      | 14. When the following three conditions are all met, the<br>frequency control register (FRQCR) should not be changed<br>while a DMAC transfer is in progress.                                                                                                   |

|                                                        |      | <ul> <li>Bits IFC2 to IFC0 are changed.</li> </ul>                                                                                                                                                                                                              |

|                                                        |      | <ul> <li>STC2 to STC0 in FRQCR are not changed.</li> </ul>                                                                                                                                                                                                      |

|                                                        |      | <ul> <li>The clock ratio of lφ (on-chip clock) to Bφ (bus clock) after<br/>the change is other than 1:1.</li> </ul>                                                                                                                                             |

| 13.4.3 Precautions<br>when Using RTC<br>Module Standby | 426  | Newly added                                                                                                                                                                                                                                                     |

| Figure 23.47 | TCLK Input Timing                                            |     |

|--------------|--------------------------------------------------------------|-----|

| Figure 23.48 | TCLK Clock Input Timing                                      |     |

| Figure 23.49 | Oscillation Settling Time at RTC Crystal Oscillator Power-on |     |

| Figure 23.50 | SCK Input Clock Timing                                       |     |

| Figure 23.51 | SCI I/O Timing in Clock Synchronous Mode                     |     |

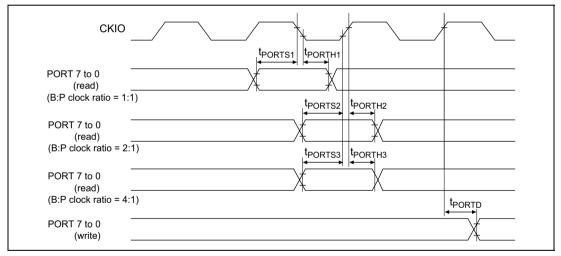

| Figure 23.52 | I/O Port Timing                                              |     |

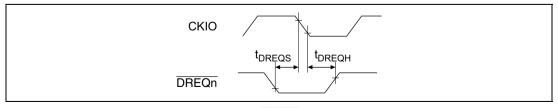

| Figure 23.53 | DREQ Input Timing                                            |     |

| Figure 23.54 | DRAK Output Timing                                           |     |

| Figure 23.55 | TCK Input Timing                                             | 709 |

| Figure 23.56 | TRST Input Timing (Reset Hold)                               | 710 |

| Figure 23.57 | UDI Data Transfer Timing                                     | 710 |

| Figure 23.58 | ASEMD0 Input Timing                                          | 710 |

| Figure 23.59 | Output Load Circuit                                          |     |

| Figure 23.60 | Load Capacitance vs. Delay Time                              |     |

| Figure D.1   | Package Dimensions (FP-208C)                                 |     |

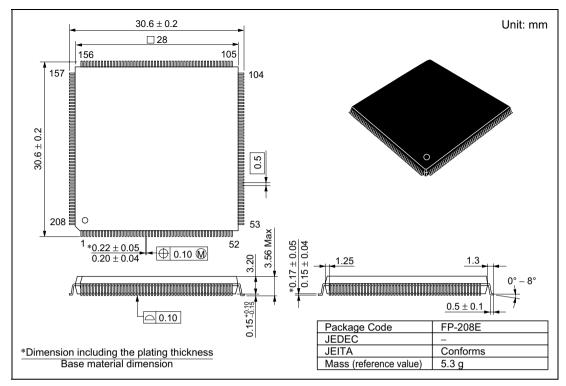

| Figure D.2   | Package Dimensions (FP-208E)                                 | 759 |

| Figure D.3   | Package Dimensions (BP-240A)                                 |     |

# 2.4 Instruction Set

# 2.4.1 Instruction Set Classified by Function

The SH7709S instruction set includes 68 basic instruction types, as listed in table 2.4.

# Table 2.4 Classification of Instructions

| Classification | Types | Operation<br>Code | Function                                                                                    | No. of<br>Instructions |

|----------------|-------|-------------------|---------------------------------------------------------------------------------------------|------------------------|

| Data transfer  | 5     | MOV               | Data transfer                                                                               | 39                     |

|                |       | MOVA              | Effective address transfer                                                                  | _                      |

|                |       | MOVT              | T bit transfer                                                                              | _                      |

|                |       | SWAP              | Swap of upper and lower bytes                                                               | _                      |

|                |       | XTRCT             | Extraction of middle of linked registers                                                    | _                      |

| Arithmetic     | 21    | ADD               | Binary addition                                                                             | 33                     |

| operations     |       | ADDC              | Binary addition with carry                                                                  | _                      |

|                |       | ADDV              | Binary addition with overflow check                                                         | _                      |

|                |       | CMP/cond          | Comparison                                                                                  | _                      |

|                |       | DIV1              | Division                                                                                    | _                      |

|                |       | DIV0S             | Initialization of signed division                                                           | _                      |

|                |       | DIV0U             | Initialization of unsigned division                                                         | _                      |

|                |       | DMULS             | Signed double-precision multiplication                                                      | _                      |

|                |       | DMULU             | Unsigned double-precision multiplication                                                    | _                      |

|                |       | DT                | Decrement and test                                                                          | _                      |

|                |       | EXTS              | Sign extension                                                                              | _                      |

|                |       | EXTU              | Zero extension                                                                              | _                      |

|                |       | MAC               | Multiply-and-accumulate operation,<br>double-precision multiply-and-accumulate<br>operation | _                      |

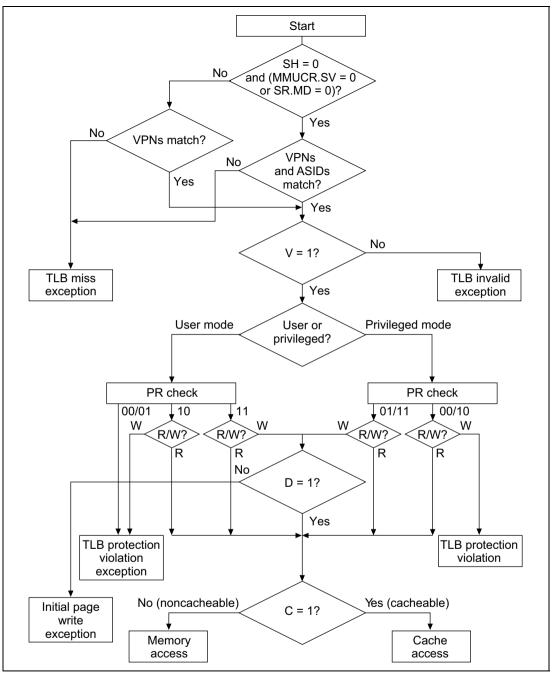

Figure 3.11 MMU Exception Generation Flowchart

# **10.3 BSC Operation**

# 10.3.1 Endian/Access Size and Data Alignment

The SH7709S supports both big endian, in which the 0 address is the most significant byte in the byte data, and little endian, in which the 0 address is the least significant byte. Switching between the two is designated by an external pin (MD5 pin) at the time of a power-on reset. After a power-on reset, big endian is engaged when MD5 is low; little endian is engaged when MD5 is high.

Three data bus widths are available for ordinary memory (byte, word, longword) and two data bus widths (word and longword) for synchronous DRAM. For the PCMCIA interface, choose from byte and word. This means data alignment is done by matching the device's data width and endian. The access unit must also be matched to the device's bus width. This also means that when longword data is read from a byte-width device, four read operations must be performed. In the SH7709S, data alignment and conversion of data length is performed automatically between the respective interfaces.

Tables 10.7 to 10.12 show the relationship between endian, device data width, and access unit.

|                         | Data Bus      |               |              | Strobe Signals |               |               |               |               |

|-------------------------|---------------|---------------|--------------|----------------|---------------|---------------|---------------|---------------|

| Operation               | D31–D24       | D23–D16       | D15–D8       | D7-D0          | WE3,<br>DQMUU | WE2,<br>DQMUL | WE1,<br>DQMLU | WEO,<br>DQMLL |

| Byte access<br>at 0     | Data<br>7–0   | _             | _            | _              | Asserted      |               |               |               |

| Byte access<br>at 1     | _             | Data<br>7–0   | _            | _              |               | Asserted      |               |               |

| Byte access<br>at 2     | —             | _             | Data<br>7–0  | _              |               |               | Asserted      |               |

| Byte access<br>at 3     | —             | _             | _            | Data<br>7–0    |               |               |               | Asserted      |

| Word access<br>at 0     | Data<br>15–8  | Data<br>7–0   | _            | _              | Asserted      | Asserted      |               |               |

| Word access<br>at 2     | _             | _             | Data<br>15–8 | Data<br>7–0    |               |               | Asserted      | Asserted      |

| Longword<br>access at 0 | Data<br>31–24 | Data<br>23–16 | Data<br>15–8 | Data<br>7–0    | Asserted      | Asserted      | Asserted      | Asserted      |

| <b>Table 10.7</b> | 32-Bit External Device/ | Big-Endian Access and Da | ata Alignment |

|-------------------|-------------------------|--------------------------|---------------|

|-------------------|-------------------------|--------------------------|---------------|

| SH7709S Address Pin |           | Synchronous DRAM Address Pin |          |                           |

|---------------------|-----------|------------------------------|----------|---------------------------|

|                     | RAS Cycle | CAS Cycle                    |          | Function                  |

| A15                 | A23       | A23                          | A13(BA1) | BANK select bank address  |

| A14                 | A22       | A22                          | A12(BA0) |                           |

| A13                 | A21       | A13                          | A11      | Address                   |

| A12                 | A20       | L/H                          | A10      | Address precharge setting |

| A11                 | A19       | A11                          | A9       | Address                   |

| A10                 | A18       | A10                          | A8       |                           |

| A9                  | A17       | A9                           | A7       |                           |

| A8                  | A16       | A8                           | A6       |                           |

| A7                  | A15       | A7                           | A5       |                           |

| A6                  | A14       | A6                           | A4       |                           |

| A5                  | A13       | A5                           | A3       |                           |

| A4                  | A12       | A4                           | A2       |                           |

| A3                  | A11       | A3                           | A1       |                           |

| A2                  | A10       | A2                           | A0       |                           |

| A1                  | A9        | A1                           | Not used |                           |

| A0                  | A0        | A0                           | Not used |                           |

# Table 10.14 Example of Correspondence between SH7709S and Synchronous DRAM Address Pins (AMX [3:0] = 0100 (32-Bit Bus Width))

**Burst Read:** In the example in figure 10.15 it is assumed that four 2M × 8-bit synchronous DRAMs are connected and a 32-bit data width is used, and the burst length is 1. Following the Tr cycle in which ACTV command output is performed, a READ command is issued in the Tc1, Tc2, and Tc3 cycles, and a READA command in the Tc4 cycle, and the read data is accepted at the rising edge of the external command clock (CKIO) from cycle Td1 to cycle Td4. The Tpc cycle is used to wait for completion of auto-precharge based on the READA command inside the synchronous DRAM; no new access command can be issued to the same bank during this cycle, but access to synchronous DRAM for another area is possible. In the SH7709S, the number of Tpc cycles is determined by the TPC bit specification in MCR, and commands cannot be issued for the same synchronous DRAM during this interval.

The example in figure 10.14 shows the basic cycle. To connect low-speed synchronous DRAM, the cycle can be extended by setting WCR2 and MCR bits. The number of cycles from the ACTV command output cycle, Tr, to the READ command output cycle, Tc1, can be specified by the RCD bits in MCR, with values of 0 to 3 specifying 1 to 4 cycles, respectively. In case of 2 or more cycles, a Trw cycle, in which an NOP command is issued for the synchronous DRAM, is inserted between the Tr cycle and the Tc cycle. The number of cycles from READ and READA command output cycles Tc1-Tc4 to the first read data latch cycle, Td1, can be specified as 1 to 3 cycles

Rev. 5.00, 09/03, page 281 of 760

# Renesas

**Power-On Sequence:** In order to use synchronous DRAM, mode setting must first be performed after powering on. To perform synchronous DRAM initialization correctly, the bus state controller registers must first be set, followed by a write to the synchronous DRAM mode register. In synchronous DRAM mode register setting, the address signal value at that time is latched by a combination of the RAS, CAS, and RD/WR signals. If the value to be set is X, the bus state controller provides for value X to be written to the synchronous DRAM mode register by performing a write to address H'FFFFD000 + X for area 2 synchronous DRAM, and to address H'FFFFE000 + X for area 3 synchronous DRAM. In this operation the data is ignored, but the mode write is performed as a byte-size access. To set burst read/single write, CAS latency 1 to 3, wrap type = sequential, and burst length 1 supported by the SH7709S, arbitrary data is written in a byte-size access.

With 32-bit bus width:

|                        | Area 2   | Area 3   |

|------------------------|----------|----------|

| CAS latency 1          | FFFFD840 | FFFFE840 |

| CAS latency 2          | FFFFD880 | FFFFE880 |

| CAS latency 3          | FFFFD8C0 | FFFFE8C0 |

| With 16-bit bus width: |          |          |

|                        | Area 2   | Area 3   |

| CAS latency 1          | FFFFD420 | FFFFE420 |

| CAS latency 2          | FFFFD440 | FFFFE440 |

| CAS latency 3          | FFFFD460 | FFFFE460 |

|                        |          |          |

Mode register setting timing is shown in figure 10.28.

As a result of the write to address H'FFFFD000 + X or H'FFFFE000 + X, a precharge all banks (PALL) command is first issued in the TRp1 cycle, then a mode register write command is issued in the TMw1 cycle.

Address signals, when the mode-register write command is issued, are as follows:

32-bit bus width:

A15–A9 = 0000100 (burst read and single write)

A8-A6 = CAS latency

A5 = 0 (burst type = sequential)

A4-A2 = 000 (burst length 1)

16-bit bus width:

A14-A8 = 0000100 (burst read and single write) A7-A5 = CAS latency A4 = 0 (burst type = sequential) A3-A1 = 000 (burst length 1)

### 10.3.5 Burst ROM Interface

Setting bits A0BST1–0, A5BST1–0, and A6BST1–0 in BCR1 to a non-zero value allows burst ROM to be connected to areas 0, 5, and 6. The burst ROM interface provides high-speed access to ROM that has a nibble access function. The timing for nibble access to burst ROM is shown in figure 10.29. Two wait cycles are set. Basically, access is performed in the same way as for normal space, but when the first cycle ends the  $\overline{CS0}$  signal is not negated, and only the address is changed before the next access is executed. When 8-bit ROM is connected, the number of consecutive accesses can be set as 4, 8, or 16 by bits A0BST1–0, A5BST1–0, or A6BST1–0. When 16-bit ROM is connected, 4 or 8 can be set in the same way. When 32-bit ROM is connected, only 4 can be set.

$\overline{\text{WAIT}}$  pin sampling is performed in the first access if one or more wait states are set, and is always performed in the second and subsequent accesses.

The second and subsequent access cycles also comprise two cycles when a burst ROM setting is made and the wait specification is 0. The timing in this case is shown in figure 10.30.

However, the  $\overline{WAIT}$  signal is ignored in the following three cases:

- A write to external address space in dual address mode with 16-byte DMA transfer

- Transfer from an external device with DACK to external address space in single address mode with 16-byte DMA transfer

- Cache write-back access

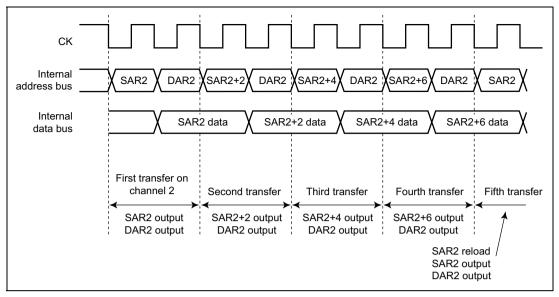

Figure 11.23 Timing Chart of Source Address Reload Function

The reload function can be executed with a transfer data size of 8, 16, or 32 bits.

DMATCR2, which specifies the transfer count, decrements 1 each time a transfer ends regardless of whether the reload function is on or off. Consequently, a multiple of four must be specified in DMATCR2 when the reload function is on. Operation is not guaranteed if other values are specified.

The counter that counts the execution of four transfers for the address reload function is reset by clearing the DME bit in DMAOR or the DE bit in CHCR2, by setting the transfer end flag (TE bit in CHCR2), by DMAC address error, and by NMI input, as well as by a reset, but the SAR2, DAR2, and DMATCR2 registers are not reset. Therefore, if these sources are generated, there will be a mix of an initialized counter and uninitialized registers in the DMAC, and a malfunction will be caused by restarting the DMAC in that state. Consequently, if one of these sources other than setting of the TE bit occurs during use of the address reload function, set SAR2, DAR2, and DMATCR2 again.

#### Renesas

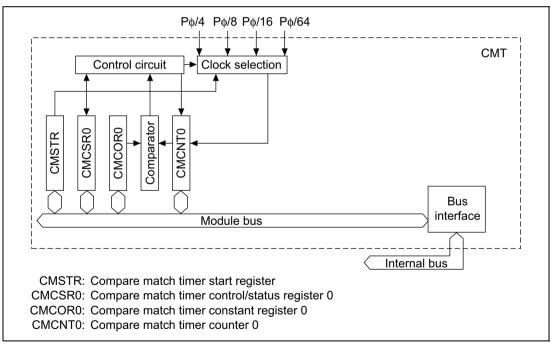

# **11.4** Compare Match Timer (CMT)

## 11.4.1 Overview

The DMAC has an on-chip compare match timer (CMT) to generate DMA transfer requests. The CMT has a 16-bit counter.

### Features

The CMT has the following features:

- Four types of counter input clock can be selected

- One of four internal clocks ( $P\phi/4$ ,  $P\phi/8$ ,  $P\phi/16$ ,  $P\phi/64$ ) can be selected.

- Generates a DMA transfer request when compare match occurs.

### **Block Diagram**

Figure 11.24 shows a block diagram of the CMT.

Figure 11.24 Block Diagram of CMT

Rev. 5.00, 09/03, page 388 of 760

Figure 14.15 Sample Flowchart for Receiving Multiprocessor Serial Data (cont)

Rev. 5.00, 09/03, page 488 of 760

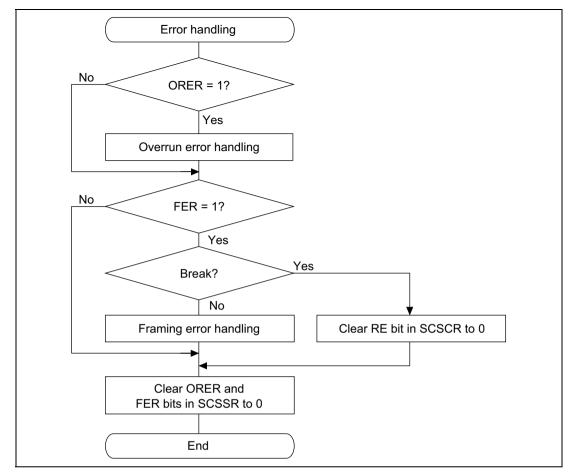

**Bit 3—Framing Error (FER):** Indicates a framing error in the data read from the receive FIFO data register (SCFRDR).

| Bit 3: FER | Description                                                                    |  |  |  |  |

|------------|--------------------------------------------------------------------------------|--|--|--|--|

| 0          | No receive framing error occurred in the data read from SCFRDR (Initial value) |  |  |  |  |

|            | [Clearing conditions]                                                          |  |  |  |  |

|            | (1) When the chip undergoes a power-on reset or enters standby mode            |  |  |  |  |

|            | (2) When no framing error is present in the data read from SCFRDR              |  |  |  |  |

| 1          | A receive framing error occurred in the data read from SCFRDR                  |  |  |  |  |

|            | [Setting condition]                                                            |  |  |  |  |

|            | When a framing error is present in the data read from SCFRDR                   |  |  |  |  |

**Bit 2—Parity Error (PER):** Indicates a parity error in the data read from the receive FIFO data register (SCFRDR).

| Bit 2: PER | Description                                                                   |   |  |  |  |

|------------|-------------------------------------------------------------------------------|---|--|--|--|

| 0          | No receive parity error occurred in the data read from SCFRDR (Initial value) |   |  |  |  |

|            | [Clearing conditions]                                                         |   |  |  |  |

|            | (1) When the chip undergoes a power-on reset or enters standby mode           |   |  |  |  |

|            | (2) When no parity error is present in the data read from SCFRDI              | ۲ |  |  |  |

| 1          | A receive framing error occurred in the data read from SCFRDR                 |   |  |  |  |

|            | [Setting condition]                                                           |   |  |  |  |

|            | When a parity error is present in the data read from SCFRDR                   |   |  |  |  |

| SCPnMD1 | SCPnMD0 | Pin State                       | Read        | Write                                                    |

|---------|---------|---------------------------------|-------------|----------------------------------------------------------|

| 0       | 0       | Other function (see table 18.1) | SCPDR value | Value is written to SCPDR, but does not affect pin state |

|         | 1       | Output                          | SCPDR value | Write value is output from pin                           |

| 1       | 0       | Input (Pull-up<br>MOS on)       | Pin state   | Value is written to SCPDR, but does not affect pin state |

|         | 1       | Input (Pull-up<br>MOS off)      | Pin state   | Value is written to SCPDR, but does not affect pin state |

|         |         |                                 |             | (n = 0  to  6)                                           |

Table 19.24 Read/Write Operation of the SC Port Data Register (SCPDR)

Write SCPnMD1 SCPnMD0 **Pin State** Read Other function Ignored (no effect on pin state) 0 Low level 0 (see table 18.1) 1 Output Ignored (no effect on pin state) Low level Input (Pull-up Ignored (no effect on pin state) 1 0 Pin state MOS on) 1 Input (Pull-up Ignored (no effect on pin state) Pin state MOS off)

(n = 7)

#### 23.3.2 Control Signal Timing

#### Table 23.6 Control Signal Timing

Vcc =  $3.3 \pm 0.3$  V, Vcc = 1.55 to 2.15 V, AVcc =  $3.3 \pm 0.3$  V, Ta = -20 to  $75^{\circ}$ C

| Item                            | Symbol             | Min               | Max | Unit | Figure |

|---------------------------------|--------------------|-------------------|-----|------|--------|

| RESETP pulse width              | t <sub>RESPW</sub> | 20 <sup>*2</sup>  | _   | tcyc | 23.11, |

| RESETP setup time <sup>*1</sup> | t <sub>RESPS</sub> | 20                | _   | ns   | 23.12  |

| RESETP hold time                | t <sub>RESPH</sub> | 4                 |     | ns   |        |

| RESETM pulse width              | t <sub>RESMW</sub> | 20 * <sup>3</sup> |     | tcyc |        |

| RESETM setup time               | t <sub>RESMS</sub> | 6                 |     | ns   |        |

| RESETM hold time                | t <sub>RESMH</sub> | 34                |     | ns   |        |

| BREQ setup time                 | t <sub>BREQS</sub> | 6                 | _   | ns   | 23.14  |

| BREQ hold time                  | t <sub>BREQH</sub> | 4                 |     | ns   |        |

| NMI setup time *1               | t <sub>NMIS</sub>  | 10                |     | ns   | 23.12  |

| NMI hold time                   | t <sub>NMIH</sub>  | 4                 | _   | ns   |        |

| IRQ5–IRQ0 setup time *1         | t <sub>IRQS</sub>  | 10                |     | ns   |        |

| IRQ5–IRQ0 hold time             | t <sub>IRQH</sub>  | 4                 |     | ns   |        |

| IRQOUT delay time               | t <sub>IRQOD</sub> | —                 | 10  | ns   | 23.13  |

| BACK delay time                 | <b>t</b> BACKD     | _                 | 10  | ns   | 23.14, |

| STATUS1, STATUS0 delay time     | t <sub>STD</sub>   | —                 | 10  | ns   | 23.15  |

| Bus tri-state delay time 1      | t <sub>BOFF1</sub> | 0                 | 15  | ns   |        |

| Bus tri-state delay time 2      | t <sub>BOFF2</sub> | 0                 | 15  | ns   |        |

| Bus buffer-on time 1            | t <sub>BON1</sub>  | 0                 | 15  | ns   |        |

| Bus buffer-on time 2            | t <sub>BON2</sub>  | 0                 | 15  | ns   |        |

Notes: 1. RESETP, NMI, and IRQ5 to IRQ0 are asynchronous. Changes are detected at the clock fall when the setup shown is used. When the setup cannot be used, detection can be delayed until the next clock falls.

2. In the standby mode,  $t_{RESPW} = t_{OSC1}$  (100 µs) when XTAL oscillation is continued and  $t_{RESPW} = t_{OSC2}$  (10 ms) when XTAL oscillation is off. In the sleep mode,  $t_{RESPW} = t_{PLL1}$  (100 µs).

When the clock multiplication ratio is changed,  $t_{RESPW} = t_{PLL1}$  (100 µs).

3. In the standby mode,  $t_{RESMW} = t_{OSC2}$  (10 ms). In the sleep mode,  $\overline{RESETM}$  must be kept low until STATUS (0-1) changes to reset (HH). When the clock multiplication ratio is changed,  $\overline{RESETM}$  must be kept low until STATUS (0-1) changes to reset (HH).

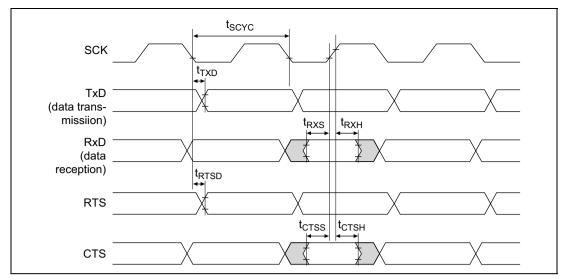

Figure 23.51 SCI I/O Timing in Clock Synchronous Mode

Figure D.2 Package Dimensions (FP-208E)