#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC G4                                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.0GHz                                                                 |

| Co-Processors/DSP               | Multimedia; SIMD                                                       |

| RAM Controllers                 | -                                                                      |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | -                                                                      |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 360-BCBGA, FCCBGA                                                      |

| Supplier Device Package         | 360-FCCBGA (25x25)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc7448hx1000ld |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

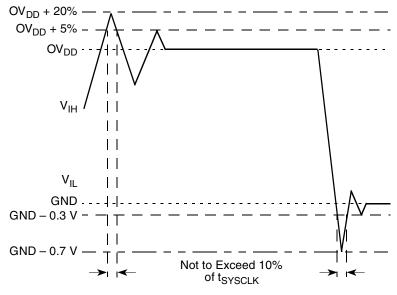

Figure 2 shows the undershoot and overshoot voltage on the MPC7448.

Figure 2. Overshoot/Undershoot Voltage

The MPC7448 provides several I/O voltages to support both compatibility with existing systems and migration to future systems. The MPC7448 core voltage must always be provided at the nominal voltage (see Table 4). The input voltage threshold for each bus is selected by sampling the state of the voltage select pins at the negation of the signal HRESET. The output voltage will swing from GND to the maximum voltage applied to the  $OV_{DD}$  power pins. Table 3 provides the input threshold voltage settings. Because these settings may change in future products, it is recommended that BVSEL[0:1] be configured using resistor options, jumpers, or some other flexible means, with the capability to reconfigure the termination of this signal in the future, if necessary.

| BVSEL0 | BVSEL1 | I/O Voltage Mode <sup>1</sup> | Notes |

|--------|--------|-------------------------------|-------|

| 0      | 0      | 1.8 V                         | 2, 3  |

| 0      | 1      | 2.5 V                         | 2, 4  |

| 1      | 0      | 1.5 V                         | 2     |

| 1      | 1      | 2.5 V                         | 4     |

Table 3. Input Threshold Voltage Setting

- 1. **Caution:** The I/O voltage mode selected must agree with the OV<sub>DD</sub> voltages supplied. See Table 4.

- 2. If used, pull-down resistors should be less than 250  $\Omega.$

- 3. The pin configuration used to select 1.8V mode on the MPC7448 is not compatible with the pin configuration used to select 1.8V mode on the MPC7447A and earlier devices.

- 4. The pin configuration used to select 2.5V mode on the MPC7448 is fully compatible with the pin configuration used to select 2.5V mode on the MPC7447A and earlier devices.

Table 5 provides the package thermal characteristics for the MPC7448. For more information regarding thermal management, see Section 9.7, "Power and Thermal Management Information."

| Characteristic                                                                      | Symbol                 | Value | Unit | Notes |

|-------------------------------------------------------------------------------------|------------------------|-------|------|-------|

| Junction-to-ambient thermal resistance, natural convection, single-layer (1s) board | $R_{	extsf{	heta}JA}$  | 26    | •C/W | 2, 3  |

| Junction-to-ambient thermal resistance, natural convection, four-layer (2s2p) board | $R_{\thetaJMA}$        | 19    | •C/W | 2, 4  |

| Junction-to-ambient thermal resistance, 200 ft/min airflow, single-layer (1s) board | $R_{	extsf{	heta}JMA}$ | 22    | •C/W | 2, 4  |

| Junction-to-ambient thermal resistance, 200 ft/min airflow, four-layer (2s2p) board | $R_{	extsf{	heta}JMA}$ | 16    | •C/W | 2, 4  |

| Junction-to-board thermal resistance                                                | $R_{	extsf{	heta}JB}$  | 11    | •C/W | 5     |

| Junction-to-case thermal resistance                                                 | $R_{	extsf{	heta}JC}$  | < 0.1 | •C/W | 6     |

## Table 5. Package Thermal Characteristics<sup>1</sup>

#### Notes:

- 1. Refer to Section 9.7, "Power and Thermal Management Information," for details about thermal management.

- Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

- 3. Per JEDEC JESD51-2 with the single-layer board horizontal

- 4. Per JEDEC JESD51-6 with the board horizontal

- 5. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 6. This is the thermal resistance between die and case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. The actual value of R<sub>θJC</sub> for the part is less than 0.1°C/W.

## Table 6 provides the DC electrical characteristics for the MPC7448.

### **Table 6. DC Electrical Specifications**

At recommended operating conditions. See Table 4.

| Characteristic                                                                                                                                           | Nominal Bus<br>Voltage <sup>1</sup> | Symbol          | Min                                  | Мах                                  | Unit | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|--------------------------------------|--------------------------------------|------|-------|

| Input high voltage                                                                                                                                       | 1.5                                 | V <sub>IH</sub> | $\mathrm{OV}_\mathrm{DD} 	imes 0.65$ | OV <sub>DD</sub> + 0.3               | V    | 2     |

| (all inputs)                                                                                                                                             | 1.8                                 | -               | $\mathrm{OV}_\mathrm{DD} 	imes 0.65$ | OV <sub>DD</sub> + 0.3               |      |       |

|                                                                                                                                                          | 2.5                                 |                 | 1.7                                  | OV <sub>DD</sub> + 0.3               |      |       |

| Input low voltage                                                                                                                                        | 1.5                                 | V <sub>IL</sub> | -0.3                                 | $\mathrm{OV}_\mathrm{DD} 	imes 0.35$ | V    | 2     |

| (all inputs)                                                                                                                                             | 1.8                                 | -               | -0.3                                 | $\mathrm{OV}_\mathrm{DD} 	imes 0.35$ |      |       |

|                                                                                                                                                          | 2.5                                 |                 | -0.3                                 | 0.7                                  |      |       |

| Input leakage current, all signals except<br>BVSEL0, LSSD_MODE, TCK, TDI, TMS,<br>TRST:<br>V <sub>in</sub> = OV <sub>DD</sub>                            | _                                   | l <sub>in</sub> | —                                    | 50                                   | μA   | 2, 3  |

| V <sub>in</sub> = GND                                                                                                                                    |                                     |                 |                                      | - 50                                 |      |       |

| Input leakage current, BVSEL0,<br><u>LSSD_MODE</u> , <u>TCK</u> , TDI, TMS, <u>TRST</u> :<br>V <sub>in</sub> = OV <sub>DD</sub><br>V <sub>in</sub> = GND | —                                   | l <sub>in</sub> | _                                    | 50<br>- 2000                         | μA   | 2, 6  |

when running a typical benchmark at temperatures in a typical system. The Full-Power Mode–Thermal value is intended to represent the sustained power consumption of the device when running a typical code sequence at high temperature and is recommended to be used as the basis for designing a thermal solution; see Section 9.7, "Power and Thermal Management Information" for more information on thermal solutions. The Full-Power Mode–Maximum value is recommended to be used for power supply design because this represents the maximum peak power draw of the device that a power supply must be capable of sourcing without voltage droop. For information on power consumption when dynamic frequency switching is enabled, see Section 9.7.5, "Dynamic Frequency Switching (DFS)."

|                 | Die Junction                       | Maximum Pr | 11        | N        |          |      |       |  |  |  |  |  |

|-----------------|------------------------------------|------------|-----------|----------|----------|------|-------|--|--|--|--|--|

|                 | Temperature -<br>(T <sub>j</sub> ) | 1000 MHz   | 1420 MHz  | 1600 MHz | 1700 MHz | Unit | Notes |  |  |  |  |  |

| Full-Power Mode |                                    |            |           |          |          |      |       |  |  |  |  |  |

| Typical         | 65 <b>•C</b>                       | 15.0       | 19.0      | 20.0     | 21.0     | W    | 1, 2  |  |  |  |  |  |

| Thermal         | 105 <b>•</b> C                     | 18.6       | 23.3      | 24.4     | 25.6     | W    | 1, 5  |  |  |  |  |  |

| Maximum         | 105 <b>•</b> C                     | 21.6       | 27.1      | 28.4     | 29.8     | W    | 1, 3  |  |  |  |  |  |

|                 |                                    |            | Nap Mode  | e        |          |      |       |  |  |  |  |  |

| Typical         | 105 <b>•</b> C                     | 11.1       | 11.8      | 13.0     | 13.0     | W    | 1,6   |  |  |  |  |  |

|                 |                                    |            | Sleep Mod | le       |          | •    |       |  |  |  |  |  |

| Typical         | 105 <b>•C</b>                      | 10.8       | 11.4      | 12.5     | 12.5     | W    | 1, 6  |  |  |  |  |  |

|                 | Deep Sleep Mode (PLL Disabled)     |            |           |          |          |      |       |  |  |  |  |  |

| Typical         | 105 <b>•</b> C                     | 10.4       | 11.0      | 12.0     | 12.0     | W    | 1, 6  |  |  |  |  |  |

#### Table 7. Power Consumption for MPC7448 at Maximum Rated Frequency

- These values specify the power consumption for the core power supply (V<sub>DD</sub>) at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include I/O supply power (OV<sub>DD</sub>) or PLL supply power (AV<sub>DD</sub>). OV<sub>DD</sub> power is system dependent but is typically < 5% of V<sub>DD</sub> power. Worst case power consumption for AV<sub>DD</sub> < 13 mW. Freescale also offers MPC7448 part numbers that meet lower power consumption specifications; for more information on these devices, see Section 11.2, "Part Numbers Not Fully Addressed by This Document."

- 2. Typical power consumption is an average value measured with the processor operating at its rated maximum processor core frequency (except for Deep Sleep Mode), at nominal recommended V<sub>DD</sub> (see Table 4) and 65°C while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz. This parameter is not 100% tested but periodically sampled.b

- 3. Maximum power consumption is the average measured with the processor operating at its rated maximum processor core frequency, at nominal V<sub>DD</sub> and maximum operating junction temperature (see Table 4) while running an entirely cache-resident, contrived sequence of instructions to keep all the execution units maximally busy.

- 4. Doze mode is not a user-definable state; it is an intermediate state between full-power and either nap or sleep mode. As a result, power consumption for this mode is not tested.

- Thermal power consumption is an average value measured at the nominal recommended V<sub>DD</sub> (see Table 4) and 105 °C while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz. This parameter is not 100% tested but periodically sampled.

- 6. Typical power consumption for these modes is measured at the nominal recommended V<sub>DD</sub> (see Table 4) and 105 °C in the mode described. This parameter is not 100% tested but is periodically sampled.

### Table 8. Clock AC Timing Specifications

At recommended operating conditions. See Table 4.

|                                                   |                     |                                            | Maximum Processor Core Frequency (Speed Grade) |      |          |      |          |      |          |      |      |         |

|---------------------------------------------------|---------------------|--------------------------------------------|------------------------------------------------|------|----------|------|----------|------|----------|------|------|---------|

| Characteristic                                    |                     | Symbol                                     | 1000 MHz                                       |      | 1420 MHz |      | 1600 MHz |      | 1700 MHz |      | Unit | Notes   |

|                                                   |                     |                                            | Min                                            | Max  | Min      | Max  | Min      | Max  | Min      | Мах  |      |         |

| Processor                                         | DFS mode disabled   | f <sub>core</sub>                          | 600                                            | 1000 | 600      | 1420 | 600      | 1600 | 600      | 1700 | MHz  | 1, 8    |

| core<br>frequency                                 | DFS mode enabled    | f <sub>core_DF</sub>                       | 300                                            | 500  | 300      | 710  | 300      | 800  | 300      | 850  |      | 9       |

| VCO frequency                                     |                     | f <sub>VCO</sub>                           | 600                                            | 1000 | 600      | 1420 | 600      | 800  | 600      | 1700 | MHz  | 1, 10   |

| SYSCLK fre                                        | SYSCLK frequency    |                                            | 33                                             | 200  | 33       | 200  | 33       | 200  | 33       | 200  | MHz  | 1, 2, 8 |

| SYSCLK cy                                         | cle time            | t <sub>SYSCLK</sub>                        | 5.0                                            | 30   | 5.0      | 30   | 5.0      | 30   | 5.0      | 30   | ns   | 2       |

| SYSCLK ris                                        | se and fall time    | t <sub>KR</sub> , t <sub>KF</sub>          | —                                              | 0.5  | _        | 0.5  | -        | 0.5  |          | 0.5  | ns   | 3       |

| SYSCLK duty cycle measured at OV <sub>DD</sub> /2 |                     | t <sub>KHKL</sub> /<br>t <sub>SYSCLK</sub> | 40                                             | 60   | 40       | 60   | 40       | 60   | 40       | 60   | %    | 4       |

| SYSCLK cy                                         | cle-to-cycle jitter |                                            | —                                              | 150  | _        | 150  |          | 150  | —        | 150  | ps   | 5, 6    |

| Internal PLL                                      | _ relock time       |                                            | —                                              | 100  | _        | 100  | _        | 100  | _        | 100  | μs   | 7       |

- 1. **Caution**: The SYSCLK frequency and PLL\_CFG[0:5] settings must be chosen such that the resulting SYSCLK (bus) frequency, processor core frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:5] signal description in Section 9.1.1, "PLL Configuration," for valid PLL\_CFG[0:5] settings.

- 2. Actual maximum system bus frequency is system-dependent. See Section 5.2.1, "Clock AC Specifications."

- 3. Rise and fall times for the SYSCLK input measured from 0.4 to 1.4 V

- 4. Timing is guaranteed by design and characterization.

- 5. Guaranteed by design

- 6. The SYSCLK driver's closed loop jitter bandwidth should be less than 1.5 MHz at -3 dB.

- 7. Relock timing is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

- 8. This reflects the maximum and minimum core frequencies when the dynamic frequency switching feature (DFS) is disabled. f<sub>core DFS</sub> provides the maximum and minimum core frequencies when operating in a DFS mode.

- 9. This specification supports the Dynamic Frequency Switching (DFS) feature and is applicable only when one of the DFS modes (divide-by-2 or divide-by-4) is enabled. When DFS is disabled, the core frequency must conform to the maximum and minimum frequencies stated for f<sub>core</sub>.

- 10.Use of the DFS feature does not affect VCO frequency.

### Table 9. Processor Bus AC Timing Specifications<sup>1</sup> (continued)

At recommended operating conditions. See Table 4.

| Parameter                                                                                      | Symbol <sup>2</sup> | All Spee | d Grades | Unit                | Notes      |  |

|------------------------------------------------------------------------------------------------|---------------------|----------|----------|---------------------|------------|--|

| Farameter                                                                                      | Symbol              | Min      | Max      | Unit                | Notes      |  |

| SYSCLK to output high impedance (all except $\overline{TS}$ , $\overline{ARTRY}$ , SHD0, SHD1) | <sup>t</sup> кноz   | —        | 1.8      | ns                  | 5          |  |

| SYSCLK to $\overline{\text{TS}}$ high impedance after precharge                                | t <sub>KHTSPZ</sub> | _        | 1        | t <sub>SYSCLK</sub> | 3, 4, 5    |  |

| Maximum delay to ARTRY/SHD0/SHD1 precharge                                                     | t <sub>KHARP</sub>  | _        | 1        | t <sub>SYSCLK</sub> | 3, 5, 6, 7 |  |

| SYSCLK to ARTRY/SHD0/SHD1 high impedance after precharge                                       | t <sub>KHARPZ</sub> | _        | 2        | t <sub>SYSCLK</sub> | 3, 5, 6, 7 |  |

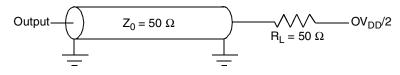

- All input specifications are measured from the midpoint of the signal in question to the midpoint of the rising edge of the input SYSCLK. All output specifications are measured from the midpoint of the rising edge of SYSCLK to the midpoint of the signal in question. All output timings assume a purely resistive 50-Ω load (see Figure 4). Input and output timings are measured at the pin; time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbology used for timing specifications herein follows the pattern of t<sub>(signal)(state)(reference)(state)</sub> for inputs and t<sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>IVKH</sub> symbolizes the time input signals (I) reach the valid state (V) relative to the SYSCLK reference (K) going to the high (H) state or input setup time. And t<sub>KHOV</sub> symbolizes the time from SYSCLK(K) going high (H) until outputs (O) are valid (V) or output valid time. Input hold time can be read as the time that the input signal (I) went invalid (X) with respect to the rising clock edge (KH) (note the position of the reference and its state for inputs) and output hold time can be read as the time from the rising edge (KH) until the output went invalid (OX).

- 3. t<sub>sysclk</sub> is the period of the external clock (SYSCLK) in ns. The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

- 4. According to the bus protocol, TS is driven only by the currently active bus master. It is asserted low and precharged high before returning to high impedance, as shown in Figure 6. The nominal precharge width for TS is t<sub>SYSCLK</sub>, that is, one clock period. Since no master can assert TS on the following clock edge, there is no concern regarding contention with the precharge. Output valid and output hold timing is tested for the signal asserted. Output valid time is tested for precharge. The high-impedance behavior is guaranteed by design.

- 5. Guaranteed by design and not tested

- 6. According to the bus protocol, ARTRY can be driven by multiple bus masters through the clock period immediately following AACK. Bus contention is not an issue because any master asserting ARTRY will be driving it low. Any master asserting it low in the first clock following AACK will then go to high impedance for a fraction of a cycle, then negated for up to an entire cycle (crossing a bus cycle boundary) before being three-stated again. The nominal precharge width for ARTRY is 1.0 t<sub>SYSCLK</sub>; that is, it should be high impedance as shown in Figure 6 before the first opportunity for another master to assert ARTRY. Output valid and output hold timing is tested for the signal asserted. The high-impedance behavior is guaranteed by design.

- 7. According to the MPX bus protocol, SHD0 and SHD1 can be driven by multiple bus masters beginning two cycles after TS. Timing is the same as ARTRY, that is, the signal is high impedance for a fraction of a cycle, then negated for up to an entire cycle (crossing a bus cycle boundary) before being three-stated again. The nominal precharge width for SHD0 and SHD1 is 1.0 t<sub>SYSCLK</sub>. The edges of the precharge vary depending on the programmed ratio of core to bus (PLL configurations).

- BMODE[0:1] and BVSEL[0:1] are mode select inputs. BMODE[0:1] are sampled before and after HRESET negation. BVSEL[0:1] are sampled before HRESET negation. These parameters represent the input setup and hold times for each sample. These values are guaranteed by design and not tested. BMODE[0:1] must remain stable after the second sample; BVSEL[0:1] must remain stable after the first (and only) sample. See Figure 5 for sample timing.

Figure 7 provides the AC test load for TDO and the boundary-scan outputs of the MPC7448.

Figure 7. Alternate AC Test Load for the JTAG Interface

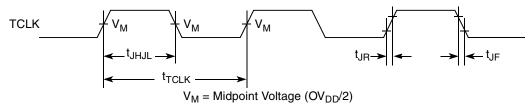

Figure 8 provides the JTAG clock input timing diagram.

Figure 8. JTAG Clock Input Timing Diagram

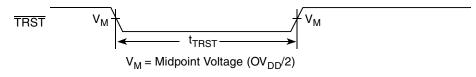

Figure 9 provides the  $\overline{\text{TRST}}$  timing diagram.

Figure 9. TRST Timing Diagram

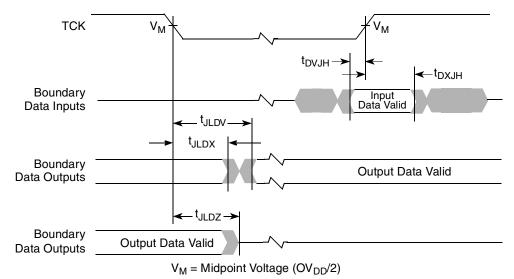

Figure 10 provides the boundary-scan timing diagram.

Figure 10. Boundary-Scan Timing Diagram

#### MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

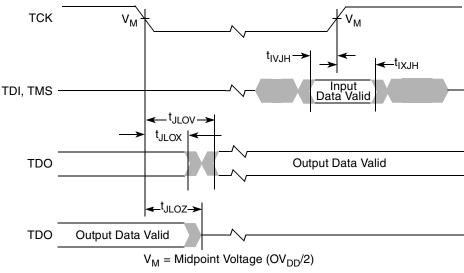

Figure 11 provides the test access port timing diagram.

Figure 11. Test Access Port Timing Diagram

# 5.3 Voltage and Frequency Derating

Voltage and frequency derating is no longer supported for part numbers described by this document beginning with datecode 0613. (See Section 11, "Part Numbering and Marking," for information on date code markings.) It is supported by some MPC7448 part numbers which target low-power applications; see Section 11.2, "Part Numbers Not Fully Addressed by This Document" and the referenced MPC7448 Hardware Specification Addenda for more information on these low-power devices. For those devices which previously supported this feature, information has been archived in the *Chip Errata for the MPC7448* (document order no. MPC7448CE).

# 7 Pinout Listings

Table 11 provides the pinout listing for the MPC7448, 360 HCTE package. The pinouts of the MPC7448 and MPC7447A are compatible, but the requirements regarding the use of the additional power and ground pins have changed. The MPC7448 requires these pins be connected to the appropriate power or ground plane to achieve high core frequencies; see Section 9.3, "Connection Recommendations," for additional information. As a result, these pins should be connected in all new designs.

Additionally, the MPC7448 may be populated on a board designed for a MPC7447 (or MPC7445 or MPC7441), provided the core voltage can be made to match the requirements in Table 4 and all pins defined as 'no connect' for the MPC7447 are unterminated, as required by the *MPC7457 RISC Microprocessor Hardware Specifications*. The MPC7448 uses pins previously marked 'no connect' for the temperature diode pins and for additional power and ground connections. The additional power and ground pins are required to achieve high core frequencies and core frequency will be limited if they are not connected; see Section 9.3, "Connection Recommendations," for additional information. Because these 'no connect' pins in the MPC7447 360 pin package are not driven in functional mode, an MPC7447 can be populated in an MPC7448 board.

### NOTE

Caution must be exercised when performing boundary scan test operations on a board designed for an MPC7448, but populated with an MPC7447 or earlier device. This is because in the MPC7447 it is possible to drive the latches associated with the former 'no connect' pins in the MPC7447, potentially causing contention on those pins. To prevent this, ensure that these pins are not connected on the board or, if they are connected, ensure that the states of internal MPC7447 latches do not cause these pins to be driven during board testing.

For the MPC7448, pins that were defined as the TEST[0:4] factory test signal group on the MPC7447A and earlier devices have been assigned new functions. For most of these, the termination recommendations for the TEST[0:4] pins of the MPC7447A are compatible with the MPC7448 and will allow correct operation with no performance loss. The exception is BVSEL1 (TEST3 on the MPC7447A and earlier devices), which may require a different termination depending which I/O voltage mode is desired; see Table 3 for more information.

### NOTE

This pinout is not compatible with the MPC750, MPC7400, or MPC7410 360 BGA package.

| Signal Name      | Pin Number                                                                                                                                                                                            | Active | I/O    | Notes      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|

| LVRAM            | B10                                                                                                                                                                                                   | —      | _      | 12, 20, 22 |

| NC (no connect)  | A6, A14, A15, B14, B15, C14, C15, C16, C17, C18, C19, D14, D15, D16, D17, D18, D19, E14, E15, F14, F15, G14, G15, H15, H16, J15, J16, J17, J18, J19, K15, K16, K17, K18, K19, L15, L16, L17, L18, L19 | _      |        | 11         |

| LSSD_MODE        | E8                                                                                                                                                                                                    | Low    | Input  | 6, 12      |

| MCP              | C9                                                                                                                                                                                                    | Low    | Input  |            |

| OV <sub>DD</sub> | B4, C2, C12, D5, F2, H3, J5, K2, L5, M3, N6, P2, P8, P11, R4, R13, R16, T6, T9, U2, U12, U16, V4, V7, V10, V14                                                                                        | —      | —      |            |

| OVDD_SENSE       | E18, G18                                                                                                                                                                                              | —      | —      | 16         |

| PLL_CFG[0:4]     | B8, C8, C7, D7, A7                                                                                                                                                                                    | High   | Input  |            |

| PLL_CFG[5]       | D10                                                                                                                                                                                                   | High   | Input  | 9, 20      |

| PMON_IN          | D9                                                                                                                                                                                                    | Low    | Input  | 13         |

| PMON_OUT         | A9                                                                                                                                                                                                    | Low    | Output |            |

| QACK             | G5                                                                                                                                                                                                    | Low    | Input  |            |

| QREQ             | P4                                                                                                                                                                                                    | Low    | Output |            |

| SHD[0:1]         | E4, H5                                                                                                                                                                                                | Low    | I/O    | 3          |

| SMI              | F9                                                                                                                                                                                                    | Low    | Input  |            |

| SRESET           | A2                                                                                                                                                                                                    | Low    | Input  |            |

| SYSCLK           | A10                                                                                                                                                                                                   | _      | Input  |            |

| TA               | К6                                                                                                                                                                                                    | Low    | Input  |            |

| TBEN             | E1                                                                                                                                                                                                    | High   | Input  |            |

| TBST             | F11                                                                                                                                                                                                   | Low    | Output |            |

| ТСК              | C6                                                                                                                                                                                                    | High   | Input  |            |

| TDI              | B9                                                                                                                                                                                                    | High   | Input  | 6          |

| TDO              | A4                                                                                                                                                                                                    | High   | Output |            |

| TEA              | L1                                                                                                                                                                                                    | Low    | Input  |            |

| TEMP_ANODE       | N18                                                                                                                                                                                                   | —      | —      | 17         |

| TEMP_CATHODE     | N19                                                                                                                                                                                                   | _      | _      | 17         |

| TMS              | F1                                                                                                                                                                                                    | High   | Input  | 6          |

| TRST             | A5                                                                                                                                                                                                    | Low    | Input  | 6, 14      |

| TS               | L4                                                                                                                                                                                                    | Low    | I/O    | 3          |

| TSIZ[0:2]        | G6, F7, E7                                                                                                                                                                                            | High   | Output |            |

| TT[0:4]          | E5, E6, F6, E9, C5                                                                                                                                                                                    | High   | I/O    |            |

| WT               | D3                                                                                                                                                                                                    | Low    | Output |            |

| V <sub>DD</sub>  | H8, H10, H12, J7, J9, J11, J13, K8, K10, K12, K14, L7, L9, L11, L13, M8, M10, M12                                                                                                                     | —      |        |            |

| V <sub>DD</sub>  | A13, A16, A18, B17, B19, C13, E13, E16, F12, F17, F19, G11, G16, H14, H17, H19, M14, M16, M18, N15, N17, P16, P18                                                                                     | —      | —      | 15         |

### MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

# 8 Package Description

The following sections provide the package parameters and mechanical dimensions for the HCTE package.

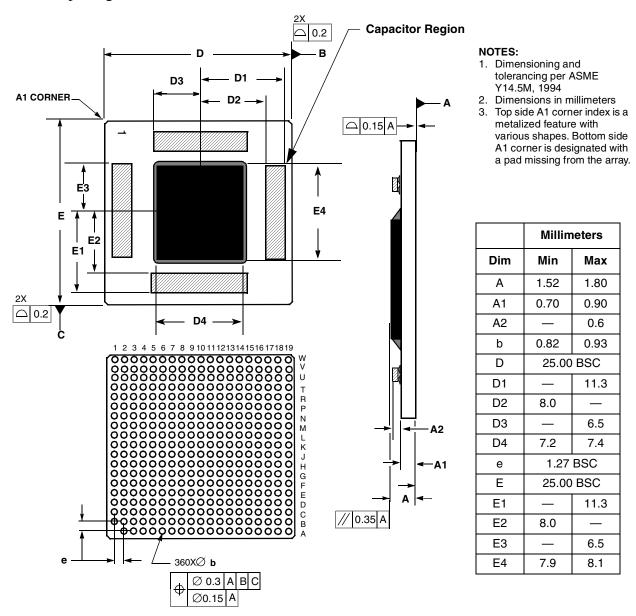

# 8.1 Package Parameters for the MPC7448, 360 HCTE BGA

The package parameters are as provided in the following list. The package type is  $25 \times 25$  mm, 360-lead high coefficient of thermal expansion ceramic ball grid array (HCTE).

| Package outline             | $25 \times 25 \text{ mm}$    |

|-----------------------------|------------------------------|

| Interconnects               | 360 (19 × 19 ball array – 1) |

| Pitch                       | 1.27 mm (50 mil)             |

| Minimum module height       | 2.32 mm                      |

| Maximum module height       | 2.80 mm                      |

| Ball diameter               | 0.89 mm (35 mil)             |

| Coefficient of thermal expa | nsion12.3 ppm/°C             |

# 8.3 Package Parameters for the MPC7448, 360 HCTE LGA

The package parameters are as provided in the following list. The package type is  $25 \times 25$  mm, 360 pin high coefficient of thermal expansion ceramic land grid array (HCTE).

| Package outline                  | $25 \times 25 \text{ mm}$    |

|----------------------------------|------------------------------|

| Interconnects                    | 360 (19 × 19 ball array – 1) |

| Pitch                            | 1.27 mm (50 mil)             |

| Minimum module height            | 1.52 mm                      |

| Maximum module height            | 1.80 mm                      |

| Pad diameter                     | 0.89 mm (35 mil)             |

| Coefficient of thermal expansion | ansion12.3 ppm/°C            |

Package Description

# 8.4 Mechanical Dimensions for the MPC7448, 360 HCTE LGA

Figure 13 provides the mechanical dimensions and bottom surface nomenclature for the MPC7448, 360 HCTE LGA package.

Figure 14. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC7448, 360 HCTE LGA Package

Package Description

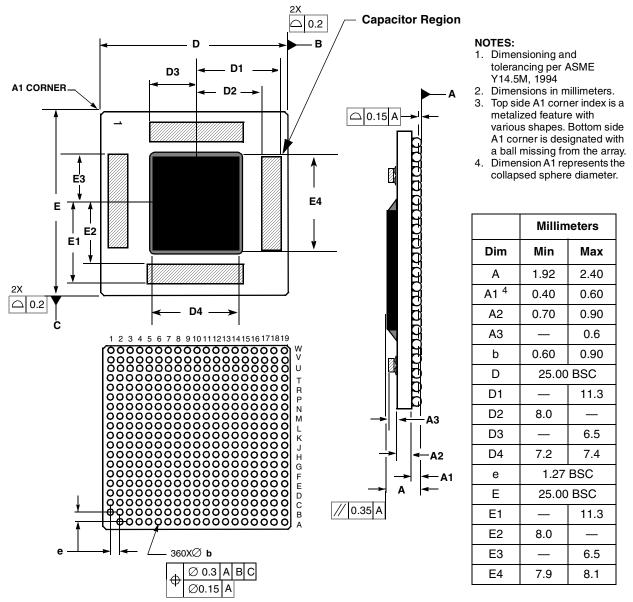

# 8.6 Mechanical Dimensions for the MPC7448, 360 HCTE RoHS-Compliant BGA

Figure 13 provides the mechanical dimensions and bottom surface nomenclature for the MPC7448, 360 HCTE BGA package with RoHS-compliant lead-free spheres.

Figure 15. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC7448, 360 HCTE RoHS-Compliant BGA Package

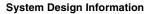

# 9 System Design Information

This section provides system and thermal design requirements and recommendations for successful application of the MPC7448.

# 9.1 Clocks

The following sections provide more detailed information regarding the clocking of the MPC7448.

# 9.1.1 PLL Configuration

The MPC7448 PLL is configured by the PLL\_CFG[0:5] signals. For a given SYSCLK (bus) frequency, the PLL configuration signals set the internal CPU and VCO frequency of operation. The PLL configuration for the MPC7448 is shown in Table 12. In this example, shaded cells represent settings that, for a given SYSCLK frequency, result in core and/or VCO frequencies that do not comply with Table 8. When enabled, dynamic frequency switching (DFS) also affects the core frequency by halving or quartering the bus-to-core multiplier; see Section 9.7.5, "Dynamic Frequency Switching (DFS)," for more information. Note that when DFS is enabled the resulting core frequency must meet the adjusted minimum core frequency requirements ( $f_{core_DFS}$ ) described in Table 8. Note that the PLL\_CFG[5] is currently used for factory test only and should be tied low, and that the MPC7448 PLL configuration settings are compatible with the MPC7447A PLL configuration settings when PLL\_CFG[5] = 0.

|              | Example Core and VCO Frequency in MHz |                         |                        |           |             |           |           |            |            |            |            |  |  |

|--------------|---------------------------------------|-------------------------|------------------------|-----------|-------------|-----------|-----------|------------|------------|------------|------------|--|--|

| PLL_CFG[0:5] | Bus-to-Core                           | Core-to-VCO             | Bus (SYSCLK) Frequency |           |             |           |           |            |            |            |            |  |  |

|              | Multiplier <sup>5</sup>               | Multiplier <sup>5</sup> | 33.3<br>MHz            | 50<br>MHz | 66.6<br>MHz | 75<br>MHz | 83<br>MHz | 100<br>MHz | 133<br>MHz | 167<br>MHz | 200<br>MHz |  |  |

| 010000       | 2x <sup>6</sup>                       | 1x                      |                        |           |             |           |           |            |            |            |            |  |  |

| 100000       | 3x <sup>6</sup>                       | 1x                      |                        |           |             |           |           |            |            |            | 600        |  |  |

| 101000       | 4x <sup>6</sup>                       | 1x                      |                        |           |             |           |           |            |            | 667        | 800        |  |  |

| 101100       | 5x                                    | 1x                      |                        |           |             |           |           |            | 667        | 835        | 1000       |  |  |

| 100100       | 5.5x                                  | 1x                      |                        |           |             |           |           |            | 733        | 919        | 1100       |  |  |

| 110100       | 6x                                    | 1x                      |                        |           |             |           |           | 600        | 800        | 1002       | 1200       |  |  |

| 010100       | 6.5x                                  | 1x                      |                        |           |             |           |           | 650        | 866        | 1086       | 1300       |  |  |

| 001000       | 7x                                    | 1x                      |                        |           |             |           |           | 700        | 931        | 1169       | 1400       |  |  |

| 000100       | 7.5x                                  | 1x                      |                        |           |             |           | 623       | 750        | 1000       | 1253       | 1500       |  |  |

| 110000       | 8x                                    | 1x                      |                        |           |             | 600       | 664       | 800        | 1064       | 1336       | 1600       |  |  |

| 011000       | 8.5x                                  | 1x                      |                        |           |             | 638       | 706       | 850        | 1131       | 1417       | 1700       |  |  |

| 011110       | 9x                                    | 1x                      |                        |           | 600         | 675       | 747       | 900        | 1197       | 1500       |            |  |  |

| 011100       | 9.5x                                  | 1x                      |                        |           | 633         | 712       | 789       | 950        | 1264       | 1583       |            |  |  |

| 101010       | 10x                                   | 1x                      |                        |           | 667         | 750       | 830       | 1000       | 1333       | 1667       |            |  |  |

| 100010       | 10.5x                                 | 1x                      |                        |           | 700         | 938       | 872       | 1050       | 1397       |            |            |  |  |

Table 12. MPC7448 Microprocessor PLL Configuration Example

| MPC7448 RISC Microprocesso | r Hardware Specifications, | Rev. 4 |

|----------------------------|----------------------------|--------|

|----------------------------|----------------------------|--------|

# 9.2.4 Decoupling Recommendations

Due to the MPC7448 dynamic power management feature, large address and data buses, and high operating frequencies, the MPC7448 can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC7448 system, and the MPC7448 itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer use sufficient decoupling capacitors, typically one capacitor for every  $V_{DD}$  pin, and a similar amount for the OV<sub>DD</sub> pins, placed as close as possible to the power pins of the MPC7448. It is also recommended that these decoupling capacitors receive their power from separate  $V_{DD}$ , OV<sub>DD</sub>, and GND power planes in the PCB, using short traces to minimize inductance.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic surface mount technology (SMT) capacitors should be used to minimize lead inductance. Orientations where connections are made along the length of the part, such as 0204, are preferable but not mandatory. Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993) and contrary to previous recommendations for decoupling Freescale microprocessors, multiple small capacitors of equal value are recommended over using multiple values of capacitance.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$  and  $OV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low equivalent series resistance (ESR) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors are 100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

# 9.3 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unless otherwise noted, unused active low inputs should be tied to  $OV_{DD}$  and unused active high inputs should be connected to GND. All NC (no connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $OV_{DD}$ , and GND pins in the MPC7448. For backward compatibility with the MPC7447, MPC7445, and MP7441, or for migrating a system originally designed for one of these devices to the MPC7448, the new power and ground signals (formerly NC, see Table 11) may be left unconnected if the core frequency is 1 GHz or less. Operation above 1 GHz requires that these additional power and ground signals be connected, and it is strongly recommended that all new designs include the additional connections. See also Section 7, "Pinout Listings," for additional information.

The MPC7448 provides VDD\_SENSE, OVDD\_SENSE, and GND\_SENSE pins. These pins connect directly to the power/ground planes in the device package and are intended to allow an external device to measure the voltage present on the  $V_{DD}$ ,  $OV_{DD}$  and GND planes in the device package. The most common use for these signals is as a feedback signal to a power supply regulator to allow it to compensate for board losses and supply the correct voltage at the device. (Note that all voltage parameters are specified at the pins of the device.) If not used for this purpose, it is recommended that these signals be connected to test points that can be used in the event that an accurate measurement of the voltage at the device is needed during system debug. Otherwise, these signals should be connected to the appropriate power/ground planes on the circuit board or left unconnected.

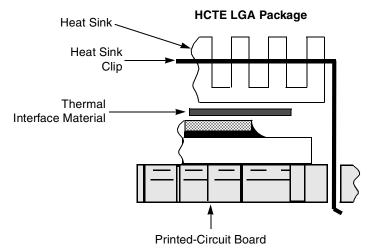

### Figure 23. LGA Package Exploded Cross-Sectional View with Several Heat Sink Options

There are several commercially-available heat sinks for the MPC7448 provided by the following vendors:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                                  | 603-224-9988 |

|----------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #12<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                                 | 408-567-8082 |

| Calgreg Thermal Solutions<br>60 Alhambra Road, Suite 1<br>Warwick, RI 02886<br>Internet: www.calgregthermalsolutions.com         | 888-732-6100 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com     | 818-842-7277 |

| Tyco Electronics<br>Chip Coolers <sup>™</sup><br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.tycoelectronics.com | 800-522-6752 |

| Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                        | 603-635-2800 |

Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost.

MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

System Design Information

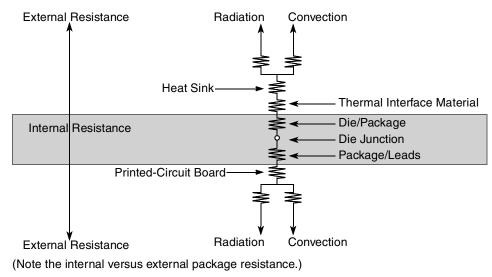

# 9.7.1 Internal Package Conduction Resistance

For the exposed-die packaging technology described in Table 5, the intrinsic conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance (the case is actually the top of the exposed silicon die)

- The die junction-to-board thermal resistance

Figure 24 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.

Figure 24. C4 Package with Heat Sink Mounted to a Printed-Circuit Board

Heat generated on the active side of the chip is conducted through the silicon, through the heat sink attach material (or thermal interface material), and, finally, to the heat sink, where it is removed by forced-air convection.

Because the silicon thermal resistance is quite small, the temperature drop in the silicon may be neglected for a first-order analysis. Thus, the thermal interface material and the heat sink conduction/convective thermal resistances are the dominant terms.

# 9.7.2 Thermal Interface Materials

A thermal interface material is recommended at the package lid-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 25 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, fluoroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. That is, the bare joint results in a thermal resistance approximately seven times greater than the thermal grease joint.

Often, heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 22). Therefore, synthetic grease offers the best thermal performance due to the low interface pressure and is recommended due to the high power dissipation of the MPC7448. Of course, the selection

Due to the complexity and variety of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection, and conduction) may vary widely. For these reasons, we recommend using conjugate heat transfer models for the board as well as system-level designs.

For system thermal modeling, the MPC7448 thermal model is shown in Figure 26. Four volumes represent this device. Two of the volumes, solder ball-air and substrate, are modeled using the package outline size of the package. The other two, die and bump-underfill, have the same size as the die. The silicon die should be modeled  $8.0 \times 7.3 \times 0.86 \text{ mm}^3$  with the heat source applied as a uniform source at the bottom of the volume. The bump and underfill layer is modeled as  $8.0 \times 7.3 \times 0.07 \text{ mm}^3$  collapsed in the z-direction with a thermal conductivity of  $5.0 \text{ W/(m} \cdot \text{K})$  in the z-direction. The substrate volume is  $25 \times 25 \times 1.14 \text{ mm}^3$  and has 9.9 W/(m  $\cdot$  K) isotropic conductivity in the xy-plane and 2.95 W/(m  $\cdot$  K) in the direction of the z-axis. The solder ball and air layer are modeled with the same horizontal dimensions as the substrate and is 0.8 mm thick. For the LGA package the solder and air layer is 0.1 mm thick, but the material properties are the same. It can also be modeled as a collapsed volume using orthotropic material properties: 0.034 W/(m  $\cdot$  K) in the xy-plane direction and 11.2 W/(m  $\cdot$  K) in the direction of the z-axis.

| Conductivity                                                         | Value                     | Unit      |                                  |                    |           |  |

|----------------------------------------------------------------------|---------------------------|-----------|----------------------------------|--------------------|-----------|--|

| Die (8.0 × 7.3 × 0.86 mm <sup>3</sup> )                              |                           | 1 1       | l l                              | Die                |           |  |

| (                                                                    |                           |           | z                                | Bump and Underfill |           |  |

| Silicon                                                              | Temperature-<br>dependent | W/(m • K) |                                  | Substrate          |           |  |

| Bump and Underfill (8.0 $\times$ 7.3 $\times$ 0.07 mm <sup>3</sup> ) |                           | -         | Solder and Air                   |                    |           |  |

| Bump and Underini (8.0 × 7.3 × 0.07 mm <sup>-</sup> )                |                           | -         | Side View of Model (Not to Scale |                    |           |  |

| kz                                                                   | 5.0                       | W/(m ∙ K) |                                  |                    |           |  |

| Substrate (25 $	imes$ 25 $	imes$ 1.14 mm <sup>3</sup> )              |                           |           | <u>×</u>                         |                    |           |  |

| k <sub>x</sub>                                                       | 9.9                       | W/(m • K) |                                  |                    |           |  |

| k <sub>y</sub>                                                       | 9.9                       |           |                                  |                    | Substrate |  |

| k <sub>z</sub>                                                       | 2.95                      |           |                                  |                    |           |  |

| Solder Ball and Air (25 $	imes$ 25 $	imes$ 0.8 mm <sup>3</sup> )     |                           |           | Die                              |                    |           |  |

| k <sub>x</sub>                                                       | 0.034                     | W/(m • K) |                                  |                    |           |  |

| k <sub>y</sub>                                                       | 0.034                     | ]         |                                  |                    |           |  |

| k <sub>z</sub>                                                       | 11.2                      |           | у                                |                    |           |  |

|                                                                      |                           | •         |                                  |                    |           |  |

Top View of Model (Not to Scale)

Figure 26. Recommended Thermal Model of MPC7448

System Design Information

| DFS mode disabled                                                         |                          | DFS divide-by-2<br>(HID1[DFS2] = 1 | mode enabled<br>or DFS2 = 0) | DFS divide-by-4 mode enabled<br>(HID1[DFS4] = 1 or DFS4 = 0) |                          |  |

|---------------------------------------------------------------------------|--------------------------|------------------------------------|------------------------------|--------------------------------------------------------------|--------------------------|--|

| Bus-to-Core Multiplier<br>Configured by<br>PLL_CFG[0:5]<br>(see Table 12) | HID1[PC0-5] <sup>3</sup> | Bus-to-Core<br>Multiplier          | HID1[PC0-5] <sup>3</sup>     | Bus-to-Core<br>Multiplier                                    | HID1[PC0-5] <sup>3</sup> |  |

| 2x <sup>4</sup>                                                           | 010000                   | N/A (unchanged) <sup>1</sup>       | unchanged <sup>1</sup>       | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 3x <sup>4</sup>                                                           | 100000                   | N/A (unchanged) <sup>1</sup>       | unchanged <sup>1</sup>       | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 4x <sup>4</sup>                                                           | 101000                   | 2x <sup>4</sup>                    | 010000                       | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 5x                                                                        | 101100                   | 2.5x <sup>4</sup>                  | 010101                       | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 5.5x                                                                      | 100100                   | 2.75x <sup>4</sup>                 | 110101 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 6x                                                                        | 110100                   | 3x <sup>4</sup>                    | 100000                       | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 6.5x                                                                      | 010100                   | 3.25x <sup>4</sup>                 | 100000 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 7x                                                                        | 001000                   | 3.5x <sup>4</sup>                  | 110101                       | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 7.5x                                                                      | 000100                   | 3.75x <sup>4</sup>                 | 110101 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 8x                                                                        | 110000                   | 4x <sup>4</sup>                    | 101000 <sup>4</sup>          | 2x <sup>4</sup>                                              | 010000                   |  |

| 8.5x                                                                      | 011000                   | 4.25x <sup>4</sup>                 | 101000 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 9x                                                                        | 011110                   | 4.5x <sup>4</sup>                  | 011101                       | 2.25x <sup>4</sup>                                           | 010000 <sup>2</sup>      |  |

| 9.5x                                                                      | 011100                   | 4.75x <sup>4</sup>                 | 011101 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 10x                                                                       | 101010                   | 5x                                 | 101100                       | 2.5x <sup>4</sup>                                            | 010101                   |  |

| 10.5x                                                                     | 100010                   | 5.25x                              | 101100 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 11x                                                                       | 100110                   | 5.5x                               | 100100                       | 2.75x <sup>4</sup>                                           | 010101 <sup>2</sup>      |  |

| 11.5x                                                                     | 000000                   | 5.75x                              | 100100 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 12x                                                                       | 101110                   | 6x                                 | 110100                       | 3x <sup>4</sup>                                              | 100000                   |  |

| 12.5x                                                                     | 111110                   | 6.25x                              | 110100 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 13x                                                                       | 010110                   | 6.5x                               | 010100                       | 3.25x <sup>4</sup>                                           | 100000 <sup>2</sup>      |  |

| 13.5x                                                                     | 111000                   | 6.75                               | 010100 <sup>2</sup>          | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |  |

| 14x                                                                       | 110010                   | 7x                                 | 001000                       | 3.5x <sup>4</sup>                                            | 110101                   |  |

| 15x                                                                       | 000110                   | 7.5x                               | 000100                       | 3.75x <sup>4</sup>                                           | 110101 <sup>2</sup>      |  |

| 16x                                                                       | 110110                   | 8x                                 | 110000                       | 4x <sup>4</sup>                                              | 101000                   |  |

| 17x                                                                       | 000010                   | 8.5x                               | 011000                       | 4.25x <sup>4</sup>                                           | 101000 <sup>2</sup>      |  |

| 18x                                                                       | 001010                   | 9x                                 | 011110                       | 4.5x <sup>4</sup>                                            | 011101                   |  |

| 20x                                                                       | 001110                   | 10x                                | 101010                       | 5x                                                           | 101100                   |  |

| 21x                                                                       | 010010                   | 10.5x                              | 100010                       | 5.25x                                                        | 101100 <sup>2</sup>      |  |

## Table 16. Valid Divide Ratio Configurations

### MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

# **11 Part Numbering and Marking**

Ordering information for the part numbers fully covered by this specification document is provided in Section 11.1, "Part Numbers Fully Addressed by This Document." Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact a local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier that may specify special application conditions. An optional specification modifier may also apply for parts to indicate a specific change in specifications, such as support for an extended temperature range. Finally, each part number contains a revision level code that refers to the die mask revision number. Section 11.2, "Part Numbers Not Fully Addressed by This Document," lists the part numbers that do not fully conform to the specifications of this document. These special part numbers require an additional document called a hardware specification addendum.

# 11.1 Part Numbers Fully Addressed by This Document

Table 18 provides the Freescale part numbering nomenclature for the MPC7448 part numbers fully addressed by this document. For information regarding other MPC7448 part numbers, see Section 11.2, "Part Numbers Not Fully Addressed by This Document."

| XX                     | 7448               | XX                             | nnnn                   | L                                  | x                                                      |

|------------------------|--------------------|--------------------------------|------------------------|------------------------------------|--------------------------------------------------------|

| Product<br>Code        | Part<br>Identifier | Package                        | Processor<br>Frequency | Application<br>Modifier            | Revision Level                                         |

| MC<br>PPC <sup>1</sup> | 7448               | HX = HCTE BGA<br>VS = RoHS LGA | 1700                   | L: 1.3 V +20/–50 mV<br>0 to 105 °C | C: 2.1; PVR = 0x8004_0201<br>D: 2.2; PVR = 0x8004_0202 |

|                        |                    | VU = RoHS BGA                  | 1600                   | L: 1.25 V ± 50 mV<br>0 to 105 °C   |                                                        |

|                        |                    |                                | 1420                   | L: 1.2 V ± 50 mV<br>0 to 105 °C    |                                                        |

|                        |                    |                                | 1000                   | L: 1.15 V ± 50 mV<br>0 to 105 °C   |                                                        |

## Table 18. Part Numbering Nomenclature

### Notes:

1. The P prefix in a Freescale part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur as pilot production prototypes are shipped.