#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC G4                                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.42GHz                                                                |

| Co-Processors/DSP               | Multimedia; SIMD                                                       |

| RAM Controllers                 | -                                                                      |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | -                                                                      |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 360-CLGA, FCCLGA                                                       |

| Supplier Device Package         | 360-FCCLGA (25x25)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc7448vs1420lc |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Reliability and serviceability

- Parity checking on system bus

- Parity checking on the L1 caches and L2 data tags

- ECC or parity checking on L2 data

# 3 Comparison with the MPC7447A, MPC7447, MPC7445, and MPC7441

Table 1 compares the key features of the MPC7448 with the key features of the earlier MPC7447A, MPC7447, MPC7445, and MPC7441. All are based on the MPC7450 RISC microprocessor and are architecturally very similar. The MPC7448 is identical to the MPC7447A, but the MPC7448 supports 1 Mbyte of L2 cache with ECC and the use of dynamic frequency switching (DFS) with more bus-to-core ratios.

| Microarchitectural Specs                | MPC7448        | MPC7447A   | MPC7447            | MPC7445 | MPC7441 |  |  |  |

|-----------------------------------------|----------------|------------|--------------------|---------|---------|--|--|--|

| Basic Pipeline Functions                |                |            |                    |         |         |  |  |  |

| Logic inversions per cycle              |                | 18         |                    |         |         |  |  |  |

| Pipeline stages up to execute           |                |            | 5                  |         |         |  |  |  |

| Total pipeline stages (minimum)         |                |            | 7                  |         |         |  |  |  |

| Pipeline maximum instruction throughput |                |            | 3 + branch         |         |         |  |  |  |

| Pipeline                                | Resources      |            |                    |         |         |  |  |  |

| Instruction buffer size                 |                |            | 12                 |         |         |  |  |  |

| Completion buffer size                  |                |            | 16                 |         |         |  |  |  |

| Renames (integer, float, vector)        |                |            | 16, 16, 16         |         |         |  |  |  |

| Maximum Exe                             | ution Throug   | nput       |                    |         |         |  |  |  |

| SFX                                     |                |            | 3                  |         |         |  |  |  |

| Vector                                  |                | 2 (a       | ny 2 of 4 uni      | ts)     |         |  |  |  |

| Scalar floating-point                   |                |            | 1                  |         |         |  |  |  |

| Out-of-Order Window                     | Size in Execut | ion Queues |                    |         |         |  |  |  |

| SFX integer units                       |                | 1 en       | try $	imes$ 3 queu | les     |         |  |  |  |

| Vector units                            |                | ln o       | rder, 4 queu       | es      |         |  |  |  |

| Scalar floating-point unit              |                |            | In order           |         |         |  |  |  |

| Branch Proce                            | ssing Resourc  | es         |                    |         |         |  |  |  |

| Prediction structures                   |                | BTIC       | , BHT, link s      | tack    |         |  |  |  |

| BTIC size, associativity                |                | 128        | B-entry, 4-wa      | ay      |         |  |  |  |

| BHT size                                |                |            | 2K-entry           |         |         |  |  |  |

| Link stack depth                        |                |            | 8                  |         |         |  |  |  |

| Unresolved branches supported           |                |            | 3                  |         |         |  |  |  |

| Branch taken penalty (BTIC hit)         |                |            | 1                  |         |         |  |  |  |

| Minimum misprediction penalty           |                |            | 6                  |         |         |  |  |  |

#### Table 1. Microarchitecture Comparison

#### Electrical and Thermal Characteristics

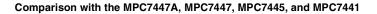

Figure 2 shows the undershoot and overshoot voltage on the MPC7448.

Figure 2. Overshoot/Undershoot Voltage

The MPC7448 provides several I/O voltages to support both compatibility with existing systems and migration to future systems. The MPC7448 core voltage must always be provided at the nominal voltage (see Table 4). The input voltage threshold for each bus is selected by sampling the state of the voltage select pins at the negation of the signal HRESET. The output voltage will swing from GND to the maximum voltage applied to the  $OV_{DD}$  power pins. Table 3 provides the input threshold voltage settings. Because these settings may change in future products, it is recommended that BVSEL[0:1] be configured using resistor options, jumpers, or some other flexible means, with the capability to reconfigure the termination of this signal in the future, if necessary.

| BVSEL0 | BVSEL1 | I/O Voltage Mode <sup>1</sup> | Notes |

|--------|--------|-------------------------------|-------|

| 0      | 0      | 1.8 V                         | 2, 3  |

| 0      | 1      | 2.5 V                         | 2, 4  |

| 1      | 0      | 1.5 V                         | 2     |

| 1      | 1      | 2.5 V                         | 4     |

Table 3. Input Threshold Voltage Setting

Notes:

- 1. **Caution:** The I/O voltage mode selected must agree with the OV<sub>DD</sub> voltages supplied. See Table 4.

- 2. If used, pull-down resistors should be less than 250  $\Omega.$

- 3. The pin configuration used to select 1.8V mode on the MPC7448 is not compatible with the pin configuration used to select 1.8V mode on the MPC7447A and earlier devices.

- 4. The pin configuration used to select 2.5V mode on the MPC7448 is fully compatible with the pin configuration used to select 2.5V mode on the MPC7447A and earlier devices.

#### Table 6. DC Electrical Specifications (continued)

At recommended operating conditions. See Table 4.

| Character                                                                        | istic                 | Nominal Bus<br>Voltage <sup>1</sup> | Symbol           | Min                     | Мах        | Unit | Notes   |

|----------------------------------------------------------------------------------|-----------------------|-------------------------------------|------------------|-------------------------|------------|------|---------|

| High-impedance (off-state) leakage current: $V_{in} = OV_{DD}$<br>$V_{in} = GND$ |                       | _                                   | I <sub>TSI</sub> | _                       | 50<br>- 50 | μA   | 2, 3, 4 |

| Output high voltage @ IC                                                         | <sub>0H</sub> = -5 mA | 1.5                                 | V <sub>OH</sub>  | OV <sub>DD</sub> - 0.45 | _          | V    |         |

|                                                                                  |                       |                                     |                  | OV <sub>DD</sub> - 0.45 | _          |      |         |

|                                                                                  |                       | 2.5                                 |                  | 1.8                     | _          |      |         |

| Output low voltage @ I <sub>OI</sub>                                             | = 5 mA                | 1.5                                 | V <sub>OL</sub>  | _                       | 0.45       | V    |         |

|                                                                                  |                       | 1.8                                 |                  | _                       | 0.45       |      |         |

|                                                                                  |                       | 2.5                                 |                  | _                       | 0.6        |      |         |

| Capacitance,<br>V <sub>in</sub> = 0 V, f = 1 MHz                                 | All inputs            |                                     | C <sub>in</sub>  | _                       | 8.0        | pF   | 5       |

#### Notes:

1. Nominal voltages; see Table 4 for recommended operating conditions.

2. All I/O signals are referenced to OV<sub>DD</sub>.

3. Excludes test signals and IEEE Std. 1149.1 boundary scan (JTAG) signals

4. The leakage is measured for nominal  $OV_{DD}$  and  $V_{DD}$ , or both  $OV_{DD}$  and  $V_{DD}$  must vary in the same direction (for example, both  $OV_{DD}$  and  $V_{DD}$  vary by either +5% or -5%).

5. Capacitance is periodically sampled rather than 100% tested.

6. These pins have internal pull-up resistors.

Table 7 provides the power consumption for the MPC7448 part numbers described by this document; see Section 11.1, "Part Numbers Fully Addressed by This Document," for information regarding which part numbers are described by this document. Freescale also offers MPC7448 part numbers that meet lower power consumption specifications by adhering to lower core voltage and core frequency specifications. For more information on these devices, including references to the MPC7448 Hardware Specification Addenda that describe these devices, see Section 11.2, "Part Numbers Not Fully Addressed by This Document."

The power consumptions provided in Table 7 represent the power consumption of each speed grade when operated at the rated maximum core frequency (see Table 8). Freescale sorts devices by power as well as by core frequency, and power limits for each speed grade are independent of each other. Each device is tested at its maximum core frequency only. (Note that Deep Sleep Mode power consumption is independent of clock frequency.) Operating a device at a frequency lower than its rated maximum is fully supported provided the clock frequencies are within the specifications given in Table 8, and a device operated below its rated maximum will have lower power consumption. However, inferences should not be made about a device's power consumption based on the power specifications of another (lower) speed grade. For example, a 1700 MHz device operated at 1420 MHz may not exhibit the same power consumption as a 1420 MHz device operated at 1420 MHz.

For all MPC7448 devices, the following guidelines on the use of these parameters for system design are suggested. The Full-Power Mode–Typical value represents the sustained power consumption of the device

#### **Electrical and Thermal Characteristics**

when running a typical benchmark at temperatures in a typical system. The Full-Power Mode–Thermal value is intended to represent the sustained power consumption of the device when running a typical code sequence at high temperature and is recommended to be used as the basis for designing a thermal solution; see Section 9.7, "Power and Thermal Management Information" for more information on thermal solutions. The Full-Power Mode–Maximum value is recommended to be used for power supply design because this represents the maximum peak power draw of the device that a power supply must be capable of sourcing without voltage droop. For information on power consumption when dynamic frequency switching is enabled, see Section 9.7.5, "Dynamic Frequency Switching (DFS)."

|         | Die Junction                       | Maximum Processor Core Frequency (Speed Grade, MHz) |              |          |          |      |       |  |  |

|---------|------------------------------------|-----------------------------------------------------|--------------|----------|----------|------|-------|--|--|

|         | Temperature -<br>(T <sub>j</sub> ) | 1000 MHz                                            | 1420 MHz     | 1600 MHz | 1700 MHz | Unit | Notes |  |  |

|         |                                    |                                                     | Full-Power M | lode     |          |      |       |  |  |

| Typical | 65 <b>•C</b>                       | 15.0                                                | 19.0         | 20.0     | 21.0     | W    | 1, 2  |  |  |

| Thermal | 105 <b>•</b> C                     | 18.6                                                | 23.3         | 24.4     | 25.6     | W    | 1, 5  |  |  |

| Maximum | 105 <b>•</b> C                     | 21.6                                                | 27.1         | 28.4     | 29.8     | W    | 1, 3  |  |  |

|         |                                    |                                                     | Nap Mode     | e        |          |      |       |  |  |

| Typical | 105 <b>•</b> C                     | 11.1                                                | 11.8         | 13.0     | 13.0     | W    | 1,6   |  |  |

|         |                                    |                                                     | Sleep Mod    | le       |          |      |       |  |  |

| Typical | 105 <b>•C</b>                      | 10.8                                                | 11.4         | 12.5     | 12.5     | W    | 1, 6  |  |  |

|         | Deep Sleep Mode (PLL Disabled)     |                                                     |              |          |          |      |       |  |  |

| Typical | 105 <b>•</b> C                     | 10.4                                                | 11.0         | 12.0     | 12.0     | W    | 1, 6  |  |  |

#### Table 7. Power Consumption for MPC7448 at Maximum Rated Frequency

Notes:

- These values specify the power consumption for the core power supply (V<sub>DD</sub>) at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include I/O supply power (OV<sub>DD</sub>) or PLL supply power (AV<sub>DD</sub>). OV<sub>DD</sub> power is system dependent but is typically < 5% of V<sub>DD</sub> power. Worst case power consumption for AV<sub>DD</sub> < 13 mW. Freescale also offers MPC7448 part numbers that meet lower power consumption specifications; for more information on these devices, see Section 11.2, "Part Numbers Not Fully Addressed by This Document."

- 2. Typical power consumption is an average value measured with the processor operating at its rated maximum processor core frequency (except for Deep Sleep Mode), at nominal recommended V<sub>DD</sub> (see Table 4) and 65°C while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz. This parameter is not 100% tested but periodically sampled.b

- 3. Maximum power consumption is the average measured with the processor operating at its rated maximum processor core frequency, at nominal V<sub>DD</sub> and maximum operating junction temperature (see Table 4) while running an entirely cache-resident, contrived sequence of instructions to keep all the execution units maximally busy.

- 4. Doze mode is not a user-definable state; it is an intermediate state between full-power and either nap or sleep mode. As a result, power consumption for this mode is not tested.

- Thermal power consumption is an average value measured at the nominal recommended V<sub>DD</sub> (see Table 4) and 105 °C while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz. This parameter is not 100% tested but periodically sampled.

- 6. Typical power consumption for these modes is measured at the nominal recommended V<sub>DD</sub> (see Table 4) and 105 °C in the mode described. This parameter is not 100% tested but is periodically sampled.

# 5.2 AC Electrical Characteristics

This section provides the AC electrical characteristics for the MPC7448. After fabrication, functional parts are sorted by maximum processor core frequency as shown in Section 5.2.1, "Clock AC Specifications," and tested for conformance to the AC specifications for that frequency. The processor core frequency, determined by the bus (SYSCLK) frequency and the settings of the PLL\_CFG[0:5] signals, can be dynamically modified using dynamic frequency switching (DFS). Parts are sold by maximum processor core frequency; see Section 11, "Part Numbering and Marking," for information on ordering parts. DFS is described in Section 9.7.5, "Dynamic Frequency Switching (DFS)."

## 5.2.1 Clock AC Specifications

Table 8 provides the clock AC timing specifications as defined in Figure 3 and represents the tested operating frequencies of the devices. The maximum system bus frequency, f<sub>SYSCLK</sub>, given in Table 8, is considered a practical maximum in a typical single-processor system. This does not exclude multi-processor systems, but these typically require considerably more design effort to achieve the maximum rated bus frequency. The actual maximum SYSCLK frequency for any application of the MPC7448 will be a function of the AC timings of the microprocessor(s), the AC timings for the system controller, bus loading, circuit board topology, trace lengths, and so forth, and may be less than the value given in Table 8.

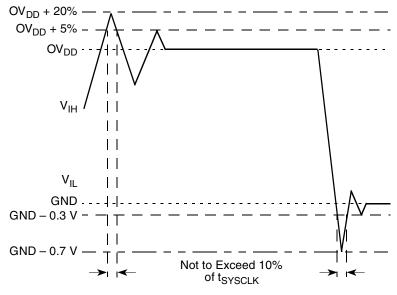

## 5.2.3 IEEE Std. 1149.1 AC Timing Specifications

Table 10 provides the IEEE Std. 1149.1 (JTAG) AC timing specifications as defined in Figure 8 through Figure 11.

Table 10. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions. See Table 4.

| Parameter                                                  | Symbol                                 | Min      | Max      | Unit | Notes |

|------------------------------------------------------------|----------------------------------------|----------|----------|------|-------|

| TCK frequency of operation                                 | f <sub>TCLK</sub>                      | 0        | 33.3     | MHz  |       |

| TCK cycle time                                             | t <sub>TCLK</sub>                      | 30       | —        | ns   |       |

| TCK clock pulse width measured at 1.4 V                    | t <sub>JHJL</sub>                      | 15       | —        | ns   |       |

| TCK rise and fall times                                    | $t_{JR}$ and $t_{JF}$                  | _        | 2        | ns   |       |

| TRST assert time                                           | t <sub>TRST</sub>                      | 25       | —        | ns   | 2     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI       | t <sub>DVJH</sub><br>tı∨JH             | 4<br>0   |          | ns   | 3     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI        | t <sub>DXJH</sub><br>tIXJH             | 20<br>25 |          | ns   | 3     |

| Valid times:<br>Boundary-scan data<br>TDO                  | t <sub>JLDV</sub><br>t <sub>JLOV</sub> | 4<br>4   | 20<br>25 | ns   | 4     |

| Output hold times:<br>Boundary-scan data<br>TDO            | t <sub>JLDX</sub><br>t <sub>JLOX</sub> | 30<br>30 |          | ns   | 4     |

| TCK to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>JLDZ</sub><br>t <sub>JLOZ</sub> | 3<br>3   | 19<br>9  | ns   | 4, 5  |

Notes:

All outputs are measured from the midpoint voltage of the falling/rising edge of TCLK to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 7). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. TRST is an asynchronous level sensitive signal. The time is for test purposes only.

3. Non-JTAG signal input timing with respect to TCK.

4. Non-JTAG signal output timing with respect to TCK.

5. Guaranteed by design and characterization.

Figure 11 provides the test access port timing diagram.

Figure 11. Test Access Port Timing Diagram

## 5.3 Voltage and Frequency Derating

Voltage and frequency derating is no longer supported for part numbers described by this document beginning with datecode 0613. (See Section 11, "Part Numbering and Marking," for information on date code markings.) It is supported by some MPC7448 part numbers which target low-power applications; see Section 11.2, "Part Numbers Not Fully Addressed by This Document" and the referenced MPC7448 Hardware Specification Addenda for more information on these low-power devices. For those devices which previously supported this feature, information has been archived in the *Chip Errata for the MPC7448* (document order no. MPC7448CE).

**Pin Assignments**

# 6 Pin Assignments

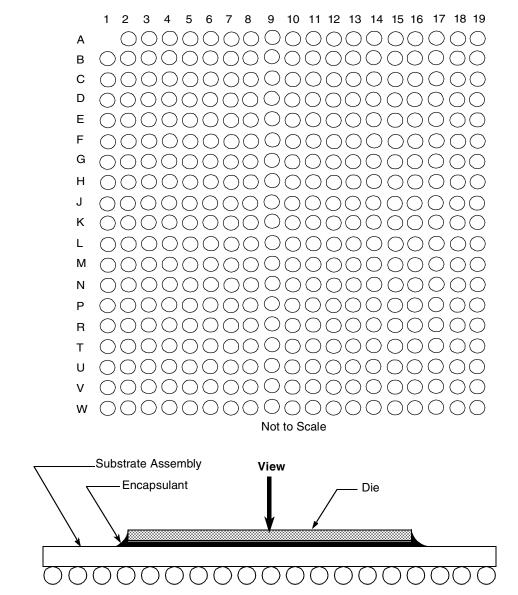

Figure 12 (in Part A) shows the pinout of the MPC7448, 360 high coefficient of thermal expansion ceramic ball grid array (HCTE) package as viewed from the top surface. Part B shows the side profile of the HCTE package to indicate the direction of the top surface view.

Part B

# 7 Pinout Listings

Table 11 provides the pinout listing for the MPC7448, 360 HCTE package. The pinouts of the MPC7448 and MPC7447A are compatible, but the requirements regarding the use of the additional power and ground pins have changed. The MPC7448 requires these pins be connected to the appropriate power or ground plane to achieve high core frequencies; see Section 9.3, "Connection Recommendations," for additional information. As a result, these pins should be connected in all new designs.

Additionally, the MPC7448 may be populated on a board designed for a MPC7447 (or MPC7445 or MPC7441), provided the core voltage can be made to match the requirements in Table 4 and all pins defined as 'no connect' for the MPC7447 are unterminated, as required by the *MPC7457 RISC Microprocessor Hardware Specifications*. The MPC7448 uses pins previously marked 'no connect' for the temperature diode pins and for additional power and ground connections. The additional power and ground pins are required to achieve high core frequencies and core frequency will be limited if they are not connected; see Section 9.3, "Connection Recommendations," for additional information. Because these 'no connect' pins in the MPC7447 360 pin package are not driven in functional mode, an MPC7447 can be populated in an MPC7448 board.

#### NOTE

Caution must be exercised when performing boundary scan test operations on a board designed for an MPC7448, but populated with an MPC7447 or earlier device. This is because in the MPC7447 it is possible to drive the latches associated with the former 'no connect' pins in the MPC7447, potentially causing contention on those pins. To prevent this, ensure that these pins are not connected on the board or, if they are connected, ensure that the states of internal MPC7447 latches do not cause these pins to be driven during board testing.

For the MPC7448, pins that were defined as the TEST[0:4] factory test signal group on the MPC7447A and earlier devices have been assigned new functions. For most of these, the termination recommendations for the TEST[0:4] pins of the MPC7447A are compatible with the MPC7448 and will allow correct operation with no performance loss. The exception is BVSEL1 (TEST3 on the MPC7447A and earlier devices), which may require a different termination depending which I/O voltage mode is desired; see Table 3 for more information.

#### NOTE

This pinout is not compatible with the MPC750, MPC7400, or MPC7410 360 BGA package.

| Signal Name      | Pin Number                                                                                                                                                                                            | Active | I/O    | Notes      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|--|

| LVRAM            | B10                                                                                                                                                                                                   | —      | _      | 12, 20, 22 |  |

| NC (no connect)  | A6, A14, A15, B14, B15, C14, C15, C16, C17, C18, C19, D14, D15, D16, D17, D18, D19, E14, E15, F14, F15, G14, G15, H15, H16, J15, J16, J17, J18, J19, K15, K16, K17, K18, K19, L15, L16, L17, L18, L19 | _      |        | 11         |  |

| LSSD_MODE        | E8                                                                                                                                                                                                    | Low    | Input  | 6, 12      |  |

| MCP              | C9                                                                                                                                                                                                    | Low    | Input  |            |  |

| OV <sub>DD</sub> | B4, C2, C12, D5, F2, H3, J5, K2, L5, M3, N6, P2, P8, P11, R4, R13, R16, T6, T9, U2, U12, U16, V4, V7, V10, V14                                                                                        | —      | —      |            |  |

| OVDD_SENSE       | E18, G18                                                                                                                                                                                              | —      | —      | 16         |  |

| PLL_CFG[0:4]     | B8, C8, C7, D7, A7                                                                                                                                                                                    | High   | Input  |            |  |

| PLL_CFG[5]       | D10                                                                                                                                                                                                   | High   | Input  | 9, 20      |  |

| PMON_IN          | D9                                                                                                                                                                                                    | Low    | Input  | 13         |  |

| PMON_OUT         | A9                                                                                                                                                                                                    | Low    | Output |            |  |

| QACK             | G5                                                                                                                                                                                                    | Low    | Input  |            |  |

| QREQ             | P4                                                                                                                                                                                                    | Low    | Output |            |  |

| SHD[0:1]         | E4, H5                                                                                                                                                                                                | Low    | I/O    | 3          |  |

| SMI              | F9                                                                                                                                                                                                    | Low    | Input  |            |  |

| SRESET           | A2                                                                                                                                                                                                    | Low    | Input  |            |  |

| SYSCLK           | A10                                                                                                                                                                                                   | _      | Input  |            |  |

| TA               | К6                                                                                                                                                                                                    | Low    | Input  |            |  |

| TBEN             | E1                                                                                                                                                                                                    | High   | Input  |            |  |

| TBST             | F11                                                                                                                                                                                                   | Low    | Output |            |  |

| ТСК              | C6                                                                                                                                                                                                    | High   | Input  |            |  |

| TDI              | B9                                                                                                                                                                                                    | High   | Input  | 6          |  |

| TDO              | A4                                                                                                                                                                                                    | High   | Output |            |  |

| TEA              | L1                                                                                                                                                                                                    | Low    | Input  |            |  |

| TEMP_ANODE       | N18                                                                                                                                                                                                   | —      | —      | 17         |  |

| TEMP_CATHODE     | N19                                                                                                                                                                                                   | _      | _      | 17         |  |

| TMS              | F1                                                                                                                                                                                                    | High   | Input  | 6          |  |

| TRST             | A5                                                                                                                                                                                                    | Low    | Input  | 6, 14      |  |

| TS               | L4                                                                                                                                                                                                    | Low    | I/O    | 3          |  |

| TSIZ[0:2]        | G6, F7, E7                                                                                                                                                                                            | High   | Output |            |  |

| TT[0:4]          | E5, E6, F6, E9, C5                                                                                                                                                                                    | High   | I/O    |            |  |

| WT               | D3                                                                                                                                                                                                    | Low    | Output |            |  |

| V <sub>DD</sub>  | H8, H10, H12, J7, J9, J11, J13, K8, K10, K12, K14, L7, L9, L11, L13, M8, M10, M12                                                                                                                     | —      |        |            |  |

| V <sub>DD</sub>  | A13, A16, A18, B17, B19, C13, E13, E16, F12, F17, F19, G11, G16, H14, H17, H19, M14, M16, M18, N15, N17, P16, P18                                                                                     | —      | —      | 15         |  |

#### Table 11. Pinout Listing for the MPC7448, 360 HCTE Package (continued)

| Signal Name | Pin Number | Active | I/O | Notes |

|-------------|------------|--------|-----|-------|

| VDD_SENSE   | G13, N12   | _      |     | 18    |

#### Notes:

1.  $OV_{DD}$  supplies power to the processor bus, JTAG, and all control signals, and is configurable. ( $V_{DD}$  supplies power to the processor core, and  $AV_{DD}$  supplies power to the PLL after filtering from  $V_{DD}$ ). To program the I/O voltage, see Table 3. If used, the pull-down resistor should be less than 250  $\Omega$ . Because these settings may change in future products, it is recommended BVSEL[0:1] be configured using resistor options, jumpers, or some other flexible means, with the capability to reconfigure the termination of this signal in the future if necessary. For actual recommended value of  $V_{in}$  or supply voltages see Table 4.

2. Unused address pins must be pulled down to GND and corresponding address parity pins pulled up to OV<sub>DD</sub>.

3. These pins require weak pull-up resistors (for example, 4.7 KΩ) to maintain the control signals in the negated state after they have been actively negated and released by the MPC7448 and other bus masters.

4. This signal selects between MPX bus mode (asserted) and 60x bus mode (negated) and will be sampled at HRESET going high.

5. This signal must be negated during reset, by pull-up resistor to OV<sub>DD</sub> or negation by ¬HRESET (inverse of HRESET), to ensure proper operation.

6. Internal pull up on die.

7. Not used in 60x bus mode.

8. These signals must be pulled down to GND if unused, or if the MPC7448 is in 60x bus mode.

9. These input signals are for factory use only and must be pulled down to GND for normal machine operation.

10. This test signal is recommended to be tied to HRESET; however, other configurations will not adversely affect performance.

11. These signals are for factory use only and must be left unconnected for normal machine operation. Some pins that were NCs on the MPC7447, MPC7445, and MPC7441 have now been defined for other purposes.

- 12. These input signals are for factory use only and must be pulled up to  $OV_{DD}$  for normal machine operation.

- 13. This pin can externally cause a performance monitor event. Counting of the event is enabled through software.

- 14. This signal must be asserted during reset, by pull down to GND or assertion by HRESET, to ensure proper operation.

- 15. These pins were NCs on the MPC7447, MPC7445, and MPC7441. See Section 9.3, "Connection Recommendations," for more information.

- 16. These pins were OV<sub>DD</sub> pins on the MPC7447, MPC7445, and MPC7441. These pins are internally connected to OV<sub>DD</sub> and are intended to allow an external device (such as a power supply) to detect the I/O voltage level present inside the device package. If unused, it is recommended they be connected to test points to facilitate system debug; otherwise, they may be connected directly to OV<sub>DD</sub> or left unconnected.

- 17. These pins provide connectivity to the on-chip temperature diode that can be used to determine the die junction temperature of the processor. These pins may be left unterminated if unused.

- 18. These pins are internally connected to  $V_{DD}$  and are intended to allow an external device (such as a power supply) to detect the processor core voltage level present inside the device package. If unused, it is recommended they be connected to test points to facilitate system debug; otherwise, they may be connected directly to  $V_{DD}$  or left unconnected.

- 19. These pins are internally connected to GND and are intended to allow an external device to detect the processor ground voltage level present inside the device package. If unused, it is recommended they be connected to test points to facilitate system debug; otherwise, they may be connected directly to GND or left unconnected.

- 20. These pins were in the TEST[0:4] factory test pin group on the MPC7447A, MPC7447, MPC7445, and MPC7441. They have been assigned new functions on the MPC7448.

- 21. These pins can be used to enable the supported dynamic frequency switching (DFS) modes via hardware. If both are pulled down, DFS mode is disabled completely and cannot be enabled via software. If unused, they should be pulled up to OV<sub>DD</sub> to allow software control of DFS. See the *MPC7450 RISC Microprocessor Family Reference Manual* for more information.

- 22. This pin is provided to allow operation of the L2 cache at low core voltages and is for factory use only. See the MPC7450 RISC Microprocessor Family Reference Manual for more information.

Package Description

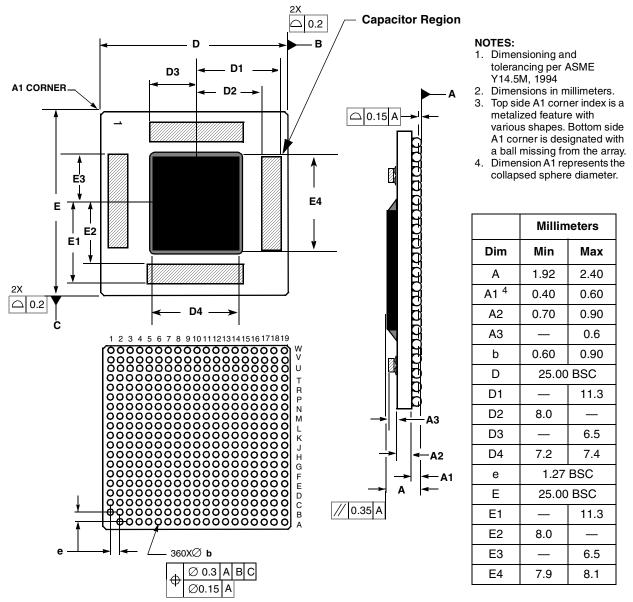

# 8.6 Mechanical Dimensions for the MPC7448, 360 HCTE RoHS-Compliant BGA

Figure 13 provides the mechanical dimensions and bottom surface nomenclature for the MPC7448, 360 HCTE BGA package with RoHS-compliant lead-free spheres.

Figure 15. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC7448, 360 HCTE RoHS-Compliant BGA Package

# 9 System Design Information

This section provides system and thermal design requirements and recommendations for successful application of the MPC7448.

# 9.1 Clocks

The following sections provide more detailed information regarding the clocking of the MPC7448.

## 9.1.1 PLL Configuration

The MPC7448 PLL is configured by the PLL\_CFG[0:5] signals. For a given SYSCLK (bus) frequency, the PLL configuration signals set the internal CPU and VCO frequency of operation. The PLL configuration for the MPC7448 is shown in Table 12. In this example, shaded cells represent settings that, for a given SYSCLK frequency, result in core and/or VCO frequencies that do not comply with Table 8. When enabled, dynamic frequency switching (DFS) also affects the core frequency by halving or quartering the bus-to-core multiplier; see Section 9.7.5, "Dynamic Frequency Switching (DFS)," for more information. Note that when DFS is enabled the resulting core frequency must meet the adjusted minimum core frequency requirements ( $f_{core_DFS}$ ) described in Table 8. Note that the PLL\_CFG[5] is currently used for factory test only and should be tied low, and that the MPC7448 PLL configuration settings are compatible with the MPC7447A PLL configuration settings when PLL\_CFG[5] = 0.

|              |                         |                         | Examp                  | ole Core  | and VCC     | ) Freque  | ncy in M  | Hz         |            |            |            |

|--------------|-------------------------|-------------------------|------------------------|-----------|-------------|-----------|-----------|------------|------------|------------|------------|

| PLL_CFG[0:5] | Bus-to-Core             | Core-to-VCO             | Bus (SYSCLK) Frequency |           |             |           |           |            |            |            |            |

|              | Multiplier <sup>5</sup> | Multiplier <sup>5</sup> | 33.3<br>MHz            | 50<br>MHz | 66.6<br>MHz | 75<br>MHz | 83<br>MHz | 100<br>MHz | 133<br>MHz | 167<br>MHz | 200<br>MHz |

| 010000       | 2x <sup>6</sup>         | 1x                      |                        |           |             |           |           |            |            |            |            |

| 100000       | 3x <sup>6</sup>         | 1x                      |                        |           |             |           |           |            |            |            | 600        |

| 101000       | 4x <sup>6</sup>         | 1x                      |                        |           |             |           |           |            |            | 667        | 800        |

| 101100       | 5x                      | 1x                      |                        |           |             |           |           |            | 667        | 835        | 1000       |

| 100100       | 5.5x                    | 1x                      |                        |           |             |           |           |            | 733        | 919        | 1100       |

| 110100       | 6x                      | 1x                      |                        |           |             |           |           | 600        | 800        | 1002       | 1200       |

| 010100       | 6.5x                    | 1x                      |                        |           |             |           |           | 650        | 866        | 1086       | 1300       |

| 001000       | 7x                      | 1x                      |                        |           |             |           |           | 700        | 931        | 1169       | 1400       |

| 000100       | 7.5x                    | 1x                      |                        |           |             |           | 623       | 750        | 1000       | 1253       | 1500       |

| 110000       | 8x                      | 1x                      |                        |           |             | 600       | 664       | 800        | 1064       | 1336       | 1600       |

| 011000       | 8.5x                    | 1x                      |                        |           |             | 638       | 706       | 850        | 1131       | 1417       | 1700       |

| 011110       | 9x                      | 1x                      |                        |           | 600         | 675       | 747       | 900        | 1197       | 1500       |            |

| 011100       | 9.5x                    | 1x                      |                        |           | 633         | 712       | 789       | 950        | 1264       | 1583       |            |

| 101010       | 10x                     | 1x                      |                        |           | 667         | 750       | 830       | 1000       | 1333       | 1667       |            |

| 100010       | 10.5x                   | 1x                      |                        |           | 700         | 938       | 872       | 1050       | 1397       |            |            |

Table 12. MPC7448 Microprocessor PLL Configuration Example

| MPC7448 RISC Microprocesso | r Hardware Specifications, | Rev. 4 |

|----------------------------|----------------------------|--------|

|----------------------------|----------------------------|--------|

#### System Design Information

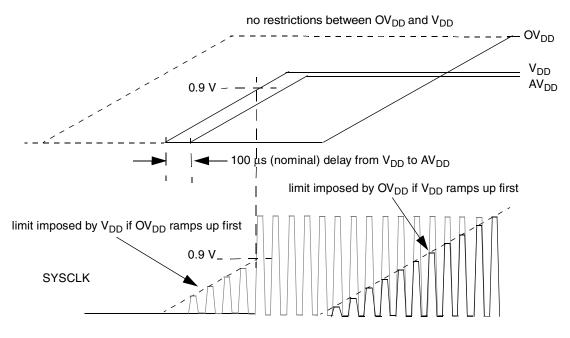

These requirements are shown graphically in Figure 16.

Figure 16. MPC7448 Power Up Sequencing Requirements

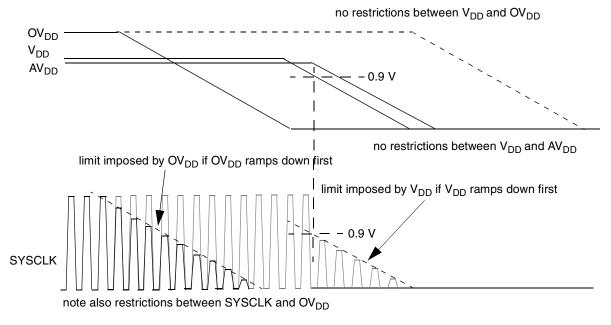

Certain stipulations also apply to the manner in which the power rails of the MPC7448 power down, as follows:

- OV<sub>DD</sub> may ramp down any time before or after V<sub>DD</sub>.

- The voltage at the SYSCLK input must not exceed V<sub>DD</sub> once V<sub>DD</sub> has ramped down below 0.9 V.

- The voltage at the SYSCLK input must not exceed OV<sub>DD</sub> by more 20% during transients (see overshoot/undershoot specifications in Figure 2) or 0.3 V DC (see Table 2) at any time.

Figure 17. MPC7448 Power Down Sequencing Requirements

There is no requirement regarding  $AV_{DD}$  during power down, but it is recommended that  $AV_{DD}$  track  $V_{DD}$  within the RC time constant of the PLL filter circuit described in Section 9.2.2, "PLL Power Supply Filtering" (nominally 100  $\mu$ s).

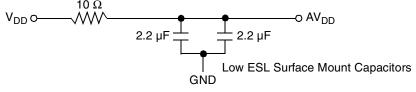

## 9.2.2 PLL Power Supply Filtering

The AV<sub>DD</sub> power signal is provided on the MPC7448 to provide power to the clock generation PLL. To ensure stability of the internal clock, the power supplied to the AV<sub>DD</sub> input signal should be filtered of any noise in the 500-KHz to 10-MHz resonant frequency range of the PLL. The circuit shown in Figure 18 using surface mount capacitors with minimum effective series inductance (ESL) is strongly recommended. In addition to filtering noise from the AV<sub>DD</sub> input, it also provides the required delay between V<sub>DD</sub> and AV<sub>DD</sub> as described in Section 9.2.1, "Power Supply Sequencing."

The circuit should be placed as close as possible to the  $AV_{DD}$  pin to minimize noise coupled from nearby circuits. It is often possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the device footprint.

Figure 18. PLL Power Supply Filter Circuit

System Design Information

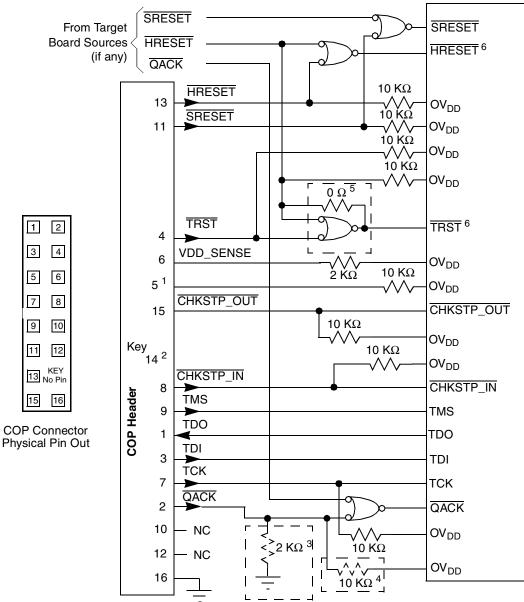

#### Notes:

- 1. RUN/STOP, normally found on pin 5 of the COP header, is not implemented on the MPC7448. Connect pin 5 of the COP header to  $OV_{DD}$  with a 10-K $\Omega$  pull-up resistor.

- 2. Key location; pin 14 is not physically present on the COP header.

- 3. Component not populated. Populate only if debug tool does not drive QACK.

- 4. Populate only if debug tool uses an open-drain type output and does not actively negate QACK.

- 5. If the JTAG interface is implemented, connect  $\overline{\text{HRESET}}$  from the target source to  $\overline{\text{TRST}}$  from the COP header though an AND gate to  $\overline{\text{TRST}}$  of the part. If the JTAG interface is not implemented, connect  $\overline{\text{HRESET}}$  from the target source to  $\overline{\text{TRST}}$  of the part through a 0- $\Omega$  isolation resistor.

- 6. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown above.

#### Figure 21. JTAG Interface Connection

Due to the complexity and variety of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection, and conduction) may vary widely. For these reasons, we recommend using conjugate heat transfer models for the board as well as system-level designs.

For system thermal modeling, the MPC7448 thermal model is shown in Figure 26. Four volumes represent this device. Two of the volumes, solder ball-air and substrate, are modeled using the package outline size of the package. The other two, die and bump-underfill, have the same size as the die. The silicon die should be modeled  $8.0 \times 7.3 \times 0.86 \text{ mm}^3$  with the heat source applied as a uniform source at the bottom of the volume. The bump and underfill layer is modeled as  $8.0 \times 7.3 \times 0.07 \text{ mm}^3$  collapsed in the z-direction with a thermal conductivity of  $5.0 \text{ W/(m} \cdot \text{K})$  in the z-direction. The substrate volume is  $25 \times 25 \times 1.14 \text{ mm}^3$  and has 9.9 W/(m  $\cdot$  K) isotropic conductivity in the xy-plane and 2.95 W/(m  $\cdot$  K) in the direction of the z-axis. The solder ball and air layer are modeled with the same horizontal dimensions as the substrate and is 0.8 mm thick. For the LGA package the solder and air layer is 0.1 mm thick, but the material properties are the same. It can also be modeled as a collapsed volume using orthotropic material properties: 0.034 W/(m  $\cdot$  K) in the xy-plane direction and 11.2 W/(m  $\cdot$  K) in the direction of the z-axis.

| Conductivity   | Value                                         | Unit               |     |           |                              |  |

|----------------|-----------------------------------------------|--------------------|-----|-----------|------------------------------|--|

| Die (8         | $0 \times 7.3 \times 0.86 \text{ mm}^3$ )     |                    | 1 1 | l l       | Die                          |  |

| (              |                                               |                    | z   |           | Bump and Underfill           |  |

| Silicon        | Temperature-<br>dependent                     | W/(m • K)          |     | Substrate |                              |  |

| Bump and Un    | derfill (8.0 × 7.3 × 0.07                     | 'mm <sup>3</sup> ) | -   |           | Solder and Air               |  |

| Builtp and On  |                                               | ······ )           | -   | Side      | View of Model (Not to Scale) |  |

| kz             | 5.0                                           | W/(m ∙ K)          |     |           |                              |  |

| Substrat       | e (25 $	imes$ 25 $	imes$ 1.14 mm <sup>3</sup> | )                  |     | X         | <b>→</b>                     |  |

| k <sub>x</sub> | 9.9                                           | W/(m • K)          |     |           |                              |  |

| k <sub>y</sub> | 9.9                                           |                    |     | Substrate |                              |  |

| k <sub>z</sub> | 2.95                                          |                    |     |           |                              |  |

| Solder Ball a  | nd Air (25 $	imes$ 25 $	imes$ 0.8 r           | nm <sup>3</sup> )  |     |           | Die                          |  |

| k <sub>x</sub> | 0.034                                         | W/(m • K)          |     |           |                              |  |

| k <sub>y</sub> | 0.034                                         | ]                  |     |           |                              |  |

| k <sub>z</sub> | 11.2                                          |                    | у   |           |                              |  |

|                |                                               | •                  |     |           |                              |  |

Top View of Model (Not to Scale)

Figure 26. Recommended Thermal Model of MPC7448

System Design Information

# 9.7.4 Temperature Diode

The MPC7448 has a temperature diode on the microprocessor that can be used in conjunction with other system temperature monitoring devices (such as Analog Devices, ADT7461<sup>TM</sup>). These devices use the negative temperature coefficient of a diode operated at a constant current to determine the temperature of the microprocessor and its environment. For proper operation, the monitoring device used should auto-calibrate the device by canceling out the V<sub>BE</sub> variation of each MPC7448's internal diode.

The following are the specifications of the MPC7448 on-board temperature diode:

$V_{f} > 0.40 V$

$V_{f} < 0.90 V$

Operating range 2–300 µA

Diode leakage  $< 10 \text{ nA} @ 125^{\circ}\text{C}$

Ideality factor over 5–150  $\mu A$  at 60°C:  $n=1.0275\pm0.9\%$

Ideality factor is defined as the deviation from the ideal diode equation:

$$I_{fw} = I_s e^{\frac{qV_f}{nKT}} - 1$$

Another useful equation is:

$$\mathbf{V}_{\mathrm{H}} - \mathbf{V}_{\mathrm{L}} = \mathbf{n} \frac{\mathrm{KT}}{\mathrm{q}} \left[ \mathbf{I} \mathbf{n} \frac{\mathrm{I}_{\mathrm{H}}}{\mathrm{I}_{\mathrm{L}}} \right] - \mathbf{1}$$

Where:

$I_{fw} = Forward current$

$I_s = Saturation current$

$V_d = Voltage at diode$

$V_f = Voltage forward biased$

$V_H = Diode \text{ voltage while } I_H \text{ is flowing}$

$V_L$  = Diode voltage while  $I_L$  is flowing

$I_{H} = Larger diode bias current$

$I_L =$ Smaller diode bias current

q = Charge of electron (1.6 x  $10^{-19}$  C)

$$n =$$

Ideality factor (normally 1.0)

K = Boltzman's constant (1.38 x

$$10^{-23}$$

Joules/K)

The ratio of  $I_H$  to  $I_L$  is usually selected to be 10:1. The previous equation simplifies to the following:

$$V_{H} - V_{L} = 1.986 \times 10^{-4} \times nT$$

**Document Revision History**

| Revision | Date | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                 |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        |      | Table 6: Added separate input leakage specification for BVSEL0, LSSD_MODE, TCK, TDI, TMS, TRST signals to correctly indicate leakage current for signals with internal pull-up resistors.                                                                                                                                                             |

|          |      | Section 5.1: Added paragraph preceding Table 7 and edited notes in Table 7 to clarify core frequencies at which power consumption is measured.                                                                                                                                                                                                        |

|          |      | Section 5.3: Removed voltage derating specifications; this feature has been made redundant by new device offerings and is no longer supported.                                                                                                                                                                                                        |

|          |      | Changed names of "Typical–Nominal" and "Typical–Thermal" power consumption parameters to "Typical" and "Thermal", respectively. (Name change only–no specifications were changed.)                                                                                                                                                                    |

|          |      | Table 11: Revised Notes 16, 18, and 19 to reflect current recommendations for connection of SENSE pins. Section 9.3: Added paragraph explaining connection recommendations for SENSE pins. (See also Table 11 entry above.)                                                                                                                           |

|          |      | Table 19: Updated table to reflect changes in specifications for MC7448xxnnnnNC devices.Table 9: Changed all instances of TT[0:3] to TT[0:4]                                                                                                                                                                                                          |

|          |      | Removed mention of these input signals from output valid times and output hold times:<br>• AACK, CKSTP_IN, DT[0:3]                                                                                                                                                                                                                                    |

|          |      | Figure 17: Modified diagram slightly to correctly show constraint on SYSCLK ramping is related to $V_{DD}$ voltage, not AV <sub>DD</sub> voltage. (Diagram clarification only; no change in power sequencing requirements.)<br>Added Table 20 to reflect introduction of extended temperature devices and associated hardware specification addendum. |

| 1        |      | Added 1600 MHz, 1420 MHz, and 1000 MHz devices                                                                                                                                                                                                                                                                                                        |

|          |      | Section 4: corrected die size                                                                                                                                                                                                                                                                                                                         |

|          |      | Table 2: Revised Note 4 to consider overshoot/undershoot and combined with Note 5.                                                                                                                                                                                                                                                                    |

|          |      | Table 4: Revised operating voltage for 1700 MHz device from $\pm$ 50 mV to +20 mV / –50 mV.                                                                                                                                                                                                                                                           |

|          |      | Table 7: Updated and expanded table to include Typical – Nominal power consumption.<br>Table 11: Added voltage derating information for 1700 MHz devices; this feature is not supported at this time for other speed grades.                                                                                                                          |

|          |      | Added transient specifications for VDD power supply in Section 9.2.3, added Table 15 and Figure 19 and renumbered subsequent tables and figures.                                                                                                                                                                                                      |

|          |      | Moved Decoupling Recommendations from Section 9.4 to Section 9.2.4 and renumbered subsequent sections.                                                                                                                                                                                                                                                |

|          |      | Section 9.2.1: Revised power sequencing requirements.                                                                                                                                                                                                                                                                                                 |

|          |      | Section 9.7.4: Added thermal diode ideality factor information (previously TBD).                                                                                                                                                                                                                                                                      |

|          |      | Table 17: Expanded table to show HID1 register values when DFS modes are enabled.                                                                                                                                                                                                                                                                     |

|          |      | Section 11.2: updated to include additional N-spec device speed grades                                                                                                                                                                                                                                                                                |

|          |      | Tables 18 and 19: corrected PVR values and added "MC" product code prefix                                                                                                                                                                                                                                                                             |

| 0        |      | Initial public release.                                                                                                                                                                                                                                                                                                                               |

#### Table 17. Document Revision History (continued)

# **11 Part Numbering and Marking**

Ordering information for the part numbers fully covered by this specification document is provided in Section 11.1, "Part Numbers Fully Addressed by This Document." Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact a local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier that may specify special application conditions. An optional specification modifier may also apply for parts to indicate a specific change in specifications, such as support for an extended temperature range. Finally, each part number contains a revision level code that refers to the die mask revision number. Section 11.2, "Part Numbers Not Fully Addressed by This Document," lists the part numbers that do not fully conform to the specifications of this document. These special part numbers require an additional document called a hardware specification addendum.

# 11.1 Part Numbers Fully Addressed by This Document

Table 18 provides the Freescale part numbering nomenclature for the MPC7448 part numbers fully addressed by this document. For information regarding other MPC7448 part numbers, see Section 11.2, "Part Numbers Not Fully Addressed by This Document."

| XX                     | 7448               | XX                                              | nnnn                   | L                                  | x                                                      |

|------------------------|--------------------|-------------------------------------------------|------------------------|------------------------------------|--------------------------------------------------------|

| Product<br>Code        | Part<br>Identifier | Package                                         | Processor<br>Frequency | Application<br>Modifier            | Revision Level                                         |

| MC<br>PPC <sup>1</sup> | 7448               | HX = HCTE BGA<br>VS = RoHS LGA<br>VU = RoHS BGA | 1700                   | L: 1.3 V +20/–50 mV<br>0 to 105 °C | C: 2.1; PVR = 0x8004_0201<br>D: 2.2; PVR = 0x8004_0202 |

|                        |                    |                                                 | 1600                   | L: 1.25 V ± 50 mV<br>0 to 105 °C   |                                                        |

|                        |                    |                                                 | 1420                   | L: 1.2 V ± 50 mV<br>0 to 105 °C    |                                                        |

|                        |                    |                                                 | 1000                   | L: 1.15 V ± 50 mV<br>0 to 105 °C   |                                                        |

#### Table 18. Part Numbering Nomenclature

#### Notes:

1. The P prefix in a Freescale part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur as pilot production prototypes are shipped.