#### Welcome to E-XFL.COM

### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC G4                                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.42GHz                                                                |

| Co-Processors/DSP               | Multimedia; SIMD                                                       |

| RAM Controllers                 | -                                                                      |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | -                                                                      |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.5V, 1.8V, 2.5V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 360-CBGA, FCCBGA                                                       |

| Supplier Device Package         | 360-FCCBGA (25x25)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc7448vu1420lc |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

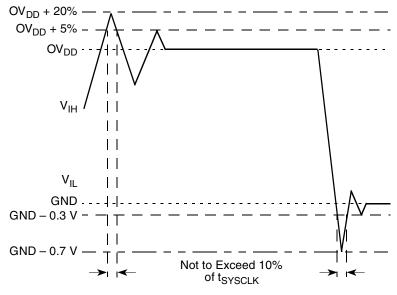

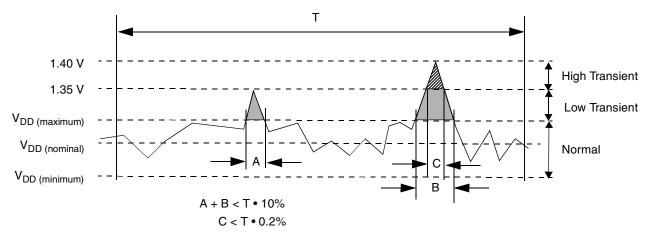

Figure 2 shows the undershoot and overshoot voltage on the MPC7448.

Figure 2. Overshoot/Undershoot Voltage

The MPC7448 provides several I/O voltages to support both compatibility with existing systems and migration to future systems. The MPC7448 core voltage must always be provided at the nominal voltage (see Table 4). The input voltage threshold for each bus is selected by sampling the state of the voltage select pins at the negation of the signal HRESET. The output voltage will swing from GND to the maximum voltage applied to the  $OV_{DD}$  power pins. Table 3 provides the input threshold voltage settings. Because these settings may change in future products, it is recommended that BVSEL[0:1] be configured using resistor options, jumpers, or some other flexible means, with the capability to reconfigure the termination of this signal in the future, if necessary.

| BVSEL0 | BVSEL1 | I/O Voltage Mode <sup>1</sup> | Notes |

|--------|--------|-------------------------------|-------|

| 0      | 0      | 1.8 V                         | 2, 3  |

| 0      | 1      | 2.5 V                         | 2, 4  |

| 1      | 0      | 1.5 V                         | 2     |

| 1      | 1      | 2.5 V                         | 4     |

Table 3. Input Threshold Voltage Setting

Notes:

- 1. **Caution:** The I/O voltage mode selected must agree with the OV<sub>DD</sub> voltages supplied. See Table 4.

- 2. If used, pull-down resistors should be less than 250  $\Omega.$

- 3. The pin configuration used to select 1.8V mode on the MPC7448 is not compatible with the pin configuration used to select 1.8V mode on the MPC7447A and earlier devices.

- 4. The pin configuration used to select 2.5V mode on the MPC7448 is fully compatible with the pin configuration used to select 2.5V mode on the MPC7447A and earlier devices.

when running a typical benchmark at temperatures in a typical system. The Full-Power Mode–Thermal value is intended to represent the sustained power consumption of the device when running a typical code sequence at high temperature and is recommended to be used as the basis for designing a thermal solution; see Section 9.7, "Power and Thermal Management Information" for more information on thermal solutions. The Full-Power Mode–Maximum value is recommended to be used for power supply design because this represents the maximum peak power draw of the device that a power supply must be capable of sourcing without voltage droop. For information on power consumption when dynamic frequency switching is enabled, see Section 9.7.5, "Dynamic Frequency Switching (DFS)."

|         | Die Junction                       | Maximum Processor Core Frequency (Speed Grade, MHz) |              |          |          |      | Neter |

|---------|------------------------------------|-----------------------------------------------------|--------------|----------|----------|------|-------|

|         | Temperature -<br>(T <sub>j</sub> ) | 1000 MHz                                            | 1420 MHz     | 1600 MHz | 1700 MHz | Unit | Notes |

|         |                                    |                                                     | Full-Power M | lode     |          |      |       |

| Typical | 65 <b>•C</b>                       | 15.0                                                | 19.0         | 20.0     | 21.0     | W    | 1, 2  |

| Thermal | 105 <b>•</b> C                     | 18.6                                                | 23.3         | 24.4     | 25.6     | W    | 1, 5  |

| Maximum | 105 <b>•</b> C                     | 21.6                                                | 27.1         | 28.4     | 29.8     | W    | 1, 3  |

|         |                                    |                                                     | Nap Mode     | e        |          |      |       |

| Typical | 105 <b>•</b> C                     | 11.1                                                | 11.8         | 13.0     | 13.0     | W    | 1,6   |

|         |                                    |                                                     | Sleep Mod    | le       |          |      |       |

| Typical | 105 <b>•C</b>                      | 10.8                                                | 11.4         | 12.5     | 12.5     | W    | 1, 6  |

|         | Deep Sleep Mode (PLL Disabled)     |                                                     |              |          |          |      |       |

| Typical | 105 <b>•</b> C                     | 10.4                                                | 11.0         | 12.0     | 12.0     | W    | 1, 6  |

### Table 7. Power Consumption for MPC7448 at Maximum Rated Frequency

Notes:

- These values specify the power consumption for the core power supply (V<sub>DD</sub>) at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include I/O supply power (OV<sub>DD</sub>) or PLL supply power (AV<sub>DD</sub>). OV<sub>DD</sub> power is system dependent but is typically < 5% of V<sub>DD</sub> power. Worst case power consumption for AV<sub>DD</sub> < 13 mW. Freescale also offers MPC7448 part numbers that meet lower power consumption specifications; for more information on these devices, see Section 11.2, "Part Numbers Not Fully Addressed by This Document."

- 2. Typical power consumption is an average value measured with the processor operating at its rated maximum processor core frequency (except for Deep Sleep Mode), at nominal recommended V<sub>DD</sub> (see Table 4) and 65°C while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz. This parameter is not 100% tested but periodically sampled.b

- 3. Maximum power consumption is the average measured with the processor operating at its rated maximum processor core frequency, at nominal V<sub>DD</sub> and maximum operating junction temperature (see Table 4) while running an entirely cache-resident, contrived sequence of instructions to keep all the execution units maximally busy.

- 4. Doze mode is not a user-definable state; it is an intermediate state between full-power and either nap or sleep mode. As a result, power consumption for this mode is not tested.

- Thermal power consumption is an average value measured at the nominal recommended V<sub>DD</sub> (see Table 4) and 105 °C while running the Dhrystone 2.1 benchmark and achieving 2.3 Dhrystone MIPs/MHz. This parameter is not 100% tested but periodically sampled.

- 6. Typical power consumption for these modes is measured at the nominal recommended V<sub>DD</sub> (see Table 4) and 105 °C in the mode described. This parameter is not 100% tested but is periodically sampled.

### Table 8. Clock AC Timing Specifications

At recommended operating conditions. See Table 4.

|                                  | Maximum Processor Core Frequency (Speed Grade) |                                            |          |      |          |      |          |      |          |      |      |         |

|----------------------------------|------------------------------------------------|--------------------------------------------|----------|------|----------|------|----------|------|----------|------|------|---------|

| Characteristic                   |                                                | Symbol                                     | 1000 MHz |      | 1420 MHz |      | 1600 MHz |      | 1700 MHz |      | Unit | Notes   |

|                                  |                                                |                                            | Min      | Max  | Min      | Max  | Min      | Max  | Min      | Мах  |      |         |

| Processor                        | DFS mode disabled                              | f <sub>core</sub>                          | 600      | 1000 | 600      | 1420 | 600      | 1600 | 600      | 1700 | MHz  | 1, 8    |

| core<br>frequency                | DFS mode enabled                               | f <sub>core_DF</sub>                       | 300      | 500  | 300      | 710  | 300      | 800  | 300      | 850  |      | 9       |

| VCO freque                       | ency                                           | f <sub>VCO</sub>                           | 600      | 1000 | 600      | 1420 | 600      | 800  | 600      | 1700 | MHz  | 1, 10   |

| SYSCLK fre                       | equency                                        | f <sub>SYSCLK</sub>                        | 33       | 200  | 33       | 200  | 33       | 200  | 33       | 200  | MHz  | 1, 2, 8 |

| SYSCLK cy                        | cle time                                       | t <sub>SYSCLK</sub>                        | 5.0      | 30   | 5.0      | 30   | 5.0      | 30   | 5.0      | 30   | ns   | 2       |

| SYSCLK ris                       | se and fall time                               | t <sub>KR</sub> , t <sub>KF</sub>          | —        | 0.5  | _        | 0.5  | -        | 0.5  |          | 0.5  | ns   | 3       |

| SYSCLK du<br>OV <sub>DD</sub> /2 | ity cycle measured at                          | t <sub>KHKL</sub> /<br>t <sub>SYSCLK</sub> | 40       | 60   | 40       | 60   | 40       | 60   | 40       | 60   | %    | 4       |

| SYSCLK cy                        | cle-to-cycle jitter                            |                                            | —        | 150  | _        | 150  |          | 150  | —        | 150  | ps   | 5, 6    |

| Internal PLL                     | _ relock time                                  |                                            | —        | 100  | _        | 100  | _        | 100  | _        | 100  | μs   | 7       |

### Notes:

- 1. **Caution**: The SYSCLK frequency and PLL\_CFG[0:5] settings must be chosen such that the resulting SYSCLK (bus) frequency, processor core frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:5] signal description in Section 9.1.1, "PLL Configuration," for valid PLL\_CFG[0:5] settings.

- 2. Actual maximum system bus frequency is system-dependent. See Section 5.2.1, "Clock AC Specifications."

- 3. Rise and fall times for the SYSCLK input measured from 0.4 to 1.4 V

- 4. Timing is guaranteed by design and characterization.

- 5. Guaranteed by design

- 6. The SYSCLK driver's closed loop jitter bandwidth should be less than 1.5 MHz at -3 dB.

- 7. Relock timing is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

- 8. This reflects the maximum and minimum core frequencies when the dynamic frequency switching feature (DFS) is disabled. f<sub>core DFS</sub> provides the maximum and minimum core frequencies when operating in a DFS mode.

- 9. This specification supports the Dynamic Frequency Switching (DFS) feature and is applicable only when one of the DFS modes (divide-by-2 or divide-by-4) is enabled. When DFS is disabled, the core frequency must conform to the maximum and minimum frequencies stated for f<sub>core</sub>.

- 10.Use of the DFS feature does not affect VCO frequency.

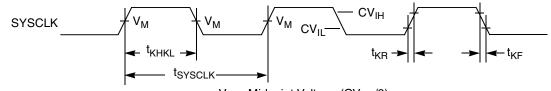

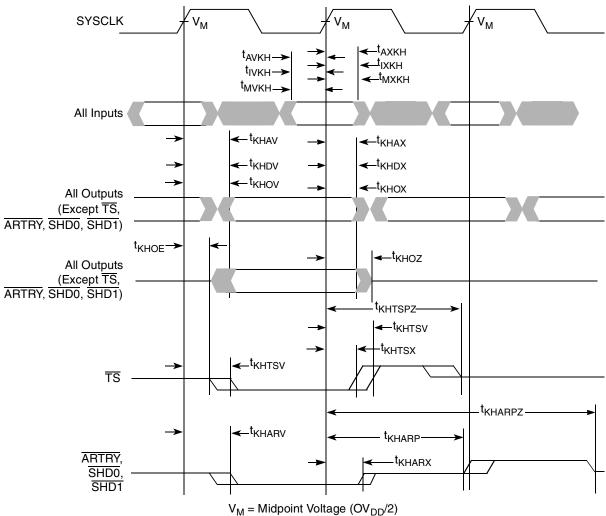

Figure 3 provides the SYSCLK input timing diagram.

$V_{M}$  = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 3. SYSCLK Input Timing Diagram

### 5.2.2 **Processor Bus AC Specifications**

Table 9 provides the processor bus AC timing specifications for the MPC7448 as defined in Figure 4 and Figure 5.

### Table 9. Processor Bus AC Timing Specifications<sup>1</sup>

At recommended operating conditions. See Table 4.

| Parameter                                                                                                                                                                        | Symbol <sup>2</sup>                                         | All Spee          | d Grades          | Unit | Notes     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------|-------------------|------|-----------|

| Farameter                                                                                                                                                                        | Symbol                                                      | Min               | Мах               | Onit | Notes     |

| Input setup times:<br>A[0:35], AP[0:4]<br>D[0:63], DP[0:7]<br>AACK, ARTRY, BG, CKSTP_IN, DBG, DTI[0:3], GBL, TT[0:4],<br>QACK, TA, TBEN, TEA, TS, EXT_QUAL, PMON_IN,<br>SHD[0:1] | t <sub>avkh</sub><br>t <sub>dvkh</sub><br>tivkh             | 1.5<br>1.5<br>1.5 | <br>              | ns   | <br><br>_ |

| BMODE[0:1], BVSEL[0:1]                                                                                                                                                           | t <sub>MVKH</sub>                                           | 1.5               | —                 |      | 8         |

| Input hold times:<br>A[0:35], AP[0:4]<br>D[0:63], DP[0:7]<br>AACK, ARTRY, BG, CKSTP_IN, DBG, DTI[0:3], GBL, TT[0:4],<br>QACK, TA, TBEN, TEA, TS, EXT_QUAL, PMON_IN,<br>SHD[0:1]  | t <sub>АХКН</sub><br>t <sub>DXKH</sub><br>tixkh             | 0<br>0<br>0       |                   | ns   | <br><br>  |

| BMODE[0:1], BVSEL[0:1]                                                                                                                                                           | t <sub>MXKH</sub>                                           | 0                 | —                 |      | 8         |

| Output valid times:<br>A[0:35], AP[0:4]<br>D[0:63], DP[0:7]<br>BR, CI, DRDY, GBL, HIT, PMON_OUT, QREQ, TBST,<br>TSIZ[0:2], TT[0:4], WT                                           | <sup>t</sup> khav<br><sup>t</sup> khdv<br><sup>t</sup> khov |                   | 1.8<br>1.8<br>1.8 | ns   |           |

| TS<br>ARTRY, SHD[0:1]                                                                                                                                                            | <sup>t</sup> KHTSV<br><sup>t</sup> KHARV                    | _                 | 1.8<br>1.8        |      |           |

| Output hold times:<br>A[0:35], AP[0:4]<br>D[0:63], DP[0:7]<br>BR, CI, DRDY, GBL, HIT, PMON_OUT, QREQ, TBST,<br>TSIZ[0:2], TT[0:4], WT                                            | <sup>t</sup> кнах<br><sup>t</sup> кндх<br><sup>t</sup> кнох | 0.5<br>0.5<br>0.5 |                   | ns   |           |

| TS<br>ARTRY, SHD[0:1]                                                                                                                                                            | t <sub>KHTSX</sub><br>t <sub>KHARX</sub>                    | 0.5<br>0.5        | —                 |      |           |

| SYSCLK to output enable                                                                                                                                                          | t <sub>KHOE</sub>                                           | 0.5               | —                 | ns   | 5         |

### MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

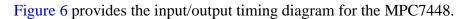

Figure 6. Input/Output Timing Diagram

## 5.2.3 IEEE Std. 1149.1 AC Timing Specifications

Table 10 provides the IEEE Std. 1149.1 (JTAG) AC timing specifications as defined in Figure 8 through Figure 11.

Table 10. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions. See Table 4.

| Parameter                                                  | Symbol                                 | Min      | Max      | Unit | Notes |

|------------------------------------------------------------|----------------------------------------|----------|----------|------|-------|

| TCK frequency of operation                                 | f <sub>TCLK</sub>                      | 0        | 33.3     | MHz  |       |

| TCK cycle time                                             | t <sub>TCLK</sub>                      | 30       | —        | ns   |       |

| TCK clock pulse width measured at 1.4 V                    | t <sub>JHJL</sub>                      | 15       | —        | ns   |       |

| TCK rise and fall times                                    | $t_{JR}$ and $t_{JF}$                  | _        | 2        | ns   |       |

| TRST assert time                                           | t <sub>TRST</sub>                      | 25       | —        | ns   | 2     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI       | t <sub>DVJH</sub><br>tı∨JH             | 4<br>0   |          | ns   | 3     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI        | t <sub>DXJH</sub><br>tIXJH             | 20<br>25 |          | ns   | 3     |

| Valid times:<br>Boundary-scan data<br>TDO                  | t <sub>JLDV</sub><br>t <sub>JLOV</sub> | 4<br>4   | 20<br>25 | ns   | 4     |

| Output hold times:<br>Boundary-scan data<br>TDO            | t <sub>JLDX</sub><br>t <sub>JLOX</sub> | 30<br>30 |          | ns   | 4     |

| TCK to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>JLDZ</sub><br>t <sub>JLOZ</sub> | 3<br>3   | 19<br>9  | ns   | 4, 5  |

Notes:

All outputs are measured from the midpoint voltage of the falling/rising edge of TCLK to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 7). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. TRST is an asynchronous level sensitive signal. The time is for test purposes only.

3. Non-JTAG signal input timing with respect to TCK.

4. Non-JTAG signal output timing with respect to TCK.

5. Guaranteed by design and characterization.

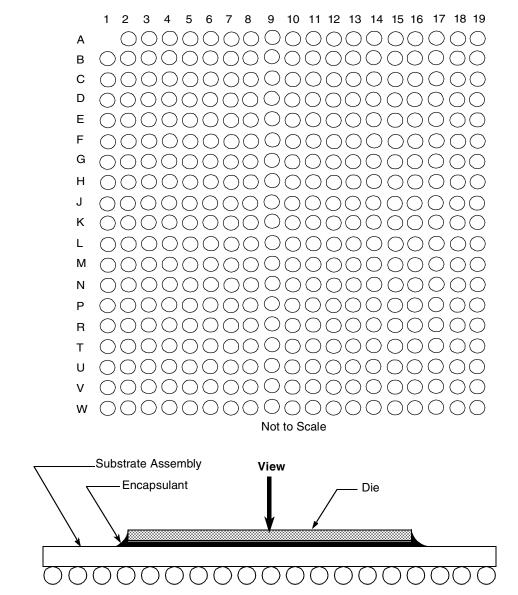

**Pin Assignments**

# 6 Pin Assignments

Figure 12 (in Part A) shows the pinout of the MPC7448, 360 high coefficient of thermal expansion ceramic ball grid array (HCTE) package as viewed from the top surface. Part B shows the side profile of the HCTE package to indicate the direction of the top surface view.

Part B

# 7 Pinout Listings

Table 11 provides the pinout listing for the MPC7448, 360 HCTE package. The pinouts of the MPC7448 and MPC7447A are compatible, but the requirements regarding the use of the additional power and ground pins have changed. The MPC7448 requires these pins be connected to the appropriate power or ground plane to achieve high core frequencies; see Section 9.3, "Connection Recommendations," for additional information. As a result, these pins should be connected in all new designs.

Additionally, the MPC7448 may be populated on a board designed for a MPC7447 (or MPC7445 or MPC7441), provided the core voltage can be made to match the requirements in Table 4 and all pins defined as 'no connect' for the MPC7447 are unterminated, as required by the *MPC7457 RISC Microprocessor Hardware Specifications*. The MPC7448 uses pins previously marked 'no connect' for the temperature diode pins and for additional power and ground connections. The additional power and ground pins are required to achieve high core frequencies and core frequency will be limited if they are not connected; see Section 9.3, "Connection Recommendations," for additional information. Because these 'no connect' pins in the MPC7447 360 pin package are not driven in functional mode, an MPC7447 can be populated in an MPC7448 board.

### NOTE

Caution must be exercised when performing boundary scan test operations on a board designed for an MPC7448, but populated with an MPC7447 or earlier device. This is because in the MPC7447 it is possible to drive the latches associated with the former 'no connect' pins in the MPC7447, potentially causing contention on those pins. To prevent this, ensure that these pins are not connected on the board or, if they are connected, ensure that the states of internal MPC7447 latches do not cause these pins to be driven during board testing.

For the MPC7448, pins that were defined as the TEST[0:4] factory test signal group on the MPC7447A and earlier devices have been assigned new functions. For most of these, the termination recommendations for the TEST[0:4] pins of the MPC7447A are compatible with the MPC7448 and will allow correct operation with no performance loss. The exception is BVSEL1 (TEST3 on the MPC7447A and earlier devices), which may require a different termination depending which I/O voltage mode is desired; see Table 3 for more information.

### NOTE

This pinout is not compatible with the MPC750, MPC7400, or MPC7410 360 BGA package.

| Signal Name      | Pin Number                                                                                                                                                                                            | Active | I/O    | Notes      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|

| LVRAM            | B10                                                                                                                                                                                                   | —      | _      | 12, 20, 22 |

| NC (no connect)  | A6, A14, A15, B14, B15, C14, C15, C16, C17, C18, C19, D14, D15, D16, D17, D18, D19, E14, E15, F14, F15, G14, G15, H15, H16, J15, J16, J17, J18, J19, K15, K16, K17, K18, K19, L15, L16, L17, L18, L19 | _      |        | 11         |

| LSSD_MODE        | E8                                                                                                                                                                                                    | Low    | Input  | 6, 12      |

| MCP              | C9                                                                                                                                                                                                    | Low    | Input  |            |

| OV <sub>DD</sub> | B4, C2, C12, D5, F2, H3, J5, K2, L5, M3, N6, P2, P8, P11, R4, R13, R16, T6, T9, U2, U12, U16, V4, V7, V10, V14                                                                                        | —      | —      |            |

| OVDD_SENSE       | E18, G18                                                                                                                                                                                              | —      | —      | 16         |

| PLL_CFG[0:4]     | B8, C8, C7, D7, A7                                                                                                                                                                                    | High   | Input  |            |

| PLL_CFG[5]       | D10                                                                                                                                                                                                   | High   | Input  | 9, 20      |

| PMON_IN          | D9                                                                                                                                                                                                    | Low    | Input  | 13         |

| PMON_OUT         | A9                                                                                                                                                                                                    | Low    | Output |            |

| QACK             | G5                                                                                                                                                                                                    | Low    | Input  |            |

| QREQ             | P4                                                                                                                                                                                                    | Low    | Output |            |

| SHD[0:1]         | E4, H5                                                                                                                                                                                                | Low    | I/O    | 3          |

| SMI              | F9                                                                                                                                                                                                    | Low    | Input  |            |

| SRESET           | A2                                                                                                                                                                                                    | Low    | Input  |            |

| SYSCLK           | A10                                                                                                                                                                                                   | _      | Input  |            |

| TA               | К6                                                                                                                                                                                                    | Low    | Input  |            |

| TBEN             | E1                                                                                                                                                                                                    | High   | Input  |            |

| TBST             | F11                                                                                                                                                                                                   | Low    | Output |            |

| ТСК              | C6                                                                                                                                                                                                    | High   | Input  |            |

| TDI              | B9                                                                                                                                                                                                    | High   | Input  | 6          |

| TDO              | A4                                                                                                                                                                                                    | High   | Output |            |

| TEA              | L1                                                                                                                                                                                                    | Low    | Input  |            |

| TEMP_ANODE       | N18                                                                                                                                                                                                   | —      | —      | 17         |

| TEMP_CATHODE     | N19                                                                                                                                                                                                   | _      | _      | 17         |

| TMS              | F1                                                                                                                                                                                                    | High   | Input  | 6          |

| TRST             | A5                                                                                                                                                                                                    | Low    | Input  | 6, 14      |

| TS               | L4                                                                                                                                                                                                    | Low    | I/O    | 3          |

| TSIZ[0:2]        | G6, F7, E7                                                                                                                                                                                            | High   | Output |            |

| TT[0:4]          | E5, E6, F6, E9, C5                                                                                                                                                                                    | High   | I/O    |            |

| WT               | D3                                                                                                                                                                                                    | Low    | Output |            |

| V <sub>DD</sub>  | H8, H10, H12, J7, J9, J11, J13, K8, K10, K12, K14, L7, L9, L11, L13, M8, M10, M12                                                                                                                     | —      |        |            |

| V <sub>DD</sub>  | A13, A16, A18, B17, B19, C13, E13, E16, F12, F17, F19, G11, G16, H14, H17, H19, M14, M16, M18, N15, N17, P16, P18                                                                                     | —      | —      | 15         |

### MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

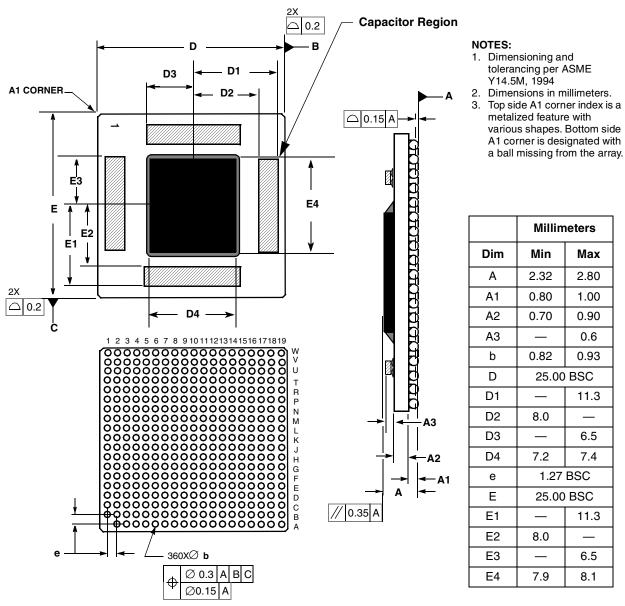

# 8 Package Description

The following sections provide the package parameters and mechanical dimensions for the HCTE package.

## 8.1 Package Parameters for the MPC7448, 360 HCTE BGA

The package parameters are as provided in the following list. The package type is  $25 \times 25$  mm, 360-lead high coefficient of thermal expansion ceramic ball grid array (HCTE).

| Package outline                             | $25 \times 25 \text{ mm}$    |  |  |  |

|---------------------------------------------|------------------------------|--|--|--|

| Interconnects                               | 360 (19 × 19 ball array – 1) |  |  |  |

| Pitch                                       | 1.27 mm (50 mil)             |  |  |  |

| Minimum module height                       | 2.32 mm                      |  |  |  |

| Maximum module height                       | 2.80 mm                      |  |  |  |

| Ball diameter                               | 0.89 mm (35 mil)             |  |  |  |

| Coefficient of thermal expansion12.3 ppm/°C |                              |  |  |  |

Package Description

# 8.2 Mechanical Dimensions for the MPC7448, 360 HCTE BGA

Figure 13 provides the mechanical dimensions and bottom surface nomenclature for the MPC7448, 360 HCTE BGA package.

Figure 13. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC7448, 360 HCTE BGA Package

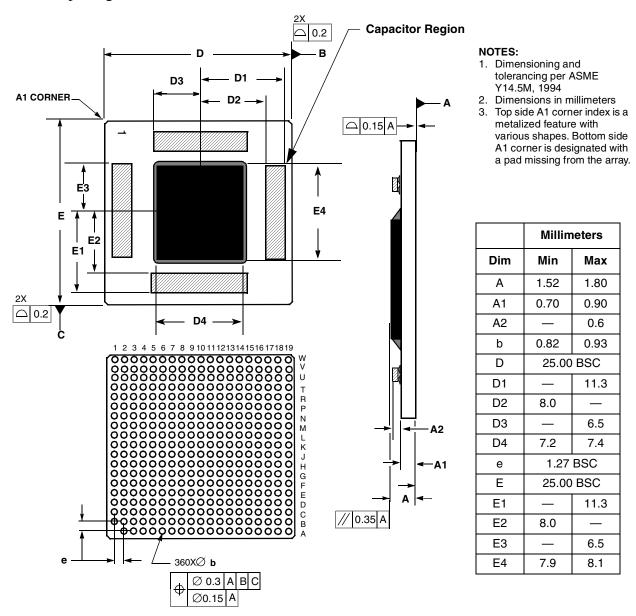

Package Description

# 8.4 Mechanical Dimensions for the MPC7448, 360 HCTE LGA

Figure 13 provides the mechanical dimensions and bottom surface nomenclature for the MPC7448, 360 HCTE LGA package.

Figure 14. Mechanical Dimensions and Bottom Surface Nomenclature for the MPC7448, 360 HCTE LGA Package

## 9.1.2 System Bus Clock (SYSCLK) and Spread Spectrum Sources

Spread spectrum clock sources are an increasingly popular way to control electromagnetic interference emissions (EMI) by spreading the emitted noise to a wider spectrum and reducing the peak noise magnitude in order to meet industry and government requirements. These clock sources intentionally add long-term jitter in order to diffuse the EMI spectral content. The jitter specification given in Table 8 considers short-term (cycle-to-cycle) jitter only and the clock generator's cycle-to-cycle output jitter should meet the MPC7448 input cycle-to-cycle jitter requirement. Frequency modulation and spread are separate concerns, and the MPC7448 is compatible with spread spectrum sources if the recommendations listed in Table 13 are observed.

| Table 13. Spread Spectrum | <b>Clock Source Recommendations</b> |

|---------------------------|-------------------------------------|

|---------------------------|-------------------------------------|

At recommended operating conditions. See Table 4.

| Parameter            | Min | Мах | Unit | Notes |

|----------------------|-----|-----|------|-------|

| Frequency modulation | —   | 50  | kHz  | 1     |

| Frequency spread     | —   | 1.0 | %    | 1, 2  |

Notes:

2. SYSCLK frequencies resulting from frequency spreading, and the resulting core and VCO frequencies, must meet the minimum and maximum specifications given in Table 8.

It is imperative to note that the processor's minimum and maximum SYSCLK, core, and VCO frequencies must not be exceeded regardless of the type of clock source. Therefore, systems in which the processor is operated at its maximum rated core or bus frequency should avoid violating the stated limits by using down-spreading only.

## 9.2 Power Supply Design and Sequencing

The following sections provide detailed information regarding power supply design for the MPC7448.

## 9.2.1 Power Supply Sequencing

The MPC7448 requires its power rails and clock to be applied in a specific sequence to ensure proper device operation and to prevent device damage. The power sequencing requirements are as follows:

- AV<sub>DD</sub> must be delayed with respect to V<sub>DD</sub> by the RC time constant of the PLL filter circuit described in Section 9.2.2, "PLL Power Supply Filtering". This time constant is nominally 100 μs.

- $OV_{DD}$  may ramp anytime before or after  $V_{DD}$  and  $AV_{DD}$ .

Additionally, the following requirements exist regarding the application of SYSCLK:

- The voltage at the SYSCLK input must not exceed  $V_{DD}$  until  $V_{DD}$  has ramped to 0.9 V.

- The voltage at the SYSCLK input must not exceed OV<sub>DD</sub> by more 20% during transients (see overshoot/undershoot specifications in Figure 2) or 0.3 V DC (see Table 2) at any time.

<sup>1.</sup> Guaranteed by design

System Design Information

### 9.2.3 Transient Specifications

The ensure the long-term reliability of the device, the MPC7448 requires that transients on the core power rail ( $V_{DD}$ ) be constrained. The recommended operating voltage specifications provided in Table 4 are DC specifications. That is, the device may be operated continuously with  $V_{DD}$  within the specified range without adversely affecting the device's reliability. Excursions above the stated recommended operation range, including overshoot during power-up, can impact the long-term reliability of the device. Excursions are described by their amplitude and duration. Duration is defined as the time period during which the  $V_{DD}$  power plane, as measured at the VDD\_SENSE pins, will be within a specific voltage range, expressed as percentage of the total time the device will be powered up over the device lifetime. In practice, the period over which transients are measured can be any arbitrary period of time that accurately represents the expected range of processor and system activity. The voltage ranges and durations for normal operation and transients are described in Table 14.

#### Voltage Range (V) Permitted Notes Voltage Region Duration<sup>1</sup> Min Max Normal V<sub>DD</sub> minimum V<sub>DD</sub> maximum 100% 2 Low Transient V<sub>DD</sub> maximum 1.35 V 10% 2, 3 1.35 V 1.40 V 0.2% High Transient 4

Table 14. VDD Power Supply Transient Specifications

At recommended operating temperatures. See Table 4.

### Notes:

1. Permitted duration is defined as the percentage of the total time the device is powered on that the V<sub>DD</sub> power supply voltage may exist within the specified voltage range.

2. See Table 4 for nominal  $V_{DD}$  specifications.

3. To simplify measurement, excursions into the High Transient region are included in this duration.

4. Excursions above the absolute maximum rating of 1.4 V are not permitted; see Table 2.

Note that, to simplify transient measurements, the duration of the excursion into the High Transient region is also included in the Low Transient duration, so that only the time the voltage is above each threshold must be considered. Figure 19 shows an example of measuring voltage transients.

Figure 19. Voltage Transient Example

### MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

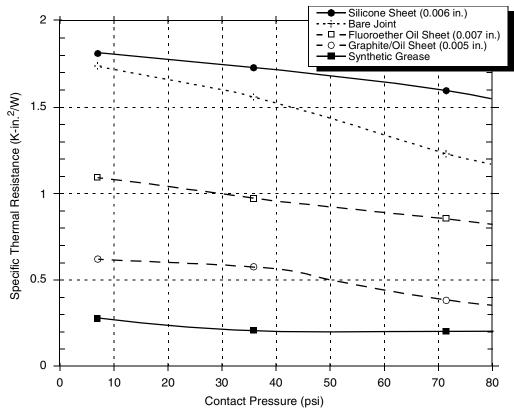

of any thermal interface material depends on many factors—thermal performance requirements, manufacturability, service temperature, dielectric properties, cost, and so on.

Figure 25. Thermal Performance of Select Thermal Interface Material

The board designer can choose between several types of thermal interfaces. Heat sink adhesive materials should be selected based on high conductivity and mechanical strength to meet equipment shock/vibration requirements. There are several commercially available thermal interfaces and adhesive materials provided by the following vendors:

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com | 800-347-4572 |

|------------------------------------------------------------------------------------------------------------------------|--------------|

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01801<br>Internet: www.chomerics.com                                    | 781-935-4850 |

| Dow-Corning Corporation<br>Corporate Center<br>P.O. Box 994.<br>Midland, MI 48686-0994<br>Internet: www.dowcorning.com | 800-248-2481 |

### System Design Information

Shin-Etsu MicroSi, Inc.888-642-767410028 S. 51st St.Phoenix, AZ 85044Internet: www.microsi.comInternet: www.microsi.comLaird Technologies - Thermal888-246-905(formerly Thermagon Inc.)4707 Detroit Ave.Cleveland, OH 44102Internet: www.lairdtech.com

The following section provides a heat sink selection example using one of the commercially available heat sinks.

### 9.7.3 Heat Sink Selection Example

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_j = T_i + T_r + (R_{\theta JC} + R_{\theta int} + R_{\theta sa}) \times P_d$$

where:

$T_j$  is the die-junction temperature

T<sub>i</sub> is the inlet cabinet ambient temperature

$T_r$  is the air temperature rise within the computer cabinet

$R_{\theta JC}$  is the junction-to-case thermal resistance

$R_{\theta int}$  is the adhesive or interface material thermal resistance

$R_{\theta sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power dissipated by the device

During operation, the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 4. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_i)$  may range from 30 to 40 C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5 to 10 C. The thermal resistance of the thermal interface material  $(R_{\theta int})$  is typically about 1.1 C/W. For example, assuming a  $T_i$  of 30 C, a  $T_r$  of 5 C, an HCTE package  $R_{\theta JC} = 0.1$ , and a power consumption  $(P_d)$  of 25.6 W, the following expression for  $T_j$  is obtained:

Die-junction temperature:  $T_i = 30$  C + 5 C + (0.1 C/W + 1.1 C/W +  $\theta_{sa}$ ) × 25.6

For this example, a  $R_{\theta sa}$  value of 1.53 C/W or less is required to maintain the die junction temperature below the maximum value of Table 4.

Though the die junction-to-ambient and the heat sink-to-ambient thermal resistances are a common figure-of-merit used for comparing the thermal performance of various microelectronic packaging technologies, one should exercise caution when only using this metric in determining thermal management because no single parameter can adequately describe three-dimensional heat flow. The final die-junction operating temperature is not only a function of the component-level thermal resistance, but the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature—airflow, board population (local heat flux of adjacent components), heat sink efficiency, heat sink attach, heat sink placement, next-level interconnect technology, system air temperature rise, altitude, and so on.

System Design Information

| DFS mode disabled                                                         |                          | DFS divide-by-2 mode enabled<br>(HID1[DFS2] = 1 or DFS2 = 0) |                          | DFS divide-by-4 mode enabled<br>(HID1[DFS4] = 1 or DFS4 = 0) |                          |

|---------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------|--------------------------|--------------------------------------------------------------|--------------------------|

| Bus-to-Core Multiplier<br>Configured by<br>PLL_CFG[0:5]<br>(see Table 12) | HID1[PC0-5] <sup>3</sup> | Bus-to-Core<br>Multiplier                                    | HID1[PC0-5] <sup>3</sup> | Bus-to-Core<br>Multiplier                                    | HID1[PC0-5] <sup>3</sup> |

| 2x <sup>4</sup>                                                           | 010000                   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 3x <sup>4</sup>                                                           | 100000                   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 4x <sup>4</sup>                                                           | 101000                   | 2x <sup>4</sup>                                              | 010000                   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 5x                                                                        | 101100                   | 2.5x <sup>4</sup>                                            | 010101                   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 5.5x                                                                      | 100100                   | 2.75x <sup>4</sup>                                           | 110101 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 6x                                                                        | 110100                   | 3x <sup>4</sup>                                              | 100000                   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 6.5x                                                                      | 010100                   | 3.25x <sup>4</sup>                                           | 100000 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 7x                                                                        | 001000                   | 3.5x <sup>4</sup>                                            | 110101                   | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 7.5x                                                                      | 000100                   | 3.75x <sup>4</sup>                                           | 110101 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 8x                                                                        | 110000                   | 4x <sup>4</sup>                                              | 101000 <sup>4</sup>      | 2x <sup>4</sup>                                              | 010000                   |

| 8.5x                                                                      | 011000                   | 4.25x <sup>4</sup>                                           | 101000 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 9x                                                                        | 011110                   | 4.5x <sup>4</sup>                                            | 011101                   | 2.25x <sup>4</sup>                                           | 010000 <sup>2</sup>      |

| 9.5x                                                                      | 011100                   | 4.75x <sup>4</sup>                                           | 011101 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 10x                                                                       | 101010                   | 5x                                                           | 101100                   | 2.5x <sup>4</sup>                                            | 010101                   |

| 10.5x                                                                     | 100010                   | 5.25x                                                        | 101100 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 11x                                                                       | 100110                   | 5.5x                                                         | 100100                   | 2.75x <sup>4</sup>                                           | 010101 <sup>2</sup>      |

| 11.5x                                                                     | 000000                   | 5.75x                                                        | 100100 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 12x                                                                       | 101110                   | 6x                                                           | 110100                   | 3x <sup>4</sup>                                              | 100000                   |

| 12.5x                                                                     | 111110                   | 6.25x                                                        | 110100 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 13x                                                                       | 010110                   | 6.5x                                                         | 010100                   | 3.25x <sup>4</sup>                                           | 100000 <sup>2</sup>      |

| 13.5x                                                                     | 111000                   | 6.75                                                         | 010100 <sup>2</sup>      | N/A (unchanged) <sup>1</sup>                                 | unchanged <sup>1</sup>   |

| 14x                                                                       | 110010                   | 7x                                                           | 001000                   | 3.5x <sup>4</sup>                                            | 110101                   |

| 15x                                                                       | 000110                   | 7.5x                                                         | 000100                   | 3.75x <sup>4</sup>                                           | 110101 <sup>2</sup>      |

| 16x                                                                       | 110110                   | 8x                                                           | 110000                   | 4x <sup>4</sup>                                              | 101000                   |

| 17x                                                                       | 000010                   | 8.5x                                                         | 011000                   | 4.25x <sup>4</sup>                                           | 101000 <sup>2</sup>      |

| 18x                                                                       | 001010                   | 9x                                                           | 011110                   | 4.5x <sup>4</sup>                                            | 011101                   |

| 20x                                                                       | 001110                   | 10x                                                          | 101010                   | 5x                                                           | 101100                   |

| 21x                                                                       | 010010                   | 10.5x                                                        | 100010                   | 5.25x                                                        | 101100 <sup>2</sup>      |

### Table 16. Valid Divide Ratio Configurations

### MPC7448 RISC Microprocessor Hardware Specifications, Rev. 4

| DFS mode disabled                                                         |                          | DFS divide-by-2 mode enabled (HID1[DFS2] = 1 or $\overline{DFS2}$ = 0) |                          | DFS divide-by-4 mode enabled<br>(HID1[DFS4] = 1 or DFS4 = 0) |                          |

|---------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------|--------------------------|

| Bus-to-Core Multiplier<br>Configured by<br>PLL_CFG[0:5]<br>(see Table 12) | HID1[PC0-5] <sup>3</sup> | Bus-to-Core<br>Multiplier                                              | HID1[PC0-5] <sup>3</sup> | Bus-to-Core<br>Multiplier                                    | HID1[PC0-5] <sup>3</sup> |

| 24x                                                                       | 011010                   | 12x                                                                    | 101110                   | 6x                                                           | 110100                   |

| 28x                                                                       | 111010                   | 14x                                                                    | 110010                   | 7x                                                           | 001000                   |

Notes:

1. DFS mode is not supported for this combination of DFS mode and PLL\_CFG[0:5] setting. As a result, the processor will ignore these settings and remain at the previous multiplier, as reflected by the HID1[PC0-PC5] bits.

2. Though supported by the MPC7448 clock circuitry, multipliers of *n*.25x and *n*.75x cannot be expressed as valid PLL configuration codes. As a result, the values displayed in HID1[PC0-PC5] are rounded down to the nearest valid PLL configuration code. However, the actual bus-to-core multiplier is as stated in this table.

- 3. Note that in the HID1 register of the MPC7448, the PC0, PC1, PC2, PC3, PC4, and PC5 bits are bits 15, 16, 17, 18, 19, and 14 (respectively). See the *MPC7450 RISC Microprocessor Reference Manual* for more information.

- 4. Special considerations regarding snooped transactions must be observed for bus-to-core multipliers less than 5x. See the *MPC7450 RISC Microprocessor Reference Manual* for more information.

### 9.7.5.3 Minimum Core Frequency Requirements with DFS

In many systems, enabling DFS can result in very low processor core frequencies. However, care must be taken to ensure that the resulting processor core frequency is within the limits specified in Table 8. Proper operation of the device is not guaranteed at core frequencies below the specified minimum  $f_{core}$ .

# **10 Document Revision History**

Table 17 provides a revision history for this hardware specification.

| Table 17. | Document | Revision | History |

|-----------|----------|----------|---------|

|-----------|----------|----------|---------|

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | 3/2007  | Table 19: Added 800 MHz processor frequency.                                                                                                                                                                                                                                                                                                                                                                                       |

| 3        | 10/2006 | Section 9.7, "Power and Thermal Management Information": Updated contact information.<br>Table 18, Table 20, and Table 19: Added Revision D PVR.<br>Table 19: Added 600 processor frequency, additional product codes, date codes for 1400 processor<br>frequency, and footnotes 1 and 2.<br>Table 20: Added PPC product code and footnote 1.<br>Table 19 and Table 20: Added Revision D information for 1267 processor frequency. |

**Document Revision History**

| Revision | Date | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                 |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        |      | Table 6: Added separate input leakage specification for BVSEL0, LSSD_MODE, TCK, TDI, TMS, TRST signals to correctly indicate leakage current for signals with internal pull-up resistors.                                                                                                                                                             |

|          |      | Section 5.1: Added paragraph preceding Table 7 and edited notes in Table 7 to clarify core frequencies at which power consumption is measured.                                                                                                                                                                                                        |

|          |      | Section 5.3: Removed voltage derating specifications; this feature has been made redundant by new device offerings and is no longer supported.                                                                                                                                                                                                        |

|          |      | Changed names of "Typical–Nominal" and "Typical–Thermal" power consumption parameters to "Typical" and "Thermal", respectively. (Name change only–no specifications were changed.)                                                                                                                                                                    |

|          |      | Table 11: Revised Notes 16, 18, and 19 to reflect current recommendations for connection of SENSE pins. Section 9.3: Added paragraph explaining connection recommendations for SENSE pins. (See also Table 11 entry above.)                                                                                                                           |

|          |      | Table 19: Updated table to reflect changes in specifications for MC7448xxnnnnNC devices.<br>Table 9: Changed all instances of TT[0:3] to TT[0:4]                                                                                                                                                                                                      |

|          |      | Removed mention of these input signals from output valid times and output hold times:<br>• AACK, CKSTP_IN, DT[0:3]                                                                                                                                                                                                                                    |

|          |      | Figure 17: Modified diagram slightly to correctly show constraint on SYSCLK ramping is related to $V_{DD}$ voltage, not AV <sub>DD</sub> voltage. (Diagram clarification only; no change in power sequencing requirements.)<br>Added Table 20 to reflect introduction of extended temperature devices and associated hardware specification addendum. |

| 1        |      | Added 1600 MHz, 1420 MHz, and 1000 MHz devices                                                                                                                                                                                                                                                                                                        |

|          |      | Section 4: corrected die size                                                                                                                                                                                                                                                                                                                         |

|          |      | Table 2: Revised Note 4 to consider overshoot/undershoot and combined with Note 5.                                                                                                                                                                                                                                                                    |

|          |      | Table 4: Revised operating voltage for 1700 MHz device from $\pm$ 50 mV to +20 mV / –50 mV.                                                                                                                                                                                                                                                           |

|          |      | Table 7: Updated and expanded table to include Typical – Nominal power consumption.<br>Table 11: Added voltage derating information for 1700 MHz devices; this feature is not supported at this time for other speed grades.                                                                                                                          |

|          |      | Added transient specifications for VDD power supply in Section 9.2.3, added Table 15 and Figure 19 and renumbered subsequent tables and figures.                                                                                                                                                                                                      |

|          |      | Moved Decoupling Recommendations from Section 9.4 to Section 9.2.4 and renumbered subsequent sections.                                                                                                                                                                                                                                                |

|          |      | Section 9.2.1: Revised power sequencing requirements.                                                                                                                                                                                                                                                                                                 |

|          |      | Section 9.7.4: Added thermal diode ideality factor information (previously TBD).                                                                                                                                                                                                                                                                      |

|          |      | Table 17: Expanded table to show HID1 register values when DFS modes are enabled.                                                                                                                                                                                                                                                                     |

|          |      | Section 11.2: updated to include additional N-spec device speed grades                                                                                                                                                                                                                                                                                |

|          |      | Tables 18 and 19: corrected PVR values and added "MC" product code prefix                                                                                                                                                                                                                                                                             |

| 0        |      | Initial public release.                                                                                                                                                                                                                                                                                                                               |

### Table 17. Document Revision History (continued)

#### How to Reach Us:

Home Page: www.freescale.com

email: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 1-800-521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MPC7448EC Rev. 4 3/2007 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. The described product is a PowerPC microprocessor. The PowerPC name is a trademark of IBM Corp. and is used under license. IEEE Stds. 1149.1<sup>™</sup> and 754<sup>™</sup> are trademarks of the Institute of Electrical and Electronics Engineers, Inc., (IEEE). This product is not endosed or approved by the IEEE. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2005, 2007.