Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 192KB (192K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 26K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xe164hn-24f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 4.7.1<br>4.7.2<br>4.7.2.1<br>4.7.2.2 | Testing Waveforms       92         Definition of Internal Timing       93         Phase Locked Loop (PLL)       94         Wakeup Clock       97 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7.2.3                              | Selecting and Changing the Operating Frequency                                                                                                   |

| 4.7.3                                | External Clock Input Parameters 98                                                                                                               |

| 4.7.4                                | Pad Properties 100                                                                                                                               |

| 4.7.5                                | External Bus Timing 104                                                                                                                          |

| 4.7.5.1                              | Bus Cycle Control with the READY Input 109                                                                                                       |

| 4.7.6                                | Synchronous Serial Interface Timing 112                                                                                                          |

| 4.7.7                                | Debug Interface Timing 116                                                                                                                       |

| 5                                    | Package and Reliability 122                                                                                                                      |

| 5.1                                  | Packaging                                                                                                                                        |

| 5.2                                  | Thermal Considerations 124                                                                                                                       |

| 5.3                                  | Quality Declarations                                                                                                                             |

### **General Device Information**

# 2 General Device Information

### The XE164xN series (16-Bit Single-Chip

Real Time Signal Controller) is a part of the Infineon XE166 Family of full-feature singlechip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

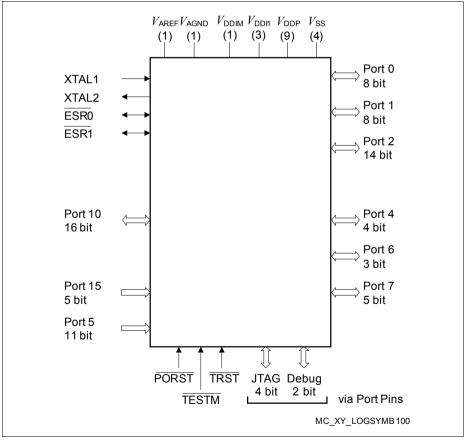

Figure 2 XE164xN Logic Symbol

#### **General Device Information**

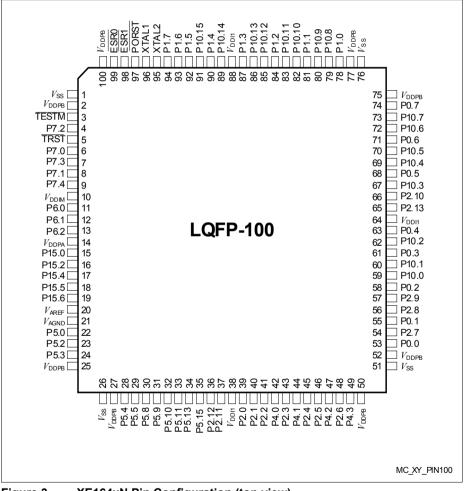

# 2.1 Pin Configuration and Definition

The pins of the XE164xN are described in detail in **Table 5**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. The following figure summarizes all pins, showing their locations on the four sides of the package.

Figure 3 XE164xN Pin Configuration (top view)

### **General Device Information**

| Pin | Symbol           | Ctrl.  | Туре | Function                                                                                                                                        |  |  |  |  |

|-----|------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 31  | P5.9             | I      | In/A | Bit 9 of Port 5, General Purpose Input                                                                                                          |  |  |  |  |

|     | ADC0_CH9         | I      | In/A | Analog Input Channel 9 for ADC0                                                                                                                 |  |  |  |  |

|     | ADC1_CH9         | 1      | In/A | Analog Input Channel 9 for ADC1                                                                                                                 |  |  |  |  |

|     | CC2_T7IN         | 1      | In/A | CAPCOM2 Timer T7 Count Input                                                                                                                    |  |  |  |  |

| 32  | P5.10            | I      | In/A | Bit 10 of Port 5, General Purpose Input                                                                                                         |  |  |  |  |

|     | ADC0_CH10        | 1      | In/A | Analog Input Channel 10 for ADC0                                                                                                                |  |  |  |  |

|     | ADC1_CH10        | 1      | In/A | Analog Input Channel 10 for ADC1                                                                                                                |  |  |  |  |

|     | BRKIN_A          | 1      | In/A | OCDS Break Signal Input                                                                                                                         |  |  |  |  |

|     | U2C1_DX0F        | 1      | In/A | USIC2 Channel 1 Shift Data Input                                                                                                                |  |  |  |  |

|     | CCU61_T13<br>HRA | I      | In/A | External Run Control Input for T13 of CCU61                                                                                                     |  |  |  |  |

| 33  | P5.11            | I      | In/A | Bit 11 of Port 5, General Purpose Input                                                                                                         |  |  |  |  |

|     | ADC0_CH11        | I      | In/A | Analog Input Channel 11 for ADC0                                                                                                                |  |  |  |  |

|     | ADC1_CH11        | I      | In/A | Analog Input Channel 11 for ADC1                                                                                                                |  |  |  |  |

| 34  | P5.13            | 1      | In/A | Bit 13 of Port 5, General Purpose Input                                                                                                         |  |  |  |  |

|     | ADC0_CH13        | I      | In/A | Analog Input Channel 13 for ADC0                                                                                                                |  |  |  |  |

| 35  | P5.15            | I      | In/A | Bit 15 of Port 5, General Purpose Input                                                                                                         |  |  |  |  |

| _   | ADC0_CH15        | I      | In/A | Analog Input Channel 15 for ADC0                                                                                                                |  |  |  |  |

| 36  | P2.12            | O0 / I | St/B | Bit 12 of Port 2, General Purpose Input/Output                                                                                                  |  |  |  |  |

|     | U0C0_SELO<br>4   | 01     | St/B | USIC0 Channel 0 Select/Control 4 Output                                                                                                         |  |  |  |  |

|     | U0C1_SELO<br>3   | O2     | St/B | USIC0 Channel 1 Select/Control 3 Output                                                                                                         |  |  |  |  |

|     | READY            | IH     | St/B | External Bus Interface READY Input                                                                                                              |  |  |  |  |

| 37  | P2.11            | O0 / I | St/B | Bit 11 of Port 2, General Purpose Input/Output                                                                                                  |  |  |  |  |

|     | U0C0_SELO<br>2   | 01     | St/B | USIC0 Channel 0 Select/Control 2 Output                                                                                                         |  |  |  |  |

|     | U0C1_SELO<br>2   | 02     | St/B | USIC0 Channel 1 Select/Control 2 Output                                                                                                         |  |  |  |  |

|     | BHE/WRH          | ОН     | St/B | <b>External Bus Interf. High-Byte Control Output</b><br>Can operate either as Byte High Enable (BHE) or<br>as Write strobe for High Byte (WRH). |  |  |  |  |

### **General Device Information**

| Table | Table 5Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-------|-----------------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 57    | P2.9                                          | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                                        |  |  |  |  |

|       | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |  |  |  |  |

|       | TxDC1                                         | 02     | St/B | CAN Node 1 Transmit Data Output                                                                                                                                                                                                                                                                      |  |  |  |  |

|       | CC2_CC22                                      | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                                            |  |  |  |  |

|       | A22                                           | ОН     | St/B | External Bus Interface Address Line 22                                                                                                                                                                                                                                                               |  |  |  |  |

|       | CLKIN1                                        | I      | St/B | Clock Signal Input 1                                                                                                                                                                                                                                                                                 |  |  |  |  |

|       | TCK_A                                         | IH     | St/B | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. A is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 0 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |  |  |

| 58    | P0.2                                          | O0 / I | St/B | Bit 2 of Port 0, General Purpose Input/Output                                                                                                                                                                                                                                                        |  |  |  |  |

|       | U1C0_SCLK<br>OUT                              | 01     | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                                                                                                                                                   |  |  |  |  |

|       | TxDC0                                         | 02     | St/B | CAN Node 0 Transmit Data Output                                                                                                                                                                                                                                                                      |  |  |  |  |

|       | CCU61_CC6<br>2                                | O3     | St/B | CCU61 Channel 2 Output                                                                                                                                                                                                                                                                               |  |  |  |  |

|       | A2                                            | OH     | St/B | External Bus Interface Address Line 2                                                                                                                                                                                                                                                                |  |  |  |  |

|       | U1C0_DX1B                                     | I      | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                    |  |  |  |  |

|       | CCU61_CC6<br>2INA                             | I      | St/B | CCU61 Channel 2 Input                                                                                                                                                                                                                                                                                |  |  |  |  |

#### **General Device Information**

| Table | Table 5Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                       |  |  |  |

| 70    | P10.5                                         | O0 / I     | St/B | Bit 5 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C1_SCLK<br>OUT                              | 01         | St/B | USIC0 Channel 1 Shift Clock Output             |  |  |  |

|       | CCU60_COU<br>T62                              | O2         | St/B | CCU60 Channel 2 Output                         |  |  |  |

|       | U2C0_DOUT                                     | O3         | St/B | USIC2 Channel 0 Shift Data Output              |  |  |  |

|       | AD5                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 5     |  |  |  |

|       | U0C1_DX1B                                     | I          | St/B | USIC0 Channel 1 Shift Clock Input              |  |  |  |

| 71    | P0.6                                          | O0 / I     | St/B | Bit 6 of Port 0, General Purpose Input/Output  |  |  |  |

|       | U1C1_DOUT                                     | 01         | St/B | USIC1 Channel 1 Shift Data Output              |  |  |  |

|       | TxDC1                                         | O2         | St/B | CAN Node 1 Transmit Data Output                |  |  |  |

|       | CCU61_COU<br>T63                              | O3         | St/B | CCU61 Channel 3 Output                         |  |  |  |

|       | A6                                            | OH         | St/B | External Bus Interface Address Line 6          |  |  |  |

|       | U1C1_DX0A                                     | I          | St/B | USIC1 Channel 1 Shift Data Input               |  |  |  |

|       | CCU61_CTR<br>APA                              | 1          | St/B | CCU61 Emergency Trap Input                     |  |  |  |

|       | U1C1_DX1B                                     | I          | St/B | USIC1 Channel 1 Shift Clock Input              |  |  |  |

| 72    | P10.6                                         | O0 / I     | St/B | Bit 6 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C0_DOUT                                     | 01         | St/B | USIC0 Channel 0 Shift Data Output              |  |  |  |

|       | U1C0_SELO<br>0                                | O3         | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |  |  |

|       | AD6                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 6     |  |  |  |

|       | U0C0_DX0C                                     | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|       | U1C0_DX2D                                     | I          | St/B | USIC1 Channel 0 Shift Control Input            |  |  |  |

|       | CCU60_CTR<br>APA                              | I          | St/B | CCU60 Emergency Trap Input                     |  |  |  |

# XE164FN, XE164GN, XE164HN, XE164KN XE166 Family / Value Line

### **General Device Information**

| Table | Table 5Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                       |  |  |  |

| 73    | P10.7                                         | O0 / I     | St/B | Bit 7 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C1_DOUT                                     | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |

|       | CCU60_COU<br>T63                              | 02         | St/B | CCU60 Channel 3 Output                         |  |  |  |

|       | AD7                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 7     |  |  |  |

|       | U0C1_DX0B                                     | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |

|       | CCU60_CCP<br>OS0A                             | I          | St/B | CCU60 Position Input 0                         |  |  |  |

|       | T4INB                                         | I          | St/B | GPT12E Timer T4 Count/Gate Input               |  |  |  |

| 74    | P0.7                                          | O0 / I     | St/B | Bit 7 of Port 0, General Purpose Input/Output  |  |  |  |

|       | U1C1_DOUT                                     | 01         | St/B | USIC1 Channel 1 Shift Data Output              |  |  |  |

|       | U1C0_SELO<br>3                                | O2         | St/B | USIC1 Channel 0 Select/Control 3 Output        |  |  |  |

|       | A7                                            | ОН         | St/B | External Bus Interface Address Line 7          |  |  |  |

|       | U1C1_DX0B                                     | I          | St/B | USIC1 Channel 1 Shift Data Input               |  |  |  |

|       | CCU61_CTR<br>APB                              | I          | St/B | CCU61 Emergency Trap Input                     |  |  |  |

| 78    | P1.0                                          | O0 / I     | St/B | Bit 0 of Port 1, General Purpose Input/Output  |  |  |  |

|       | U1C0_MCLK<br>OUT                              | 01         | St/B | USIC1 Channel 0 Master Clock Output            |  |  |  |

|       | U1C0_SELO<br>4                                | 02         | St/B | USIC1 Channel 0 Select/Control 4 Output        |  |  |  |

|       | A8                                            | ОН         | St/B | External Bus Interface Address Line 8          |  |  |  |

|       | ESR1_3                                        | I          | St/B | ESR1 Trigger Input 3                           |  |  |  |

|       | T6INB                                         | I          | St/B | GPT12E Timer T6 Count/Gate Input               |  |  |  |

# XE164FN, XE164GN, XE164HN, XE164KN XE166 Family / Value Line

### **General Device Information**

| Table            | Table 5Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                     |  |  |  |

|------------------|-----------------------------------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin              | Symbol                                        | Ctrl.  | Туре | Function                                                                                                                                                                            |  |  |  |

| 98               | ESR1                                          | O0 / I | St/B | <b>External Service Request 1</b><br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                             |  |  |  |

|                  | RxDC0E                                        | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                       |  |  |  |

|                  | U1C0_DX0F                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                    |  |  |  |

|                  | U1C0_DX2C                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                 |  |  |  |

|                  | U1C1_DX0C                                     | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                    |  |  |  |

|                  | U1C1_DX2B                                     | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                 |  |  |  |

|                  | U2C1_DX2C                                     | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                 |  |  |  |

| 99               | ESR0                                          | O0 / I | St/B | <b>External Service Request 0</b><br>After power-up, ESR0 operates as open-drain<br>bidirectional reset with a weak pull-up.                                                        |  |  |  |

|                  | U1C0_DX0E                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                    |  |  |  |

|                  | U1C0_DX2B                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                 |  |  |  |

| 10               | V <sub>DDIM</sub>                             | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                |  |  |  |

| 38,<br>64,<br>88 | V <sub>DDI1</sub>                             | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All $V_{\text{DDI1}}$ pins must be connected to each other. |  |  |  |

| 14               | V <sub>DDPA</sub>                             | -      | PS/A | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent $V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.              |  |  |  |

|                  |                                               |        |      | Note: The A/D_Converters and ports P5, P6 and P15 are fed from supply voltage $V_{DDPA}$ .                                                                                          |  |  |  |

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |

|----------------------|----------------------|----------------------|-------------------------|-------|

| Reserved for DSRAM   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                |       |

| External memory area | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               |       |

### Table 7 XE164xN Memory Map (cont'd)<sup>1)</sup>

Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

- 2) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

- 3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

- Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 16 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the quoted device type.

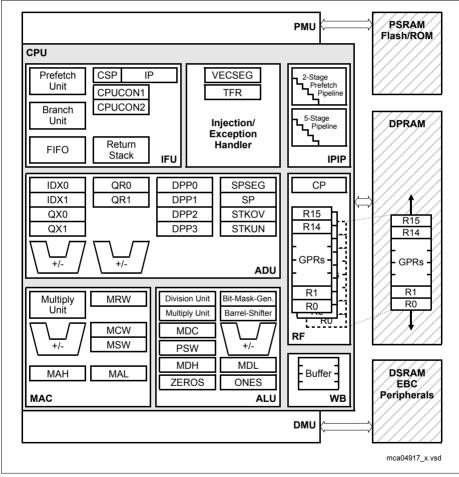

# 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

Figure 5 CPU Block Diagram

### **Functional Description**

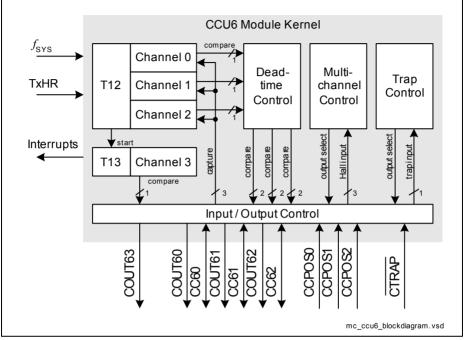

### Figure 7 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

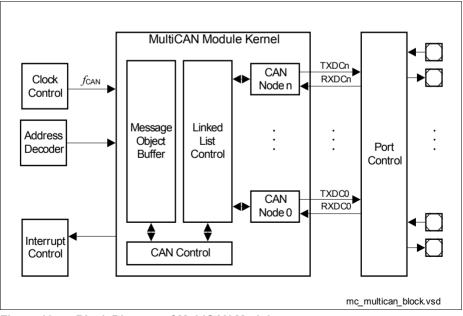

# 3.14 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 12 Block Diagram of MultiCAN Module

### 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE164xN from a number of external or internal clock sources:

- · External clock signals with pad voltage or core voltage levels

- · External crystal or resonator using the on-chip oscillator

- · On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

## 3.18 Parallel Ports

The XE164xN provides up to 76 I/O lines which are organized into 7 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in Table 9.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |

|------|-------|-----|---------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0), CCU6, USIC, CAN                                                     |

| P1   | 8     | I/O | EBC (A15A8), CCU6, USIC                                                         |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P4   | 4     | I/O | EBC (CS3CS0), CC2, CAN, GPT12E, USIC                                            |

| P5   | 11    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |

| P6   | 3     | I/O | ADC, CAN, GPT12E                                                                |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN                    |

| P15  | 5     | I   | Analog Inputs, GPT12E                                                           |

### Table 9Summary of the XE164xN's Ports

- 7) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pins leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ}| + (|I_{OV}| K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- 8) Value is controlled by on-chip regulator

### 4.2 Voltage Range definitions

The XE164xN timing depends on the supply voltage. If such a dependency exists the timing values are given for 2 voltage areas commonly used. The voltage areas are defined in the following tables.

Table 13 Upper Voltage Range Definition

| Parameter                                                       | imeter Symbol Values |      |      | Unit | Note / |                |

|-----------------------------------------------------------------|----------------------|------|------|------|--------|----------------|

|                                                                 |                      | Min. | Тур. | Max. |        | Test Condition |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 4.5  | 5    | 5.5  | V      |                |

| Table 14 | Lower Voltage Range Definition |

|----------|--------------------------------|

|----------|--------------------------------|

| Parameter                                                       | Symbol               |      | Values |      | Unit | Note /         |

|-----------------------------------------------------------------|----------------------|------|--------|------|------|----------------|

|                                                                 |                      | Min. | Тур.   | Max. |      | Test Condition |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 3.0  | 3.3    | 4.5  | V    |                |

### 4.2.1 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XE164xN and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

CC (Controller Characteristics):

The logic of the XE164xN provides signals with the specified characteristics.

#### SR (System Requirement):

The external system must provide signals with the specified characteristics to the XE164xN.

- This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

- 3)  $f_{WU}$  in MHz

- 4) This value includes a hysteresis of approximately 50 mV for rising voltage.

- 5)  $V_{\rm LV}$  = selected SWD voltage level

- 6) The limit  $V_{LV}$  0.10 V is valid for the OK1 level. The limit for the OK2 level is  $V_{LV}$  0.15 V.

### Conditions for t<sub>SPO</sub> Timing Measurement

The time required for the transition from **Power-on** to **Base** mode is called  $t_{SPO}$ . It is measured under the following conditions:

Precondition: The pad supply is valid, i.e.  $V_{\text{DDPB}}$  is above 3.0V and remains above 3.0V even though the XE164xN is starting up. No debugger is attached.

Start condition: Power-on reset is removed ( $\overline{PORST} = 1$ ).

End condition: External pin toggle caused by first user instruction executed from FLASH after startup.

### Conditions for t<sub>SSO</sub> Timing Measurement

The time required for the transition from **Stopover** to **Stopover Waked-Up** mode is called  $t_{SSO}$ . It is measured under the following conditions:

Precondition: The **Stopover** mode has been entered using the procedure defined in the Programmer's Guide.

Start condition: Pin toggle on ESR pin triggering the startup sequence.

End condition: External pin toggle caused by first user instruction executed from PSRAM after startup.

| Parameter                                                    | Symbol                  | Values |      |      | Unit | Note /                      |

|--------------------------------------------------------------|-------------------------|--------|------|------|------|-----------------------------|

|                                                              |                         | Min.   | Тур. | Max. |      | Test Condition              |

| Maximum output driver current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -      | -    | 2.5  | mA   | Driver_Strength<br>= Medium |

|                                                              |                         | _      | -    | 10   | mA   | Driver_Strength<br>= Strong |

|                                                              |                         | -      | -    | 0.5  | mA   | Driver_Strength<br>= Weak   |

| Nominal output driver<br>current (absolute value)            | I <sub>Onom</sub><br>CC | -      | -    | 1.0  | mA   | Driver_Strength<br>= Medium |

|                                                              |                         | -      | -    | 2.5  | mA   | Driver_Strength<br>= Strong |

|                                                              |                         | _      | -    | 0.1  | mA   | Driver_Strength<br>= Weak   |

### Table 28 Standard Pad Parameters for Lower Voltage Range

### Variable Memory Cycles

External bus cycles of the XE164xN are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

| Table 30 | Programmable Bus Cy | cle Phases (s | see timing diagrams) |

|----------|---------------------|---------------|----------------------|

|          | riegrammasie Dae ey |               |                      |

| Bus Cycle Phase                                                                                                                | Parameter | Valid Values | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 2 TCS) can be extended by 0 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                            | tpC       | 03           | TCS  |

| Write Data setup/MUX Tristate phase                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                  | tpF       | 03           | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply.

**Table 31** is valid under the following conditions:  $C_L$ = 20 pF; voltage\_range= upper; voltage\_range= upper

| Table 31 | External Bus | Timing for | Upper Voltage Range |

|----------|--------------|------------|---------------------|

|----------|--------------|------------|---------------------|

| Parameter                                                                    | Symbol                    | Values |      |      | Unit | Note /         |

|------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                              |                           | Min.   | Тур. | Max. |      | Test Condition |

| $\frac{\text{Output valid delay for }\overline{\text{RD}},}{\text{WR}(L/H)}$ | <i>t</i> <sub>10</sub> CC | -      | 7    | 13   | ns   |                |

| Output valid delay for BHE, ALE                                              | <i>t</i> <sub>11</sub> CC | -      | 7    | 14   | ns   |                |

| Address output valid delay for A23 A0                                        | <i>t</i> <sub>12</sub> CC | -      | 8    | 14   | ns   |                |

#### Table 35 USIC SSC Slave Mode Timing for Upper Voltage Range (cont'd)

| Parameter                                                                      | Symbol                    | Values |      |      | Unit | Note /         |

|--------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                |                           | Min.   | Тур. | Max. |      | Test Condition |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>13</sub> SR | 5      | -    | -    | ns   |                |

| Data output DOUT valid time                                                    | <i>t</i> <sub>14</sub> CC | 7      | -    | 33   | ns   |                |

These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

**Table 36** is valid under the following conditions:  $C_L$ = 20 pF; *SSC*= slave ; voltage range= lower

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                   |                           | Min.   | Тур. | Max. | _    | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5      | -    | -    | ns   |                |

| Data output DOUT valid time                                                       | <i>t</i> <sub>14</sub> CC | 8      | -    | 41   | ns   |                |

#### Table 36 USIC SSC Slave Mode Timing for Lower Voltage Range

These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

#### Package and Reliability

# 5.2 Thermal Considerations

When operating the XE164xN in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}}-V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- · Reduce the system frequency

- · Reduce the number of output pins

- Reduce the load on active output drivers