Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 192KB (192K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 26K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 11x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xe164kn-24f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2                                                                                                                                  | Summary of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                                                  | General Device Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                             |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19 | Functional Description         Memory Subsystem and Organization         External Bus Controller         Central Processing Unit (CPU)         Memory Protection Unit (MPU)         Memory Checker Module (MCHK)         Interrupt System         On-Chip Debug Support (OCDS)         Capture/Compare Unit (CC2)         Capture/Compare Units CCU6x         General Purpose Timer (GPT12E) Unit         Real Time Clock         A/D Converters         Universal Serial Interface Channel Modules (USIC)         MultiCAN Module         System Timer         Watchdog Timer         Clock Generation         Parallel Ports         Instruction Set Summary | $\begin{array}{r} 38\\ 42\\ 43\\ 45\\ 46\\ 47\\ 48\\ 51\\ 53\\ 57\\ 60\\ 62\\ 63\\ 63\\ 64\\ 65\\ \end{array}$ |

| <b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4<br>4.5<br>4.6<br>4.7                                                           | Electrical Parameters<br>General Parameters<br>Operating Conditions<br>Voltage Range definitions<br>Parameter Interpretation<br>DC Parameters<br>DC Parameters for Upper Voltage Area<br>DC Parameters for Lower Voltage Area<br>Power Consumption<br>Analog/Digital Converter Parameters<br>System Parameters<br>Flash Memory Parameters<br>AC Parameters                                                                                                                                                                                                                                                                                                     | 69<br>70<br>72<br>73<br>75<br>77<br>79<br>83<br>87<br>90                                                       |

#### Summary of Features

- On-Chip Peripheral Modules

- Two synchronizable A/D Converters with up to 16 channels, 10-bit resolution, conversion time below 1  $\mu$ s, optional data preprocessing (data reduction, range check), broken wire detection

- 16-channel general purpose capture/compare unit (CC2)

- Two capture/compare units for flexible PWM signal generation (CCU6x)

- Multi-functional general purpose timer unit with 5 timers

- Up to 6 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI/QSPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with 64 message objects (Full CAN/Basic CAN) on up to 2 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Four programmable chip-select signals

- Single power supply from 3.0 V to 5.5 V

- Power reduction and wake-up modes

- Programmable watchdog timer and oscillator watchdog

- Up to 76 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- · On-chip debug support via Device Access Port (DAP) or JTAG interface

- 100-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the temperature range:

- SAF-...: -40°C to 85°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XE164xN please contact your sales representative or local distributor.

### **General Device Information**

| Pin | Symbol           | Ctrl.  | Туре | Function                                          |

|-----|------------------|--------|------|---------------------------------------------------|

| 11  | P6.0             | O0 / I | DA/A | Bit 0 of Port 6, General Purpose Input/Output     |

|     | EMUX0            | 01     | DA/A | External Analog MUX Control Output 0 (ADC0)       |

|     | BRKOUT           | O3     | DA/A | OCDS Break Signal Output                          |

|     | ADCx_REQG<br>TyG | I      | DA/A | External Request Gate Input for ADC0/1            |

|     | U1C1_DX0E        | I      | DA/A | USIC1 Channel 1 Shift Data Input                  |

| 12  | P6.1             | O0 / I | DA/A | Bit 1 of Port 6, General Purpose Input/Output     |

|     | EMUX1            | 01     | DA/A | External Analog MUX Control Output 1 (ADC0)       |

|     | T3OUT            | O2     | DA/A | GPT12E Timer T3 Toggle Latch Output               |

|     | U1C1_DOUT        | O3     | DA/A | USIC1 Channel 1 Shift Data Output                 |

|     | ADCx_REQT<br>RyE | I      | DA/A | External Request Trigger Input for ADC0/1         |

|     | ESR1_6           | I      | DA/A | ESR1 Trigger Input 6                              |

| 13  | P6.2             | O0 / I | DA/A | Bit 2 of Port 6, General Purpose Input/Output     |

|     | EMUX2            | 01     | DA/A | External Analog MUX Control Output 2 (ADC0)       |

|     | T6OUT            | O2     | DA/A | GPT12E Timer T6 Toggle Latch Output               |

|     | U1C1_SCLK<br>OUT | O3     | DA/A | USIC1 Channel 1 Shift Clock Output                |

|     | U1C1_DX1C        | I      | DA/A | USIC1 Channel 1 Shift Clock Input                 |

| 15  | P15.0            | I      | In/A | Bit 0 of Port 15, General Purpose Input           |

|     | ADC1_CH0         | I      | In/A | Analog Input Channel 0 for ADC1                   |

| 16  | P15.2            | I      | In/A | Bit 2 of Port 15, General Purpose Input           |

|     | ADC1_CH2         | I      | In/A | Analog Input Channel 2 for ADC1                   |

|     | T5INA            | I      | In/A | GPT12E Timer T5 Count/Gate Input                  |

| 17  | P15.4            | I      | In/A | Bit 4 of Port 15, General Purpose Input           |

|     | ADC1_CH4         | I      | In/A | Analog Input Channel 4 for ADC1                   |

|     | T6INA            | I      | In/A | GPT12E Timer T6 Count/Gate Input                  |

| 18  | P15.5            | I      | In/A | Bit 5 of Port 15, General Purpose Input           |

|     | ADC1_CH5         | 1      | In/A | Analog Input Channel 5 for ADC1                   |

|     | T6EUDA           | I      | In/A | GPT12E Timer T6 External Up/Down Control<br>Input |

### **General Device Information**

| Pin | Symbol            | Ctrl.      | Туре | Function                                       |

|-----|-------------------|------------|------|------------------------------------------------|

| 59  | P10.0             | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |

|     | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |

|     | CCU60_CC6<br>0    | O2         | St/B | CCU60 Channel 0 Output                         |

|     | AD0               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |

|     | CCU60_CC6<br>0INA | 1          | St/B | CCU60 Channel 0 Input                          |

|     | ESR1_2            | I          | St/B | ESR1 Trigger Input 2                           |

|     | U0C0_DX0A         | I          | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U0C1_DX0A         | I          | St/B | USIC0 Channel 1 Shift Data Input               |

| 60  | P10.1             | O0 / I     | St/B | Bit 1 of Port 10, General Purpose Input/Output |

|     | U0C0_DOUT         | 01         | St/B | USIC0 Channel 0 Shift Data Output              |

|     | CCU60_CC6<br>1    | O2         | St/B | CCU60 Channel 1 Output                         |

|     | AD1               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 1     |

|     | CCU60_CC6<br>1INA | I          | St/B | CCU60 Channel 1 Input                          |

|     | U0C0_DX1A         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |

|     | U0C0_DX0B         | I          | St/B | USIC0 Channel 0 Shift Data Input               |

| 61  | P0.3              | O0 / I     | St/B | Bit 3 of Port 0, General Purpose Input/Output  |

|     | U1C0_SELO<br>0    | O1         | St/B | USIC1 Channel 0 Select/Control 0 Output        |

|     | U1C1_SELO<br>1    | O2         | St/B | USIC1 Channel 1 Select/Control 1 Output        |

|     | CCU61_COU<br>T60  | O3         | St/B | CCU61 Channel 0 Output                         |

|     | A3                | ОН         | St/B | External Bus Interface Address Line 3          |

|     | U1C0_DX2A         | I          | St/B | USIC1 Channel 0 Shift Control Input            |

|     | RxDC0B            | I          | St/B | CAN Node 0 Receive Data Input                  |

#### **General Device Information**

| Table 5Pin Definitions and Functions (cont'd) |                   |            |      |                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----------------------------------------------|-------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin                                           | Symbol            | Ctrl.      | Туре | Function                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 79                                            | P10.8             | O0 / I     | St/B | Bit 8 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |  |  |  |  |

|                                               | U0C0_MCLK<br>OUT  | 01         | St/B | USIC0 Channel 0 Master Clock Output                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                               | U0C1_SELO<br>0    | O2         | St/B | USIC0 Channel 1 Select/Control 0 Output                                                                                                                                                                                                                                                              |  |  |  |  |

|                                               | U2C1_DOUT         | O3         | St/B | USIC2 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                               | AD8               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 8                                                                                                                                                                                                                                                           |  |  |  |  |

|                                               | CCU60_CCP<br>OS1A | I          | St/B | CCU60 Position Input 1                                                                                                                                                                                                                                                                               |  |  |  |  |

|                                               | U0C0_DX1C         | I          | St/B | USIC0 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                               | BRKIN_B           | I          | St/B | OCDS Break Signal Input                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                               | T3EUDB            | 1          | St/B | GPT12E Timer T3 External Up/Down Control Input                                                                                                                                                                                                                                                       |  |  |  |  |

| 80                                            | P10.9             | O0 / I     | St/B | Bit 9 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |  |  |  |  |

|                                               | U0C0_SELO<br>4    | 01         | St/B | USIC0 Channel 0 Select/Control 4 Output                                                                                                                                                                                                                                                              |  |  |  |  |

|                                               | U0C1_MCLK<br>OUT  | O2         | St/B | USIC0 Channel 1 Master Clock Output                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                               | AD9               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 9                                                                                                                                                                                                                                                           |  |  |  |  |

|                                               | CCU60_CCP<br>OS2A | 1          | St/B | CCU60 Position Input 2                                                                                                                                                                                                                                                                               |  |  |  |  |

|                                               | ТСК_В             | IH         | St/B | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |  |  |

|                                               |                   | 1          | St/B | GPT12E Timer T3 Count/Gate Input                                                                                                                                                                                                                                                                     |  |  |  |  |

Up to 16 Kbytes of on-chip Data SRAM (DSRAM) are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

Note: The actual size of the DSRAM depends on the quoted device type.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XE166 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 7**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**The on-chip Flash memory** stores code, constant data, and control data. The 320 Kbytes of on-chip Flash memory consist of 1 module of 64 Kbytes (preferably for data storage) and 1 module of 256 Kbytes. Each module is organized in 4-Kbyte sectors. The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see Section 4.6.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

### **Memory Content Protection**

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Depending on the package option up to 3 External Service Request (ESR) pins are provided. The ESR unit processes their input values and allows to implement user controlled trap functions (System Requests SR0 and SR1). In this way reset, wakeup and power control can be efficiently realized.

Software interrupts are supported by the 'TRAP' instruction in combination with an individual trap (interrupt) number. Alternatively to emulate an interrupt by software a program can trigger interrupt requests by writing the Interrupt Request (IR) bit of an interrupt control register.

# 3.7 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XE164xN provides a broad range of debug and emulation features. User software running on the XE164xN can be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface. This either consists of the 2-pin Device Access Port (DAP) or of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (DAP or JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing of data can be obtained via the debug interface, or via the external bus interface for increased performance.

Tracing of program execution is supported by the XE166 Family emulation device. With this device the DAP can operate on clock rates of up to 20 MHz.

The DAP interface uses two interface signals, the JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

# 3.8 Capture/Compare Unit (CC2)

The CAPCOM unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, external count inputs allow event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

| Compare Modes | Function                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

Table 8 Compare Modes

### 3.12 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 11 + 5 multiplexed input channels and a sample and hold circuit have been integrated on-chip. 4 inputs can be converted by both A/D converters. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XE164xN support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

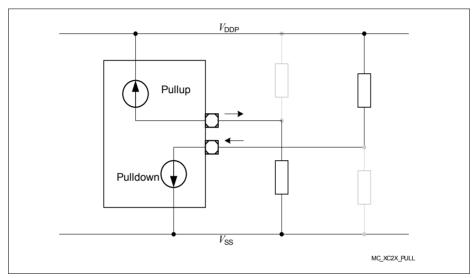

### Pullup/Pulldown Device Behavior

Most pins of the XE164xN feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 13** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 13 Pullup/Pulldown Current Definition

### 4.3.2 DC Parameters for Lower Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

Table 16 is valid under the following conditions:  $V_{\rm DDP} \ge 3.0$  V;  $V_{\rm DDP}$ typ. 3.3 V;  $V_{\rm DDP} \le 4.5$  V

| Parameter                                                                                   | Symbol                   |                            | Values | 6                         | Unit | Note /                                                                                                                        |

|---------------------------------------------------------------------------------------------|--------------------------|----------------------------|--------|---------------------------|------|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             |                          | Min.                       | Тур.   | Max.                      |      | Test Condition                                                                                                                |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. <sup>1)</sup> | C <sub>IO</sub> CC       | _                          | -      | 10                        | pF   | not subject to production test                                                                                                |

| Input Hysteresis <sup>2)</sup>                                                              | HYS CC                   | 0.07 x<br>V <sub>DDP</sub> | -      | -                         | V    | R <sub>S</sub> = 0 Ohm                                                                                                        |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                        | I <sub>oz1</sub>  <br>CC | -                          | 10     | 200                       | nA   | $V_{\rm IN}$ > $V_{\rm SS}$ ;<br>$V_{\rm IN}$ < $V_{\rm DDP}$                                                                 |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double           | I <sub>OZ2</sub>  <br>CC | _                          | 0.2    | 2.5                       | μA   | $\begin{array}{l} T_{\rm J} \leq 110 ~^{\circ}{\rm C}; \\ V_{\rm IN} > V_{\rm SS} ~; \\ V_{\rm IN} < V_{\rm DDP} \end{array}$ |

| bond pins. <sup>3)1)4)</sup>                                                                |                          | _                          | 0.2    | 8                         | μA   | $T_{J} \le 150 \ ^{\circ}C;$<br>$V_{IN} > V_{SS};$<br>$V_{IN} < V_{DDP}$                                                      |

| Pull Level Force Current <sup>5)</sup>                                                      | I <sub>PLF</sub>   SR    | 150                        | _      | _                         | μA   | $ \begin{array}{l} V_{\rm IN} \geq V_{\rm IHmin}(pull \\ down) ; \\ V_{\rm IN} \leq V_{\rm ILmax}(pull \\ up) \end{array} $   |

| Pull Level Keep Current <sup>6)</sup>                                                       | I <sub>PLK</sub>  <br>SR | -                          | -      | 10                        | μA   | $V_{\rm IN} \ge V_{\rm IHmin}(pull up);$<br>$V_{\rm IN} \le V_{\rm ILmax}(pull down)$                                         |

| Input high voltage (all except XTAL1)                                                       | V <sub>IH</sub> SR       | 0.7 x<br>V <sub>DDP</sub>  | -      | V <sub>DDP</sub> + 0.3    | V    |                                                                                                                               |

| Input low voltage<br>(all except XTAL1)                                                     | $V_{\rm IL}$ SR          | -0.3                       | -      | 0.3 x<br>V <sub>DDP</sub> | V    |                                                                                                                               |

### Table 16 DC Characteristics for Lower Voltage Range

| Parameter                         | Symbol             |                        | Values | 5    | Unit | Note /<br>Test Condition                 |

|-----------------------------------|--------------------|------------------------|--------|------|------|------------------------------------------|

|                                   |                    | Min.                   | Тур.   | Max. |      |                                          |

| Output High voltage <sup>7)</sup> | V <sub>OH</sub> CC | V <sub>DDP</sub> - 1.0 | -      | -    | V    | $I_{\rm OH} \ge I_{\rm OHmax}$           |

|                                   |                    | V <sub>DDP</sub> - 0.4 | -      | -    | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{8}$ |

| Output Low Voltage <sup>7)</sup>  | V <sub>OL</sub> CC | -                      | -      | 0.4  | V    | $I_{\rm OL} \le I_{\rm OLnom}^{8}$       |

|                                   |                    | -                      | -      | 1.0  | V    | $I_{\rm OL} \leq I_{\rm OLmax}$          |

#### Table 16 DC Characteristics for Lower Voltage Range (cont'd)

1) Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm CV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (*T*<sub>J</sub> = junction temperature [°C]): *I*<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x TJ<sup>-</sup>)</sup> [µA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 µA. Leakage derating depending on voltage level (DV = *V*<sub>DDP</sub> *V*<sub>PIN</sub> [V]): *I*<sub>OZ</sub> = *I*<sub>OZtempmax</sub> (1.6 x DV) (µA]. This voltage derating formula is an approximation which applies for maximum temperature.

- Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device: V<sub>PIN</sub> <= V<sub>IL</sub> for a pullup; V<sub>PIN</sub> >= V<sub>IH</sub> for a pulldown.

- 6) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> >= V<sub>IL</sub> for a pullup; V<sub>PIN</sub> <= V<sub>IL</sub> for a pulldown.

- 7) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 8) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL}$ -> $V_{SS}$ ,  $V_{OH}$ -> $V_{DDP}$ ). However, only the levels for nominal output currents are verified.

### 4.3.3 Power Consumption

The power consumed by the XE164xN depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current  $I_{\rm LK}$  depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

### Table 17 Switching Power Consumption

| Parameter                                                                    | Symbol                  |      | Values                      |                                           | Unit | Note /                                                              |

|------------------------------------------------------------------------------|-------------------------|------|-----------------------------|-------------------------------------------|------|---------------------------------------------------------------------|

|                                                                              |                         | Min. | Тур.                        | Max.                                      |      | Test Condition                                                      |

| Power supply current<br>(active) with all peripherals<br>active and EVVRs on | I <sub>SACT</sub><br>CC | _    | $6 + 0.6 \\ x f_{SYS}^{1)}$ | 8+1.0<br>x f <sub>SYS</sub> <sup>1)</sup> | mA   | power_mode=<br>active ;<br>voltage_range=<br>both <sup>2)3)4)</sup> |

| Power supply current in stopover mode, EVVRs on                              | I <sub>SSO</sub> CC     | _    | 0.7                         | 2.0                                       | mA   | power_mode=<br>stopover ;<br>voltage_range=<br>both <sup>4)</sup>   |

1)  $f_{\rm SYS}$  in MHz

2) The pad supply voltage pins ( $V_{\text{DDPB}}$ ) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers input stages are switched. In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to 3 + 0.6 x  $f_{\text{SYS}}$ .

3) Please consider the additional conditions described in section "Active Mode Power Supply Current".

4) The pad supply voltage has only a minor influence on this parameter.

### Active Mode Power Supply Current

The actual power supply current in active mode not only depends on the system frequency but also on the configuration of the XE164xN's subsystem.

Besides the power consumed by the device logic the power supply pins also provide the current that flows through the pin output drivers.

A small current is consumed because the drivers' input stages are switched.

The IO power domains can be supplied separately. Power domain A ( $V_{\rm DDPA}$ ) supplies the A/D converters and Port 6. Power domain B ( $V_{\rm DDPB}$ ) supplies the on-chip EVVRs and all other ports.

During operation domain A draws a maximum current of 1.5 mA for each active A/D converter module from  $V_{\rm DDPA}$ .

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to 3 +  $0.6 \times f_{SYS}$  mA.

### 4.5 System Parameters

The following parameters specify several aspects which are important when integrating the XE164xN into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                  |                                         | Values          | 6                                       | Unit | Note /<br>Test Condition                 |

|-----------------------------------------------------------------------|-------------------------|-----------------------------------------|-----------------|-----------------------------------------|------|------------------------------------------|

|                                                                       |                         | Min.                                    | Тур.            | Max.                                    |      |                                          |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC    | -1                                      | -               | 1                                       | %    | $\Delta T_{\rm J} \le 10^{\circ}{\rm C}$ |

| Internal clock source frequency                                       | $f_{\rm INT}{\rm CC}$   | 4.8                                     | 5.0             | 5.2                                     | MHz  |                                          |

| Wakeup clock source                                                   | $f_{\rm WU}$ CC         | 400                                     | -               | 700                                     | kHz  | FREQSEL= 00                              |

| frequency <sup>2)</sup>                                               |                         | 210                                     | -               | 390                                     | kHz  | FREQSEL= 01                              |

|                                                                       |                         | 140                                     | -               | 260                                     | kHz  | FREQSEL= 10                              |

|                                                                       |                         | 110                                     | -               | 200                                     | kHz  | FREQSEL= 11                              |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC     | 1.5                                     | 2.0             | 2.4                                     | ms   | ∫ <sub>WU</sub> = 500 kHz                |

| Startup time from stopover<br>mode with code execution<br>from PSRAM  | t <sub>SSO</sub> CC     | 11 /<br>f <sub>WU</sub> <sup>3)</sup>   | -               | 12 /<br>f <sub>WU</sub> <sup>3)</sup>   | μS   |                                          |

| Core voltage (PVC) supervision level                                  | $V_{\rm PVC}  {\rm CC}$ | V <sub>LV</sub> -<br>0.03               | $V_{\rm LV}$    | V <sub>LV</sub> +<br>0.07 <sup>4)</sup> | V    | 5)                                       |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC  | V <sub>LV</sub> -<br>0.10 <sup>6)</sup> | V <sub>LV</sub> | V <sub>LV</sub> +<br>0.15               | V    | voltage_range=<br>lower <sup>5)</sup>    |

|                                                                       |                         | V <sub>LV</sub> -<br>0.15               | V <sub>LV</sub> | V <sub>LV</sub> +<br>0.15               | V    | voltage_range=<br>upper <sup>5)</sup>    |

|                                                                       |                         | V <sub>LV</sub> -<br>0.30               | $V_{\rm LV}$    | V <sub>LV</sub> + 0.30                  | V    | $V_{\rm LV}$ = 5.5 V <sup>5)</sup>       |

### Table 21 Various System Parameters

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

### **Direct Drive**

When direct drive operation is selected (SYSCON0.CLKSEL =  $11_B$ ), the system clock is derived directly from the input clock signal CLKIN1:

$f_{SYS} = f_{IN}$ .

The frequency of  $f_{SYS}$  is the same as the frequency of  $f_{IN}$ . In this case the high and low times of  $f_{SYS}$  are determined by the duty cycle of the input clock  $f_{IN}$ .

Selecting Bypass Operation from the XTAL1<sup>1)</sup> input and using a divider factor of 1 results in a similar configuration.

### Prescaler Operation

When prescaler operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $1_B$ ), the system clock is derived either from the crystal oscillator (input clock signal XTAL1) or from the internal clock source through the output prescaler K1 (= K1DIV+1):

$f_{\text{SYS}} = f_{\text{OSC}} / \text{K1}.$

If a divider factor of 1 is selected, the frequency of  $f_{\rm SYS}$  equals the frequency of  $f_{\rm OSC}$ . In this case the high and low times of  $f_{\rm SYS}$  are determined by the duty cycle of the input clock  $f_{\rm OSC}$  (external or internal).

The lowest system clock frequency results from selecting the maximum value for the divider factor K1:

$f_{\rm SYS} = f_{\rm OSC} / 1024.$

# 4.7.2.1 Phase Locked Loop (PLL)

When PLL operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $0_B$ ), the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor **F** ( $f_{SYS} = f_{IN} \times F$ ).

**F** is calculated from the input divider P (= PDIV+1), the multiplication factor N (= NDIV+1), and the output divider K2 (= K2DIV+1):

$(F = N / (P \times K2)).$

The input clock can be derived either from an external source at XTAL1 or from the onchip clock source.

The PLL circuit synchronizes the system clock to the input clock. This synchronization is performed smoothly so that the system clock frequency does not change abruptly.

Adjustment to the input clock continuously changes the frequency of  $f_{\text{SYS}}$  so that it is locked to  $f_{\text{IN}}$ . The slight variation causes a jitter of  $f_{\text{SYS}}$  which in turn affects the duration of individual TCSs.

<sup>1)</sup> Voltages on XTAL1 must comply to the core supply voltage  $V_{\text{DDIM}}$ .

**Electrical Parameters**

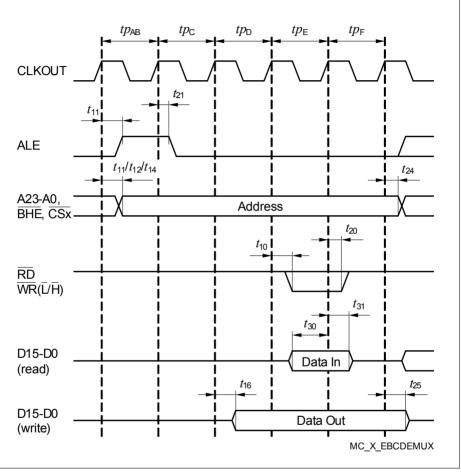

Figure 24 Demultiplexed Bus Cycle

# 4.7.5.1 Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum

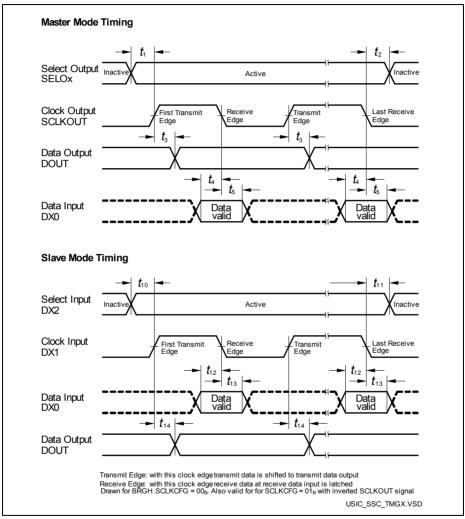

### Table 34 USIC SSC Master Mode Timing for Lower Voltage Range

| Parameter                                                               | Symbol            |                                        | Values | ;    | Unit | Note /<br>Test Condition |

|-------------------------------------------------------------------------|-------------------|----------------------------------------|--------|------|------|--------------------------|

|                                                                         |                   | Min.                                   | Тур.   | Max. |      |                          |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC | t <sub>SYS</sub> -<br>10 <sup>1)</sup> | -      | -    | ns   |                          |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC | t <sub>SYS</sub> -<br>9 <sup>1)</sup>  | -      | -    | ns   |                          |

| Data output DOUT valid<br>time                                          | t <sub>3</sub> CC | -7                                     | -      | 11   | ns   |                          |

| Receive data input setup time to SCLKOUT receive edge                   | t <sub>4</sub> SR | 40                                     | -      | -    | ns   |                          |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge                | t <sub>5</sub> SR | -5                                     | -      | -    | ns   |                          |

1)  $t_{SYS} = 1 / f_{SYS}$

**Table 35** is valid under the following conditions:  $C_L = 20 \text{ pF}$ ; *SSC*= slave ; voltage\_range= upper

### Table 35 USIC SSC Slave Mode Timing for Upper Voltage Range

|                                                                                   |                           |      | -      | -    | -    |                |

|-----------------------------------------------------------------------------------|---------------------------|------|--------|------|------|----------------|

| Parameter                                                                         | Symbol                    |      | Values |      | Unit | Note /         |

|                                                                                   |                           | Min. | Тур.   | Max. |      | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7    | -      | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7    | -      | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7    | -      | -    | ns   |                |

### **Electrical Parameters**

Figure 26 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.