Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 18K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 11x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xe164gn-16f80l-aa |

16-Bit

**Architecture**

XE164FN, XE164GN, XE164HN, XE164KN

16-Bit Single-Chip Real Time Signal Controller XE166 Family / Value Line

Data Sheet V1.4 2013-02

Microcontrollers

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2                                                                                                                           | Summary of Features  Device Types  Definition of Feature Variants                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                                           | General Device Information Pin Configuration and Definition Identification Registers                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                                                           |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19 | Functional Description  Memory Subsystem and Organization External Bus Controller Central Processing Unit (CPU) Memory Protection Unit (MPU) Memory Checker Module (MCHK) Interrupt System On-Chip Debug Support (OCDS) Capture/Compare Unit (CC2) Capture/Compare Units CCU6x General Purpose Timer (GPT12E) Unit Real Time Clock A/D Converters Universal Serial Interface Channel Modules (USIC) MultiCAN Module System Timer Watchdog Timer Clock Generation Parallel Ports Instruction Set Summary | 38<br>42<br>43<br>45<br>46<br>47<br>48<br>51<br>53<br>57<br>59<br>60<br>62<br>63<br>64<br>65 |

| 4.1<br>4.1.1<br>4.2<br>4.2.1<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4<br>4.5<br>4.6<br>4.7                                                              | Electrical Parameters General Parameters Operating Conditions Voltage Range definitions Parameter Interpretation DC Parameters DC Parameters for Upper Voltage Area DC Parameters for Lower Voltage Area Power Consumption Analog/Digital Converter Parameters System Parameters Flash Memory Parameters AC Parameters                                                                                                                                                                                  | 69<br>70<br>72<br>73<br>75<br>77<br>79<br>83<br>87<br>90                                     |

#### **General Device Information**

Table 5

Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Type | Function                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----|-------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 57  | P2.9              | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                 |  |  |  |  |  |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                             |  |  |  |  |  |

|     | TxDC1             | O2     | St/B | CAN Node 1 Transmit Data Output                                                                                                                                                                                                                                               |  |  |  |  |  |

|     | CC2_CC22          | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                     |  |  |  |  |  |

|     | A22               | ОН     | St/B | External Bus Interface Address Line 22                                                                                                                                                                                                                                        |  |  |  |  |  |

|     | CLKIN1            | I      | St/B | Clock Signal Input 1                                                                                                                                                                                                                                                          |  |  |  |  |  |

|     | TCK_A             | IH     | St/B | DAP0/JTAG Clock Input  If JTAG pos. A is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it.  If DAP pos. 0 is selected during start-up, an internal pull-down device will hold this pin low when nothing is driving it. |  |  |  |  |  |

| 58  | P0.2              | O0 / I | St/B | Bit 2 of Port 0, General Purpose Input/Output                                                                                                                                                                                                                                 |  |  |  |  |  |

|     | U1C0_SCLK<br>OUT  | 01     | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                                                                                                                            |  |  |  |  |  |

|     | TxDC0             | O2     | St/B | CAN Node 0 Transmit Data Output                                                                                                                                                                                                                                               |  |  |  |  |  |

|     | CCU61_CC6         | О3     | St/B | CCU61 Channel 2 Output                                                                                                                                                                                                                                                        |  |  |  |  |  |

|     | A2                | ОН     | St/B | External Bus Interface Address Line 2                                                                                                                                                                                                                                         |  |  |  |  |  |

|     | U1C0_DX1B         | I      | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                             |  |  |  |  |  |

|     | CCU61_CC6<br>2INA | I      | St/B | CCU61 Channel 2 Input                                                                                                                                                                                                                                                         |  |  |  |  |  |

#### **General Device Information**

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.      | Type | Function                                       |

|-----|-------------------|------------|------|------------------------------------------------|

| 59  | P10.0             | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |

|     | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |

|     | CCU60_CC6         | O2         | St/B | CCU60 Channel 0 Output                         |

|     | AD0               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |

|     | CCU60_CC6<br>0INA | I          | St/B | CCU60 Channel 0 Input                          |

|     | ESR1_2            | I          | St/B | ESR1 Trigger Input 2                           |

|     | U0C0_DX0A         | I          | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U0C1_DX0A         | I          | St/B | USIC0 Channel 1 Shift Data Input               |

| 60  | P10.1             | O0 / I     | St/B | Bit 1 of Port 10, General Purpose Input/Output |

|     | U0C0_DOUT         | 01         | St/B | USIC0 Channel 0 Shift Data Output              |

|     | CCU60_CC6         | O2         | St/B | CCU60 Channel 1 Output                         |

|     | AD1               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 1     |

|     | CCU60_CC6<br>1INA | Ι          | St/B | CCU60 Channel 1 Input                          |

|     | U0C0_DX1A         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |

|     | U0C0_DX0B         | I          | St/B | USIC0 Channel 0 Shift Data Input               |

| 61  | P0.3              | O0 / I     | St/B | Bit 3 of Port 0, General Purpose Input/Output  |

|     | U1C0_SELO<br>0    | 01         | St/B | USIC1 Channel 0 Select/Control 0 Output        |

|     | U1C1_SELO<br>1    | O2         | St/B | USIC1 Channel 1 Select/Control 1 Output        |

|     | CCU61_COU<br>T60  | О3         | St/B | CCU61 Channel 0 Output                         |

|     | A3                | ОН         | St/B | External Bus Interface Address Line 3          |

|     | U1C0_DX2A         | I          | St/B | USIC1 Channel 0 Shift Control Input            |

|     | RxDC0B            | I          | St/B | CAN Node 0 Receive Data Input                  |

### **Functional Description**

# 3.1 Memory Subsystem and Organization

The memory space of the XE164xN is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

Table 7 XE164xN Memory Map 1)

| Address Area             | Start Loc.           | End Loc.             | Area Size <sup>2)</sup>  | Notes               |

|--------------------------|----------------------|----------------------|--------------------------|---------------------|

| IMB register space       | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes                |                     |

| Reserved                 | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | < 1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM      | E8'4000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 496 Kbytes               | Mirrors EPSRAM      |

| Emulated PSRAM           | E8'0000 <sub>H</sub> | E8'3FFF <sub>H</sub> | up to<br>16 Kbytes       | With Flash timing   |

| Reserved for PSRAM       | E0'4000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 496 Kbytes               | Mirrors PSRAM       |

| PSRAM                    | E0,0000 <sup>H</sup> | E0'3FFF <sub>H</sub> | up to<br>16 Kbytes       | Program SRAM        |

| Reserved for Flash       | C5'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | 1,728 Kbytes             |                     |

| Flash 1                  | C4'0000 <sub>H</sub> | C4'FFFF <sub>H</sub> | 64 Kbytes                |                     |

| Flash 0                  | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes <sup>3)</sup> | Minus res. seg.     |

| External memory area     | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                 |                     |

| External IO area4)       | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | 1,984 Kbytes             |                     |

| Reserved                 | 20'BC00 <sub>H</sub> | 20'FFFF <sub>H</sub> | 17 Kbytes                |                     |

| USIC0–2 alternate regs.  | 20'B000 <sub>H</sub> | 20'BBFF <sub>H</sub> | 3 Kbytes                 | Accessed via EBC    |

| MultiCAN alternate regs. | 20'8000 <sub>H</sub> | 20'AFFF <sub>H</sub> | 12 Kbytes                | Accessed via EBC    |

| Reserved                 | 20'5800 <sub>H</sub> | 20'7FFF <sub>H</sub> | 10 Kbytes                |                     |

| USIC0–2 registers        | 20'4000 <sub>H</sub> | 20'57FF <sub>H</sub> | 6 Kbytes                 | Accessed via EBC    |

| Reserved                 | 20'6800 <sub>H</sub> | 20'7FFF <sub>H</sub> | 6 Kbytes                 |                     |

| MultiCAN registers       | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes                | Accessed via EBC    |

| External memory area     | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | 1984 Kbytes              |                     |

| SFR area                 | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbytes               |                     |

| Dualport RAM (DPRAM)     | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                 |                     |

| Reserved for DPRAM       | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbytes                 |                     |

| ESFR area                | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbytes               |                     |

| XSFR area                | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                 |                     |

| Data SRAM (DSRAM)        | 00'A000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 16 Kbytes                |                     |

#### **Functional Description**

## 3.8 Capture/Compare Unit (CC2)

The CAPCOM unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, external count inputs allow event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

Table 8 Compare Modes

| <b>Compare Modes</b> | Function                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------|

| Mode 0               | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1               | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

### **Functional Description**

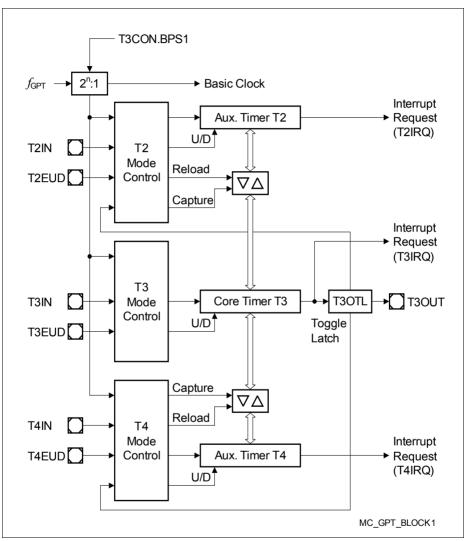

Figure 8 Block Diagram of GPT1

**Functional Description**

#### 3.12 A/D Converters

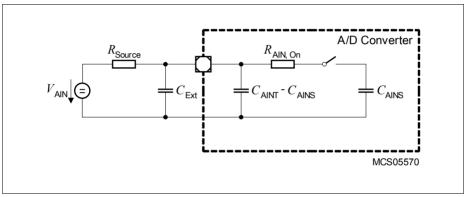

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 11 + 5 multiplexed input channels and a sample and hold circuit have been integrated on-chip. 4 inputs can be converted by both A/D converters. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XE164xN support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

### **Functional Description**

#### 3.18 Parallel Ports

The XE164xN provides up to 76 I/O lines which are organized into 7 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in **Table 9**.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

Table 9 Summary of the XE164xN's Ports

| Port | Width | I/O | Connected Modules                                                            |

|------|-------|-----|------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0), CCU6, USIC, CAN                                                  |

| P1   | 8     | I/O | EBC (A15A8), CCU6, USIC                                                      |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13), CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P4   | 4     | I/O | EBC (CS3CS0), CC2, CAN, GPT12E, USIC                                         |

| P5   | 11    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                   |

| P6   | 3     | I/O | ADC, CAN, GPT12E                                                             |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                  |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN                 |

| P15  | 5     | I   | Analog Inputs, GPT12E                                                        |

#### **Electrical Parameters**

- 7) An overload current  $(I_{\text{OV}})$  through a pin injects a certain error current  $(I_{\text{INJ}})$  into the adjacent pins. This error current adds to the respective pins leakage current  $(I_{\text{OZ}})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{\text{OV}}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{\text{TOT}}| = |I_{\text{OZ}}| + (|I_{\text{OV}}| K_{\text{OV}})$ . The additional error current may distort the input voltage on analog inputs.

- 8) Value is controlled by on-chip regulator

### 4.2 Voltage Range definitions

The XE164xN timing depends on the supply voltage. If such a dependency exists the timing values are given for 2 voltage areas commonly used. The voltage areas are defined in the following tables.

Table 13 Upper Voltage Range Definition

| Parameter                                                 | Symbol      |      | Values |      | Unit | Note /         |

|-----------------------------------------------------------|-------------|------|--------|------|------|----------------|

|                                                           |             | Min. | Тур.   | Max. |      | Test Condition |

| Digital supply voltage for IO pads and voltage regulators | $V_{DDP}SR$ | 4.5  | 5      | 5.5  | V    |                |

Table 14 Lower Voltage Range Definition

| Parameter                                                 | Symbol      | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------|-------------|--------|------|------|------|----------------|

|                                                           |             | Min.   | Тур. | Max. |      | Test Condition |

| Digital supply voltage for IO pads and voltage regulators | $V_{DDP}SR$ | 3.0    | 3.3  | 4.5  | V    |                |

## 4.2.1 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XE164xN and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

#### CC (Controller Characteristics):

The logic of the XE164xN provides signals with the specified characteristics.

#### **SR** (System Requirement):

The external system must provide signals with the specified characteristics to the XE164xN.

#### **Electrical Parameters**

## 4.3.1 DC Parameters for Upper Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

**Table 15** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}} \text{typ. 5 V}$ ;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

Table 15 DC Characteristics for Upper Voltage Range

| Parameter                                                                                   | Symbol                   |                                  | Values |                                  | Unit | Note /                                                                                                                                                   |

|---------------------------------------------------------------------------------------------|--------------------------|----------------------------------|--------|----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             |                          | Min. Typ.                        |        | Max.                             |      | Test Condition                                                                                                                                           |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. <sup>1)</sup> | $C_{IO}CC$               | _                                | _      | 10                               | pF   | not subject to production test                                                                                                                           |

| Input Hysteresis <sup>2)</sup>                                                              | HYS CC                   | $V_{\rm DDP}$                    | _      | -                                | V    | R <sub>S</sub> = 0 Ohm                                                                                                                                   |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                        | I <sub>OZ1</sub>  <br>CC | _                                | 10     | 200                              | nA   | $\begin{array}{c} V_{\rm IN} \!\!> V_{\rm SS} \; ; \\ V_{\rm IN} \!\!< V_{\rm DDP} \end{array} \label{eq:VIN}$                                           |

| Absolute input leakage current for all other pins. To be doubled for double                 | I <sub>OZ2</sub>  <br>CC | _                                | 0.2    | 5                                | μΑ   | $T_{\rm J} \le$ 110 °C;<br>$V_{\rm IN} > V_{\rm SS}$ ;<br>$V_{\rm IN} < V_{\rm DDP}$                                                                     |

| bond pins. <sup>3)1)4)</sup>                                                                |                          | _                                | 0.2    | 15                               | μА   | $T_{\rm J} \le$ 150 °C;<br>$V_{\rm IN} > V_{\rm SS}$ ;<br>$V_{\rm IN} < V_{\rm DDP}$                                                                     |

| Pull Level Force Current <sup>5)</sup>                                                      | $ I_{\rm PLF} $ SR       | 250                              | _      | _                                | μА   | $ \begin{aligned} V_{\text{IN}} &\geq V_{\text{IHmin}}(pull\\ down\_enabled);\\ V_{\text{IN}} &\leq V_{\text{ILmax}}(pull\\ up\_enabled) \end{aligned} $ |

| Pull Level Keep Current <sup>6)</sup>                                                       | I <sub>PLK</sub>  <br>SR | -                                | _      | 30                               | μА   | $\begin{array}{c} V_{\rm IN} \!\! \geq V_{\rm IHmin}(pull\\ up\_enabled);\\ V_{\rm IN} \!\! \leq V_{\rm ILmax}(pull\\ down\_enabled) \end{array}$        |

| Input high voltage (all except XTAL1)                                                       | $V_{IH}SR$               | $0.7 \text{ x}$ $V_{\text{DDP}}$ | _      | V <sub>DDP</sub> + 0.3           | V    |                                                                                                                                                          |

| Input low voltage (all except XTAL1)                                                        | $V_{IL}SR$               | -0.3                             | _      | $0.3 \text{ x}$ $V_{\text{DDP}}$ | V    |                                                                                                                                                          |

#### **Electrical Parameters**

- 4) The broken wire detection delay against V<sub>AREF</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 10 μs. This function is influenced by leakage current, in particular at high temperature. Result above 80% (332<sub>H</sub>)

- 5) TUE is tested at V<sub>AREF</sub> = V<sub>DDPA</sub> = 5.0 V, V<sub>AGND</sub> = 0 V. It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see I<sub>OV</sub> specification) does not exceed 10 mA, and if V<sub>AREF</sub> and V<sub>AGND</sub> remain stable during the measurement time.

- 6)  $V_{\text{AIN}}$  may exceed  $V_{\text{AGND}}$  or  $V_{\text{AREF}}$  up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

Figure 16 Equivalent Circuitry for Analog Inputs

#### **Electrical Parameters**

### 4.6 Flash Memory Parameters

The XE164xN is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XE164xN's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

Table 24 Flash Parameters

| Parameter                                                  | Symbol                        |      | Values          | s               | Unit   | Note /                                                                         |

|------------------------------------------------------------|-------------------------------|------|-----------------|-----------------|--------|--------------------------------------------------------------------------------|

|                                                            |                               | Min. | Тур.            | Max.            |        | Test Condition                                                                 |

| Parallel Flash module                                      | $N_{PP}SR$                    | -    | _               | 2 <sup>1)</sup> |        | $N_{\text{FL\_RD}} \le 1$                                                      |

| program/erase limit<br>depending on Flash read<br>activity |                               | _    | _               | 1 <sup>2)</sup> |        | <i>N</i> <sub>FL_RD</sub> > 1                                                  |

| Flash erase endurance for security pages                   | $N_{\mathrm{SEC}}\mathrm{SR}$ | 10   | -               | _               | cycles | t <sub>RET</sub> ≥ 20 years                                                    |

| Flash wait states <sup>3)</sup>                            | $N_{\rm WSFLAS}$              | 1    | _               | _               |        | f <sub>SYS</sub> ≤ 8 MHz                                                       |

|                                                            | <sub>H</sub> SR               | 2    | _               | _               |        | f <sub>SYS</sub> ≤ 13 MHz                                                      |

|                                                            |                               | 3    | _               | _               |        | $f_{\rm SYS} \le$ 17 MHz                                                       |

|                                                            |                               | 4    | _               | _               |        | $f_{\rm SYS}$ > 17 MHz                                                         |

| Erase time per sector/page                                 | $t_{ER}CC$                    | _    | 7 <sup>4)</sup> | 8.0             | ms     |                                                                                |

| Programming time per page                                  | $t_{PR}CC$                    | _    | 3 <sup>4)</sup> | 3.5             | ms     |                                                                                |

| Data retention time                                        | $t_{RET}CC$                   | 20   | -               | _               | years  | $N_{\rm ER} \le$ 1,000 cycl es                                                 |

| Drain disturb limit                                        | $N_{\rm DD}{\rm SR}$          | 32   | _               | _               | cycles |                                                                                |

| Number of erase cycles                                     | $N_{ER}SR$                    | _    | _               | 15.000          | cycles | $t_{\rm RET} \ge 5$ years;<br>Valid for Flash<br>module 1 (up to<br>64 kbytes) |

|                                                            |                               | -    | _               | 1.000           | cycles | $t_{RET} \ge 20 \; years$                                                      |

The unused Flash module(s) can be erased/programmed while code is executed and/or data is read from only

one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be

erased/programmed.

#### **Electrical Parameters**

## 4.7.5 External Bus Timing

The following parameters specify the behavior of the XE164xN bus interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

Table 29 Parameters

| Parameter                       | Symbol            | Values |                      |      | Unit | Note /         |

|---------------------------------|-------------------|--------|----------------------|------|------|----------------|

|                                 |                   | Min.   | Тур.                 | Max. |      | Test Condition |

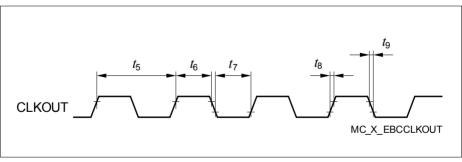

| CLKOUT Cycle Time <sup>1)</sup> | t <sub>5</sub> CC | -      | 1 / f <sub>SYS</sub> | -    | ns   |                |

| CLKOUT high time                | t <sub>6</sub> CC | 3      | _                    | -    |      |                |

| CLKOUT low time                 | t <sub>7</sub> CC | 3      | _                    | -    |      |                |

| CLKOUT rise time                | t <sub>8</sub> CC | -      | _                    | 3    | ns   |                |

| CLKOUT fall time                | t <sub>9</sub> CC | -      | _                    | 3    |      |                |

The CLKOUT cycle time is influenced by PLL jitter. For longer periods the relative deviation decreases (see PLL deviation formula).

Figure 22 CLKOUT Signal Timing

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{\rm SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

### **Electrical Parameters**

### Variable Memory Cycles

External bus cycles of the XE164xN are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

Table 30 Programmable Bus Cycle Phases (see timing diagrams)

| Bus Cycle Phase                                                                                                                | Parameter | Valid Values | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 2 TCS) can be extended by 0 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                            | tpC       | 0 3          | TCS  |

| Write Data setup/MUX Tristate phase                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                  | tpF       | 0 3          | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply.

**Table 31** is valid under the following conditions:  $C_L$ = 20 pF; voltage\_range= upper; voltage\_range= upper

Table 31 External Bus Timing for Upper Voltage Range

| Parameter                                                                                     | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                               |                           | Min.   | Тур. | Max. |      | Test Condition |

| Output valid delay for $\overline{\text{RD}}$ , $\overline{\text{WR}}(\overline{\text{L/H}})$ | t <sub>10</sub> CC        | _      | 7    | 13   | ns   |                |

| Output valid delay for BHE, ALE                                                               | <i>t</i> <sub>11</sub> CC | _      | 7    | 14   | ns   |                |

| Address output valid delay for A23 A0                                                         | <i>t</i> <sub>12</sub> CC | _      | 8    | 14   | ns   |                |

#### **Electrical Parameters**

Table 31 External Bus Timing for Upper Voltage Range (cont'd)

| Parameter                                                                                   | Symbol                    |      | Values | Values Uni |    | t Note /       |

|---------------------------------------------------------------------------------------------|---------------------------|------|--------|------------|----|----------------|

|                                                                                             |                           | Min. | Тур.   | Max.       |    | Test Condition |

| Address output valid delay for AD15 AD0 (MUX mode)                                          | t <sub>13</sub> CC        | -    | 8      | 15         | ns |                |

| Output valid delay for CS                                                                   | t <sub>14</sub> CC        | _    | 7      | 13         | ns |                |

| Data output valid delay for AD15 AD0 (write data, MUX mode)                                 | t <sub>15</sub> CC        | -    | 8      | 15         | ns |                |

| Data output valid delay for D15 D0 (write data, DEMUX mode)                                 | t <sub>16</sub> CC        | -    | 8      | 15         | ns |                |

| Output hold time for $\overline{\text{RD}}$ , $\overline{\text{WR}}(\overline{\text{L/H}})$ | t <sub>20</sub> CC        | -2   | 6      | 8          | ns |                |

| Output hold time for BHE, ALE                                                               | t <sub>21</sub> CC        | -2   | 6      | 10         | ns |                |

| Address output hold time for AD15 AD0                                                       | <i>t</i> <sub>23</sub> CC | -3   | 6      | 8          | ns |                |

| Output hold time for CS                                                                     | t <sub>24</sub> CC        | -3   | 6      | 11         | ns |                |

| Data output hold time for D15 D0 and AD15 AD0                                               | t <sub>25</sub> CC        | -3   | 6      | 8          | ns |                |

| Input setup time for<br>READY, D15 D0, AD15<br>AD0                                          | t <sub>30</sub> SR        | 25   | 15     | _          | ns |                |

| Input hold time READY,<br>D15 D0, AD15 AD0 <sup>1)</sup>                                    | <i>t</i> <sub>31</sub> SR | 0    | -7     | _          | ns |                |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge

of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can

change after the rising edge of RD.

**Table 32** is valid under the following conditions:  $C_L$ = 20 pF; voltage\_range= lower; voltage\_range= lower

#### **Electrical Parameters**

## 4.7.6 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 33** is valid under the following conditions:  $C_L$ = 20 pF; SSC= master; voltage range= upper

Table 33 USIC SSC Master Mode Timing for Upper Voltage Range

| Parameter                                                         | Symbol            | Values                                    |      |      | Unit | Note /         |

|-------------------------------------------------------------------|-------------------|-------------------------------------------|------|------|------|----------------|

|                                                                   |                   | Min.                                      | Тур. | Max. |      | Test Condition |

| Slave select output SELO active to first SCLKOUT transmit edge    | t <sub>1</sub> CC | <i>t</i> <sub>SYS</sub> - 8 <sup>1)</sup> | _    | _    | ns   |                |

| Slave select output SELO inactive after last SCLKOUT receive edge | t <sub>2</sub> CC | <i>t</i> <sub>SYS</sub> - 6 <sup>1)</sup> | _    | _    | ns   |                |

| Data output DOUT valid time                                       | t <sub>3</sub> CC | -6                                        | _    | 9    | ns   |                |

| Receive data input setup time to SCLKOUT receive edge             | t <sub>4</sub> SR | 31                                        | -    | -    | ns   |                |

| Data input DX0 hold time from SCLKOUT receive edge                | t <sub>5</sub> SR | -4                                        | _    | -    | ns   |                |

<sup>1)</sup>  $t_{SYS} = 1 / f_{SYS}$

**Table 34** is valid under the following conditions:  $C_L$ = 20 pF; SSC= master; voltage\_range= lower

Data Sheet 112 V1.4, 2013-02

#### **Electrical Parameters**

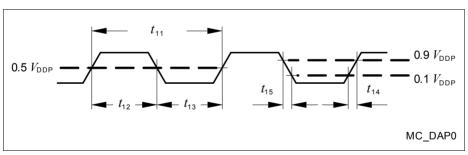

### 4.7.7 Debug Interface Timing

The debugger can communicate with the XE164xN either via the 2-pin DAP interface or via the standard JTAG interface.

### Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 37** is valid under the following conditions:  $C_1 = 20 \text{ pF}$ ; voltage range= upper

Table 37 DAP Interface Timing for Upper Voltage Range

| Parameter                                      | Symbol             |      | Values |      |    | Note /         |

|------------------------------------------------|--------------------|------|--------|------|----|----------------|

|                                                |                    | Min. | Тур.   | Max. |    | Test Condition |

| DAP0 clock period <sup>1)</sup>                | t <sub>11</sub> SR | 25   | _      | _    | ns |                |

| DAP0 high time                                 | t <sub>12</sub> SR | 8    | _      | _    | ns |                |

| DAP0 low time <sup>1)</sup>                    | t <sub>13</sub> SR | 8    | _      | _    | ns |                |

| DAP0 clock rise time                           | t <sub>14</sub> SR | -    | _      | 4    | ns |                |

| DAP0 clock fall time                           | t <sub>15</sub> SR | -    | _      | 4    | ns |                |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR | 6    | -      | _    | ns |                |

| DAP1 hold after DAP0 rising edge               | t <sub>17</sub> SR | 6    | -      | _    | ns |                |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC | 17   | 20     | -    | ns |                |

<sup>1)</sup> See the DAP chapter for clock rate restrictions in the Active::IDLE protocol state.

**Table 38** is valid under the following conditions:  $C_1 = 20 \text{ pF}$ ; voltage\_range= lower

Data Sheet 116 V1.4, 2013-02

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

#### **Electrical Parameters**

Table 38 DAP Interface Timing for Lower Voltage Range

| Parameter                                      | Symbol             | Values |      |      | Unit | Note /                |

|------------------------------------------------|--------------------|--------|------|------|------|-----------------------|

|                                                |                    | Min.   | Тур. | Max. |      | <b>Test Condition</b> |

| DAP0 clock period <sup>1)</sup>                | t <sub>11</sub> SR | 25     | _    | _    | ns   |                       |

| DAP0 high time                                 | t <sub>12</sub> SR | 8      | _    | _    | ns   |                       |

| DAP0 low time <sup>1)</sup>                    | t <sub>13</sub> SR | 8      | -    | _    | ns   |                       |

| DAP0 clock rise time                           | t <sub>14</sub> SR | -      | _    | 4    | ns   |                       |

| DAP0 clock fall time                           | t <sub>15</sub> SR | -      | _    | 4    | ns   |                       |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR | 6      | -    | _    | ns   |                       |

| DAP1 hold after DAP0 rising edge               | t <sub>17</sub> SR | 6      | -    | _    | ns   |                       |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC | 12     | 17   | -    | ns   |                       |

<sup>1)</sup> See the DAP chapter for clock rate restrictions in the Active::IDLE protocol state.

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 27 Test Clock Timing (DAP0)

Data Sheet 117 V1.4, 2013-02

### Package and Reliability

# 5.3 Quality Declarations

The operation lifetime of the XE164xN depends on the operating temperature. The life time decreases with increasing temperature as shown in **Table 43**.

Table 42 Quality Parameters

| Parameter                                                    | Symbol                 | Values |      |       | Unit | Note /                |  |

|--------------------------------------------------------------|------------------------|--------|------|-------|------|-----------------------|--|

|                                                              |                        | Min.   | Тур. | Max.  |      | Test Condition        |  |

| Operation lifetime                                           | $t_{\sf OP}$ CC        | _      | _    | 20    | а    | See Table 43          |  |

| ESD susceptibility<br>according to Human Body<br>Model (HBM) | V <sub>HBM</sub><br>SR | -      | -    | 2 000 | V    | EIA/JESD22-<br>A114-B |  |

| Moisture sensitivity level                                   | MSL CC                 | _      | _    | 3     | _    | JEDEC<br>J-STD-020C   |  |

Table 43 Lifetime dependency from Temperature

| Operating Time | Operating Temperature             |

|----------------|-----------------------------------|

| 20 a           | <i>T</i> <sub>J</sub> ≤ 110°C     |

| 95 500 h       | T <sub>J</sub> = 120°C            |

| 68 500 h       | $T_{J} = 125^{\circ}C$            |

| 49 500 h       | $T_{\rm J} = 130 {\rm ^{\circ}C}$ |

| 26 400 h       | $T_{J} = 140^{\circ}C$            |

| 14 500 h       | $T_{\rm J} = 150 {\rm ^{\circ}C}$ |

Data Sheet 125 V1.4, 2013-02