Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 18K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 11x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xe164kn-16f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Summary of Features**

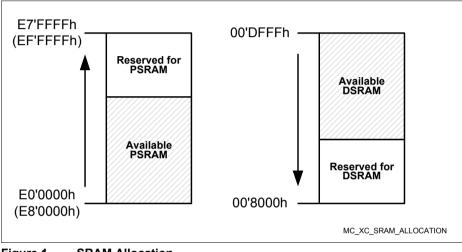

The XE164xN types are offered with several SRAM memory sizes. **Figure 1** shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

### **General Device Information**

## Key to Pin Definitions

Ctrl.: The output signal for a port pin is selected by bit field PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bit field PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc.

Output signal OH is controlled by hardware.

- **Type**: Indicates the pad type and its power supply domain (A, B, M, 1).

- St: Standard pad

- Sp: Special pad e.g. XTALx

- DP: Double pad can be used as standard or high speed pad

- In: Input only pad

- PS: Power supply pad

| Pin | Symbol | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TESTM  | I      | In/B | <b>Testmode Enable</b><br>Enables factory test modes, must be held HIGH for<br>normal operation (connect to $V_{\text{DDPB}}$ ).<br>An internal pull-up device will hold this pin high<br>when nothing is driving it.                                                                                                                                              |

| 4   | P7.2   | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                      |

|     | EMUX0  | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                        |

|     | TDI_C  | IH     | St/B | JTAG Test Data Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.                                                                                                                                                                                                           |

| 5   | TRST   | 1      | In/B | <b>Test-System Reset Input</b><br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XE164xN's debug system.<br>In this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pull-down device will hold this pin low<br>when nothing is driving it. |

Table 5 Pin Definitions and Functions

## XE164FN, XE164GN, XE164HN, XE164KN XE166 Family / Value Line

## **General Device Information**

| Table | e 5 Pin De       | finitior   | ns and | Functions (cont'd)                                                                                                                                                                                                                                                                                   |

|-------|------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   | Symbol           | Ctrl.      | Туре   | Function                                                                                                                                                                                                                                                                                             |

| 6     | P7.0             | O0 / I     | St/B   | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                        |

|       | T3OUT            | 01         | St/B   | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                  |

|       | T6OUT            | 02         | St/B   | GPT12E Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                  |

|       | TDO_A            | OH /<br>IH | St/B   | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 0 or 2 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it.                                                                                                                   |

|       | ESR2_1           | I          | St/B   | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                 |

| 7     | P7.3             | O0 / I     | St/B   | Bit 3 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                        |

|       | EMUX1            | 01         | St/B   | External Analog MUX Control Output 1 (ADC1)                                                                                                                                                                                                                                                          |

|       | U0C1_DOUT        | 02         | St/B   | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |

|       | U0C0_DOUT        | O3         | St/B   | USIC0 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                    |

|       | TMS_C            | IH         | St/B   | JTAG Test Mode Selection Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin low when<br>nothing is driving it.                                                                                                                                    |

|       | U0C1_DX0F        | I          | St/B   | USIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                     |

| 8     | P7.1             | O0 / I     | St/B   | Bit 1 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                        |

|       | EXTCLK           | 01         | St/B   | Programmable Clock Signal Output                                                                                                                                                                                                                                                                     |

|       | BRKIN_C          | I          | St/B   | OCDS Break Signal Input                                                                                                                                                                                                                                                                              |

| 9     | P7.4             | 00 / 1     | St/B   | Bit 4 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                        |

|       | EMUX2            | 01         | St/B   | External Analog MUX Control Output 2 (ADC1)                                                                                                                                                                                                                                                          |

|       | U0C1_DOUT        | 02         | St/B   | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |

|       | U0C1_SCLK<br>OUT | O3         | St/B   | USIC0 Channel 1 Shift Clock Output                                                                                                                                                                                                                                                                   |

|       | тск_с            | IH         | St/B   | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 2 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |

|       | U0C0_DX0D        | I          | St/B   | USIC0 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                     |

|       | U0C1_DX1E        | I          | St/B   | USIC0 Channel 1 Shift Clock Input                                                                                                                                                                                                                                                                    |

## XE164FN, XE164GN, XE164HN, XE164KN XE166 Family / Value Line

#### **General Device Information**

| Table | e 5 Pin De        | finitior   | ns and | Functions (cont'd)                                                                                                                                                                                                                                                                                   |

|-------|-------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   | Symbol            | Ctrl.      | Туре   | Function                                                                                                                                                                                                                                                                                             |

| 79    | P10.8             | O0 / I     | St/B   | Bit 8 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |

|       | U0C0_MCLK<br>OUT  | 01         | St/B   | USIC0 Channel 0 Master Clock Output                                                                                                                                                                                                                                                                  |

|       | U0C1_SELO<br>0    | O2         | St/B   | USIC0 Channel 1 Select/Control 0 Output                                                                                                                                                                                                                                                              |

|       | U2C1_DOUT         | O3         | St/B   | USIC2 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |

|       | AD8               | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 8                                                                                                                                                                                                                                                           |

|       | CCU60_CCP<br>OS1A | I          | St/B   | CCU60 Position Input 1                                                                                                                                                                                                                                                                               |

|       | U0C0_DX1C         | I          | St/B   | USIC0 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                    |

|       | BRKIN_B           | I          | St/B   | OCDS Break Signal Input                                                                                                                                                                                                                                                                              |

|       | T3EUDB            | 1          | St/B   | GPT12E Timer T3 External Up/Down Control Input                                                                                                                                                                                                                                                       |

| 80    | P10.9             | O0 / I     | St/B   | Bit 9 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |

|       | U0C0_SELO<br>4    | 01         | St/B   | USIC0 Channel 0 Select/Control 4 Output                                                                                                                                                                                                                                                              |

|       | U0C1_MCLK<br>OUT  | O2         | St/B   | USIC0 Channel 1 Master Clock Output                                                                                                                                                                                                                                                                  |

|       | AD9               | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 9                                                                                                                                                                                                                                                           |

|       | CCU60_CCP<br>OS2A | 1          | St/B   | CCU60 Position Input 2                                                                                                                                                                                                                                                                               |

|       | ТСК_В             | IH         | St/B   | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |

|       |                   | 1          | St/B   | GPT12E Timer T3 Count/Gate Input                                                                                                                                                                                                                                                                     |

## XE164FN, XE164GN, XE164HN, XE164KN XE166 Family / Value Line

## **General Device Information**

| Table 5Pin Definitions and Functions (cont'd) |                   |        |      |                                                                                                                                                                                     |  |  |  |  |

|-----------------------------------------------|-------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin                                           | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                            |  |  |  |  |

| 98                                            | ESR1              | O0 / I | St/B | <b>External Service Request 1</b><br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                             |  |  |  |  |

|                                               | RxDC0E            | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                       |  |  |  |  |

|                                               | U1C0_DX0F         | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                    |  |  |  |  |

|                                               | U1C0_DX2C         | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                 |  |  |  |  |

|                                               | U1C1_DX0C         | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                    |  |  |  |  |

|                                               | U1C1_DX2B         | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                 |  |  |  |  |

|                                               | U2C1_DX2C         | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                 |  |  |  |  |

| 99                                            | ESR0              | O0 / I | St/B | <b>External Service Request 0</b><br>After power-up, ESR0 operates as open-drain<br>bidirectional reset with a weak pull-up.                                                        |  |  |  |  |

|                                               | U1C0_DX0E         | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                    |  |  |  |  |

|                                               | U1C0_DX2B         | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                 |  |  |  |  |

| 10                                            | V <sub>DDIM</sub> | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                |  |  |  |  |

| 38,<br>64,<br>88                              | V <sub>DDI1</sub> | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All $V_{\text{DDI1}}$ pins must be connected to each other. |  |  |  |  |

| 14                                            | V <sub>DDPA</sub> | -      | PS/A | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent $V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.              |  |  |  |  |

|                                               |                   |        |      | Note: The A/D_Converters and ports P5, P6 and P15 are fed from supply voltage $V_{DDPA}$ .                                                                                          |  |  |  |  |

Up to 16 Kbytes of on-chip Data SRAM (DSRAM) are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

Note: The actual size of the DSRAM depends on the quoted device type.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XE166 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 7**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**The on-chip Flash memory** stores code, constant data, and control data. The 320 Kbytes of on-chip Flash memory consist of 1 module of 64 Kbytes (preferably for data storage) and 1 module of 256 Kbytes. Each module is organized in 4-Kbyte sectors. The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see Section 4.6.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

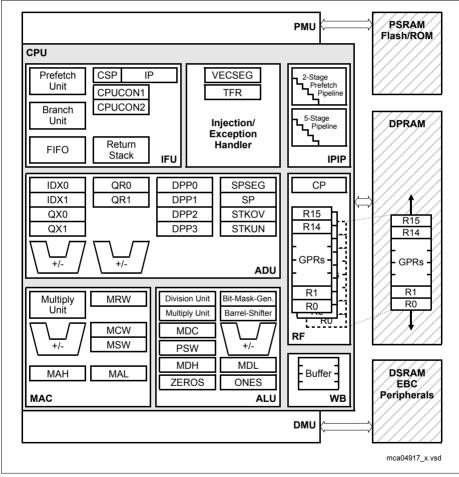

# 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

Figure 5 CPU Block Diagram

# 3.4 Memory Protection Unit (MPU)

The XE164xN's Memory Protection Unit (MPU) protects user-specified memory areas from unauthorized read, write, or instruction fetch accesses. The MPU can protect the whole address space including the peripheral area. This completes established mechanisms such as the register security mechanism or stack overrun/underrun detection.

Four Protection Levels support flexible system programming where operating system, low level drivers, and applications run on separate levels. Each protection level permits different access restrictions for instructions and/or data.

Every access is checked (if the MPU is enabled) and an access violating the permission rules will be marked as invalid and leads to a protection trap.

A set of protection registers for each protection level specifies the address ranges and the access permissions. Applications requiring more than 4 protection levels can dynamically re-program the protection registers.

## 3.5 Memory Checker Module (MCHK)

The XE164xN's Memory Checker Module calculates a checksum (fractional polynomial division) on a block of data, often called Cyclic Redundancy Code (CRC). It is based on a 32-bit linear feedback shift register and may, therefore, also be used to generate pseudo-random numbers.

The Memory Checker Module is a 16-bit parallel input signature compression circuitry which enables error detection within a block of data stored in memory, registers, or communicated e.g. via serial communication lines. It reduces the probability of error masking due to repeated error patterns by calculating the signature of blocks of data.

The polynomial used for operation is configurable, so most of the commonly used polynomials may be used. Also, the block size for generating a CRC result is configurable via a local counter. An interrupt may be generated if testing the current data block reveals an error.

An autonomous CRC compare circuitry is included to enable redundant error detection, e.g. to enable higher safety integrity levels.

The Memory Checker Module provides enhanced fault detection (beyond parity or ECC) for data and instructions in volatile and non volatile memories. This is especially important for the safety and reliability of embedded systems.

## XE164FN, XE164GN, XE164HN, XE164KN XE166 Family / Value Line

## **Functional Description**

## 3.18 Parallel Ports

The XE164xN provides up to 76 I/O lines which are organized into 7 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in Table 9.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |

|------|-------|-----|---------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0), CCU6, USIC, CAN                                                     |

| P1   | 8     | I/O | EBC (A15A8), CCU6, USIC                                                         |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P4   | 4     | I/O | EBC (CS3CS0), CC2, CAN, GPT12E, USIC                                            |

| P5   | 11    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |

| P6   | 3     | I/O | ADC, CAN, GPT12E                                                                |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN                    |

| P15  | 5     | I   | Analog Inputs, GPT12E                                                           |

### Table 9Summary of the XE164xN's Ports

## 4.1.1 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XE164xN. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

| Parameter                                                        | Symbol                 |      | Values                    | 5                         | Unit | Note /                                                       |

|------------------------------------------------------------------|------------------------|------|---------------------------|---------------------------|------|--------------------------------------------------------------|

|                                                                  |                        | Min. | Тур.                      | Max.                      |      | Test Condition                                               |

| Voltage Regulator Buffer<br>Capacitance for DMP_M                | $C_{\rm EVRM}$ SR      | 1.0  | -                         | 4.7                       | μF   | 1)                                                           |

| Voltage Regulator Buffer<br>Capacitance for DMP_1                | $C_{\rm EVR1}$ SR      | 0.47 | -                         | 2.2                       | μF   | 2)1)                                                         |

| External Load<br>Capacitance                                     | $C_{L}$ SR             | -    | 20 <sup>3)</sup>          | -                         | pF   | pin out<br>driver= default<br>4)                             |

| System frequency                                                 | $f_{\rm SYS}{\rm SR}$  | -    | -                         | 80                        | MHz  | 5)                                                           |

| Overload current for analog inputs <sup>6)</sup>                 | $I_{\rm OVA}{\rm SR}$  | -2   | -                         | 5                         | mA   | not subject to production test                               |

| Overload current for digital inputs <sup>6)</sup>                | $I_{\rm OVD}{\rm SR}$  | -5   | -                         | 5                         | mA   | not subject to production test                               |

| Overload current coupling factor for analog inputs <sup>7)</sup> | K <sub>OVA</sub><br>CC | -    | 2.5 x<br>10 <sup>-4</sup> | 1.5 x<br>10 <sup>-3</sup> | -    | I <sub>OV</sub> < 0 mA; not<br>subject to<br>production test |

|                                                                  |                        | _    | 1.0 x<br>10⁻ <sup>6</sup> | 1.0 x<br>10 <sup>-4</sup> | -    | I <sub>OV</sub> > 0 mA; not<br>subject to<br>production test |

### Table 12 Operating Conditions

## 4.3 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

The XE164xN can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XE164xN are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.7.4**.

## 4.3.1 DC Parameters for Upper Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

**Table 15** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}}$  typ. 5 V;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

| Parameter                                                                                   | Symbol                   |                            | Values |                           | Unit | Note /                                                                                                                                       |

|---------------------------------------------------------------------------------------------|--------------------------|----------------------------|--------|---------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             |                          | Min.                       | Тур.   | Max.                      |      | Test Condition                                                                                                                               |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. <sup>1)</sup> | C <sub>IO</sub> CC       | _                          | -      | 10                        | pF   | not subject to production test                                                                                                               |

| Input Hysteresis <sup>2)</sup>                                                              | HYS CC                   | 0.11 x<br>V <sub>DDP</sub> | -      | -                         | V    | R <sub>S</sub> = 0 Ohm                                                                                                                       |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                        | I <sub>oz1</sub>  <br>CC | -                          | 10     | 200                       | nA   | $V_{\rm IN}$ > $V_{\rm SS}$ ; $V_{\rm IN}$ < $V_{\rm DDP}$                                                                                   |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double           | I <sub>OZ2</sub>  <br>CC | -                          | 0.2    | 5                         | μA   | $T_{\rm J} \leq$ 110 °C;<br>$V_{\rm IN} > V_{\rm SS}$ ;<br>$V_{\rm IN} < V_{\rm DDP}$                                                        |

| bond pins. <sup>3)1)4)</sup>                                                                |                          | _                          | 0.2    | 15                        | μA   | $T_{ m J} \leq$ 150 °C;<br>$V_{ m IN} > V_{ m SS}$ ;<br>$V_{ m IN} < V_{ m DDP}$                                                             |

| Pull Level Force Current <sup>5)</sup>                                                      | $ I_{PLF} $ SR           | 250                        | -      | -                         | μA   | $V_{\text{IN}} \ge V_{\text{IHmin}}(pull down_enabled); V_{\text{IN}} \le V_{\text{ILmax}}(pull up_enabled)$                                 |

| Pull Level Keep Current <sup>6)</sup>                                                       | I <sub>PLK</sub>  <br>SR | _                          | -      | 30                        | μA   | $ \begin{array}{l} V_{\rm IN} \geq V_{\rm IHmin}(pull \\ up\_enabled); \\ V_{\rm IN} \leq V_{\rm ILmax}(pull \\ down\_enabled) \end{array} $ |

| Input high voltage (all except XTAL1)                                                       | V <sub>IH</sub> SR       | 0.7 x<br>V <sub>DDP</sub>  | -      | V <sub>DDP</sub> + 0.3    | V    |                                                                                                                                              |

| Input low voltage<br>(all except XTAL1)                                                     | $V_{\rm IL}{ m SR}$      | -0.3                       | -      | 0.3 x<br>V <sub>DDP</sub> | V    |                                                                                                                                              |

Table 15

DC Characteristics for Upper Voltage Range

### Table 19ADC Parameters (cont'd)

| Parameter                                               | Symbol               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Values | S                           | Unit | Note /         |

|---------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------|------|----------------|

|                                                         |                      | Min. Typ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | Max.                        |      | Test Condition |

| Broken wire detection delay against VAGND <sup>2)</sup> | t <sub>BWG</sub> CC  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -      | 50 <sup>3)</sup>            |      |                |

| Broken wire detection delay against VAREF <sup>2)</sup> | t <sub>BWR</sub> CC  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _      | 50 <sup>4)</sup>            |      |                |

| Conversion time for 8-bit result <sup>2)</sup>          | t <sub>c8</sub> CC   | $(11+S)$ $TC) \times t_{ADCI} + 2 \times t_{AD$ | _      | _                           |      |                |

| Conversion time for 10-bit result <sup>2)</sup>         | t <sub>c10</sub> CC  | $\frac{t_{SYS}}{(13+S)}$ $\frac{(13+S)}{TC} \times t_{ADCI} + 2 \times t_{SYS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _      | -                           |      |                |

| Total Unadjusted Error                                  | TUE <br>CC           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1      | 2                           | LSB  | 5)             |

| Wakeup time from analog powerdown, fast mode            | t <sub>WAF</sub> CC  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -      | 4                           | μS   |                |

| Wakeup time from analog powerdown, slow mode            | t <sub>WAS</sub> CC  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _      | 15                          | μS   |                |

| Analog reference ground                                 | $V_{AGND}$ SR        | V <sub>SS</sub> -<br>0.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | 1.5                         | V    |                |

| Analog input voltage range                              | $V_{\rm AIN}{ m SR}$ | $V_{AGND}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -      | V <sub>AREF</sub>           | V    | 6)             |

| Analog reference voltage                                | $V_{AREF}$ SR        | V <sub>AGND</sub><br>+ 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -      | V <sub>DDPA</sub><br>+ 0.05 | V    |                |