Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 320KB (320K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 11x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xe164kn-40f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

VE464vN Data Chast

| Revision F | Jata Sheet<br>listory: V1.4 2013-02                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous V | ersions:                                                                                                                                          |

| V1.3, 2011 | -07                                                                                                                                               |

| V1.2, 2010 | -04                                                                                                                                               |

| V1.1, 2009 |                                                                                                                                                   |

| V1.0, 2009 | -03 Preliminary                                                                                                                                   |

| Page       | Subjects (major changes since last revision)                                                                                                      |

| 36         | Added AB step marking.                                                                                                                            |

| 87         | Errata SWD_X.P002 implemented: $V_{\rm SWD}$ tolerance boundaries for 5.5 V are changed.                                                          |

| 89         | Clarified "Coding of bit fields LEVxV" descriptions. Matched with Operating Conditions: marked some coding values "out of valid operation range". |

| 90         | Errata FLASH_X.P001 implemented: Test Condition for Flash parameter $N_{\rm ER}$ corrected                                                        |

### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

| Table                           | e 5 Pin De       | finitior   | ns and                                        | Functions (cont'd)                                                                                                                                                                                                                                                                                   |

|---------------------------------|------------------|------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                             | Symbol           | Ctrl.      | Туре                                          | Function                                                                                                                                                                                                                                                                                             |

| 6                               | P7.0             | O0 / I     | St/B                                          | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                        |

|                                 | T3OUT            | 01         | St/B                                          | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                  |

|                                 | T6OUT            | 02         | St/B                                          | GPT12E Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                  |

|                                 | TDO_A            | OH /<br>IH | St/B                                          | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 0 or 2 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it.                                                                                                                   |

|                                 | ESR2_1           | I          | St/B                                          | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                 |

| 7                               | P7.3             | O0 / I     | St/B                                          | Bit 3 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                        |

|                                 | EMUX1            | 01         | St/B                                          | External Analog MUX Control Output 1 (ADC1)                                                                                                                                                                                                                                                          |

|                                 | U0C1_DOUT        | 02         | St/B                                          | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |

|                                 | U0C0_DOUT        | O3         | St/B                                          | USIC0 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                    |

|                                 | TMS_C            | IH         | St/B                                          | JTAG Test Mode Selection Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin low when<br>nothing is driving it.                                                                                                                                    |

|                                 | U0C1_DX0F        | I          | St/B                                          | USIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                     |

| 8                               | P7.1             | O0 / I     | St/B                                          | Bit 1 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                        |

|                                 | EXTCLK           | 01         | St/B                                          | Programmable Clock Signal Output                                                                                                                                                                                                                                                                     |

|                                 | BRKIN_C          | I          | St/B                                          | OCDS Break Signal Input                                                                                                                                                                                                                                                                              |

| 9 P7.4 O0 / I St/B Bit 4 of Por |                  | St/B       | Bit 4 of Port 7, General Purpose Input/Output |                                                                                                                                                                                                                                                                                                      |

|                                 | EMUX2            | 01         | St/B                                          | External Analog MUX Control Output 2 (ADC1)                                                                                                                                                                                                                                                          |

|                                 | U0C1_DOUT        | 02         | St/B                                          | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |

|                                 | U0C1_SCLK<br>OUT | O3         | St/B                                          | USIC0 Channel 1 Shift Clock Output                                                                                                                                                                                                                                                                   |

|                                 | тск_с            | IH         | St/B                                          | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 2 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |

|                                 | U0C0_DX0D        | I          | St/B                                          | USIC0 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                     |

|                                 | U0C1_DX1E        | I          | St/B                                          | USIC0 Channel 1 Shift Clock Input                                                                                                                                                                                                                                                                    |

| Pin | Symbol            | n Symbol Ctrl. Type Function |      |                                                   |  |  |  |  |

|-----|-------------------|------------------------------|------|---------------------------------------------------|--|--|--|--|

| 19  | P15.6             | 1                            | In/A | Bit 6 of Port 15, General Purpose Input           |  |  |  |  |

| 19  | ADC1_CH6          | 1                            | In/A | Analog Input Channel 6 for ADC1                   |  |  |  |  |

| 00  |                   | 1                            |      |                                                   |  |  |  |  |

| 20  | V <sub>AREF</sub> | -                            | PS/A | Reference Voltage for A/D Converters ADC0/1       |  |  |  |  |

| 21  | V <sub>AGND</sub> | -                            | PS/A | Reference Ground for A/D Converters ADC0/1        |  |  |  |  |

| 22  | P5.0              | I                            | In/A | Bit 0 of Port 5, General Purpose Input            |  |  |  |  |

|     | ADC0_CH0          | I                            | In/A | Analog Input Channel 0 for ADC0                   |  |  |  |  |

| 23  | P5.2              | I                            | In/A | Bit 2 of Port 5, General Purpose Input            |  |  |  |  |

|     | ADC0_CH2          | I                            | In/A | Analog Input Channel 2 for ADC0                   |  |  |  |  |

|     | TDI_A             | I                            | In/A | JTAG Test Data Input                              |  |  |  |  |

| 24  | P5.3              | I                            | In/A | Bit 3 of Port 5, General Purpose Input            |  |  |  |  |

|     | ADC0_CH3          | I                            | In/A | Analog Input Channel 3 for ADC0                   |  |  |  |  |

|     | T3INA             | I                            | In/A | GPT12E Timer T3 Count/Gate Input                  |  |  |  |  |

| 28  | P5.4              | I                            | In/A | Bit 4 of Port 5, General Purpose Input            |  |  |  |  |

|     | ADC0_CH4          | I                            | In/A | Analog Input Channel 4 for ADC0                   |  |  |  |  |

|     | T3EUDA            | I                            | In/A | GPT12E Timer T3 External Up/Down Control<br>Input |  |  |  |  |

|     | TMS_A             | I                            | In/A | JTAG Test Mode Selection Input                    |  |  |  |  |

| 29  | P5.5              | I                            | In/A | Bit 5 of Port 5, General Purpose Input            |  |  |  |  |

|     | ADC0_CH5          | I                            | In/A | Analog Input Channel 5 for ADC0                   |  |  |  |  |

|     | CCU60_T12<br>HRB  | I                            | In/A | External Run Control Input for T12 of CCU60       |  |  |  |  |

| 30  | P5.8              | I                            | In/A | Bit 8 of Port 5, General Purpose Input            |  |  |  |  |

|     | ADC0_CH8          | I                            | In/A | Analog Input Channel 8 for ADC0                   |  |  |  |  |

|     | ADC1_CH8          | I                            | In/A | Analog Input Channel 8 for ADC1                   |  |  |  |  |

|     | CCU6x_T12H<br>RC  | I                            | In/A | External Run Control Input for T12 of CCU60/1     |  |  |  |  |

|     | CCU6x_T13H<br>RC  | I                            | In/A | External Run Control Input for T13 of CCU60/1     |  |  |  |  |

|     | U2C0 DX0F         | I                            | In/A | USIC2 Channel 0 Shift Data Input                  |  |  |  |  |

| PinSymbolCtrl.TypeFunction44P4.1O0 / ISt/BBit 1 of Port 4, General Purpose Input/OuCC2_CC25O3 / ISt/BCAPCOM2 CC25IO Capture Inp./ CompareCS1OHSt/BExternal Bus Interface Chip Select 1 OutpT4EUDBISt/BGPT12E Timer T4 External Up/Down ContESR1_8ISt/BESR1 Trigger Input 845P2.4O0 / ISt/BBit 4 of Port 2, General Purpose Input/OuU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputTxDC0O2St/BCAN Node 0 Transmit Data Output                                                               | out<br>rol                                |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|

| CC2_CC25       O3 / I       St/B       CAPCOM2 CC25IO Capture Inp./ Compare         CS1       OH       St/B       External Bus Interface Chip Select 1 Outp         T4EUDB       I       St/B       GPT12E Timer T4 External Up/Down Continput         ESR1_8       I       St/B       ESR1 Trigger Input 8         45       P2.4       O0 / I       St/B       Bit 4 of Port 2, General Purpose Input/Output         U0C1_DOUT       O1       St/B       USIC0 Channel 1 Shift Data Output | out<br>rol                                |  |  |

| CS1       OH       St/B       External Bus Interface Chip Select 1 Outperface         T4EUDB       I       St/B       GPT12E Timer T4 External Up/Down Continuut         ESR1_8       I       St/B       ESR1 Trigger Input 8         45       P2.4       O0 / I       St/B       Bit 4 of Port 2, General Purpose Input/Ou         U0C1_DOUT       O1       St/B       USIC0 Channel 1 Shift Data Output                                                                                   | out<br>rol                                |  |  |

| T4EUDB       I       St/B       GPT12E Timer T4 External Up/Down Continput         ESR1_8       I       St/B       ESR1 Trigger Input 8         45       P2.4       O0 / I       St/B       Bit 4 of Port 2, General Purpose Input/Ou         U0C1_DOUT       O1       St/B       USIC0 Channel 1 Shift Data Output                                                                                                                                                                         | rol                                       |  |  |

| Input       ESR1_8     I     St/B     ESR1 Trigger Input 8       45     P2.4     O0 / I     St/B     Bit 4 of Port 2, General Purpose Input/Ou       U0C1_DOUT     O1     St/B     USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                        |                                           |  |  |

| 45 P2.4 O0 / I St/B Bit 4 of Port 2, General Purpose Input/Ou<br>U0C1_DOUT O1 St/B USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                                                                                                        | tput                                      |  |  |

| U0C1_DOUT 01 St/B USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                         | tput                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |  |  |

| TxDC0         O2         St/B         CAN Node 0 Transmit Data Output                                                                                                                                                                                                                                                                                                                                                                                                                       |                                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |  |  |

| CC2_CC17 O3 / I St/B CAPCOM2 CC17IO Capture Inp./ Compare                                                                                                                                                                                                                                                                                                                                                                                                                                   | CAPCOM2 CC17IO Capture Inp./ Compare Out. |  |  |

| A17 OH St/B External Bus Interface Address Line 17                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |  |  |

| ESR1_0 I St/B ESR1 Trigger Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |  |  |

| U0C0_DX0F I St/B USIC0 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |  |  |

| RxDC1A         I         St/B         CAN Node 1 Receive Data Input                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           |  |  |

| 46         P2.5         O0 / I         St/B         Bit 5 of Port 2, General Purpose Input/Out                                                                                                                                                                                                                                                                                                                                                                                              | tput                                      |  |  |

| U0C0_SCLK O1 St/B USIC0 Channel 0 Shift Clock Output<br>OUT                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |  |  |

| TxDC0         O2         St/B         CAN Node 0 Transmit Data Output                                                                                                                                                                                                                                                                                                                                                                                                                       |                                           |  |  |

| CC2_CC18 O3 / I St/B CAPCOM2 CC18IO Capture Inp./ Compare                                                                                                                                                                                                                                                                                                                                                                                                                                   | Out.                                      |  |  |

| A18 OH St/B External Bus Interface Address Line 18                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |  |  |

| U0C0_DX1D I St/B USIC0 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |  |  |

| ESR1_10 I St/B ESR1 Trigger Input 10                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |  |  |

| 47     P4.2     O0 / I     St/B     Bit 2 of Port 4, General Purpose Input/Out                                                                                                                                                                                                                                                                                                                                                                                                              | tput                                      |  |  |

| CC2_CC26 O3 / I St/B CAPCOM2 CC26IO Capture Inp./ Compare                                                                                                                                                                                                                                                                                                                                                                                                                                   | Out.                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ut                                        |  |  |

| CS2         OH         St/B         External Bus Interface Chip Select 2 Outplace                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |  |  |

| Table | Fin Definitions and Functions (cont'd) |        |      |                                                |  |  |

|-------|----------------------------------------|--------|------|------------------------------------------------|--|--|

| Pin   | Symbol                                 | Ctrl.  | Туре | Function                                       |  |  |

| 48    | P2.6                                   | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output  |  |  |

|       | U0C0_SELO<br>0                         | 01     | St/B | USIC0 Channel 0 Select/Control 0 Output        |  |  |

|       | U0C1_SELO<br>1                         | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output        |  |  |

|       | CC2_CC19                               | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.      |  |  |

|       | A19                                    | ОН     | St/B | External Bus Interface Address Line 19         |  |  |

|       | U0C0_DX2D                              | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |  |

|       | RxDC0D                                 | I      | St/B | CAN Node 0 Receive Data Input                  |  |  |

|       | ESR2_6                                 | I      | St/B | ESR2 Trigger Input 6                           |  |  |

| 49    | P4.3                                   | O0 / I | St/B | Bit 3 of Port 4, General Purpose Input/Output  |  |  |

|       | U0C1_DOUT                              | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |  |

|       | CC2_CC27                               | O3 / I | St/B | CAPCOM2 CC27IO Capture Inp./ Compare Out.      |  |  |

|       | CS3                                    | OH     | St/B | External Bus Interface Chip Select 3 Output    |  |  |

|       | T2EUDA                                 | I      | St/B | GPT12E Timer T2 External Up/Down Control Input |  |  |

| 53    | P0.0                                   | O0 / I | St/B | Bit 0 of Port 0, General Purpose Input/Output  |  |  |

|       | U1C0_DOUT                              | 01     | St/B | USIC1 Channel 0 Shift Data Output              |  |  |

|       | CCU61_CC6<br>0                         | O3     | St/B | CCU61 Channel 0 IOutput                        |  |  |

|       | A0                                     | OH     | St/B | External Bus Interface Address Line 0          |  |  |

|       | U1C0_DX0A                              | I      | St/B | USIC1 Channel 0 Shift Data Input               |  |  |

|       | CCU61_CC6<br>0INA                      | I      | St/B | CCU61 Channel 0 Input                          |  |  |

|       | ESR1_11                                | I      | St/B | ESR1 Trigger Input 11                          |  |  |

| Table | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                               |  |  |  |

|-------|--------------------------------------------------------|--------|------|-----------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                      |  |  |  |

| 54    | P2.7                                                   | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |  |

|       | U0C1_SELO<br>0                                         | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |  |

|       | U0C0_SELO<br>1                                         | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |  |

|       | CC2_CC20                                               | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |  |

|       | A20                                                    | ОН     | St/B | External Bus Interface Address Line 20        |  |  |  |

|       | U0C1_DX2C                                              | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |  |

|       | RxDC1C                                                 | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |  |

|       | ESR2_7                                                 | I      | St/B | ESR2 Trigger Input 7                          |  |  |  |

| 55    | P0.1                                                   | O0 / I | St/B | Bit 1 of Port 0, General Purpose Input/Output |  |  |  |

|       | U1C0_DOUT                                              | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |  |  |

|       | TxDC0                                                  | 02     | St/B | CAN Node 0 Transmit Data Output               |  |  |  |

|       | CCU61_CC6<br>1                                         | O3     | St/B | CCU61 Channel 1 Output                        |  |  |  |

|       | A1                                                     | OH     | St/B | External Bus Interface Address Line 1         |  |  |  |

|       | U1C0_DX0B                                              | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |  |

|       | CCU61_CC6<br>1INA                                      | I      | St/B | CCU61 Channel 1 Input                         |  |  |  |

|       | U1C0_DX1A                                              | I      | St/B | USIC1 Channel 0 Shift Clock Input             |  |  |  |

| 56    | P2.8                                                   | O0 / I | DP/B | Bit 8 of Port 2, General Purpose Input/Output |  |  |  |

|       | U0C1_SCLK<br>OUT                                       | 01     | DP/B | USIC0 Channel 1 Shift Clock Output            |  |  |  |

|       | EXTCLK                                                 | O2     | DP/B | Programmable Clock Signal Output              |  |  |  |

|       | CC2_CC21                                               | O3 / I | DP/B | CAPCOM2 CC21IO Capture Inp./ Compare Out.     |  |  |  |

|       | A21                                                    | OH     | DP/B | External Bus Interface Address Line 21        |  |  |  |

|       | U0C1_DX1D                                              | I      | DP/B | USIC0 Channel 1 Shift Clock Input             |  |  |  |

| Table | 1                 | 1          | i    | Functions (cont'd)                             |  |  |

|-------|-------------------|------------|------|------------------------------------------------|--|--|

| Pin   | Symbol            | Ctrl.      | Туре |                                                |  |  |

| 62    | P10.2             | O0 / I     |      | Bit 2 of Port 10, General Purpose Input/Output |  |  |

|       | U0C0_SCLK<br>OUT  | 01         | St/B | USIC0 Channel 0 Shift Clock Output             |  |  |

|       | CCU60_CC6<br>2    | O2         | St/B | CCU60 Channel 2 Output                         |  |  |

|       | AD2               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 2     |  |  |

|       | CCU60_CC6<br>2INA | I          | St/B | CCU60 Channel 2 Input                          |  |  |

|       | U0C0_DX1B         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |

| 63    | P0.4              | O0 / I     | St/B | Bit 4 of Port 0, General Purpose Input/Output  |  |  |

|       | U1C1_SELO<br>0    | O1         | St/B | USIC1 Channel 1 Select/Control 0 Output        |  |  |

|       | U1C0_SELO<br>1    | 02         | St/B | USIC1 Channel 0 Select/Control 1 Output        |  |  |

|       | CCU61_COU<br>T61  | O3         | St/B | CCU61 Channel 1 Output                         |  |  |

|       | A4                | OH         | St/B | External Bus Interface Address Line 4          |  |  |

|       | U1C1_DX2A         | I          | St/B | USIC1 Channel 1 Shift Control Input            |  |  |

|       | RxDC1B            | I          | St/B | CAN Node 1 Receive Data Input                  |  |  |

|       | ESR2_8            | I          | St/B | ESR2 Trigger Input 8                           |  |  |

| 65    | P2.13             | O0 / I     | St/B | Bit 13 of Port 2, General Purpose Input/Output |  |  |

|       | U2C1_SELO<br>2    | O1         | St/B | USIC2 Channel 1 Select/Control 2 Output        |  |  |

| 66    | P2.10             | O0 / I     | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |  |

|       | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |  |

|       | U0C0_SELO<br>3    | O2         | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |

|       | CC2_CC23          | O3 / I     | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |  |

|       | A23               | ОН         | St/B | External Bus Interface Address Line 23         |  |  |

|       | U0C1_DX0E         | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |  |

|       | CAPINA            | I          | St/B | GPT12E Register CAPREL Capture Input           |  |  |

| Table | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                                 |  |  |  |

|-------|--------------------------------------------------------|--------|------|-------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                        |  |  |  |

| 87    | P1.3                                                   | O0 / I | St/B | Bit 3 of Port 1, General Purpose Input/Output   |  |  |  |

|       | U1C0_SELO<br>7                                         | O2     | St/B | USIC1 Channel 0 Select/Control 7 Output         |  |  |  |

|       | U2C0_SELO<br>4                                         | O3     | St/B | USIC2 Channel 0 Select/Control 4 Output         |  |  |  |

|       | A11                                                    | ОН     | St/B | External Bus Interface Address Line 11          |  |  |  |

|       | ESR2_4                                                 | I      | St/B | ESR2 Trigger Input 4                            |  |  |  |

| 89    | P10.14                                                 | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output |  |  |  |

|       | U1C0_SELO<br>1                                         | O1     | St/B | USIC1 Channel 0 Select/Control 1 Output         |  |  |  |

|       | U0C1_DOUT                                              | 02     | St/B | USIC0 Channel 1 Shift Data Output               |  |  |  |

|       | RD                                                     | ОН     | St/B | External Bus Interface Read Strobe Output       |  |  |  |

|       | ESR2_2                                                 | I      | St/B | ESR2 Trigger Input 2                            |  |  |  |

|       | U0C1_DX0C                                              | I      | St/B | USIC0 Channel 1 Shift Data Input                |  |  |  |

| 90    | P1.4                                                   | 00 / 1 | St/B | Bit 4 of Port 1, General Purpose Input/Output   |  |  |  |

|       | U1C1_SELO<br>4                                         | O2     | St/B | USIC1 Channel 1 Select/Control 4 Output         |  |  |  |

|       | U2C0_SELO<br>5                                         | O3     | St/B | USIC2 Channel 0 Select/Control 5 Output         |  |  |  |

|       | A12                                                    | OH     | St/B | External Bus Interface Address Line 12          |  |  |  |

|       | U2C0_DX2B                                              | I      | St/B | USIC2 Channel 0 Shift Control Input             |  |  |  |

| 91    | P10.15                                                 | O0 / I | St/B | Bit 15 of Port 10, General Purpose Input/Output |  |  |  |

|       | U1C0_SELO<br>2                                         | 01     | St/B | USIC1 Channel 0 Select/Control 2 Output         |  |  |  |

|       | U0C1_DOUT                                              | 02     | St/B | USIC0 Channel 1 Shift Data Output               |  |  |  |

|       | U1C0_DOUT                                              | O3     | St/B | USIC1 Channel 0 Shift Data Output               |  |  |  |

|       | ALE                                                    | ОН     | St/B | External Bus Interf. Addr. Latch Enable Output  |  |  |  |

|       | U0C1_DX1C                                              | I      | St/B | USIC0 Channel 1 Shift Clock Input               |  |  |  |

# XE164FN, XE164GN, XE164HN, XE164KN XE166 Family / Value Line

# **General Device Information**

| Table            | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                     |  |  |

|------------------|--------------------------------------------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin              | Symbol                                                 | Ctrl.  | Туре | Function                                                                                                                                                                            |  |  |

| 98               | ESR1                                                   | O0 / I | St/B | <b>External Service Request 1</b><br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                             |  |  |

|                  | RxDC0E                                                 | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                       |  |  |

|                  | U1C0_DX0F                                              | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                    |  |  |

|                  | U1C0_DX2C                                              | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                 |  |  |

|                  | U1C1_DX0C                                              | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                    |  |  |

|                  | U1C1_DX2B                                              | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                 |  |  |

|                  | U2C1_DX2C                                              | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                 |  |  |

| 99               | ESR0                                                   | O0 / I | St/B | External Service Request 0<br>After power-up, ESR0 operates as open-drain<br>bidirectional reset with a weak pull-up.                                                               |  |  |

|                  | U1C0_DX0E                                              | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                    |  |  |

|                  | U1C0_DX2B                                              | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                 |  |  |

| 10               | V <sub>DDIM</sub>                                      | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                |  |  |

| 38,<br>64,<br>88 | V <sub>DDI1</sub>                                      | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All V <sub>DDI1</sub> pins must be connected to each other. |  |  |

| 14               | V <sub>DDPA</sub>                                      | -      | PS/A | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent $V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.              |  |  |

|                  |                                                        |        |      | Note: The A/D_Converters and ports P5, P6 and P15 are fed from supply voltage $V_{DDPA}$ .                                                                                          |  |  |

#### **General Device Information**

# 2.2 Identification Registers

The identification registers describe the current version of the XE164xN and of its modules.

### Table 6 XE164xN Identification Registers

| Short Name  | Value                  | Address              | Notes                   |

|-------------|------------------------|----------------------|-------------------------|

| SCU_IDMANUF | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |                         |

| SCU_IDCHIP  | 3001 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking EES-AA or ES-AA |

|             | 3002 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking AA, AB          |

| SCU_IDMEM   | 304F <sub>H</sub>      | 00'F07A <sub>H</sub> |                         |

| SCU_IDPROG  | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |                         |

| JTAG_ID     | 0018'B083 <sub>H</sub> |                      | marking EES-AA or ES-AA |

|             | 1018'B083 <sub>H</sub> |                      | marking AA, AB          |

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |

|----------------------|----------------------|----------------------|-------------------------|-------|

| Reserved for DSRAM   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                |       |

| External memory area | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               |       |

### Table 7 XE164xN Memory Map (cont'd)<sup>1)</sup>

Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

- 2) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

- 3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

- Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 16 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the quoted device type.

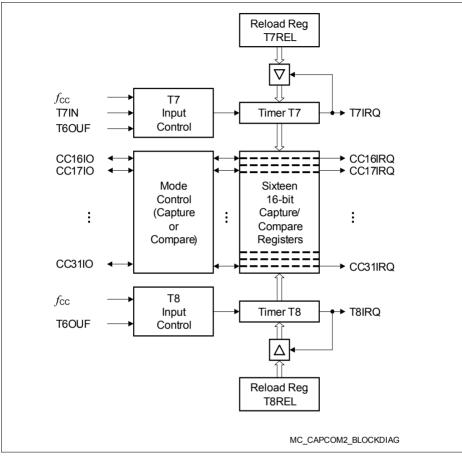

# 3.8 Capture/Compare Unit (CC2)

The CAPCOM unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, external count inputs allow event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

| Compare Modes | Function                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

Table 8 Compare Modes

### **Functional Description**

Figure 6 CAPCOM Unit Block Diagram

### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- · Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- · Flexible and powerful message transfer control and error handling capabilities

- · Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

## 3.15 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

## 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz).

The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

## 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE164xN from a number of external or internal clock sources:

- · External clock signals with pad voltage or core voltage levels

- · External crystal or resonator using the on-chip oscillator

- · On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

# 3.18 Parallel Ports

The XE164xN provides up to 76 I/O lines which are organized into 7 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in Table 9.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |  |  |  |  |  |

|------|-------|-----|---------------------------------------------------------------------------------|--|--|--|--|--|

| P0   | 8     | I/O | EBC (A7A0), CCU6, USIC, CAN                                                     |  |  |  |  |  |

| P1   | 8     | I/O | EBC (A15A8), CCU6, USIC                                                         |  |  |  |  |  |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |  |  |  |  |  |

| P4   | 4     | I/O | EBC (CS3CS0), CC2, CAN, GPT12E, USIC                                            |  |  |  |  |  |

| P5   | 11    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |  |  |  |  |  |

| P6   | 3     | I/O | ADC, CAN, GPT12E                                                                |  |  |  |  |  |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |  |  |  |  |  |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN                    |  |  |  |  |  |

| P15  | 5     | I   | Analog Inputs, GPT12E                                                           |  |  |  |  |  |

### Table 9Summary of the XE164xN's Ports

### **Functional Description**

| Table 10Instruction Set Summary (cont'd) |                                     |       |  |  |  |  |

|------------------------------------------|-------------------------------------|-------|--|--|--|--|

| Mnemonic                                 | Description                         | Bytes |  |  |  |  |

| NOP                                      | Null operation                      | 2     |  |  |  |  |

| CoMUL/CoMAC                              | Multiply (and accumulate)           | 4     |  |  |  |  |

| CoADD/CoSUB                              | Add/Subtract                        | 4     |  |  |  |  |

| Co(A)SHR                                 | (Arithmetic) Shift right            | 4     |  |  |  |  |

| CoSHL                                    | Shift left                          | 4     |  |  |  |  |

| CoLOAD/STORE                             | Load accumulator/Store MAC register | 4     |  |  |  |  |

| CoCMP                                    | Compare                             | 4     |  |  |  |  |

| CoMAX/MIN                                | Maximum/Minimum                     | 4     |  |  |  |  |

| CoABS/CoRND                              | Absolute value/Round accumulator    | 4     |  |  |  |  |

| CoMOV                                    | Data move                           | 4     |  |  |  |  |

| CoNEG/NOP                                | Negate accumulator/Null operation   | 4     |  |  |  |  |

The Enter Power Down Mode instruction is not used in the XE164xN, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

#### **Electrical Parameters**

## 4.3.3 Power Consumption

The power consumed by the XE164xN depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current  $I_{\rm LK}$  depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

#### **Electrical Parameters**

# 4.7.7 Debug Interface Timing

The debugger can communicate with the XE164xN either via the 2-pin DAP interface or via the standard JTAG interface.

### Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 37** is valid under the following conditions:  $C_1 = 20 \text{ pF}$ ; voltage\_range= upper

| Parameter                                         | Symbol                    | Values |      |      | Unit | Note /         |

|---------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                   |                           | Min.   | Тур. | Max. | 1    | Test Condition |

| DAP0 clock period <sup>1)</sup>                   | <i>t</i> <sub>11</sub> SR | 25     | -    | _    | ns   |                |

| DAP0 high time                                    | t <sub>12</sub> SR        | 8      | -    | _    | ns   |                |

| DAP0 low time <sup>1)</sup>                       | t <sub>13</sub> SR        | 8      | -    | _    | ns   |                |

| DAP0 clock rise time                              | t <sub>14</sub> SR        | -      | -    | 4    | ns   |                |

| DAP0 clock fall time                              | t <sub>15</sub> SR        | -      | -    | 4    | ns   |                |

| DAP1 setup to DAP0<br>rising edge                 | <i>t</i> <sub>16</sub> SR | 6      | -    | -    | ns   |                |

| DAP1 hold after DAP0 rising edge                  | <i>t</i> <sub>17</sub> SR | 6      | -    | -    | ns   |                |

| DAP1 valid per DAP0<br>clock period <sup>2)</sup> | <i>t</i> <sub>19</sub> CC | 17     | 20   | -    | ns   |                |

Table 37

DAP Interface Timing for Upper Voltage Range

1) See the DAP chapter for clock rate restrictions in the Active::IDLE protocol state.

2) The Host has to find a suitable sampling point by analyzing the sync telegram response.

**Table 38** is valid under the following conditions:  $C_{L}$  = 20 pF; voltage\_range = lower

#### Package and Reliability

# 5.2 Thermal Considerations

When operating the XE164xN in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}}-V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- · Reduce the system frequency

- · Reduce the number of output pins

- Reduce the load on active output drivers