Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFl

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 320KB (320K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe164fn40f80laafxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2013-02 Published by Infineon Technologies AG 81726 Munich, Germany © 2013 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

VE464vN Data Chast

| Revision F | Jata Sheet<br>listory: V1.4 2013-02                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Previous V | ersions:                                                                                                                                          |

| V1.3, 2011 | -07                                                                                                                                               |

| V1.2, 2010 | -04                                                                                                                                               |

| V1.1, 2009 |                                                                                                                                                   |

| V1.0, 2009 | -03 Preliminary                                                                                                                                   |

| Page       | Subjects (major changes since last revision)                                                                                                      |

| 36         | Added AB step marking.                                                                                                                            |

| 87         | Errata SWD_X.P002 implemented: $V_{\rm SWD}$ tolerance boundaries for 5.5 V are changed.                                                          |

| 89         | Clarified "Coding of bit fields LEVxV" descriptions. Matched with Operating Conditions: marked some coding values "out of valid operation range". |

| 90         | Errata FLASH_X.P001 implemented: Test Condition for Flash parameter $N_{\rm ER}$ corrected                                                        |

## Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

## **Table of Contents**

| 4.7.1<br>4.7.2<br>4.7.2.1<br>4.7.2.2 | Testing Waveforms       92         Definition of Internal Timing       93         Phase Locked Loop (PLL)       94         Wakeup Clock       97 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7.2.3                              | Selecting and Changing the Operating Frequency                                                                                                   |

| 4.7.3                                | External Clock Input Parameters 98                                                                                                               |

| 4.7.4                                | Pad Properties 100                                                                                                                               |

| 4.7.5                                | External Bus Timing 104                                                                                                                          |

| 4.7.5.1                              | Bus Cycle Control with the READY Input 109                                                                                                       |

| 4.7.6                                | Synchronous Serial Interface Timing 112                                                                                                          |

| 4.7.7                                | Debug Interface Timing 116                                                                                                                       |

| 5                                    | Package and Reliability 122                                                                                                                      |

| 5.1                                  | Packaging                                                                                                                                        |

| 5.2                                  | Thermal Considerations 124                                                                                                                       |

| 5.3                                  | Quality Declarations                                                                                                                             |

## **General Device Information**

| PinSymbolCtrl.TypeFunction39P2.0O0 / ISt/BBit 0 of Port 2, General Purpose Input/OuAD13OH /<br>IHSt/BExternal Bus Interface Address/Data LineRxDC0CISt/BCAN Node 0 Receive Data Input40P2.1O0 / ISt/BGPT12E Timer T5 Count/Gate Input40P2.1O0 / ISt/BBit 1 of Port 2, General Purpose Input/Ou40TxDC0O1St/BCAN Node 0 Transmit Data Output41AD14OH /<br>IHSt/BExternal Bus Interface Address/Data Line41P2.2O0 / ISt/BGPT12E Timer T5 External Up/Down Con<br>Input41P2.2O0 / ISt/BBit 2 of Port 2, General Purpose Input/Ou41P2.2O0 / ISt/BBit 2 of Port 2, General Purpose Input/Ou42P4.0O0 / ISt/BBit 2 of Port 4, General Purpose Input/Ou                                                                                                            | tput       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| AD13OH /<br>IHSt/BExternal Bus Interface Address/Data LineRxDC0CISt/BCAN Node 0 Receive Data InputT5INBISt/BGPT12E Timer T5 Count/Gate Input40P2.1O0 / ISt/BBit 1 of Port 2, General Purpose Input/OuTxDC0O1St/BCAN Node 0 Transmit Data OutputAD14OH /<br>St/BExternal Bus Interface Address/Data LineT5EUDBISt/BGPT12E Timer T5 External Up/Down Con<br>InputESR1_5ISt/BESR1 Trigger Input 541P2.2O0 / ISt/BBit 2 of Port 2, General Purpose Input/Ou<br>TxDC1AD15OH /<br>St/BExternal Bus Interface Address/Data Line<br>                                                                                                                                                                                                                              | tput       |

| IHIHRxDC0CISt/BCAN Node 0 Receive Data InputT5INBISt/BGPT12E Timer T5 Count/Gate Input40P2.1O0 / ISt/BBit 1 of Port 2, General Purpose Input/OuTxDC0O1St/BCAN Node 0 Transmit Data OutputAD14OH /<br>IHSt/BExternal Bus Interface Address/Data LineT5EUDBISt/BGPT12E Timer T5 External Up/Down Con<br>InputESR1_5ISt/BESR1 Trigger Input 541P2.2O0 / ISt/BBit 2 of Port 2, General Purpose Input/OuTxDC1O1St/BExternal Bus Interface Address/Data LineAD15OH /<br>IHSt/BExternal Bus Interface Address/Data LineESR2_5ISt/BBit 2 of Port 2, General Purpose Input/OuAD15OH /<br>IHSt/BExternal Bus Interface Address/Data LineESR2_5ISt/BExternal Bus Interface Address/Data Line42P4.0O0 / ISt/BBit 0 of Port 4, General Purpose Input/Ou                | tput<br>14 |

| T5INBISt/BGPT12E Timer T5 Count/Gate Input40P2.1O0 / ISt/BBit 1 of Port 2, General Purpose Input/OuTxDC0O1St/BCAN Node 0 Transmit Data OutputAD14OH /<br>IHSt/BExternal Bus Interface Address/Data LineT5EUDBISt/BGPT12E Timer T5 External Up/Down Con<br>InputESR1_5ISt/BESR1 Trigger Input 541P2.2O0 / ISt/BBit 2 of Port 2, General Purpose Input/OuTxDC1O1St/BCAN Node 1 Transmit Data OutputAD15OH /<br>IHSt/BExternal Bus Interface Address/Data LineESR2_5ISt/BExternal Purpose Input/Ou42P4.0O0 / ISt/BBit 0 of Port 4, General Purpose Input/Ou                                                                                                                                                                                                  | 9 14       |

| 40       P2.1       O0 / I       St/B       Bit 1 of Port 2, General Purpose Input/Ou         TxDC0       O1       St/B       CAN Node 0 Transmit Data Output         AD14       OH /<br>IH       St/B       External Bus Interface Address/Data Line         T5EUDB       I       St/B       GPT12E Timer T5 External Up/Down Con<br>Input         ESR1_5       I       St/B       ESR1 Trigger Input 5         41       P2.2       O0 / I       St/B       Bit 2 of Port 2, General Purpose Input/Ou         TxDC1       O1       St/B       External Bus Interface Address/Data Line         AD15       OH /<br>IH       St/B       EsR2 Trigger Input 5         42       P4.0       O0 / I       St/B       Bit 0 of Port 4, General Purpose Input/Ou | 9 14       |

| TxDC0       O1       St/B       CAN Node 0 Transmit Data Output         AD14       OH /<br>IH       St/B       External Bus Interface Address/Data Line         T5EUDB       I       St/B       GPT12E Timer T5 External Up/Down Con<br>Input         ESR1_5       I       St/B       ESR1 Trigger Input 5         41       P2.2       O0 / I       St/B       Bit 2 of Port 2, General Purpose Input/Ou<br>TxDC1         AD15       OH /<br>IH       St/B       External Bus Interface Address/Data Line         ESR2_5       I       St/B       External Bus Interface Address/Data Line         42       P4.0       O0 / I       St/B       Bit 0 of Port 4, General Purpose Input/Ou                                                                  | 9 14       |

| AD14       OH /<br>IH       St/B       External Bus Interface Address/Data Line         T5EUDB       I       St/B       GPT12E Timer T5 External Up/Down Con<br>Input         ESR1_5       I       St/B       ESR1 Trigger Input 5         41       P2.2       O0 / I       St/B       Bit 2 of Port 2, General Purpose Input/Ou         TxDC1       O1       St/B       CAN Node 1 Transmit Data Output         AD15       OH /<br>IH       St/B       External Bus Interface Address/Data Line         ESR2_5       I       St/B       ESR2 Trigger Input 5         42       P4.0       O0 / I       St/B       Bit 0 of Port 4, General Purpose Input/Ou                                                                                               |            |

| IH       IH         T5EUDB       I       St/B       GPT12E Timer T5 External Up/Down Con Input         ESR1_5       I       St/B       ESR1 Trigger Input 5         41       P2.2       O0 / I       St/B       Bit 2 of Port 2, General Purpose Input/Out         TxDC1       O1       St/B       CAN Node 1 Transmit Data Output         AD15       OH / IH       St/B       External Bus Interface Address/Data Line         ESR2_5       I       St/B       ESR2 Trigger Input 5         42       P4.0       O0 / I       St/B       Bit 0 of Port 4, General Purpose Input/Out                                                                                                                                                                       |            |

| Imput         ESR1_5       I       St/B       ESR1 Trigger Input 5         41       P2.2       O0 / I       St/B       Bit 2 of Port 2, General Purpose Input/Ou         TxDC1       O1       St/B       CAN Node 1 Transmit Data Output         AD15       OH /<br>IH       St/B       External Bus Interface Address/Data Line         ESR2_5       I       St/B       ESR2 Trigger Input 5         42       P4.0       O0 / I       St/B       Bit 0 of Port 4, General Purpose Input/Ou                                                                                                                                                                                                                                                               | trol       |

| 41       P2.2       O0 / I       St/B       Bit 2 of Port 2, General Purpose Input/Out         TxDC1       O1       St/B       CAN Node 1 Transmit Data Output         AD15       OH /       St/B       External Bus Interface Address/Data Line         ESR2_5       I       St/B       ESR2 Trigger Input 5         42       P4.0       O0 / I       St/B       Bit 0 of Port 4, General Purpose Input/Out                                                                                                                                                                                                                                                                                                                                              |            |

| TxDC1       O1       St/B       CAN Node 1 Transmit Data Output         AD15       OH /<br>IH       St/B       External Bus Interface Address/Data Line         ESR2_5       I       St/B       ESR2 Trigger Input 5         42       P4.0       O0 / I       St/B       Bit 0 of Port 4, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| AD15     OH /<br>IH     St/B     External Bus Interface Address/Data Line       ESR2_5     I     St/B     ESR2 Trigger Input 5       42     P4.0     O0 / I     St/B     Bit 0 of Port 4, General Purpose Input/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tput       |

| IH         ESR2_5         I         St/B         ESR2 Trigger Input 5           42         P4.0         O0 / I         St/B         Bit 0 of Port 4, General Purpose Input/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| 42 P4.0 O0 / I St/B Bit 0 of Port 4, General Purpose Input/Ou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tput       |

| CC2_CC24 O3 / I St/B CAPCOM2 CC24IO Capture Inp./ Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ) Out.     |

| CS0         OH         St/B         External Bus Interface Chip Select 0 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | out        |

| 43 P2.3 O0 / I St/B Bit 3 of Port 2, General Purpose Input/Ou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tput       |

| U0C0_DOUT O1 St/B USIC0 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| CC2_CC16 O3 / I St/B CAPCOM2 CC16IO Capture Inp./ Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ) Out.     |

| A16 OH St/B External Bus Interface Address Line 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| ESR2_0 I St/B ESR2 Trigger Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

| U0C0_DX0E I St/B USIC0 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| U0C1_DX0D I St/B USIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| RxDC0A         I         St/B         CAN Node 0 Receive Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

#### **General Device Information**

| Table | e 5 Pin De     | finitior | ns and | Functions (cont'd)                              |

|-------|----------------|----------|--------|-------------------------------------------------|

| Pin   | Symbol         | Ctrl.    | Туре   | Function                                        |

| 87    | P1.3           | O0 / I   | St/B   | Bit 3 of Port 1, General Purpose Input/Output   |

|       | U1C0_SELO<br>7 | O2       | St/B   | USIC1 Channel 0 Select/Control 7 Output         |

|       | U2C0_SELO<br>4 | O3       | St/B   | USIC2 Channel 0 Select/Control 4 Output         |

|       | A11            | ОН       | St/B   | External Bus Interface Address Line 11          |

|       | ESR2_4         | I        | St/B   | ESR2 Trigger Input 4                            |

| 89    | P10.14         | O0 / I   | St/B   | Bit 14 of Port 10, General Purpose Input/Output |

|       | U1C0_SELO<br>1 | O1       | St/B   | USIC1 Channel 0 Select/Control 1 Output         |

|       | U0C1_DOUT      | 02       | St/B   | USIC0 Channel 1 Shift Data Output               |

|       | RD             | ОН       | St/B   | External Bus Interface Read Strobe Output       |

|       | ESR2_2         | I        | St/B   | ESR2 Trigger Input 2                            |

|       | U0C1_DX0C      | I        | St/B   | USIC0 Channel 1 Shift Data Input                |

| 90    | P1.4           | 00 / 1   | St/B   | Bit 4 of Port 1, General Purpose Input/Output   |

|       | U1C1_SELO<br>4 | O2       | St/B   | USIC1 Channel 1 Select/Control 4 Output         |

|       | U2C0_SELO<br>5 | O3       | St/B   | USIC2 Channel 0 Select/Control 5 Output         |

|       | A12            | OH       | St/B   | External Bus Interface Address Line 12          |

|       | U2C0_DX2B      | I        | St/B   | USIC2 Channel 0 Shift Control Input             |

| 91    | P10.15         | O0 / I   | St/B   | Bit 15 of Port 10, General Purpose Input/Output |

|       | U1C0_SELO<br>2 | 01       | St/B   | USIC1 Channel 0 Select/Control 2 Output         |

|       | U0C1_DOUT      | 02       | St/B   | USIC0 Channel 1 Shift Data Output               |

|       | U1C0_DOUT      | O3       | St/B   | USIC1 Channel 0 Shift Data Output               |

|       | ALE            | ОН       | St/B   | External Bus Interf. Addr. Latch Enable Output  |

|       | U0C1_DX1C      | I        | St/B   | USIC0 Channel 1 Shift Clock Input               |

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |

|----------------------|----------------------|----------------------|-------------------------|-------|

| Reserved for DSRAM   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                |       |

| External memory area | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               |       |

## Table 7 XE164xN Memory Map (cont'd)<sup>1)</sup>

Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

- 2) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

- 3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

- Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 16 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the quoted device type.

Up to 16 Kbytes of on-chip Data SRAM (DSRAM) are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

Note: The actual size of the DSRAM depends on the quoted device type.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XE166 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 7**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**The on-chip Flash memory** stores code, constant data, and control data. The 320 Kbytes of on-chip Flash memory consist of 1 module of 64 Kbytes (preferably for data storage) and 1 module of 256 Kbytes. Each module is organized in 4-Kbyte sectors. The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see Section 4.6.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

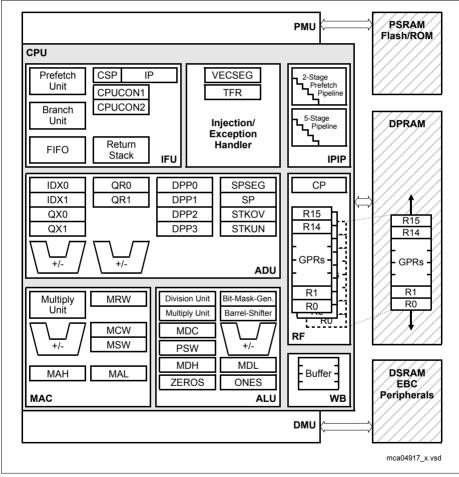

# 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

Figure 5 CPU Block Diagram

## **Functional Description**

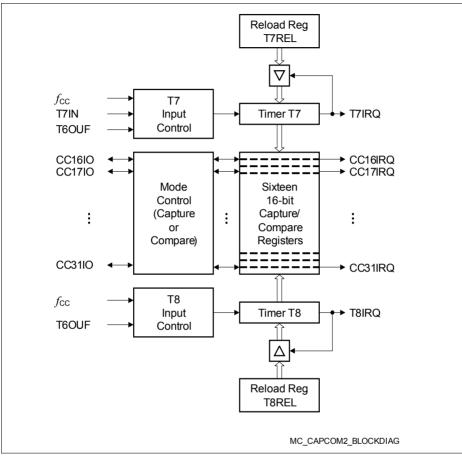

Figure 6 CAPCOM Unit Block Diagram

## **Functional Description**

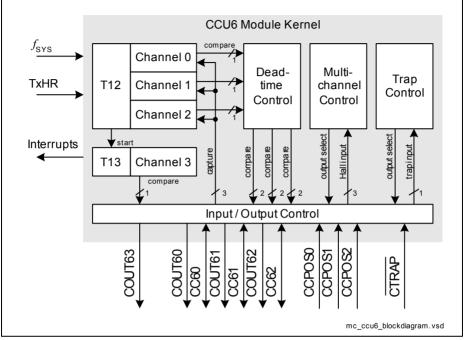

## Figure 7 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

## **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

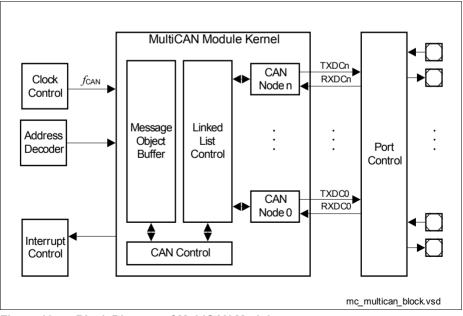

## 3.14 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 12 Block Diagram of MultiCAN Module

## 3.18 Parallel Ports

The XE164xN provides up to 76 I/O lines which are organized into 7 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in Table 9.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |

|------|-------|-----|---------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0), CCU6, USIC, CAN                                                     |

| P1   | 8     | I/O | EBC (A15A8), CCU6, USIC                                                         |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P4   | 4     | I/O | EBC (CS3CS0), CC2, CAN, GPT12E, USIC                                            |

| P5   | 11    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |

| P6   | 3     | I/O | ADC, CAN, GPT12E                                                                |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN                    |

| P15  | 5     | I   | Analog Inputs, GPT12E                                                           |

## Table 9Summary of the XE164xN's Ports

## 4.7.3 External Clock Input Parameters

These parameters specify the external clock generation for the XE164xN. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2.

- By supplying an external clock signal

- This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain).

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . If connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

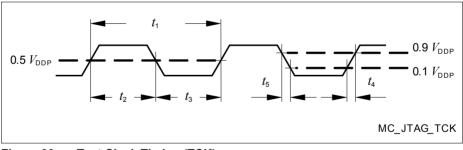

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

Note: Operating Conditions apply.

| Parameter                                      | Symbol                |                             | Values | 5    | Unit | Note /                                                     |

|------------------------------------------------|-----------------------|-----------------------------|--------|------|------|------------------------------------------------------------|

|                                                |                       | Min.                        | Тур.   | Max. |      | Test Condition                                             |

| Oscillator frequency                           | $f_{\rm OSC}{\rm SR}$ | 4                           | -      | 40   | MHz  | Input= Clock<br>Signal                                     |

|                                                |                       | 4                           | -      | 16   | MHz  | Input= Crystal<br>or Ceramic<br>Resonator                  |

| XTAL1 input current absolute value             | I <sub>IL</sub>   CC  | -                           | -      | 20   | μA   |                                                            |

| Input clock high time                          | t <sub>1</sub> SR     | 6                           | -      | -    | ns   |                                                            |

| Input clock low time                           | $t_2  \mathrm{SR}$    | 6                           | -      | -    | ns   |                                                            |

| Input clock rise time                          | t <sub>3</sub> SR     | -                           | 8      | 8    | ns   |                                                            |

| Input clock fall time                          | $t_4$ SR              | -                           | 8      | 8    | ns   |                                                            |

| Input voltage amplitude on XTAL1 <sup>1)</sup> | $V_{AX1}SR$           | 0.3 x<br>V <sub>DDIM</sub>  | -      | -    | V    | $f_{OSC} \ge 4 \text{ MHz};$<br>$f_{OSC} < 16 \text{ MHz}$ |

|                                                |                       | 0.4 x<br>V <sub>DDIM</sub>  | -      | -    | V    | $f_{\rm OSC} \ge$ 16 MHz;<br>$f_{\rm OSC} <$ 25 MHz        |

|                                                |                       | 0.5 x<br>V <sub>DDIM</sub>  | -      | -    | V    | $f_{\rm OSC} \ge$ 25 MHz;<br>$f_{\rm OSC} \le$ 40 MHz      |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}$ SR      | -1.7 +<br>V <sub>DDIM</sub> | -      | 1.7  | V    | 2)                                                         |

Table 26 External Clock Input Characteristics

| Parameter                                                    | Symbol                  |      | Values | 5    | Unit | Note /                      |

|--------------------------------------------------------------|-------------------------|------|--------|------|------|-----------------------------|

|                                                              |                         | Min. | Тур.   | Max. |      | Test Condition              |

| Maximum output driver current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -    | -      | 2.5  | mA   | Driver_Strength<br>= Medium |

|                                                              |                         | _    | -      | 10   | mA   | Driver_Strength<br>= Strong |

|                                                              |                         | -    | -      | 0.5  | mA   | Driver_Strength<br>= Weak   |

| Nominal output driver current (absolute value)               | I <sub>Onom</sub><br>CC | -    | -      | 1.0  | mA   | Driver_Strength<br>= Medium |

|                                                              |                         | -    | -      | 2.5  | mA   | Driver_Strength<br>= Strong |

|                                                              |                         | _    | -      | 0.1  | mA   | Driver_Strength<br>= Weak   |

## Table 28 Standard Pad Parameters for Lower Voltage Range

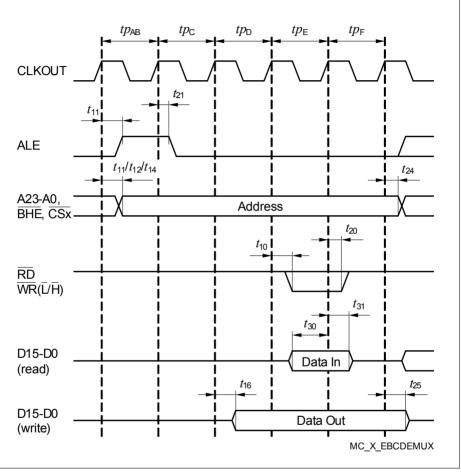

### Table 31 External Bus Timing for Upper Voltage Range (cont'd)

| Parameter                                                                  | Symbol                    | Values |      |      | Unit | Note /         |

|----------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                            |                           | Min.   | Тур. | Max. |      | Test Condition |

| Address output valid delay<br>for AD15 AD0 (MUX<br>mode)                   | <i>t</i> <sub>13</sub> CC | -      | 8    | 15   | ns   |                |

| Output valid delay for CS                                                  | <i>t</i> <sub>14</sub> CC | -      | 7    | 13   | ns   |                |

| Data output valid delay for<br>AD15 AD0 (write data,<br>MUX mode)          | <i>t</i> <sub>15</sub> CC | -      | 8    | 15   | ns   |                |

| Data output valid delay for<br>D15 D0 (write data,<br>DEMUX mode)          | <i>t</i> <sub>16</sub> CC | _      | 8    | 15   | ns   |                |

| $\frac{\text{Output hold time for }\overline{\text{RD}},}{\text{WR}(L/H)}$ | <i>t</i> <sub>20</sub> CC | -2     | 6    | 8    | ns   |                |

| Output hold time for $\overline{BHE}$ , ALE                                | <i>t</i> <sub>21</sub> CC | -2     | 6    | 10   | ns   |                |

| Address output hold time for AD15 AD0                                      | <i>t</i> <sub>23</sub> CC | -3     | 6    | 8    | ns   |                |

| Output hold time for CS                                                    | t <sub>24</sub> CC        | -3     | 6    | 11   | ns   |                |

| Data output hold time for<br>D15 D0 and AD15<br>AD0                        | <i>t</i> <sub>25</sub> CC | -3     | 6    | 8    | ns   |                |

| Input setup time for<br>READY, D15 D0, AD15<br>AD0                         | <i>t</i> <sub>30</sub> SR | 25     | 15   | -    | ns   |                |

| Input hold time READY,<br>D15 D0, AD15 AD0 <sup>1)</sup>                   | <i>t</i> <sub>31</sub> SR | 0      | -7   | -    | ns   |                |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can change after the rising edge of RD.

**Table 32** is valid under the following conditions:  $C_L$ = 20 pF; voltage\_range= lower; voltage\_range= lower

**Electrical Parameters**

Figure 24 Demultiplexed Bus Cycle

# 4.7.5.1 Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum

### Table 40 JTAG Interface Timing for Lower Voltage Range (cont'd)

|                                                                          |                           | -      |      | -    | - ·  | ,              |

|--------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

| Parameter                                                                | Symbol                    | Values |      |      | Unit | Note /         |

|                                                                          |                           | Min.   | Тур. | Max. |      | Test Condition |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6      | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>1)</sup>        | t <sub>8</sub> CC         | -      | 32   | 36   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>2)1)</sup> | t <sub>9</sub> CC         | -      | 32   | 36   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>1)</sup>   | <i>t</i> <sub>10</sub> CC | -      | 32   | 36   | ns   |                |

| TDO hold after TCK falling edge <sup>1)</sup>                            | <i>t</i> <sub>18</sub> CC | 5      | -    | -    | ns   |                |

1) The falling edge on TCK is used to generate the TDO timing.

2) The setup time for TDO is given implicitly by the TCK cycle time.

Figure 30 Test Clock Timing (TCK)

## Package and Reliability

# 5 Package and Reliability

The XE166 Family devices use the package type PG-LQFP (Plastic Green - Low Profile Quad Flat Package). The following specifications must be regarded to ensure proper integration of the XE164xN in its target environment.

## 5.1 Packaging

These parameters specify the packaging rather than the silicon.

| Parameter             | Symbol Limit     |      | nit Values | Unit | Notes                         |

|-----------------------|------------------|------|------------|------|-------------------------------|

|                       |                  | Min. | Max.       |      |                               |

| Exposed Pad Dimension | $E x \times E y$ | -    | 5.2 × 5.2  | mm   | -                             |

| Power Dissipation     | $P_{DISS}$       | -    | 0.8        | W    | -                             |

| Thermal resistance    | $R_{\Theta JA}$  | -    | 54         | K/W  | No thermal via <sup>1)</sup>  |

| Junction-Ambient      |                  |      | 49         | K/W  | 4-layer, no pad <sup>2)</sup> |

|                       |                  |      | 27         | K/W  | 4-layer, pad <sup>3)</sup>    |

## Table 41 Package Parameters (PG-LQFP-100-8)

1) Device mounted on a 4-layer board without thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad soldered to the board.

Note: To improve the EMC behavior, it is recommended to connect the exposed pad to the board ground, independent of the thermal requirements. Board layout examples are given in an application note.

## Package Compatibility Considerations

The XE164xN is a member of the XE166 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Pad (if present) may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.

www.infineon.com

Published by Infineon Technologies AG