Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                         |

| Core Processor            | C166SV2                                                                          |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 80MHz                                                                            |

| Connectivity              | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals               | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O             | 75                                                                               |

| Program Memory Size       | 128KB (128K x 8)                                                                 |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AAM Size                  | 18K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Oata Converters           | A/D 16x10b                                                                       |

| Oscillator Type           | Internal                                                                         |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type             | Surface Mount                                                                    |

| ackage / Case             | 100-LQFP Exposed Pad                                                             |

| upplier Device Package    | PG-LQFP-100-8                                                                    |

| urchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe164hn16f80laafxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

# **Table of Contents**

| Summary of Features  Device Types  Definition of Feature Variants                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Device Information  Pin Configuration and Definition Identification Registers                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Functional Description  Memory Subsystem and Organization External Bus Controller  Central Processing Unit (CPU)  Memory Protection Unit (MPU)  Memory Checker Module (MCHK) Interrupt System  On-Chip Debug Support (OCDS)  Capture/Compare Unit (CC2)  Capture/Compare Units CCU6x  General Purpose Timer (GPT12E) Unit  Real Time Clock  A/D Converters  Universal Serial Interface Channel Modules (USIC)  MultiCAN Module  System Timer  Watchdog Timer  Clock Generation  Parallel Ports  Instruction Set Summary | 38<br>42<br>43<br>45<br>46<br>47<br>48<br>51<br>53<br>57<br>59<br>60<br>62<br>63<br>64<br>65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Electrical Parameters General Parameters Operating Conditions Voltage Range definitions Parameter Interpretation DC Parameters DC Parameters for Upper Voltage Area DC Parameters for Lower Voltage Area Power Consumption Analog/Digital Converter Parameters System Parameters Flash Memory Parameters AC Parameters                                                                                                                                                                                                  | 69<br>70<br>72<br>73<br>75<br>77<br>79<br>83<br>87<br>90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Device Types Definition of Feature Variants  General Device Information Pin Configuration and Definition Identification Registers  Functional Description Memory Subsystem and Organization External Bus Controller Central Processing Unit (CPU) Memory Protection Unit (MPU) Memory Checker Module (MCHK) Interrupt System On-Chip Debug Support (OCDS) Capture/Compare Unit (CC2) Capture/Compare Units CCU6x General Purpose Timer (GPT12E) Unit Real Time Clock A/D Converters Universal Serial Interface Channel Modules (USIC) MultiCAN Module System Timer Watchdog Timer Clock Generation Parallel Ports Instruction Set Summary  Electrical Parameters General Parameters General Parameters Operating Conditions Voltage Range definitions Parameter Interpretation DC Parameters or Upper Voltage Area DC Parameters for Upper Voltage Area Power Consumption Analog/Digital Converter Parameters System Parameters |

**Summary of Features**

16-Bit Single-Chip Real Time Signal Controller XE164xN (XE166 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XE164xN are summarized here.

- · High-performance CPU with five-stage pipeline and MPU

- 12.5 ns instruction cycle @ 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1,024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- Interrupt system with 16 priority levels providing 96 interrupt nodes

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 16 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 320 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

### **Summary of Features**

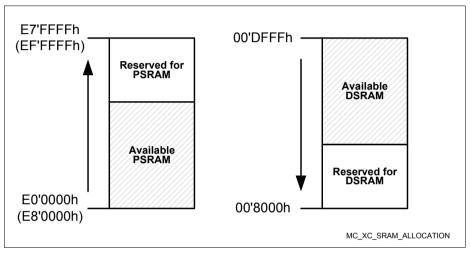

The XE164xN types are offered with several SRAM memory sizes. Figure 1 shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

### **General Device Information**

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol    | Ctrl.      | Type | Function                                       |

|-----|-----------|------------|------|------------------------------------------------|

| 39  | P2.0      | O0 / I     | St/B | Bit 0 of Port 2, General Purpose Input/Output  |

|     | AD13      | OH /<br>IH | St/B | External Bus Interface Address/Data Line 13    |

|     | RxDC0C    | I          | St/B | CAN Node 0 Receive Data Input                  |

|     | T5INB     | I          | St/B | GPT12E Timer T5 Count/Gate Input               |

| 40  | P2.1      | O0 / I     | St/B | Bit 1 of Port 2, General Purpose Input/Output  |

|     | TxDC0     | 01         | St/B | CAN Node 0 Transmit Data Output                |

|     | AD14      | OH /<br>IH | St/B | External Bus Interface Address/Data Line 14    |

|     | T5EUDB    | I          | St/B | GPT12E Timer T5 External Up/Down Control Input |

|     | ESR1_5    | I          | St/B | ESR1 Trigger Input 5                           |

| 41  | P2.2      | O0 / I     | St/B | Bit 2 of Port 2, General Purpose Input/Output  |

|     | TxDC1     | 01         | St/B | CAN Node 1 Transmit Data Output                |

|     | AD15      | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15    |

|     | ESR2_5    | I          | St/B | ESR2 Trigger Input 5                           |

| 42  | P4.0      | O0 / I     | St/B | Bit 0 of Port 4, General Purpose Input/Output  |

|     | CC2_CC24  | O3 / I     | St/B | CAPCOM2 CC24IO Capture Inp./ Compare Out.      |

|     | CS0       | ОН         | St/B | External Bus Interface Chip Select 0 Output    |

| 43  | P2.3      | O0 / I     | St/B | Bit 3 of Port 2, General Purpose Input/Output  |

|     | U0C0_DOUT | 01         | St/B | USIC0 Channel 0 Shift Data Output              |

|     | CC2_CC16  | O3 / I     | St/B | CAPCOM2 CC16IO Capture Inp./ Compare Out.      |

|     | A16       | ОН         | St/B | External Bus Interface Address Line 16         |

|     | ESR2_0    | I          | St/B | ESR2 Trigger Input 0                           |

|     | U0C0_DX0E | I          | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U0C1_DX0D | I          | St/B | USIC0 Channel 1 Shift Data Input               |

|     | RxDC0A    | I          | St/B | CAN Node 0 Receive Data Input                  |

### **General Device Information**

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----|------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 92  | P1.5             | O0 / I | St/B | Bit 5 of Port 1, General Purpose Input/Output                                                                                                                                                                                                                                                                        |  |  |  |

|     | U1C1_SELO<br>3   | O2     | St/B | USIC1 Channel 1 Select/Control 3 Output                                                                                                                                                                                                                                                                              |  |  |  |

|     | BRKOUT           | О3     | St/B | OCDS Break Signal Output                                                                                                                                                                                                                                                                                             |  |  |  |

|     | A13              | ОН     | St/B | External Bus Interface Address Line 13                                                                                                                                                                                                                                                                               |  |  |  |

|     | U2C0_DX0C        | I      | St/B | USIC2 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |  |

| 93  | P1.6             | O0 / I | St/B | Bit 6 of Port 1, General Purpose Input/Output                                                                                                                                                                                                                                                                        |  |  |  |

|     | U1C1_SELO<br>2   | O2     | St/B | USIC1 Channel 1 Select/Control 2 Output                                                                                                                                                                                                                                                                              |  |  |  |

|     | U2C0_DOUT        | О3     | St/B | USIC2 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                                    |  |  |  |

|     | A14              | ОН     | St/B | External Bus Interface Address Line 14                                                                                                                                                                                                                                                                               |  |  |  |

|     | U2C0_DX0D        | I      | St/B | USIC2 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |  |

| 94  | P1.7             | O0 / I | St/B | Bit 7 of Port 1, General Purpose Input/Output                                                                                                                                                                                                                                                                        |  |  |  |

|     | U1C1_MCLK<br>OUT | O2     | St/B | USIC1 Channel 1 Master Clock Output                                                                                                                                                                                                                                                                                  |  |  |  |

|     | U2C0_SCLK<br>OUT | О3     | St/B | USIC2 Channel 0 Shift Clock Output                                                                                                                                                                                                                                                                                   |  |  |  |

|     | A15              | ОН     | St/B | External Bus Interface Address Line 15                                                                                                                                                                                                                                                                               |  |  |  |

|     | U2C0_DX1C        | I      | St/B | USIC2 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                    |  |  |  |

| 95  | XTAL2            | 0      | Sp/M | Crystal Oscillator Amplifier Output                                                                                                                                                                                                                                                                                  |  |  |  |

| 96  | XTAL1            | 1      | Sp/M | Crystal Oscillator Amplifier Input To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Voltages on XTAL1 must comply to the core supply voltage $V_{\rm DDIM}$ .                                                                                                              |  |  |  |

|     | ESR2_9           | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                                                                                                                                 |  |  |  |

| 97  | PORST            | I      | In/B | Power On Reset Input A low level at this pin resets the XE164xN completely. A spike filter suppresses input pulses <10 ns. Input pulses >100 ns safely pass the filter. The minimum duration for a safe recognition should be 120 ns. An internal pull-up device will hold this pin high when nothing is driving it. |  |  |  |

#### **General Device Information**

## 2.2 Identification Registers

The identification registers describe the current version of the XE164xN and of its modules.

Table 6 XE164xN Identification Registers

| Short Name  | Value                  | Address              | Notes                   |

|-------------|------------------------|----------------------|-------------------------|

| SCU_IDMANUF | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |                         |

| SCU_IDCHIP  | 3001 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking EES-AA or ES-AA |

|             | 3002 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking AA, AB          |

| SCU_IDMEM   | 304F <sub>H</sub>      | 00'F07A <sub>H</sub> |                         |

| SCU_IDPROG  | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |                         |

| JTAG_ID     | 0018'B083 <sub>H</sub> |                      | marking EES-AA or ES-AA |

|             | 1018'B083 <sub>H</sub> |                      | marking AA, AB          |

Data Sheet 36 V1.4, 2013-02

**Functional Description**

# 3 Functional Description

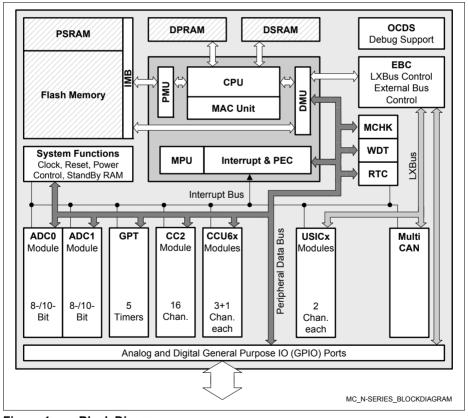

The architecture of the XE164xN combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XE164xN.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XE164xN.

Figure 4 Block Diagram

### **Functional Description**

### **Memory Content Protection**

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

### **Functional Description**

Table 8 Compare Modes (cont'd)

| Compare Modes           | Function                                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Mode 2                  | Interrupt-only compare mode; Only one compare interrupt per timer period is generated                                     |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated    |

| Double Register<br>Mode | Two registers operate on one pin; Pin toggles on each compare match; Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses; Can be used with any compare mode                                                       |

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the compare mode selected.

### **Functional Description**

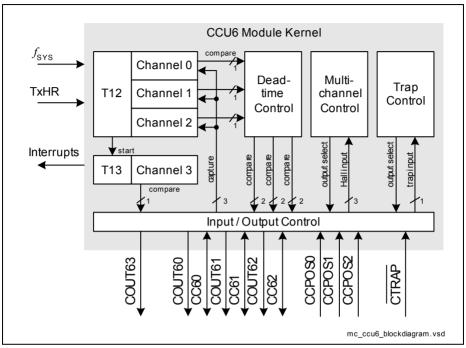

Figure 7 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

### **Functional Description**

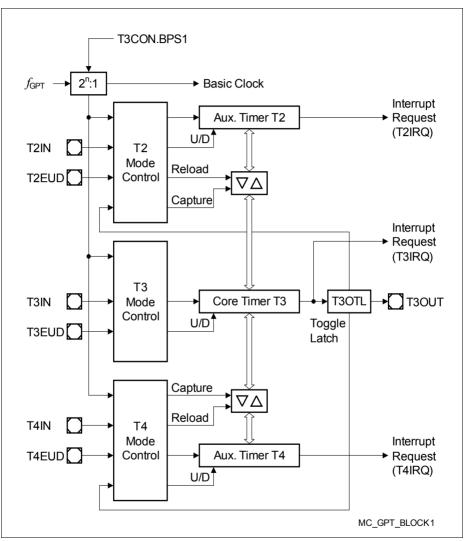

Figure 8 Block Diagram of GPT1

### **Functional Description**

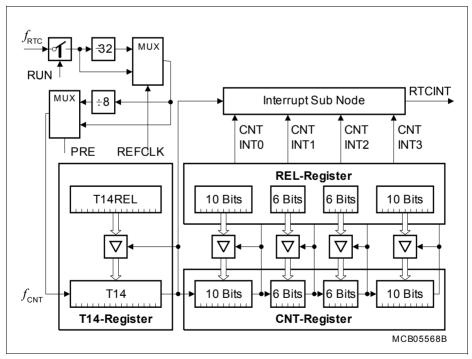

#### 3.11 Real Time Clock

The Real Time Clock (RTC) module of the XE164xN can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

### **Functional Description**

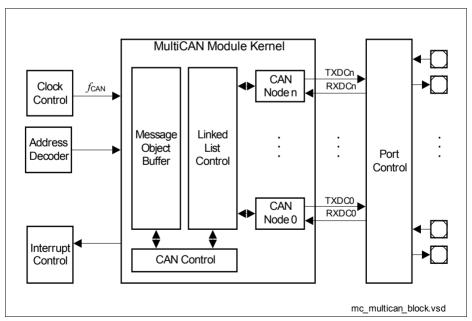

#### 3.14 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 12 Block Diagram of MultiCAN Module

## **Functional Description**

Table 10 Instruction Set Summary (cont'd)

| Mnemonic     | Description                         | Bytes |

|--------------|-------------------------------------|-------|

| NOP          | Null operation                      | 2     |

| CoMUL/CoMAC  | Multiply (and accumulate)           | 4     |

| CoADD/CoSUB  | Add/Subtract                        | 4     |

| Co(A)SHR     | (Arithmetic) Shift right            | 4     |

| CoSHL        | Shift left                          | 4     |

| CoLOAD/STORE | Load accumulator/Store MAC register | 4     |

| CoCMP        | Compare                             | 4     |

| CoMAX/MIN    | Maximum/Minimum                     | 4     |

| CoABS/CoRND  | Absolute value/Round accumulator    | 4     |

| CoMOV        | Data move                           | 4     |

| CoNEG/NOP    | Negate accumulator/Null operation   | 4     |

The Enter Power Down Mode instruction is not used in the XE164xN, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

#### **Electrical Parameters**

# 4.1.1 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XE164xN. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

Table 12 Operating Conditions

| Parameter                                                        | Symbol                                                  |      | Values                    | \$                        | Unit | Note /                                                 |

|------------------------------------------------------------------|---------------------------------------------------------|------|---------------------------|---------------------------|------|--------------------------------------------------------|

|                                                                  |                                                         | Min. | Тур.                      | Max.                      |      | Test Condition                                         |

| Voltage Regulator Buffer Capacitance for DMP_M                   | $\begin{array}{c} C_{\rm EVRM} \\ {\rm SR} \end{array}$ | 1.0  | -                         | 4.7                       | μF   | 1)                                                     |

| Voltage Regulator Buffer Capacitance for DMP_1                   | $C_{\mathrm{EVR1}}$ SR                                  | 0.47 | -                         | 2.2                       | μF   | 2)1)                                                   |

| External Load<br>Capacitance                                     | $C_{L}$ SR                                              | _    | 203)                      | _                         | pF   | pin out<br>driver= default                             |

| System frequency                                                 | $f_{\rm SYS}{\rm SR}$                                   | -    | _                         | 80                        | MHz  | 5)                                                     |

| Overload current for analog inputs <sup>6)</sup>                 | $I_{OVA}SR$                                             | -2   | _                         | 5                         | mA   | not subject to production test                         |

| Overload current for digital inputs <sup>6)</sup>                | $I_{\mathrm{OVD}}\mathrm{SR}$                           | -5   | -                         | 5                         | mA   | not subject to production test                         |

| Overload current coupling factor for analog inputs <sup>7)</sup> | K <sub>OVA</sub><br>CC                                  | _    | 2.5 x<br>10 <sup>-4</sup> | 1.5 x<br>10 <sup>-3</sup> | -    | $I_{\rm OV}$ < 0 mA; not subject to production test    |

|                                                                  |                                                         | _    | 1.0 x<br>10 <sup>-6</sup> | 1.0 x<br>10 <sup>-4</sup> | -    | I <sub>OV</sub> > 0 mA; not subject to production test |

#### **Electrical Parameters**

## 4.3.2 DC Parameters for Lower Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

**Table 16** is valid under the following conditions:  $V_{\rm DDP} \ge 3.0 \, \rm V; \ V_{\rm DDP} \ typ. \ 3.3 \, \rm V; \ V_{\rm DDP} \le 4.5 \, \rm V$

Table 16 DC Characteristics for Lower Voltage Range

| Parameter                                                                                                | Symbol                   |                                                                | Values |                                   | Unit | Note /                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------|--------|-----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                          |                          | Min.                                                           | Тур.   | Max.                              |      | Test Condition                                                                                                                                           |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. 1)                         | C <sub>IO</sub> CC       | _                                                              | _      | 10                                | pF   | not subject to production test                                                                                                                           |

| Input Hysteresis <sup>2)</sup>                                                                           | HYS CC                   | $\begin{matrix} 0.07 \text{ x} \\ V_{\text{DDP}} \end{matrix}$ | -      | _                                 | V    | R <sub>S</sub> = 0 Ohm                                                                                                                                   |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                                     | I <sub>OZ1</sub>  <br>CC | _                                                              | 10     | 200                               | nA   | $V_{\rm IN}$ > $V_{\rm SS}$ ; $V_{\rm IN}$ < $V_{\rm DDP}$                                                                                               |

| Absolute input leakage current for all other pins. To be doubled for double bond pins. <sup>3)1)4)</sup> | I <sub>OZ2</sub>  <br>CC | _                                                              | 0.2    | 2.5                               | μΑ   | $T_{\rm J} \le$ 110 °C;<br>$V_{\rm IN} > V_{\rm SS}$ ;<br>$V_{\rm IN} < V_{\rm DDP}$                                                                     |

|                                                                                                          |                          | _                                                              | 0.2    | 8                                 | μА   | $T_{\rm J} \le$ 150 °C;<br>$V_{\rm IN} > V_{\rm SS}$ ;<br>$V_{\rm IN} < V_{\rm DDP}$                                                                     |

| Pull Level Force Current <sup>5)</sup>                                                                   | $ I_{\rm PLF} $ SR       | 150                                                            | _      | _                                 | μА   | $ \begin{aligned} &V_{\text{IN}} \!\! \geq V_{\text{IHmin}}(pull\\ &down) \ ;\\ &V_{\text{IN}} \!\! \leq V_{\text{ILmax}}(pull\\ &up) \end{aligned} $    |

| Pull Level Keep Current <sup>6)</sup>                                                                    | I <sub>PLK</sub>  <br>SR | -                                                              | _      | 10                                | μА   | $ \begin{aligned} &V_{\text{IN}} \!\! \geq V_{\text{IHmin}}(pull \\ &up) \ ; \\ &V_{\text{IN}} \!\! \leq V_{\text{ILmax}}(pull \\ &down) \end{aligned} $ |

| Input high voltage (all except XTAL1)                                                                    | $V_{IH}SR$               | $V_{\rm DDP}$                                                  | _      | <i>V</i> <sub>DDP</sub> + 0.3     | V    |                                                                                                                                                          |

| Input low voltage (all except XTAL1)                                                                     | $V_{IL}SR$               | -0.3                                                           | -      | $0.3~\mathrm{x}$ $V_\mathrm{DDP}$ | V    |                                                                                                                                                          |

#### **Electrical Parameters**

Table 16 DC Characteristics for Lower Voltage Range (cont'd)

| Parameter                         | Symbol     |                        | Value | s    | Unit | Note /<br>Test Condition                  |

|-----------------------------------|------------|------------------------|-------|------|------|-------------------------------------------|

|                                   |            | Min.                   | Тур.  | Max. |      |                                           |

| Output High voltage <sup>7)</sup> | $V_{OH}CC$ | V <sub>DDP</sub> - 1.0 | _     | -    | V    | $I_{\mathrm{OH}} \geq I_{\mathrm{OHmax}}$ |

|                                   |            | V <sub>DDP</sub> - 0.4 | -     | -    | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{8)}$ |

| Output Low Voltage <sup>7)</sup>  | $V_{OL}CC$ | -                      | _     | 0.4  | V    | $I_{\rm OL} \le I_{\rm OLnom}^{8)}$       |

|                                   |            | _                      | -     | 1.0  | ٧    | $I_{OL} \leq I_{OLmax}$                   |

- Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

- Not subject to production test verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing  $(V_{\rm IN} < V_{\rm SS})$  or supply ripple  $(V_{\rm IN} > V_{\rm DDP})$ , a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current  $(I_{\rm INJ})$  will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm DV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (T<sub>J</sub> = junction temperature [°C]): I<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x TJ-)</sup> [μA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 μA. Leakage derating depending on voltage level (DV = V<sub>DDP</sub> V<sub>PIN</sub> [V]): I<sub>OZ</sub> = I<sub>OZtempmax</sub> (1.6 x DV) (μA]. This voltage derating formula is an approximation which applies for maximum temperature.

- 5) Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device: V<sub>PIN</sub> <= V<sub>IL</sub> for a pullup; V<sub>PIN</sub> >= V<sub>IH</sub> for a pulldown.

- 6) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> >= V<sub>IH</sub> for a pullup; V<sub>PIN</sub> <= V<sub>II</sub> for a pulldown.

- 7) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 8) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{\rm OL}$ -> $V_{\rm SS}$ ,  $V_{\rm OH}$ -> $V_{\rm DDP}$ ). However, only the levels for nominal output currents are verified.

#### **Electrical Parameters**

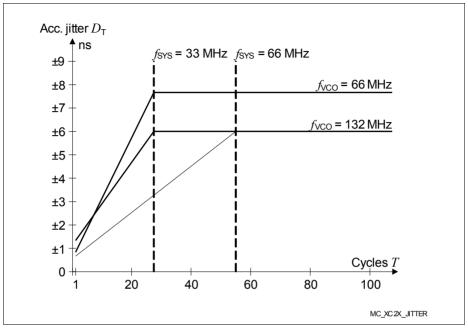

Figure 20 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_1 = 20$  pF.

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{\rm DDPB}$  pin 100 and  $V_{\rm SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{\rm PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

### PLL frequency band selection

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

#### **Electrical Parameters**

### 4.7.5 External Bus Timing

The following parameters specify the behavior of the XE164xN bus interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

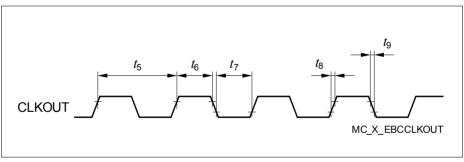

Table 29 Parameters

| Parameter                       | Symbol            |      | Values               |      | Unit | Note /<br>Test Condition |

|---------------------------------|-------------------|------|----------------------|------|------|--------------------------|

|                                 |                   | Min. | Тур.                 | Max. |      |                          |

| CLKOUT Cycle Time <sup>1)</sup> | t <sub>5</sub> CC | -    | 1 / f <sub>SYS</sub> | _    | ns   |                          |

| CLKOUT high time                | t <sub>6</sub> CC | 3    | _                    | _    |      |                          |

| CLKOUT low time                 | t <sub>7</sub> CC | 3    | _                    | _    |      |                          |

| CLKOUT rise time                | t <sub>8</sub> CC | -    | _                    | 3    | ns   |                          |

| CLKOUT fall time                | t <sub>9</sub> CC | -    | _                    | 3    |      |                          |

The CLKOUT cycle time is influenced by PLL jitter. For longer periods the relative deviation decreases (see PLL deviation formula).

Figure 22 CLKOUT Signal Timing

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{\rm SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

#### **Electrical Parameters**

### 4.7.7 Debug Interface Timing

The debugger can communicate with the XE164xN either via the 2-pin DAP interface or via the standard JTAG interface.

### Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 37** is valid under the following conditions:  $C_L$  = 20 pF; voltage\_range= upper

Table 37 DAP Interface Timing for Upper Voltage Range

| Parameter                                      | Symbol             | ol Values |      |      | Unit | Note /         |

|------------------------------------------------|--------------------|-----------|------|------|------|----------------|

|                                                |                    | Min.      | Тур. | Max. |      | Test Condition |

| DAP0 clock period <sup>1)</sup>                | t <sub>11</sub> SR | 25        | _    | _    | ns   |                |

| DAP0 high time                                 | t <sub>12</sub> SR | 8         | _    | _    | ns   |                |

| DAP0 low time <sup>1)</sup>                    | t <sub>13</sub> SR | 8         | _    | _    | ns   |                |

| DAP0 clock rise time                           | t <sub>14</sub> SR | -         | _    | 4    | ns   |                |

| DAP0 clock fall time                           | t <sub>15</sub> SR | -         | _    | 4    | ns   |                |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR | 6         | -    | _    | ns   |                |

| DAP1 hold after DAP0 rising edge               | t <sub>17</sub> SR | 6         | -    | _    | ns   |                |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC | 17        | 20   | -    | ns   |                |

<sup>1)</sup> See the DAP chapter for clock rate restrictions in the Active::IDLE protocol state.

**Table 38** is valid under the following conditions:  $C_L$ = 20 pF; voltage\_range= lower

Data Sheet 116 V1.4, 2013-02

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.