Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | S08                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 26                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08rna32w0mlcr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Input/Output

- Up to 55 GPIOs including one output-only pin

- Two 8-bit keyboard interrupt modules (KBI)

- Two true open-drain output pins

- Eight, ultra-high current sink pins supporting 20 mA source/sink current

- Package options

- 64-pin LQFP

- 48-pin LQFP

- 32-pin LQFP

# 1 Ordering parts

## 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to www.freescale.com and perform a part number search for the following device numbers: RN60, RN48 and RN32.

### 2 Part identification

## 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

#### 2.2 Format

Part numbers for this device have the following format:

S 9 S08 RN AA F1 B CC

### 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                  | Values                                                                 |

|-------|------------------------------|------------------------------------------------------------------------|

| s     | Qualification status         | S = fully qualified, general market flow                               |

| 9     | Memory                       | 9 = flash based                                                        |

| S08   | Core                         | • S08 = 8-bit CPU                                                      |

| RN    | Device family                | • RN                                                                   |

| AA    | Approximate flash size in KB | <ul> <li>60 = 60 KB</li> <li>48 = 48 KB</li> <li>32 = 32 KB</li> </ul> |

| F1    | Fab and mask set identifier  | • W1                                                                   |

| В     | Temperature range (°C)       | • M = -40 to 125                                                       |

| Field | Description        | Values                                                                                   |  |  |

|-------|--------------------|------------------------------------------------------------------------------------------|--|--|

| CC    | Package designator | <ul> <li>LH = 64-pin LQFP</li> <li>LF = 48-pin LQFP</li> <li>LC = 32-pin LQFP</li> </ul> |  |  |

## 2.4 Example

This is an example part number:

S9S08RN60W1MLH

### 3 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

**Table 1. Parameter Classifications**

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 4 Ratings

# 4.1 Thermal handling ratings

| Symbol           | Description                   | Min.        | Max. | Unit | Notes |

|------------------|-------------------------------|-------------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | <b>-</b> 55 | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _           | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

| Symbol         | Description                                                                             | Min.                  | Max.                  | Unit |

|----------------|-----------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| $V_{DIO}$      | Digital input voltage (except RESET, EXTAL, XTAL, or true open drain pin PTA2 and PTA3) | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

|                | Digital input voltage (true open drain pin PTA2 and PTA3)                               | -0.3                  | 6                     | V    |

| $V_{AIO}$      | Analog <sup>1</sup> , RESET, EXTAL, and XTAL input voltage                              | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>D</sub> | Instantaneous maximum current single pin limit (applies to all port pins)               | -25                   | 25                    | mA   |

| $V_{DDA}$      | Analog supply voltage                                                                   | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

<sup>1.</sup> All digital I/O pins, except open-drain pin PTA2 and PTA3, are internally clamped to  $V_{SS}$  and  $V_{DD}$ . PTA2 and PTA3 is only clamped to  $V_{SS}$ .

#### 5 General

# 5.1 Nonswitching electrical specifications

#### 5.1.1 DC characteristics

This section includes information about power supply requirements and I/O pin characteristics.

**Symbol** C **Descriptions** Min Typical<sup>1</sup> Max Unit Operating voltage 2.7 5.5 V  $V_{OH}$ С Output high All I/O pins, standard-5 V,  $I_{load} =$  $V_{DD} - 0.8$ ٧ drive strength voltage -5 mA V С 3 V,  $I_{load} =$  $V_{DD} - 0.8$ -2.5 mA 5 V,  $I_{load} =$ С High current drive  $V_{DD} - 0.8$ ٧ pins, high-drive -20 mA strength<sup>2, 2</sup> 3 V,  $I_{load}$  = С V<sub>DD</sub> - 0.8 ٧ -10 mA 5 V I<sub>OHT</sub> D Output high Max total I<sub>OH</sub> for all -100 mΑ current ports 3 V -50  $V_{OL}$ С Output low All I/O pins, standard-5 V,  $I_{load} = 5$ 8.0 ٧ voltage drive strength mΑ ٧ С 3 V,  $I_{load} =$ 8.0 2.5 mA ٧ С High current drive 5 V, I<sub>load</sub> 8.0 pins, high-drive =20 mA strength<sup>2</sup> 3 V,  $I_{load} =$ ٧ С 8.0 10 mA

Table 2. DC characteristics

### Table 3. LVD and POR Specification (continued)

| Symbol              | С | Descr                                | ription                                           | Min  | Тур  | Max  | Unit |

|---------------------|---|--------------------------------------|---------------------------------------------------|------|------|------|------|

| V <sub>LVDH</sub>   | С |                                      | oltage detect<br>h range (LVDV<br>1) <sup>3</sup> | 4.2  | 4.3  | 4.4  | V    |

| V <sub>LVW1H</sub>  | С | Falling low-<br>voltage              | Level 1 falling<br>(LVWV = 00)                    | 4.3  | 4.4  | 4.5  | V    |

| V <sub>LVW2H</sub>  | С | warning<br>threshold -<br>high range | Level 2 falling<br>(LVWV = 01)                    | 4.5  | 4.5  | 4.6  | V    |

| V <sub>LVW3H</sub>  | С | High range                           | Level 3 falling<br>(LVWV = 10)                    | 4.6  | 4.6  | 4.7  | V    |

| V <sub>LVW4H</sub>  | С |                                      | Level 4 falling<br>(LVWV = 11)                    | 4.7  | 4.7  | 4.8  | V    |

| V <sub>HYSH</sub>   | С |                                      | low-voltage<br>ng hysteresis                      | _    | 100  | _    | mV   |

| V <sub>LVDL</sub>   | С |                                      | oltage detect<br>range (LVDV =                    | 2.56 | 2.61 | 2.66 | V    |

| V <sub>LVDW1L</sub> | С | Falling low-<br>voltage              | Level 1 falling<br>(LVWV = 00)                    | 2.62 | 2.7  | 2.78 | V    |

| V <sub>LVDW2L</sub> | С | warning<br>threshold -<br>low range  | Level 2 falling<br>(LVWV = 01)                    | 2.72 | 2.8  | 2.88 | V    |

| V <sub>LVDW3L</sub> | С | low range                            | Level 3 falling<br>(LVWV = 10)                    | 2.82 | 2.9  | 2.98 | V    |

| V <sub>LVDW4L</sub> | С |                                      | Level 4 falling<br>(LVWV = 11)                    | 2.92 | 3.0  | 3.08 | V    |

| V <sub>HYSDL</sub>  | С | Low range low hyste                  | -voltage detect<br>eresis                         | _    | 40   | _    | mV   |

| V <sub>HYSWL</sub>  | С | Low range<br>warning h               | low-voltage<br>nysteresis                         | _    | 80   | _    | mV   |

| V <sub>BG</sub>     | Р | Buffered band                        | dgap output 4                                     | 1.14 | 1.16 | 1.18 | V    |

- 1. Maximum is highest voltage that POR is guaranteed.

- 2. POR ramp time must be longer than 20us/V to get a stable startup.

- 3. Rising thresholds are falling threshold + hysteresis.

- 4. Voltage factory trimmed at  $V_{DD}$  = 5.0 V, Temp = 125 °C

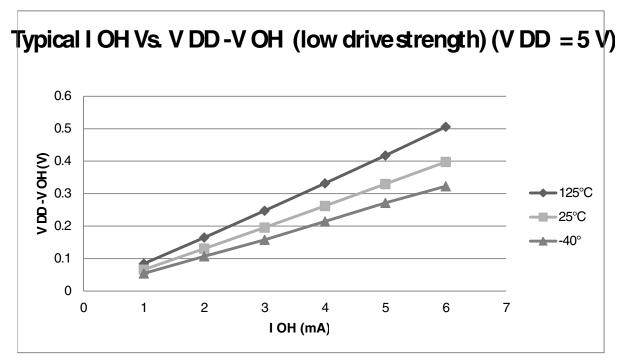

Figure 1. Typical  $I_{OH}$  Vs.  $V_{DD}$ - $V_{OH}$  (standard drive strength) ( $V_{DD}$  = 5 V)

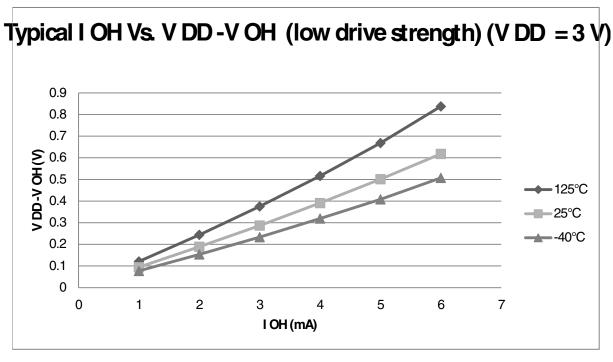

Figure 2. Typical  $I_{OH}$  Vs.  $V_{DD}$ - $V_{OH}$  (standard drive strength) ( $V_{DD}$  = 3 V)

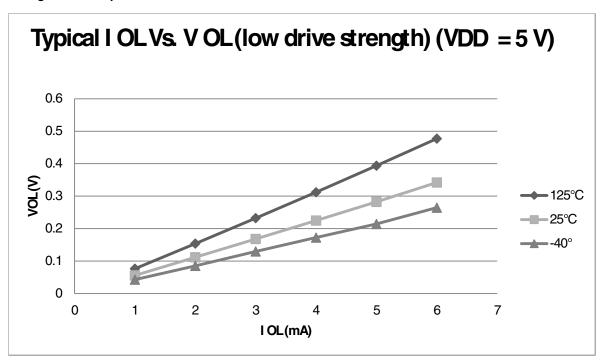

Figure 5. Typical  $I_{OL}$  Vs.  $V_{OL}$  (standard drive strength) ( $V_{DD} = 5 \text{ V}$ )

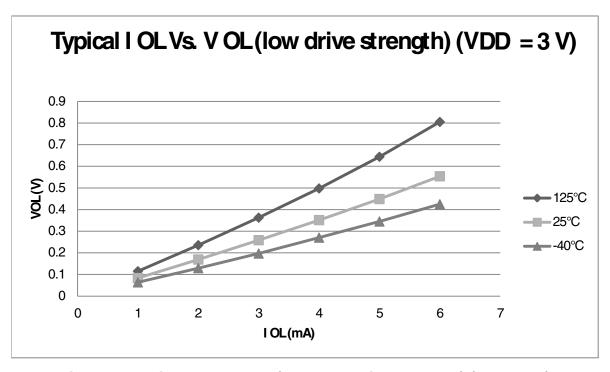

Figure 6. Typical  $I_{OL}$  Vs.  $V_{OL}$  (standard drive strength) ( $V_{DD} = 3 \text{ V}$ )

# 5.1.2 Supply current characteristics

This section includes information about power supply current in various operating modes.

Table 4. Supply current characteristics

| Num | С | Parameter                                                               | Symbol            | Bus Freq | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max  | Unit | Temp          |

|-----|---|-------------------------------------------------------------------------|-------------------|----------|---------------------|----------------------|------|------|---------------|

| 1   | С | Run supply current FEI                                                  | RI <sub>DD</sub>  | 20 MHz   | 5                   | 12.6                 | _    | mA   | -40 to 125 °C |

|     | С | mode, all modules on; run<br>from flash                                 |                   | 10 MHz   |                     | 7.2                  | _    |      |               |

|     |   | Hom hash                                                                |                   | 1 MHz    |                     | 2.4                  | _    |      |               |

|     | С |                                                                         |                   | 20 MHz   | 3                   | 9.6                  | _    |      |               |

|     | С |                                                                         |                   | 10 MHz   |                     | 6.1                  | _    |      |               |

|     |   |                                                                         |                   | 1 MHz    |                     | 2.1                  | _    |      |               |

| 2   | С | Run supply current FEI                                                  | RI <sub>DD</sub>  | 20 MHz   | 5                   | 10.5                 | _    | mA   | -40 to 125 °C |

|     | С | mode, all modules off & gated; run from flash                           |                   | 10 MHz   |                     | 6.2                  | _    |      |               |

|     |   | gated, full from flash                                                  |                   | 1 MHz    |                     | 2.3                  | _    |      |               |

|     | С |                                                                         |                   | 20 MHz   | 3                   | 7.4                  | _    |      |               |

|     | С |                                                                         |                   | 10 MHz   |                     | 5.0                  | _    |      |               |

|     |   |                                                                         |                   | 1 MHz    |                     | 2.0                  | _    |      |               |

| 3   | Р | Run supply current FBE                                                  | $RI_{DD}$         | 20 MHz   | 5                   | 12.1                 | 14.8 | mA   | -40 to 125 °C |

|     | С | mode, all modules on; run<br>from RAM                                   |                   | 10 MHz   |                     | 6.5                  | _    |      |               |

|     |   | IIOIII I IAWI                                                           |                   | 1 MHz    |                     | 1.8                  | _    |      |               |

|     | Р |                                                                         |                   | 20 MHz   | 3                   | 9.1                  | 11.8 |      |               |

|     | С |                                                                         |                   | 10 MHz   |                     | 5.5                  | _    |      |               |

|     |   |                                                                         |                   | 1 MHz    |                     | 1.5                  | _    |      |               |

| 4   | Р | Run supply current FBE                                                  | RI <sub>DD</sub>  | 20 MHz   | 5                   | 9.8                  | 12.3 | mA   | -40 to 125 °C |

|     | С | mode, all modules off & gated; run from RAM                             |                   | 10 MHz   |                     | 5.4                  | _    |      |               |

|     |   | gated, full from that                                                   |                   | 1 MHz    |                     | 1.6                  | _    |      |               |

|     | Р |                                                                         |                   | 20 MHz   | 3                   | 6.9                  | 9.2  |      |               |

|     | С |                                                                         |                   | 10 MHz   |                     | 4.4                  | _    |      |               |

|     |   |                                                                         |                   | 1 MHz    |                     | 1.4                  | _    |      |               |

| 5   | С | Wait mode current FEI                                                   | WI <sub>DD</sub>  | 20 MHz   | 5                   | 7.8                  | _    | mA   | -40 to 125 °C |

|     | С | mode, all modules on                                                    |                   | 10 MHz   |                     | 4.5                  | _    |      |               |

|     |   |                                                                         |                   | 1 MHz    |                     | 1.3                  | _    |      |               |

|     | С |                                                                         |                   | 20 MHz   | 3                   | 5.1                  | _    |      |               |

|     |   |                                                                         |                   | 10 MHz   |                     | 3.5                  | _    |      |               |

|     |   |                                                                         |                   | 1 MHz    |                     | 1.2                  | _    |      |               |

| 6   | С | Stop3 mode supply                                                       | S3I <sub>DD</sub> | _        | 5                   | 3.8                  | _    | μΑ   | -40 to 125 °C |

|     | С | current no clocks active<br>(except 1 kHz LPO<br>clock) <sup>2, 3</sup> |                   | _        | 3                   | 3                    | _    |      | -40 to 125 °C |

| Table 4. | Supply current | characteristics ( | (continued) |

|----------|----------------|-------------------|-------------|

|----------|----------------|-------------------|-------------|

| Num | С | Parameter                       | Symbol | Bus Freq | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max | Unit | Temp          |

|-----|---|---------------------------------|--------|----------|---------------------|----------------------|-----|------|---------------|

| 7   | С | ADC adder to stop3              | _      | _        | 5                   | 44                   | _   | μΑ   | -40 to 125 °C |

|     | С | ADLPC = 1                       |        |          | 3                   | 40                   | _   |      |               |

|     |   | ADLSMP = 1                      |        |          |                     |                      |     |      |               |

|     |   | ADCO = 1                        |        |          |                     |                      |     |      |               |

|     |   | MODE = 10B                      |        |          |                     |                      |     |      |               |

|     |   | ADICLK = 11B                    |        |          |                     |                      |     |      |               |

| 8   | С | TSI adder to stop34             | _      | _        | 5                   | 111                  | _   | μΑ   | -40 to 125 °C |

|     | С | PS = 010B                       |        |          | 3                   | 110                  | _   |      |               |

|     |   | NSCN =0x0F                      |        |          |                     |                      |     |      |               |

|     |   | EXTCHRG = 0                     |        |          |                     |                      |     |      |               |

|     |   | REFCHRG = 0                     |        |          |                     |                      |     |      |               |

|     |   | DVOLT = 01B                     |        |          |                     |                      |     |      |               |

| 9   | С | LVD adder to stop3 <sup>5</sup> | _      | _        | 5                   | 130                  |     | μΑ   | -40 to 125 °C |

|     | С |                                 |        |          | 3                   | 125                  |     |      |               |

- 1. Data in Typical column was characterized at 5.0 V, 25 °C or is typical recommended value.

- 2. RTC adder cause <1 μA I<sub>DD</sub> increase typically, RTC clock source is 1 kHz LPO clock.

- 3. ACMP adder cause <1  $\mu$ A I<sub>DD</sub> increase typically.

- 4. The current varies with TSI configuration and capacity of touch electrode. Please refer to TSI electrical specifications.

- 5. LVD is periodically woken up from stop3 by 5% duty cycle. The period is equal to or less than 2 ms.

### 5.1.3 EMC performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

## 5.1.3.1 EMC radiated emissions operating behaviors

# 5.2 Switching specifications

## 5.2.1 Control timing

Table 5. Control timing

| Num | С | Rating                                                                         |                   | Symbol              | Min                     | Typical <sup>1</sup> | Max  | Unit |

|-----|---|--------------------------------------------------------------------------------|-------------------|---------------------|-------------------------|----------------------|------|------|

| 1   | Р | Bus frequency (t <sub>cyc</sub> = 1/f <sub>Bus</sub> )                         | f <sub>Bus</sub>  | DC                  | _                       | 20                   | MHz  |      |

| 2   | Р | Internal low power oscillator                                                  | frequency         | f <sub>LPO</sub>    | 0.67                    | 1.0                  | 1.25 | KHz  |

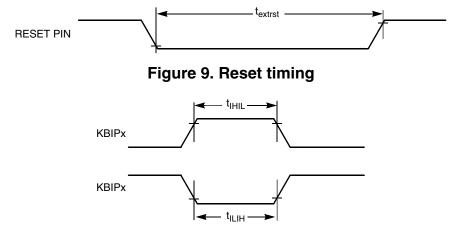

| 3   | D | External reset pulse width <sup>2,</sup>                                       | 2                 | t <sub>extrst</sub> | 1.5 ×                   | _                    | _    | ns   |

|     |   |                                                                                |                   |                     | t <sub>Self_reset</sub> |                      |      |      |

| 4   | D | Reset low drive                                                                |                   | t <sub>rstdrv</sub> | $34 \times t_{cyc}$     | _                    | _    | ns   |

| 5   | D | BKGD/MS setup time after debug force reset to enter u                          | t <sub>MSSU</sub> | 500                 | _                       | _                    | ns   |      |

| 6   | D | BKGD/MS hold time after is debug force reset to enter u                        | t <sub>MSH</sub>  | 100                 | _                       | _                    | ns   |      |

| 7   | D | Keyboard interrupt pulse width                                                 |                   |                     | 100                     | _                    | _    | ns   |

|     | D |                                                                                | Synchronous path  | t <sub>IHIL</sub>   | $1.5 \times t_{cyc}$    | _                    | _    | ns   |

| 8   | С | Port rise and fall time -                                                      | _                 | t <sub>Rise</sub>   | _                       | 10.2                 | _    | ns   |

|     | С | Normal drive strength (HDRVE_PTXx = 0) (load = 50 pF) <sup>4, 4</sup>          |                   | t <sub>Fall</sub>   | _                       | 9.5                  | _    | ns   |

|     | С | Port rise and fall time -                                                      | _                 | t <sub>Rise</sub>   | _                       | 5.4                  | _    | ns   |

|     | С | Extreme high drive<br>strength (HDRVE_PTXx =<br>1) (load = 50 pF) <sup>4</sup> |                   | t <sub>Fall</sub>   | _                       | 4.6                  | _    | ns   |

- 1. Typical values are based on characterization data at  $V_{DD}$  = 5.0 V, 25 °C unless otherwise stated.

- 2. This is the shortest pulse that is guaranteed to be recognized as a reset pin request.

- To enter BDM mode following a POR, BKGD/MS must be held low during the powerup and for a hold time of t<sub>MSH</sub> after V<sub>DD</sub> rises above V<sub>LVD</sub>.

- 4. Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range -40 °C to 125 °C.

Figure 10. KBIPx timing

S9S08RN60 Series Data Sheet Data Sheet, Rev. 1, 01/2014.

Table 7. FTM input timing (continued)

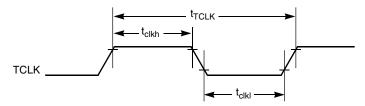

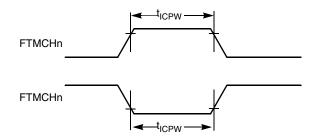

| No. | С | Function                  | Symbol            | Min | Max | Unit             |

|-----|---|---------------------------|-------------------|-----|-----|------------------|

| 2   | D | External clock period     | t <sub>TCLK</sub> | 4   | _   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub> | 1.5 | _   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>clkl</sub> | 1.5 | _   | t <sub>cyc</sub> |

| 5   | D | Input capture pulse width | t <sub>ICPW</sub> | 1.5 | _   | t <sub>cyc</sub> |

Figure 13. Timer external clock

Figure 14. Timer input capture pulse

## 5.3 Thermal specifications

#### 5.3.1 Thermal characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

| Table 8 | Thermal | characteristics |

|---------|---------|-----------------|

| Rating                                 | Symbol             | Value                                       | Unit |  |  |

|----------------------------------------|--------------------|---------------------------------------------|------|--|--|

| Operating temperature range (packaged) | T <sub>A</sub>     | T <sub>L</sub> to T <sub>H</sub> -40 to 125 | °C   |  |  |

| Junction temperature range             | $T_J$              | -40 to 135                                  | °C   |  |  |

|                                        | Thermal resistance | e single-layer board                        |      |  |  |

| 64-pin LQFP                            | $\theta_{JA}$      | 71                                          | °C/W |  |  |

| 48-pin LQFP                            | $\theta_{JA}$      | 81                                          | °C/W |  |  |

| 32-pin LQFP                            | $\theta_{JA}$      | 86                                          | °C/W |  |  |

| Thermal resistance four-layer board    |                    |                                             |      |  |  |

| 64-pin LQFP                            | $\theta_{JA}$      | 53                                          | °C/W |  |  |

| 48-pin LQFP $\theta_{JA}$              |                    | 57                                          | °C/W |  |  |

| 32-pin LQFP                            | $\theta_{JA}$      | 57                                          | °C/W |  |  |

The average chip-junction temperature  $(T_I)$  in  ${}^{\circ}C$  can be obtained from:

$$T_J = T_A + (P_D \times \theta_{JA})$$

Where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$$P_D = P_{int} + P_{I/O}$$

$P_{int} = I_{DD} \times V_{DD}$ , Watts - chip internal power

$P_{I/O}$  = Power dissipation on input and output pins - user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_I$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_J + 273 \, ^{\circ}C)$$

Solving the equations above for K gives:

$$K = P_D \times (T_A + 273 \text{ }^{\circ}\text{C}) + \theta_{JA} \times (P_D)^2$$

where K is a constant pertaining to the particular part. K can be determined by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $P_D$  and the obtained by solving the above equations iteratively for any value of  $P_D$ .

# 6 Peripheral operating requirements and behaviors

reripheral operating requirements and behaviors

## 6.2 NVM specifications

This section provides details about program/erase times and program/erase endurance for the flash and EEPROM memories.

Table 10. Flash characteristics

| С | Characteristic                                                                                                        | Symbol                  | Min <sup>1</sup> | Typical <sup>2</sup> | Max <sup>3</sup> | Unit <sup>4</sup> |

|---|-----------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|----------------------|------------------|-------------------|

| D | Supply voltage for program/erase -40 °C to 125 °C                                                                     | V <sub>prog/erase</sub> | 2.7              | _                    | 5.5              | V                 |

| D | Supply voltage for read operation                                                                                     | $V_{Read}$              | 2.7              | _                    | 5.5              | V                 |

| D | NVM Bus frequency                                                                                                     | f <sub>NVMBUS</sub>     | 1                | _                    | 25               | MHz               |

| D | NVM Operating frequency                                                                                               | f <sub>NVMOP</sub>      | 0.8              | 1                    | 1.05             | MHz               |

| D | Erase Verify All Blocks                                                                                               | t <sub>VFYALL</sub>     | _                | _                    | 17338            | t <sub>cyc</sub>  |

| D | Erase Verify Flash Block                                                                                              | t <sub>RD1BLK</sub>     | _                | _                    | 16913            | t <sub>cyc</sub>  |

| D | Erase Verify EEPROM Block                                                                                             | t <sub>RD1BLK</sub>     | _                | _                    | 810              | t <sub>cyc</sub>  |

| D | Erase Verify Flash Section                                                                                            | t <sub>RD1SEC</sub>     | _                | _                    | 484              | t <sub>cyc</sub>  |

| D | Erase Verify EEPROM Section                                                                                           | t <sub>DRD1SEC</sub>    | _                | _                    | 555              | t <sub>cyc</sub>  |

| D | Read Once                                                                                                             | t <sub>RDONCE</sub>     | _                | _                    | 450              | t <sub>cyc</sub>  |

| D | Program Flash (2 word)                                                                                                | t <sub>PGM2</sub>       | 0.12             | 0.12                 | 0.29             | ms                |

| D | Program Flash (4 word)                                                                                                | t <sub>PGM4</sub>       | 0.20             | 0.21                 | 0.46             | ms                |

| D | Program Once                                                                                                          | t <sub>PGMONCE</sub>    | 0.20             | 0.21                 | 0.21             | ms                |

| D | Program EEPROM (1 Byte)                                                                                               | t <sub>DPGM1</sub>      | 0.10             | 0.10                 | 0.27             | ms                |

| D | Program EEPROM (2 Byte)                                                                                               | t <sub>DPGM2</sub>      | 0.17             | 0.18                 | 0.43             | ms                |

| D | Program EEPROM (3 Byte)                                                                                               | t <sub>DPGM3</sub>      | 0.25             | 0.26                 | 0.60             | ms                |

| D | Program EEPROM (4 Byte)                                                                                               | t <sub>DPGM4</sub>      | 0.32             | 0.33                 | 0.77             | ms                |

| D | Erase All Blocks                                                                                                      | t <sub>ERSALL</sub>     | 96.01            | 100.78               | 101.49           | ms                |

| D | Erase Flash Block                                                                                                     | t <sub>ERSBLK</sub>     | 95.98            | 100.75               | 101.44           | ms                |

| D | Erase Flash Sector                                                                                                    | t <sub>ERSPG</sub>      | 19.10            | 20.05                | 20.08            | ms                |

| D | Erase EEPROM Sector                                                                                                   | t <sub>DERSPG</sub>     | 4.81             | 5.05                 | 20.57            | ms                |

| D | Unsecure Flash                                                                                                        | t <sub>UNSECU</sub>     | 96.01            | 100.78               | 101.48           | ms                |

| D | Verify Backdoor Access Key                                                                                            | t <sub>VFYKEY</sub>     | _                | _                    | 464              | t <sub>cyc</sub>  |

| D | Set User Margin Level                                                                                                 | t <sub>MLOADU</sub>     | _                | _                    | 407              | t <sub>cyc</sub>  |

| С | FLASH Program/erase endurance $T_L$ to $T_H$ = -40 °C to 125 °C                                                       | n <sub>FLPE</sub>       | 10 k             | 100 k                | _                | Cycles            |

| С | EEPROM Program/erase endurance TL<br>to TH = -40 °C to 125 °C                                                         | n <sub>FLPE</sub>       | 50 k             | 500 k                | _                | Cycles            |

| С | Data retention at an average junction temperature of T <sub>Javg</sub> = 85°C after up to 10,000 program/erase cycles | t <sub>D_ret</sub>      | 15               | 100                  | _                | years             |

<sup>1.</sup> Minimum times are based on maximum  $f_{\mbox{\scriptsize NVMOP}}$  and maximum  $f_{\mbox{\scriptsize NVMBUS}}$

<sup>2.</sup> Typical times are based on typical f<sub>NVMOP</sub> and maximum f<sub>NVMBUS</sub>

<sup>3.</sup> Maximum times are based on typical f<sub>NVMOP</sub> and typical f<sub>NVMBUS</sub> plus aging

<sup>4.</sup>  $t_{cyc} = 1 / f_{NVMBUS}$

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see the Memory section.

# 6.3 Analog

#### 6.3.1 ADC characteristics

Table 11. 5 V 12-bit ADC operating conditions

| Characteri<br>stic               |                                                                            |                   | Min               | Typ <sup>1</sup> | Max               | Unit | Comment         |

|----------------------------------|----------------------------------------------------------------------------|-------------------|-------------------|------------------|-------------------|------|-----------------|

| Supply                           | Absolute                                                                   | V <sub>DDA</sub>  | 2.7               | _                | 5.5               | V    | _               |

| voltage                          | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> )             | $\Delta V_{DDA}$  | -100              | 0                | +100              | mV   |                 |

| Ground voltage                   | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSA</sub> ) <sup>2</sup> | $\Delta V_{SSA}$  | -100              | 0                | +100              | mV   |                 |

| Input<br>voltage                 |                                                                            | V <sub>ADIN</sub> | V <sub>REFL</sub> | _                | V <sub>REFH</sub> | V    |                 |

| Input capacitance                |                                                                            | C <sub>ADIN</sub> | _                 | 4.5              | 5.5               | pF   |                 |

| Input resistance                 |                                                                            | R <sub>ADIN</sub> | _                 | 3                | 5                 | kΩ   | _               |

| Analog<br>source                 | 12-bit mode<br>• f <sub>ADCK</sub> > 4 MHz                                 | R <sub>AS</sub>   | _                 | _                | 2                 | kΩ   | External to MCU |

| resistance                       | • f <sub>ADCK</sub> < 4 MHz                                                |                   | _                 | _                | 5                 |      |                 |

|                                  | <ul><li>10-bit mode</li><li>f<sub>ADCK</sub> &gt; 4 MHz</li></ul>          |                   | _                 | _                | 5                 |      |                 |

|                                  | • f <sub>ADCK</sub> < 4 MHz                                                |                   | _                 | _                | 10                |      |                 |

|                                  | 8-bit mode                                                                 |                   | _                 | _                | 10                | 1    |                 |

|                                  | (all valid f <sub>ADCK</sub> )                                             |                   |                   |                  |                   |      |                 |

| ADC                              | High speed (ADLPC=0)                                                       | f <sub>ADCK</sub> | 0.4               | _                | 8.0               | MHz  | _               |

| conversion<br>clock<br>frequency | Low power (ADLPC=1)                                                        |                   | 0.4               | _                | 4.0               |      |                 |

<sup>1.</sup> Typical values assume  $V_{DDA} = 5.0 \text{ V}$ , Temp = 25°C,  $f_{ADCK} = 1.0 \text{ MHz}$  unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2.</sup> DC potential difference.

# Table 12. 12-bit ADC Characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

| Characteristic                    | Conditions                  | С | Symb                | Min  | Typ <sup>1</sup>                  | Max   | Unit                |

|-----------------------------------|-----------------------------|---|---------------------|------|-----------------------------------|-------|---------------------|

| ADC asynchronous clock source     | High speed (ADLPC = 0)      | Р | f <sub>ADACK</sub>  | 2    | 3.3                               | 5     | MHz                 |

|                                   | Low power (ADLPC = 1)       |   |                     | 1.25 | 2                                 | 3.3   |                     |

| Conversion time (including sample | Short sample (ADLSMP = 0)   | Т | t <sub>ADC</sub>    | _    | 20                                | _     | ADCK<br>cycles      |

| time)                             | Long sample<br>(ADLSMP = 1) |   |                     | _    | 40                                | _     |                     |

| Sample time                       | Short sample (ADLSMP = 0)   | Т | t <sub>ADS</sub>    | _    | 3.5                               | _     | ADCK<br>cycles      |

|                                   | Long sample<br>(ADLSMP = 1) |   |                     | _    | 23.5                              | _     |                     |

| Total unadjusted                  | 12-bit mode                 | Т | E <sub>TUE</sub>    | _    | ±5.0                              | _     | LSB <sup>3, 3</sup> |

| Error <sup>2, 2</sup>             | 10-bit mode                 | Р |                     | _    | ±1.5                              | ±2.0  | -                   |

|                                   | 8-bit mode                  | Р |                     | _    | ±0.7                              | ±1.0  |                     |

| Differential Non-                 | 12-bit mode                 | Т | DNL                 | _    | ±1.0                              | _     | LSB <sup>3</sup>    |

| Linearity                         | 10-bit mode <sup>4, 4</sup> | Р |                     | _    | ±0.25                             | ±0.5  |                     |

|                                   | 8-bit mode <sup>4</sup>     | Р |                     | _    | ±0.15                             | ±0.25 | _                   |

| Integral Non-Linearity            | 12-bit mode                 | Т | INL                 | _    | ±1.0                              | _     | LSB <sup>3</sup>    |

|                                   | 10-bit mode                 | Т |                     | _    | ±0.3                              | ±0.5  |                     |

|                                   | 8-bit mode                  | Т |                     | _    | ±0.15                             | ±0.25 |                     |

| Zero-scale error <sup>5, 5</sup>  | 12-bit mode                 | С | E <sub>ZS</sub>     | _    | ±2.0                              | _     | LSB <sup>3</sup>    |

|                                   | 10-bit mode                 | Р |                     | _    | ±0.25                             | ±1.0  |                     |

|                                   | 8-bit mode                  | Р |                     | _    | ±0.65                             | ±1.0  |                     |

| Full-scale error <sup>6</sup>     | 12-bit mode                 | Т | E <sub>FS</sub>     | _    | ±2.5                              | _     | LSB <sup>3</sup>    |

|                                   | 10-bit mode                 | Т |                     | _    | ±0.5                              | ±1.0  |                     |

|                                   | 8-bit mode                  | Т |                     | _    | ±0.5                              | ±1.0  |                     |

| Quantization error                | ≤12 bit modes               | D | EQ                  | _    | _                                 | ±0.5  | LSB <sup>3</sup>    |

| Input leakage error <sup>7</sup>  | all modes                   | D | E <sub>IL</sub>     |      | I <sub>In</sub> * R <sub>AS</sub> |       | mV                  |

| Temp sensor slope                 | -40°C- 25°C                 | D | m                   | _    | 3.266                             | _     | mV/°C               |

|                                   | 25°C- 125°C                 |   |                     | _    | 3.638                             | _     |                     |

| Temp sensor voltage               | 25°C                        | D | V <sub>TEMP25</sub> | _    | 1.396                             | _     | V                   |

<sup>1.</sup> Typical values assume  $V_{DDA} = 5.0 \text{ V}$ , Temp = 25°C,  $f_{ADCK} = 1.0 \text{ MHz}$  unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2.</sup> Includes quantization.

<sup>3.</sup>  $1 LSB = (V_{REFH} - V_{REFL})/2^N$

<sup>4.</sup> Monotonicity and no-missing-codes guaranteed in 10-bit and 8-bit modes

<sup>5.</sup>  $V_{ADIN} = V_{SSA}$

<sup>6.</sup>  $V_{ADIN} = V_{DDA}$

<sup>7.</sup> I<sub>In</sub> = leakage current (refer to DC characteristics)

## 6.3.2 Analog comparator (ACMP) electricals

Table 13. Comparator electrical specifications

| С | Characteristic                        | Symbol              | Min                   | Typical | Max       | Unit |

|---|---------------------------------------|---------------------|-----------------------|---------|-----------|------|

| D | Supply voltage                        | $V_{DDA}$           | 2.7                   | _       | 5.5       | V    |

| Т | Supply current (Operation mode)       | I <sub>DDA</sub>    | _                     | 10      | 20        | μΑ   |

| D | Analog input voltage                  | V <sub>AIN</sub>    | V <sub>SS</sub> - 0.3 | _       | $V_{DDA}$ | V    |

| Р | Analog input offset voltage           | V <sub>AIO</sub>    | _                     | _       | 40        | mV   |

| С | Analog comparator hysteresis (HYST=0) | V <sub>H</sub>      | _                     | 15      | 20        | mV   |

| С | Analog comparator hysteresis (HYST=1) | V <sub>H</sub>      | _                     | 20      | 30        | mV   |

| Т | Supply current (Off mode)             | I <sub>DDAOFF</sub> | _                     | 60      | _         | nA   |

| С | Propagation Delay                     | t <sub>D</sub>      | _                     | 0.4     | 1         | μs   |

### 6.4 Communication interfaces

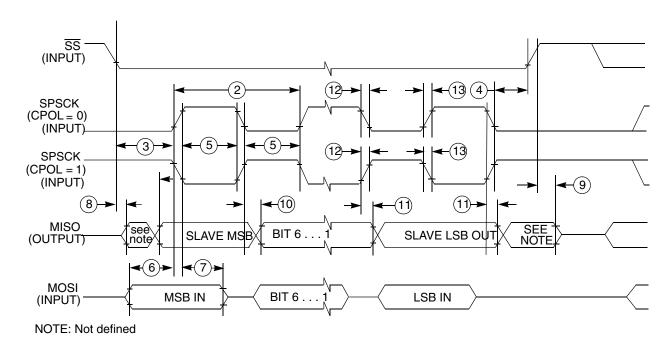

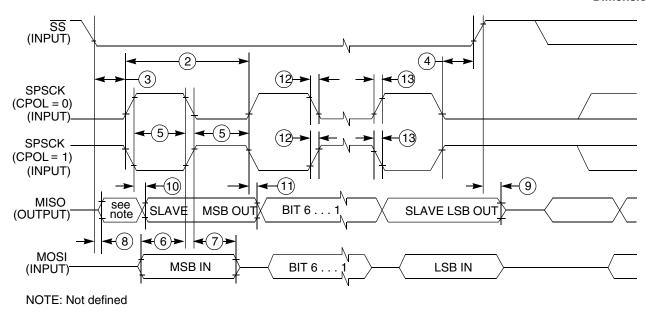

## 6.4.1 SPI switching specifications

The serial peripheral interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. Refer to the SPI chapter of the chip's reference manual for information about the modified transfer formats used for communicating with slower peripheral devices. All timing is shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD}$ , unless noted, and 100 pF load on all SPI pins. All timing assumes slew rate control is disabled and high drive strength is enabled for SPI output pins.

Table 14. SPI master mode timing

| Nu<br>m. | Symbol              | Description                    | Min.                   | Max.                    | Unit               | Comment                              |

|----------|---------------------|--------------------------------|------------------------|-------------------------|--------------------|--------------------------------------|

| 1        | f <sub>op</sub>     | Frequency of operation         | f <sub>Bus</sub> /2048 | f <sub>Bus</sub> /2     | Hz                 | f <sub>Bus</sub> is the bus<br>clock |

| 2        | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>Bus</sub>   | 2048 x t <sub>Bus</sub> | ns                 | $t_{Bus} = 1/f_{Bus}$                |

| 3        | t <sub>Lead</sub>   | Enable lead time               | 1/2                    | _                       | t <sub>SPSCK</sub> | _                                    |

| 4        | t <sub>Lag</sub>    | Enable lag time                | 1/2                    | _                       | t <sub>SPSCK</sub> | _                                    |

| 5        | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>Bus</sub> - 30  | 1024 x t <sub>Bus</sub> | ns                 | _                                    |

| 6        | t <sub>SU</sub>     | Data setup time (inputs)       | 15                     | _                       | ns                 | _                                    |

| 7        | t <sub>HI</sub>     | Data hold time (inputs)        | 0                      | _                       | ns                 | _                                    |

| 8        | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                      | 25                      | ns                 | _                                    |

| 9        | t <sub>HO</sub>     | Data hold time (outputs)       | 0                      | _                       | ns                 | _                                    |

#### reripheral operating requirements and behaviors

Table 15. SPI slave mode timing

| Nu<br>m. | Symbol              | Description                    | Min.                  | Max.                  | Unit             | Comment                                           |

|----------|---------------------|--------------------------------|-----------------------|-----------------------|------------------|---------------------------------------------------|

| 1        | f <sub>op</sub>     | Frequency of operation         | 0                     | f <sub>Bus</sub> /4   | Hz               | f <sub>Bus</sub> is the bus clock as defined in . |

| 2        | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>Bus</sub>  | _                     | ns               | $t_{Bus} = 1/f_{Bus}$                             |

| 3        | t <sub>Lead</sub>   | Enable lead time               | 1                     | _                     | t <sub>Bus</sub> | _                                                 |

| 4        | t <sub>Lag</sub>    | Enable lag time                | 1                     | _                     | t <sub>Bus</sub> | _                                                 |

| 5        | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>Bus</sub> - 30 | _                     | ns               | _                                                 |

| 6        | t <sub>SU</sub>     | Data setup time (inputs)       | 15                    | _                     | ns               | _                                                 |

| 7        | t <sub>HI</sub>     | Data hold time (inputs)        | 25                    | _                     | ns               | _                                                 |

| 8        | t <sub>a</sub>      | Slave access time              | _                     | t <sub>Bus</sub>      | ns               | Time to data active from high-impedance state     |

| 9        | t <sub>dis</sub>    | Slave MISO disable time        | _                     | t <sub>Bus</sub>      | ns               | Hold time to high-<br>impedance state             |

| 10       | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                     | 25                    | ns               | _                                                 |

| 11       | t <sub>HO</sub>     | Data hold time (outputs)       | 0                     | _                     | ns               | _                                                 |

| 12       | t <sub>RI</sub>     | Rise time input                | _                     | t <sub>Bus</sub> - 25 | ns               | _                                                 |

|          | t <sub>Fl</sub>     | Fall time input                |                       |                       |                  |                                                   |

| 13       | t <sub>RO</sub>     | Rise time output               | _                     | 25                    | ns               | _                                                 |

|          | t <sub>FO</sub>     | Fall time output               |                       |                       |                  |                                                   |

Figure 19. SPI slave mode timing (CPHA = 0)

Figure 20. SPI slave mode timing (CPHA=1)

# 6.5 Human-machine interfaces (HMI)

# 6.5.1 TSI electrical specifications

Table 16. TSI electrical specifications

| Symbol    | Description                                                                        | Min. | Туре | Max | Unit |

|-----------|------------------------------------------------------------------------------------|------|------|-----|------|

| TSI_RUNF  | Fixed power consumption in run mode                                                | _    | 100  | _   | μA   |

| TSI_RUNV  | Variable power consumption in run mode (depends on oscillator's current selection) | 1.0  | _    | 128 | μА   |

| TSI_EN    | Power consumption in enable mode                                                   | _    | 100  | _   | μA   |

| TSI_DIS   | Power consumption in disable mode                                                  | _    | 1.2  | _   | μA   |

| TSI_TEN   | TSI analog enable time                                                             | _    | 66   | _   | μs   |

| TSI_CREF  | TSI reference capacitor                                                            | _    | 1.0  | _   | pF   |

| TSI_DVOLT | Voltage variation of VP & VM around nominal values                                 | -10  | _    | 10  | %    |

### 7 Dimensions

# 7.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

S9S08RN60 Series Data Sheet Data Sheet, Rev. 1, 01/2014.

Table 17. Pin availability by package pin-count (continued)

| Pin Number Lowest Priority <> Highest |         |         |                      | ighest     |         |       |                 |

|---------------------------------------|---------|---------|----------------------|------------|---------|-------|-----------------|

| 64-LQFP                               | 48-LQFP | 32-LQFP | Port Pin             | Alt 1      | Alt 2   | Alt 3 | Alt 4           |

| 20                                    | 16      | 11      | PTC3                 | FTM2CH3    | _       | ADP11 | _               |

| 21                                    | 17      | 12      | PTC2                 | FTM2CH2    | _       | ADP10 | _               |

| 22                                    | 18      | _       | PTD7                 | KBI1P7     | TXD2    | _     | _               |

| 23                                    | 19      | _       | PTD6                 | KBI1P6     | RXD2    | _     | _               |

| 24                                    | 20      | _       | PTD5                 | KBI1P5     | _       | _     | _               |

| 25                                    | 21      | 13      | PTC1                 | _          | FTM2CH1 | ADP9  | TSI7            |

| 26                                    | 22      | 14      | PTC0                 | _          | FTM2CH0 | ADP8  | TSI6            |

| 27                                    | _       | _       | PTF7                 | _          | _       | ADP15 | _               |

| 28                                    | _       | _       | PTF6                 | _          | _       | ADP14 | _               |

| 29                                    | _       | _       | PTF5                 | _          | _       | ADP13 | _               |

| 30                                    | _       | _       | PTF4                 | _          | _       | ADP12 | _               |

| 31                                    | 23      | 15      | PTB3                 | KBI0P7     | MOSI0   | ADP7  | TSI5            |

| 32                                    | 24      | 16      | PTB2                 | KBI0P6     | SPSCK0  | ADP6  | TSI4            |

| 33                                    | 25      | 17      | PTB1                 | KBI0P5     | TXD0    | ADP5  | TSI3            |

| 34                                    | 26      | 18      | PTB0                 | KBI0P4     | RXD0    | ADP4  | TSI2            |

| 35                                    | _       | _       | PTF3                 | _          | _       | _     | TSI15           |

| 36                                    | _       | _       | PTF2                 | _          | _       | _     | TSI14           |

| 37                                    | 27      | 19      | PTA7                 | FTM2FAULT2 | _       | ADP3  | TSI1            |

| 38                                    | 28      | 20      | PTA6                 | FTM2FAULT1 | _       | ADP2  | TSI0            |

| 39                                    | 29      | _       | PTE4                 | _          | _       | _     | _               |

| 40                                    | 30      | _       | _                    | _          | _       | _     | V <sub>SS</sub> |

| 41                                    | 31      | _       |                      | _          | _       | _     | $V_{DD}$        |

| 42                                    | _       | _       | PTF1                 | _          | _       | _     | TSI13           |

| 43                                    | _       | _       | PTF0                 | _          | _       | _     | TSI12           |

| 44                                    | 32      | _       | PTD4                 | KBI1P4     | _       | _     | _               |

| 45                                    | 33      | 21      | PTD3                 | KBI1P3     | SS1     | _     | TSI11           |

| 46                                    | 34      | 22      | PTD2                 | KBI1P2     | MISO1   | _     | TSI10           |

| 47                                    | 35      | 23      | PTA3 <sup>2, 2</sup> | KBI0P3     | TXD0    | SCL   | _               |

| 48                                    | 36      | 24      | PTA2 <sup>2</sup>    | KBI0P2     | RXD0    | SDA   | _               |

| 49                                    | 37      | 25      | PTA1                 | KBI0P1     | FTM0CH1 | ACMP1 | ADP1            |

| 50                                    | 38      | 26      | PTA0                 | KBI0P0     | FTM0CH0 | ACMP0 | ADP0            |

| 51                                    | 39      | 27      | PTC7                 | _          | TxD1    | _     | TSI9            |

| 52                                    | 40      | 28      | PTC6                 |            | RxD1    | _     | TSI8            |

| 53                                    | 41      | _       | PTE3                 | _          | SS0     | _     | _               |

| 54                                    | 42      | _       | PTE2                 | _          | MISO0   | _     | _               |

| 55                                    | _       | _       | PTG3                 | _          | _       | _     | _               |

| 56                                    | _       | _       | PTG2                 | _          | _       | _     | _               |

| 57                                    | _       | _       | PTG1                 |            | _       | _     | _               |

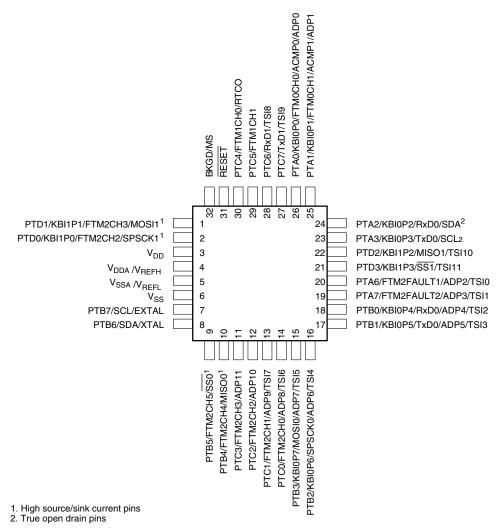

Figure 23. S9S08RN60 32-pin LQFP package

# 9 Revision history

The following table provides a revision history for this document.

Table 18. Revision history

| Rev. No. | Date    | Substantial Changes |

|----------|---------|---------------------|

| 1        | 01/2014 | Initial Release     |