Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                                    |

| Peripherals                | POR, WDT                                                                        |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 6K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

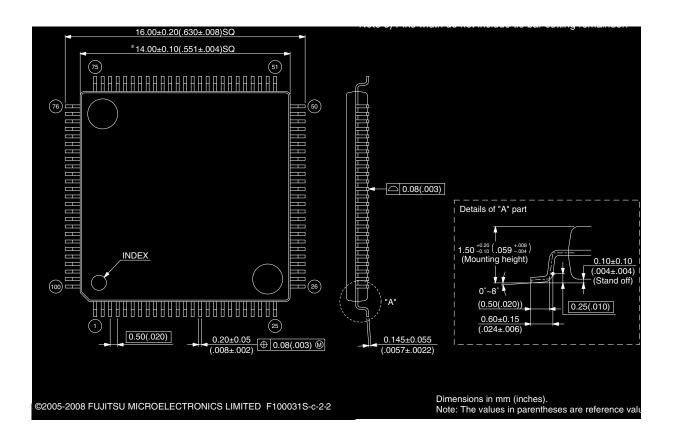

| Package / Case             | 100-BQFP                                                                        |

| Supplier Device Package    | 100-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f543gspf-gs-9003 |

# 1. Product Lineup

| Features                        | MB90F543G (S) /F548G (S)<br>MB90F549G (S) /F546G (S)<br>MB90F548GL(S)                                                                                                                                                                                               | MB90543G (S)<br>MB90547G (S)<br>MB90548G (S)<br>MB90549G (S)                              | MB90V540G           |  |  |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|--|--|--|--|--|

| CPU                             | F <sup>2</sup> MC-16LX CPU                                                                                                                                                                                                                                          |                                                                                           |                     |  |  |  |  |  |

| System clock                    | On-chip PLL clock multiplier (×1, ×2, ×3, ×4, 1/2 when PLL stop)  Minimum instruction exection time: 62.5 ns (machine clock 16MHz, 4MHz osc. four times multiplied by PLL)                                                                                          |                                                                                           |                     |  |  |  |  |  |

| ROM                             | Flash memory MB90F543G(S)/F548G(S) / F548GL(S) : 128 Kbytes MB90F549G(S)/F546G(S): 256 Kbytes                                                                                                                                                                       | MASK ROM: MB90547G(S): 64 Kbytes MB90543G(S)/548G(S): 128 Kbytes MB90549G(S): 256 Kbytes  | External            |  |  |  |  |  |

| RAM                             | MB90F548G(S)/F548GL(S): 4 Kbytes  MB90F543G (S) /F549G(S): 6 Kbytes  MB90F546G(S): 8 Kbytes  MB90F546G(S): 8 Kbytes  MB90F546G(S): 8 Kbytes                                                                                                                         |                                                                                           | 8 Kbytes            |  |  |  |  |  |

| Clocks                          | MB90F543G/F548G/F549G/F546G/<br>F548GL:<br>Two clocks system<br>MB90F543GS/F548GS/F549GS/<br>F546GS/F548GLS:<br>One clock system                                                                                                                                    | MB90543G/547G/548G/549G: Two clocks system MB90543GS/547GS/548GS/ 549GS: One clock system | Two clocks system*1 |  |  |  |  |  |

| Operating voltage range         | *3                                                                                                                                                                                                                                                                  |                                                                                           |                     |  |  |  |  |  |

| Temperature range               | ─40 °C to 105 °C                                                                                                                                                                                                                                                    |                                                                                           |                     |  |  |  |  |  |

| Package                         | QFP100, LQFP100                                                                                                                                                                                                                                                     |                                                                                           | PGA-256             |  |  |  |  |  |

| Emulator-specify power supply*2 | _                                                                                                                                                                                                                                                                   |                                                                                           | None                |  |  |  |  |  |

| UART0                           | Full duplex double buffer Support asynchronous/synchronous (wit Baud rate : 4808/5208/9615/10417/1923 500 K/1 M/2 Mbps (synchron                                                                                                                                    | . ,                                                                                       | hronous)            |  |  |  |  |  |

| UART1<br>(SCI)                  | Full duplex double buffer Asynchronous (start-stop synchronized) and CLK-synchronous communication Baud rate: 1202/2404/4808/9615/19230/31250/38460/62500 bps (asynchronous) 62.5 K/125 K/250 K/500 K/1 M/2 Mbps (synchronous) at 6, 8, 10, 12, 16 MHz              |                                                                                           |                     |  |  |  |  |  |

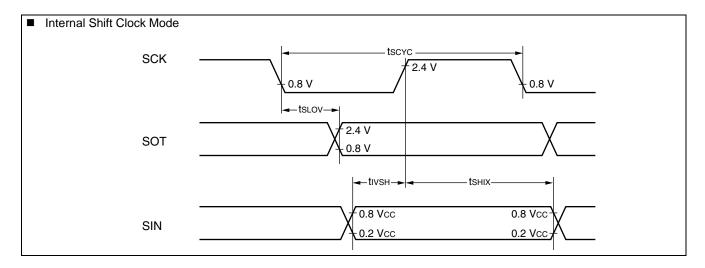

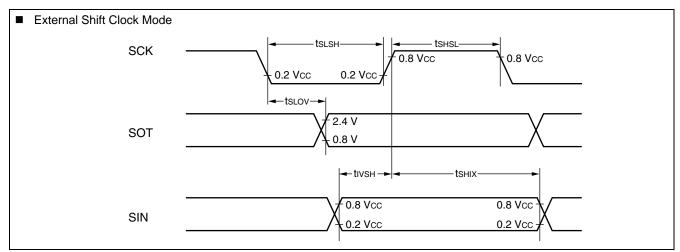

| Serial I/O                      | Transfer can be started from MSB or LSB Supports internal clock synchronized transfer and external clock synchronized transfer Supports positive-edge and nagative-edge clock synchronization Baud rate: 31.25 K/62.5 K/125 K/500 K/1 Mbps at System clock = 16 MHz |                                                                                           |                     |  |  |  |  |  |

| A/D Converter                   | 10-bit or 8-bit resolution 8 input channels Conversion time: 26.3 μs (per one channel)                                                                                                                                                                              |                                                                                           |                     |  |  |  |  |  |

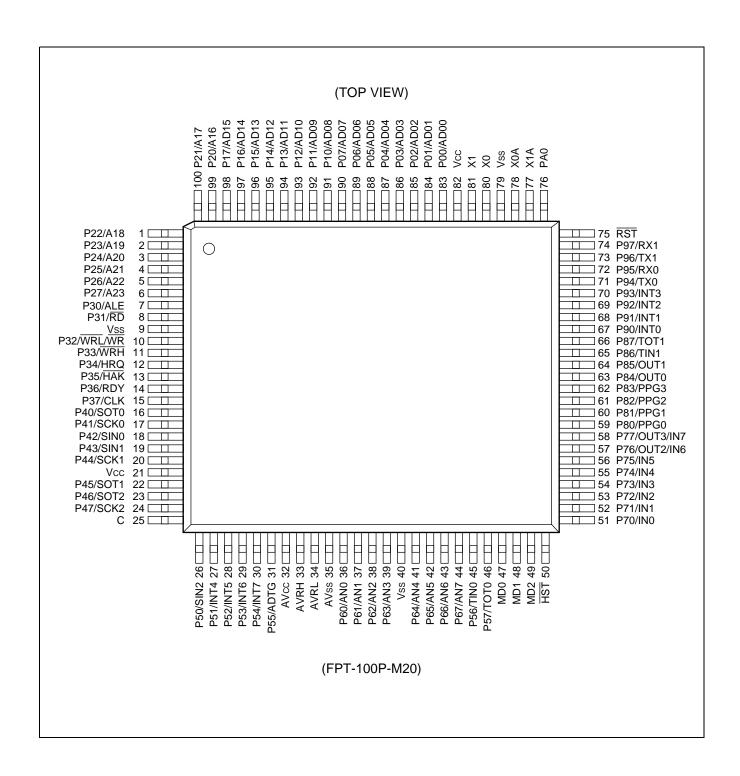

# 3. Pin Description

| Pin No.  |           |              |                    | <b>-</b>                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|----------|-----------|--------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| LQFP*2   | QFP*1     | Pin name     | Circuit type       | Function                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 80<br>81 | 82<br>83  | X0<br>X1     | A<br>(Oscillation) | High speed crystal oscillator input pins                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 78       | 80        | X0A          | A                  | Low speed crystal oscillator input pins. For the one clock system parts, perfom external pull-down processing.                                                                                                                                                                                          |  |  |  |  |  |  |

| 77       | 79        | X1A          | (Oscillation)      | Low speed crystal oscillator input pins. For the one clock system parts, leave it open.                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 75       | 77        | RST          | В                  | External reset request input pin                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 50       | 52        | HST          | С                  | Hardware standby input pin                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 83 to 90 | 85 to 92  | P00 to P07   |                    | General I/O port with programmable pullup. This function is enabled in the single-chip mode.                                                                                                                                                                                                            |  |  |  |  |  |  |

| 83 10 90 | 65 10 92  | AD00 to AD07 |                    | I/O pins for 8 lower bits of the external address/data bus. This function is enabled when the external bus is enabled.                                                                                                                                                                                  |  |  |  |  |  |  |

| 04 += 00 | 02 += 400 | P10 to P17   |                    | General I/O port with programmable pullup. This function is enabled in the single-chip mode.                                                                                                                                                                                                            |  |  |  |  |  |  |

| 91 to 98 | 93 to 100 | AD08 to AD15 |                    | I/O pins for 8 higher bits of the external address/data bus. This function is enabled when the external bus is enabled.                                                                                                                                                                                 |  |  |  |  |  |  |

| 00.45.0  | 4.15.0    | P20 to P27   |                    | General I/O port with programmable pullup. In external bus mode, this function is valid when the corresponding bits in the external address output control resister (HACR) are set to "1".                                                                                                              |  |  |  |  |  |  |

| 99 to 6  | 1 to 8    | A16 to A23   |                    | 8-bit I/O pins for A16 to A23 at the external address/data bus. In external bus mode, this function is valid when the corresponding bits in the external address output control resister (HACR) are set to "0".                                                                                         |  |  |  |  |  |  |

| 7        |           | P30          |                    | General I/O port with programmable pullup. This function is enabled in the single-chip mode.                                                                                                                                                                                                            |  |  |  |  |  |  |

| 7        | 9         | ALE          |                    | Address latch enable output pin. This function is enabled when the external bus is enabled.                                                                                                                                                                                                             |  |  |  |  |  |  |

| 0        | 10        | P31          |                    | General I/O port with programmable pullup. This function is enabled in the single-chip mode.                                                                                                                                                                                                            |  |  |  |  |  |  |

| 8        | 10        | RD           |                    | Read strobe output pin for the data bus. This function is enabled when the external bus is enabled.                                                                                                                                                                                                     |  |  |  |  |  |  |

|          |           | P32          |                    | General I/O port with programmable pullup. This function is enabled in the single-chip mode or when the WR/WRL pin output is disabled.                                                                                                                                                                  |  |  |  |  |  |  |

| 10       | 12        | WRL<br>WR    | I                  | Write strobe output pin for the data bus. This function is enabled when both the external bus and the WR/WRL pin output are enabled. WRL is writestrobe output pin for the lower 8 bits of the data bus in 16-bit access. WR is write-strobe output pin for the 8 bits of the data bus in 8-bit access. |  |  |  |  |  |  |

(Continued)

Document Number: 002- 07696 Rev. \*A Page 9 of 70

| Pin No. |       | D'         | 01           | F                                                                                                                                                                                                                |  |  |  |  |

|---------|-------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LQFP*2  | QFP*1 | - Pin name | Circuit type | Function                                                                                                                                                                                                         |  |  |  |  |

|         |       | P33        |              | General I/O port with programmable pullup. This function is enabled in the single-chip mode, external bus 8-bit mode or when WRH pin output is disabled.                                                         |  |  |  |  |

| 11      | 13    | WRH        | 1            | Write strobe output pin for the 8 higher bits of the data bus. This function is enabled when the external bus is enabled, when the external bus 16-bit mode is selected, and when the WRH output pin is enabled. |  |  |  |  |

| 12      | 14    | P34        |              | General I/O port with programmable pullup. This function is enabled in the single-chip mode or when the hold function is disabled.                                                                               |  |  |  |  |

| 12      | 14    | HRQ        |              | Hold request input pin. This function is enabled when both the external bus and the hold functions are enabled.                                                                                                  |  |  |  |  |

| 12      | 45    | P35        |              | General I/O port with programmable pullup. This function is enabled in the single-chip mode or when the hold function is disabled.                                                                               |  |  |  |  |

| 13      | 15    | HAK        |              | Hold acknowledge output pin. This function is enabled when both the external bus and the hold functions are enabled.                                                                                             |  |  |  |  |

| 4.4     | 40    | P36        |              | General I/O port with programmable pullup. This function is enabled in the single-chip mode or when the external ready function is disabled.                                                                     |  |  |  |  |

| 14      | 16    | RDY        |              | Ready input pin. This function is enabled when both the external bus and the external ready functions are enabled.                                                                                               |  |  |  |  |

| 15      | 17    | P37        | – н          | General I/O port with programmable pullup. This function is enabled in the single-chip mode or when the CLK output is disabled.                                                                                  |  |  |  |  |

| 15      | 17    | CLK        |              | CLK output pin. This function is enabled when both the external bus and CLK outputs are enabled.                                                                                                                 |  |  |  |  |

| 16      | 18    | P40        | - G          | General I/O port. This function is enabled when UART0 disables the serial data output.                                                                                                                           |  |  |  |  |

| 10      | 10    | SOT0       |              | Serial data output pin for UART0. This function is enabled when UART0 enables the serial data output.                                                                                                            |  |  |  |  |

| 17      | 19    | P41        | - G          | General I/O port. This function is enabled when UART0 disables serial clock output.                                                                                                                              |  |  |  |  |

| 17      | 19    | SCK0       |              | Serial clock I/O pin for UART0. This function is enabled when UART0 enables the serial clock output.                                                                                                             |  |  |  |  |

|         |       | P42        |              | General I/O port. This function is always enabled.                                                                                                                                                               |  |  |  |  |

| 18      | 20    | SIN0       | G            | Serial data input pin for UART0. Set the corresponding Port Direction Register to input if this function is used.                                                                                                |  |  |  |  |

|         |       | P43        |              | General I/O port. This function is always enabled.                                                                                                                                                               |  |  |  |  |

| 19      | 21    | SIN1       | G            | Serial data input pin for UART1. Set the corresponding Port Direction Register to input if this function is used.                                                                                                |  |  |  |  |

| Pin No.  |          |              | <b>a.</b>    | Finally                                                                                                                                                                   |  |  |  |  |

|----------|----------|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LQFP*2   | QFP*1    | Pin name     | Circuit type | Function                                                                                                                                                                  |  |  |  |  |

| 46       | 48       | P57          | - D          | General I/O port. This function is enabled when the 16-bit reload timers 0 disables the output.                                                                           |  |  |  |  |

| 40       | 40       | тото         |              | Output pin for the 16-bit reload timers 0. This function is enabled when the 16-bit reload timers 0 enables the output.                                                   |  |  |  |  |

|          |          | P70 to P75   |              | General I/O ports. This function is always enabled.                                                                                                                       |  |  |  |  |

| 51 to 56 | 53 to 58 | IN0 to IN5   | D            | Trigger input pins for input captures ICU0 to ICU5. Set the corresponding Port Direction Register to input if this function is used.                                      |  |  |  |  |

|          |          | P76 , P77    |              | General I/O ports. This function is enabled when the OCU disables the waveform output.                                                                                    |  |  |  |  |

| 57 , 58  | 59,60    | OUT2 , OUT3  | D            | Event output pins for output compares OCU2 and OCU3. This function is enabled when the OCU enables the waveform output.                                                   |  |  |  |  |

|          |          | IN6 , IN7    |              | Trigger input pins for input captures ICU6 and ICU7. Set the corresponding Port Direction Register to input and disable the OCU waveform output if this function is used. |  |  |  |  |

| 59 to 62 | 61 to 64 | P80 to P83   | - D          | General I/O ports. This function is enabled when 8/16-bit PPG disables the waveform output.                                                                               |  |  |  |  |

| 39 10 62 | 61 10 64 | PPG0 to PPG3 |              | Output pins for 8/16-bit PPGs. This function is enabled when 8/16-bit PPG enables the waveform output.                                                                    |  |  |  |  |

| 63 , 64  | 65 , 66  | P84 , P85    | - D          | General I/O ports. This function is enabled when the OCU disables the waveform output.                                                                                    |  |  |  |  |

| 63,64    | 05,00    | OUT0 , OUT1  |              | Waveform output pins for output compares OCU0 and OCU1. This function is enabled when the OCU enables the waveform output.                                                |  |  |  |  |

|          |          | P86          |              | General I/O port. This function is always enabled.                                                                                                                        |  |  |  |  |

| 65       | 67       | TIN1         | D            | Input pin for the 16-bit reload timers 1. Set the corresponding Port Direction Register to input if this function is used.                                                |  |  |  |  |

| 66       | 68       | P87          | D            | General I/O port. This function is enabled when the 16-bit reload timers 1 disables the output.                                                                           |  |  |  |  |

| 00       | 00       | тот1         |              | Output pin for the 16-bit reload timers 1. This function is enabled when the 16-bit reload timers 1 enables the output.                                                   |  |  |  |  |

|          |          | P90 to P93   |              | General I/O port. This function is always enabled.                                                                                                                        |  |  |  |  |

| 67 to 70 | 69 to 72 | INT0 to INT3 | D            | External interrupt request input pins for INT0 to INT3. Set the corresponding Port Direction Register to input if this function is used.                                  |  |  |  |  |

|          |          | P94          |              | General I/O port. This function is enabled when CAN0 disables the output.                                                                                                 |  |  |  |  |

| 71       | 73       | TX0          | D            | TX output pin for CAN0. This function is enabled when CAN0 enables the output.                                                                                            |  |  |  |  |

| Pin No.   |            | Pin name    | Circuit type | Function                                                                                                                                                                |  |  |  |  |  |

|-----------|------------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LQFP*2    | QFP*1      | Fill Hallie | Circuit type | i unotion                                                                                                                                                               |  |  |  |  |  |

|           |            | P95         |              | General I/O port. This function is always enabled.                                                                                                                      |  |  |  |  |  |

| 72        | 74         | RX0         | D            | RX input pin for CAN0 Interface. When the CAN function is used, output from the other functions must be stopped.                                                        |  |  |  |  |  |

|           |            | P96         |              | General I/O port. This function is enabled when CAN1 disables the output.                                                                                               |  |  |  |  |  |

| 73        | 75         | TX1         | D            | TX output pin for CAN1. This function is enabled when CAN1 enables the output (only MB90540G series) .                                                                  |  |  |  |  |  |

|           |            | P97         |              | General I/O port. This function is always enabled.                                                                                                                      |  |  |  |  |  |

| 74        | 76         | RX1         | D            | RX input pin for CAN1 Interface. When the CAN function is used, output from the other functions must be stopped (only MB90540G series) .                                |  |  |  |  |  |

| 76        | 78         | PA0         | D            | General I/O port. This function is always enabled.                                                                                                                      |  |  |  |  |  |

| 32        | 34         | AVcc        | Power supply | Power supply pin for the A/D Converter. This power supply must be turned on or off while a voltage higher than or equal to AVcc is applied to Vcc.                      |  |  |  |  |  |

| 35        | 37         | AVss        | Power supply | Power supply pin for the A/D Converter.                                                                                                                                 |  |  |  |  |  |

| 33        | 35         | AVRH        | Power supply | External reference voltage input pin for the A/D Converter. This power supply must be turned on or off while a voltage higher than or equal to AVRH is applied to AVcc. |  |  |  |  |  |

| 34        | 36         | AVRL        | Power supply | External reference voltage input pin for the A/D Converter.                                                                                                             |  |  |  |  |  |

| 47, 48    | 49, 50     | MD0, MD1    | С            | Input pins for specifying the operating mode. The pins must be directly connected to Vcc or Vss.                                                                        |  |  |  |  |  |

| 49        | 51         | MD2         | F            | Input pin for specifying the operating mode. The pin must be directly connected to Vcc or Vss.                                                                          |  |  |  |  |  |

| 25        | 27         | С           | _            | Power supply stabilization capacitor pin. It should be connected externally to an 0.1 $\mu F$ ceramic capacitor.                                                        |  |  |  |  |  |

| 21, 82    | 23, 84     | Vcc         | Power supply | Input pin for power supply (5.0 V) .                                                                                                                                    |  |  |  |  |  |

| 9, 40, 79 | 11, 42, 81 | Vss         | Power supply | Input pin for power supply (0.0 V) .                                                                                                                                    |  |  |  |  |  |

\*1 : FPT-100P-M06 \*2 : FPT-100P-M20

### (6) Pull-up/down resistors

The MB90540G/545G Series does not support internal pull-up/down resistors (except Port0 - Port3 : pull-up resistors) . Use external components where needed.

#### (7) Crystal Oscillator Circuit

Noises around X0 or X1 pins may be possible causes of abnormal operations. Make sure to provide bypass capacitors via the shortest distances from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure, to the utmost effort, that lines of oscillation circuits do not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board artwork surrounding X0 and X1 pins with a ground area for stabilizing the operation.

#### (8) Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

Make sure to turn on the A/D converter power supply (AVcc, AVRH, AVRL) and analog inputs (AN0 to AN7) after turning-on the digital power supply (Vcc).

Turn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure that the voltage does not exceed AVRH or AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

#### (9) Connection of Unused Pins of A/D Converter

Connect unused pins of A/D converter to AVcc = Vcc, AVss = AVRH = Vss.

#### (10) N.C. Pin

The N.C. (internally connected) pin must be opened for use.

#### (11) Notes on Energization

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at  $50 \mu s$  or more (0.2 V to 2.7 V).

Document Number: 002- 07696 Rev. \*A Page 18 of 70

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 \text{ V to } 5.5 \text{ V}, V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 \text{ °C to } +105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 \text{ °C to } +105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 \text{ °C to } +105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 \text{ °C to } +105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 \text{ °C to } +105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 \text{ °C to } +105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 \text{ °C to } +105 \text{ °C}) \\ (Other than MB90543G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G$

| Doromotor      | Parameter Symbol Pin name |                                                            | Condition                                                 |     | Value |      | Units                               | Remarks             |

|----------------|---------------------------|------------------------------------------------------------|-----------------------------------------------------------|-----|-------|------|-------------------------------------|---------------------|

| Farameter      |                           |                                                            | Condition                                                 | Min | Тур   | Max  | Units                               | Remarks             |

|                | Icc                       |                                                            | Internal frequency : 16 MHz, At normal operating          | _   | 40    | 55   | mA                                  |                     |

|                | icc                       |                                                            | Internal frequency : 16 MHz, At Flash programming/erasing | -   | 50    | 70   | mA                                  | Flash device        |

|                | Iccs                      |                                                            | Internal frequency : 16 MHz, At sleep mode                | -   | 12    | 20   | mA                                  |                     |

|                |                           | ]                                                          | $V_{CC} = 5.0 \text{ V} \pm 10\%$                         | _   | 300   | 600  | μΑ                                  |                     |

|                | Істѕ                      |                                                            |                                                           | _   | 600   | 1100 | μΑ                                  | MB90F548GL (S) only |

| Power          |                           | Internal frequency : 2 MHz,<br>At pseudo timer mode        | _                                                         | 200 | 400   | μА   | MB90543G(S)/547G(S)/<br>548(S) only |                     |

| supply         |                           | Vcc                                                        | Internal frequency: 8 kHz,                                | _   | 400   | 750  | μΑ                                  | MB90F548GL only     |

| current*       | Iccl                      |                                                            | At sub operation, T <sub>A</sub> = 25 °C                  | _   | 50    | 100  | μΑ                                  | MASK ROM            |

|                |                           |                                                            | At sub operation, TA = 25 C                               | _   | 150   | 300  | μΑ                                  | Flash device        |

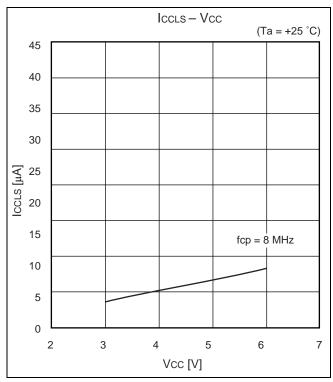

|                | Iccls                     |                                                            | Internal frequency: 8 kHz,                                |     | 15    | 40   | μА                                  |                     |

|                | ICCLS                     |                                                            | At sub sleep, T <sub>A</sub> = 25 °C                      |     | 13    | 40   | μΛ                                  |                     |

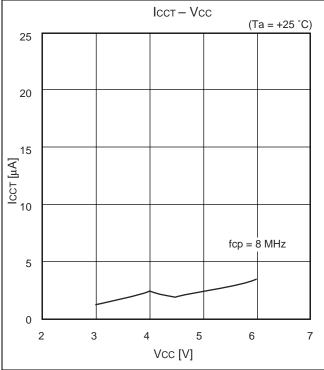

|                | Ісст                      |                                                            | Internal frequency: 8 kHz,                                |     | 7     | 25   | μА                                  |                     |

|                | ICCI                      |                                                            | At timer mode, T <sub>A</sub> = 25 °C                     |     | '     | 20   | μΑ                                  |                     |

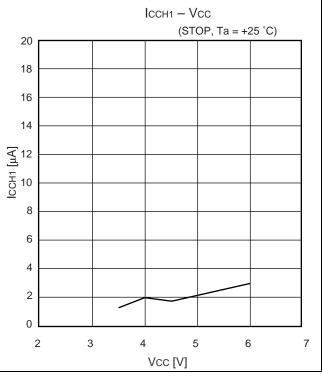

|                | Іссн1                     |                                                            | At stop, T <sub>A</sub> = 25 °C                           | _   | 5     | 20   | μΑ                                  |                     |

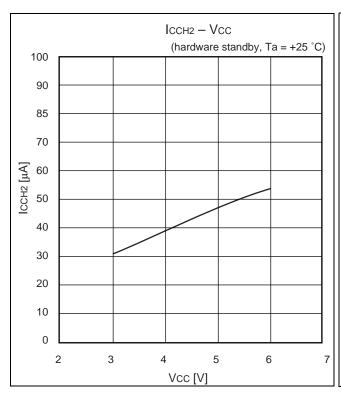

|                | Іссн2                     |                                                            | At hardware standby mode, $T_A = 25 ^{\circ}\text{C}$     | _   | 50    | 100  | μА                                  |                     |

| Input capacity | Cin                       | Other than<br>AVcc, AVss,<br>AVRH,<br>AVRL, C,<br>Vcc, Vss | _                                                         | _   | 5     | 15   | pF                                  |                     |

<sup>\*:</sup> The power supply current testing conditions are when using the external clock.

Document Number: 002-07696 Rev. \*A

## 11.4 AC Characteristics

## 11.4.1 Clock Timing

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): \ V_{CC} = 3.5 \ V \ to \ 5.5 \ V, \ V_{SS} = AV_{SS} = 0.0 \ V, \ T_A = -40 \ ^{\circ}C \ to \ +105 \ ^{\circ}C)$  (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S):  $V_{CC} = 5.0 \ V \pm 10\%$ ,  $V_{SS} = AV_{SS} = 0.0 \ V, \ T_A = -40 \ ^{\circ}C \ to \ +105 \ ^{\circ}C)$

| Parameter             | Cumbal | Pin name |        | Value  |      | Units  | Remarks                                                                                    |                                                                        |

|-----------------------|--------|----------|--------|--------|------|--------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Parameter             | Symbol | Pin name | Min    | Тур    | Max  | Ullits | Remarks                                                                                    |                                                                        |

|                       |        |          | 3      | _      | 16   | MHz    | No multiplier When using an oscillator circuit Vcc = 5.0 V $\pm$ 10%                       |                                                                        |

|                       |        |          | 8      | _      | 16   | MHz    | PLL multiplied by 1 When using an oscillator circuit Vcc = 5.0 V ± 10%                     |                                                                        |

|                       |        |          | 4      | _      | 8    | MHz    | PLL multiplied by 2 When using an oscillator circuit Vcc = 5.0 V ± 10%                     |                                                                        |

|                       | fc     |          | 3      | _      | 5.33 | MHz    | PLL multiplied by 3 When using an oscillator circuit Vcc = 5.0 V ± 10%                     |                                                                        |

| Oscillation frequency |        | fc X     | X0, X1 | 3      | _    | 4      | MHz                                                                                        | PLL multiplied by 4 When using an oscillator circuit Vcc = 5.0 V ± 10% |

| Community requestey   |        |          | 3      | _      | 5    | MHz    | When using an oscillator circuit<br>Vcc < 4.5 V(MB90F548GL(S)/543G(S)/<br>547G(S)/548G(S)) |                                                                        |

|                       |        |          | 3      | _      | 16   | MHz    | No multiplier When using an external clock                                                 |                                                                        |

|                       |        |          | 8      | _      | 16   | MHz    | PLL multiplied by 1<br>When using an external clock                                        |                                                                        |

|                       |        |          | 4      | _      | 8    | MHz    | PLL multiplied by 2<br>When using an external clock                                        |                                                                        |

|                       |        |          | 3      | _      | 5.33 | MHz    | PLL multiplied by 3<br>When using an external clock                                        |                                                                        |

|                       |        |          | 3      | _      | 4    | MHz    | PLL multiplied by 4<br>When using an external clock                                        |                                                                        |

|                       | fcL    | X0A, X1A | _      | 32.768 | _    | kHz    |                                                                                            |                                                                        |

## 11.4.5 Bus Timing (Read)

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 \text{ V to } 5.5 \text{ V}, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/$

| Parameter                                                              | Symbol                     | Pin name                            | Condition | Va                      | lue          | Units   | Remarks |

|------------------------------------------------------------------------|----------------------------|-------------------------------------|-----------|-------------------------|--------------|---------|---------|

| Farameter                                                              | Symbol I in hame Condition |                                     | Min       | Max                     | Units        | Remarks |         |

| ALE pulse width                                                        | <b>t</b> LHLL              | ALE                                 |           | tcp/2 — 20              | _            | ns      |         |

| Valid address → ALE↓ time                                              | tavll                      | ALE,<br>A16 to A23,<br>AD00 to AD15 |           | tcp/2 — 20              | _            | ns      |         |

| ALE↓ → Address valid time                                              | tLLAX                      | ALE, AD00 to<br>AD15                |           | tcp/2 — 15              | _            | ns      |         |

| Valid address → $\overline{\text{RD}} \downarrow$ time                 | tavrl                      | A16 toA23,<br>AD00 to AD15,<br>RD   |           | tcp — 15                | _            | ns      |         |

| Valid address → Valid data input                                       | tavdv                      | A16 to A23,<br>AD00 to AD15         |           | _                       | 5 tcp/2 — 60 | ns      |         |

| RD pulse width                                                         | trlrh                      | RD                                  | _         | 3 tcp/2 — 20            | _            | ns      |         |

| $\overline{\text{RD}} \downarrow \rightarrow \text{ Valid data input}$ | trldv                      | RD, AD00 to<br>AD15                 |           | _                       | 3 tcp/2 — 60 | ns      |         |

| RD↑ → Data hold time                                                   | <b>t</b> RHDX              | RD, AD00 to<br>AD15                 |           | 0                       | _            | ns      |         |

| $\overline{RD} \uparrow \to ALE \uparrow time$                         | <b>t</b> RHLH              | RD, ALE                             |           | tcp/2 — 15              | _            | ns      |         |

| RD↑ → Address valid time                                               | <b>t</b> rhax              | RD, A16 to A23                      |           | tcp/2 — 10              | _            | ns      |         |

| Valid address → CLK↑ time                                              | tavch                      | A16 to A23,<br>AD00 to AD15,<br>CLK |           | tcp/2 — 20              | _            | ns      |         |

| RD↓ → CLK↑ time                                                        | <b>t</b> RLCH              | RD, CLK                             |           | t <sub>CP</sub> /2 — 20 | _            | ns      |         |

| $ALE \downarrow \rightarrow \overline{RD} \downarrow time$             | tllrl                      | ALE, RD                             |           | tcp/2 — 15              | _            | ns      |         |

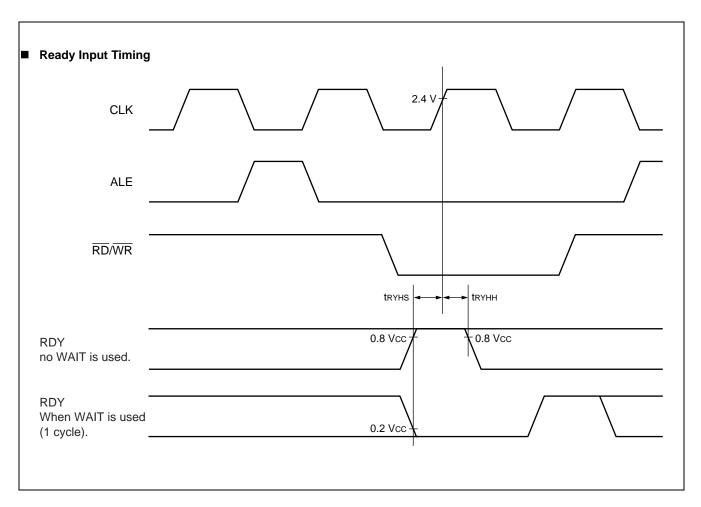

## 11.4.7 Ready Input Timing

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 \text{ V to } 5.5 \text{ V}, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/548G(S)/F548GL(S): V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = \text{AV}_{SS} = 0.0 \text{ V}, T_{A} = -40 \text{ °C to } + 105 \text{ °C}) \\ (Other than MB90543G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S)/F548G(S$

| Parameter      | Symbol Pin name |             | Condition | Value |     | Units | Remarks |

|----------------|-----------------|-------------|-----------|-------|-----|-------|---------|

| Faranietei     | Symbol          | Fill Hallie | Condition | Min   | Max | Units | Remarks |

| RDY setup time | tryhs           | RDY         | _         | 45    | _   | ns    |         |

| RDY hold time  | tкүнн           | RDY         |           | 0     | _   | ns    |         |

Note: If the RDY setup time is insufficient, use the auto-ready function.

# 11.6 Flash Memory Program/Erase Characteristics

| Parameter                            | Condition                | Value  |     |       | Units | Remarks                              |                          |  |

|--------------------------------------|--------------------------|--------|-----|-------|-------|--------------------------------------|--------------------------|--|

| Farameter                            | Condition                | Min    | Тур | Max   | Units | Remarks                              |                          |  |

| Sector erase time                    |                          | _      | 1   | 15    | s     | Excludes 00H programming p           | orior erasure            |  |

| Chip erase time                      | T <sub>A</sub> = + 25 °C | _      | 5   | _     | s     | MB90F543G (S) /F548G (S) /F548GL (S) | Excludes 00H programming |  |

|                                      | Vcc = 5.0 V              |        | 7   | _     | s     | MB90F549G (S) /F546G (S)             | prior erasure            |  |

| Word (16 bit width) programming time |                          | _      | 16  | 3,600 | μs    | Excludes system-level overhead       |                          |  |

| Erase/Program cycle                  | _                        | 10,000 | _   | _     | cycle |                                      |                          |  |

Document Number: 002- 07696 Rev. \*A Page 60 of 70

# 15. Major Changes

Spansion Publication Number: DS07-13703-7E

| Section                                                | Change Results                                                                                                                                  |  |  |  |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ■ PRODUCT LINEUP                                       | Changed the name in peripheral resource.  16-bit I/O Timer → 16-bit Free-run Timer                                                              |  |  |  |

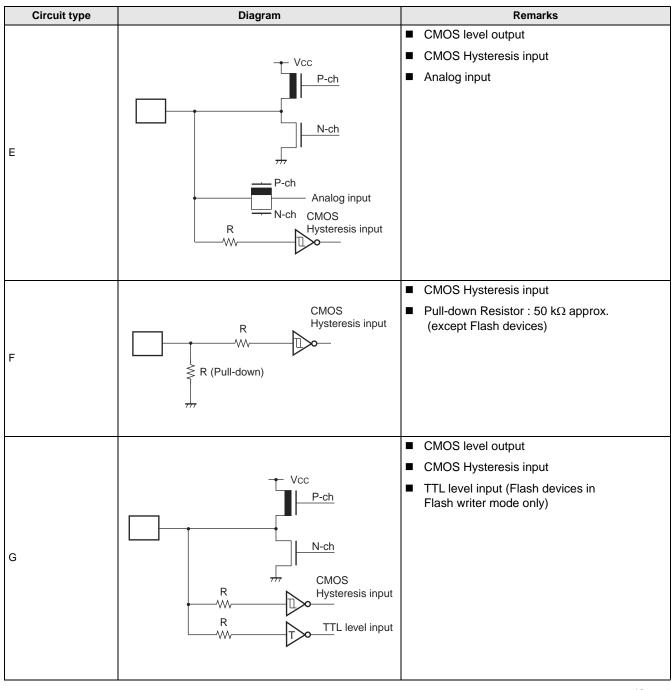

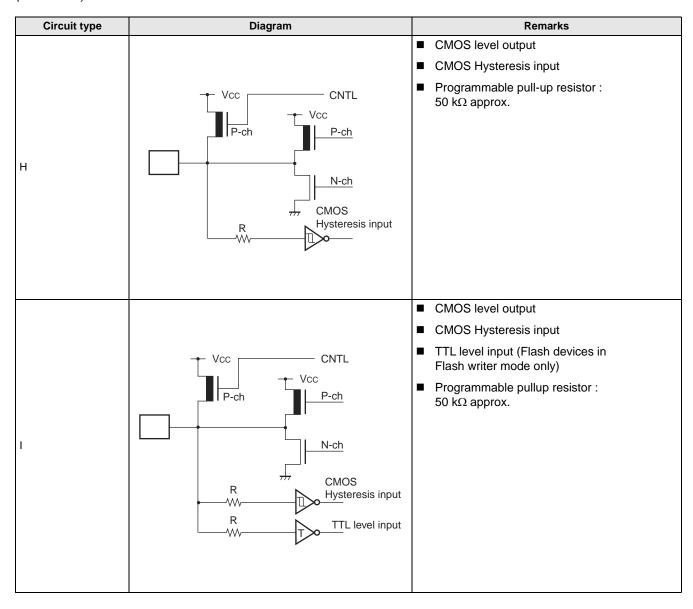

| ■ I/O CIRCUIT TYPE                                     | Changed the name of input typ.  Hysteresis → CMOS Hysteresis  HYS → CMOS Hysteresis                                                             |  |  |  |

| ■ BLOCK DIAGRAM                                        | Changed the arrow direction of SOT1 signal at UART1(SCI). " $\leftarrow$ $\rightarrow$ " (input/output) $\rightarrow$ " $\leftarrow$ " (output) |  |  |  |

| ■ I/O MAP                                              | Changed the text of "Note".                                                                                                                     |  |  |  |

| ■ INTERRUPT MAP                                        | Changed the name of peripheral resource of the pin number: #19.  I/O Timer → 16-bit Free-run Timer                                              |  |  |  |

| ■ ELECTRICAL CHARACTERISTICS 2. Recommended Conditions | Changed the remarks of "parameter: Power supply voltage".                                                                                       |  |  |  |

| 3. DC Characteristics                                  | Changed the maximum value of symbol : VILM of parameter: Input voltage. Vcc + 0.3 $\rightarrow$ Vss + 0.3                                       |  |  |  |

|                                                        | Added the following remarks for parameter : Pull-down resistance. Except Flash device                                                           |  |  |  |

| AC Characteristics     Clock Timing                    | Added the value when using an external clock in Oscillation frequency and Clock cycle time on (1) Clock Timing for parameter.                   |  |  |  |

|                                                        | Added the item of A/D converter operation range in figure of "■ Guaranteed PLL operation range"                                                 |  |  |  |

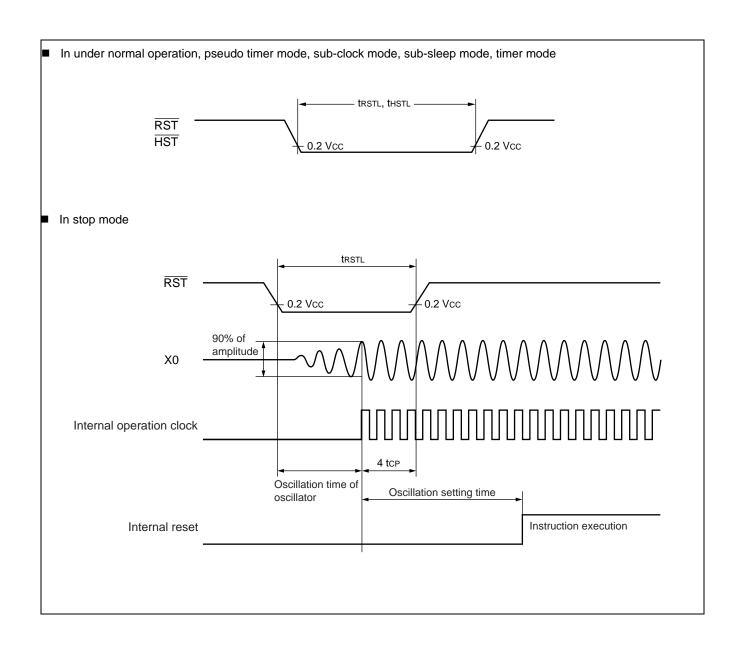

| (3) Reset and Hardware Standby Input Timing            | Changed the following item.  (3) Reset and Hardware Standby Input Timing Remarks: In sub-clock mode, sub-sleep mode, timer mode  2tcp → 2tlcp   |  |  |  |

| (4) Power On Reset                                     | Changed as follows;  Due to repetitive operation → Waiting time until power-on                                                                  |  |  |  |

| 5. A/D Converter                                       | Changed the unit of Zero transition voltage and Full scale transition voltage.<br>$mV \rightarrow V$                                            |  |  |  |

| ■ ORDERING INFORMATION                                 | Added the MB90F548GLPMC in Part Numbers.                                                                                                        |  |  |  |

NOTE: Please see "Document History" about later revised information.

# **Document History**

| Document Title: MB90F543G(S)/546G(S)/548G(S)/549G(S)/549G(S)/V540G/MB90543G(S)/547G(S)/548G(S)/F548GL(S) CMOS F2MC-16LX MB90540G/545G Series 16-bit Proprietary Microcontroller Document Number: 002-07696 |         |                    |                    |                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|

| Revision                                                                                                                                                                                                   | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |

| **                                                                                                                                                                                                         | _       | AKIH               | 11/13/2008         | Migrated to Cypress and assigned document number 002-07696.<br>No change to document contents or format. |

| *A                                                                                                                                                                                                         | 5537115 | AKIH               | 11/30/2016         | Updated to Cypress template                                                                              |

Document Number: 002- 07696 Rev. \*A Page 69 of 70

# Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc Touch Sensing cypress.com/touch **USB** Controllers cypress.com/usb Wireless/RF cypress.com/wireless

#### PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | Projects | Video | Blogs | Training | Components

## **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2002-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the aliure of the device or system (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the aliure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.