Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, SCI, Serial I/O, UART/USART                                    |

| Peripherals                | POR, WDT                                                                        |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 6K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-BQFP                                                                        |

| Supplier Device Package    | 100-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90f543gspf-gs-9017 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

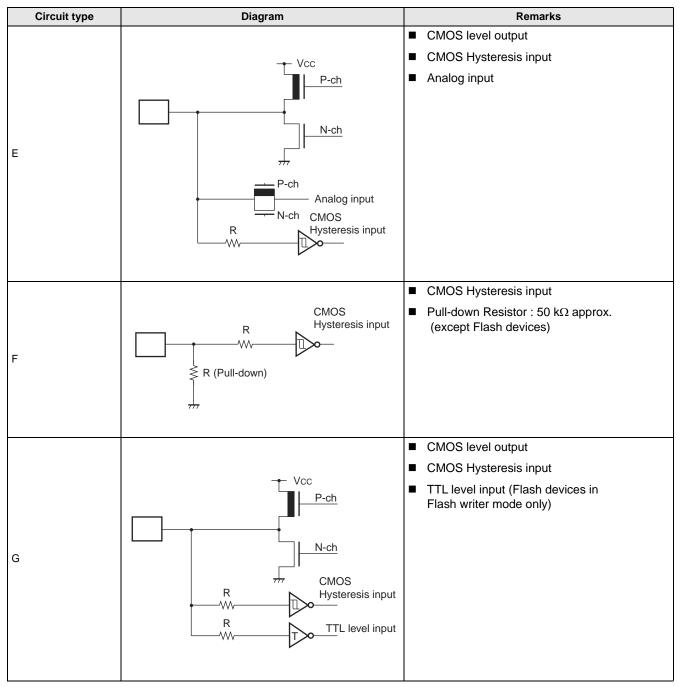

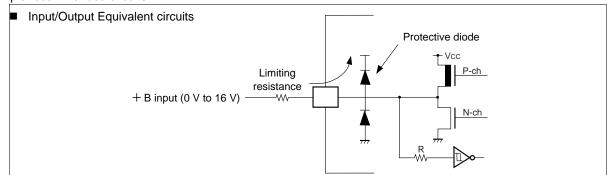

| Circuit type | Diagram                                                             | Remarks                                                                           |

|--------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|              |                                                                     | CMOS level output                                                                 |

|              |                                                                     | <ul> <li>CMOS Hysteresis input</li> </ul>                                         |

| н            | Vcc<br>Vcc<br>P-ch<br>P-ch<br>N-ch<br>m<br>CMOS<br>Hysteresis input | <ul> <li>Programmable pull-up resistor :<br/>50 kΩ approx.</li> </ul>             |

|              |                                                                     | CMOS level output                                                                 |

|              |                                                                     | <ul> <li>CMOS Hysteresis input</li> </ul>                                         |

|              |                                                                     | <ul> <li>TTL level input (Flash devices in<br/>Flash writer mode only)</li> </ul> |

|              | P-ch                                                                | <ul> <li>Programmable pullup resistor :<br/>50 kΩ approx.</li> </ul>              |

| 1            | N-ch                                                                |                                                                                   |

|              | R<br>R<br>Hysteresis input                                          |                                                                                   |

|              | TTL level input                                                     |                                                                                   |

# 5. Handling Devices

#### (1) Preventing latch-up

CMOS IC chips may suffer latch-up under the following conditions :

- A voltage higher than Vcc or lower than Vss is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between Vcc and Vss.

■ The AVcc power supply is applied before the Vcc voltage.

Latch-up may increase the power supply current drastically, causing thermal damage to the device.

For the same reason, care must also be taken in not allowing the analog power-supply voltage (AVcc, AVRH) to exceed the digital power-supply voltage.

#### (2) Handling unused pins

Leaving unused input pins open may result in misbehavior or latch up and possible permanent damage of the device. Therefor they must be pulled up or pulled down through resistors. In this case those resistors should be more than 2 k $\Omega$ .

Unused bi-directional pins should be set to the output state and can be left open, or the input state with the above described connection.

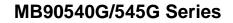

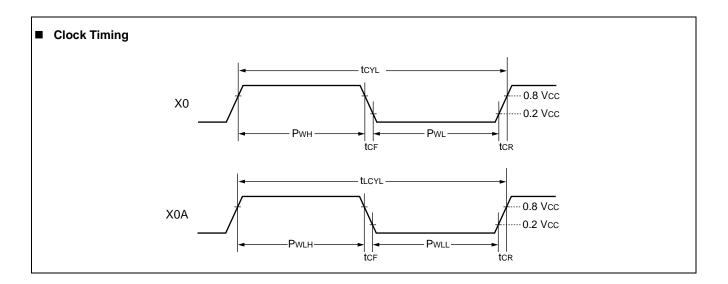

#### (3) Using external clock

To use external clock, drive X0 pin only and leave X1 pin unconnected. Below is a diagram of how to use external clock.

#### (4) Use of the sub-clock

Use one clock system parts when the sub-clock is not used. In that case, pull-down the pin X0A and leave the pin X1A open. When using two clock system parts, a 32 kHz oscillator has to be connected to the X0A and X1A pins.

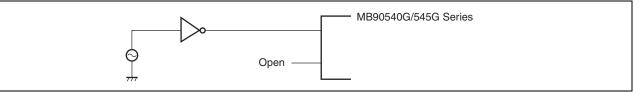

#### (5) Power supply pins (Vcc/Vss)

In products with multiple V<sub>cc</sub> or V<sub>ss</sub> pins, the pins of a same potential are internally connected in the device to avoid abnormal operations including latch-up. However you must connect the pins to an external power and a ground line to lower the electromagnetic emission level to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total current rating.

Make sure to connect Vcc and Vss pins via the lowest impedance to power lines.

It is recommended to provide a bypass capacitor of around 0.1 µF between Vcc and Vss pins near the device.

#### (12) Indeterminate outputs from ports 0 and 1 (MB90V540G only)

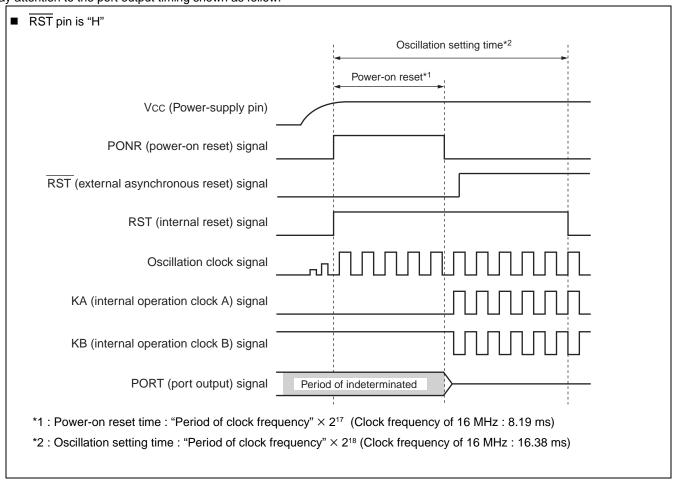

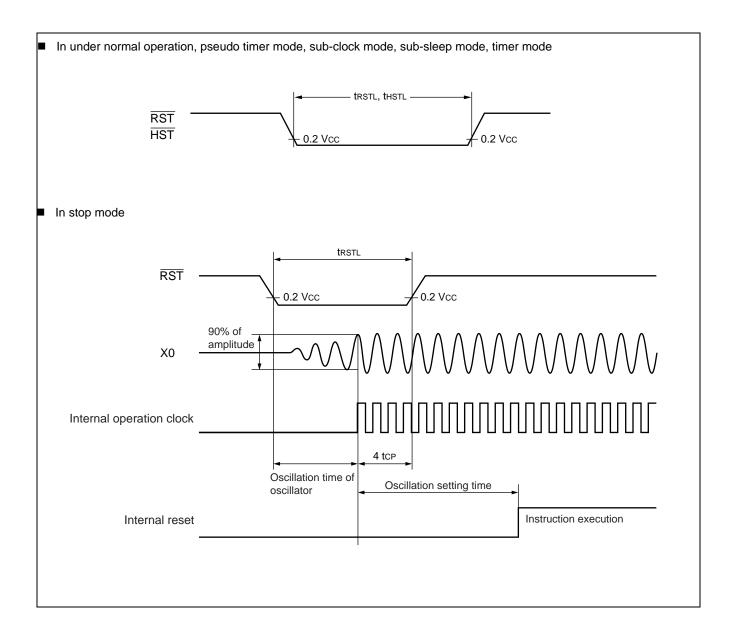

During oscillation setting time of step-down circuit (during a power-on reset) after the power is turned on, the outputs from ports 0 and 1 become following state.

■ If RST pin is "H", the outputs become indeterminate.

■ If RST pin is "L", the outputs become high-impedance. Pay attention to the port output timing shown as follow.

# MB90540G/545G Series

(Continued)

| Address        | Register                      | Abbreviation | Access | Resource name      | Initial value |  |  |  |

|----------------|-------------------------------|--------------|--------|--------------------|---------------|--|--|--|

| 3928н          | Output Compare Register 0     | OCCP0        | R/W    |                    | XXXXXXXXB     |  |  |  |

| 3929н          | Output Compare Register 0     | OCCP0        | R/W    | Output Compare 0/1 | XXXXXXXXB     |  |  |  |

| 392Ан          | Output Compare Register 1     | OCCP1        | R/W    | Output Compare 0/1 | XXXXXXXXB     |  |  |  |

| 392Вн          | Output Compare Register 1     | OCCP1        | R/W    |                    | XXXXXXXXB     |  |  |  |

| 392Сн          | Output Compare Register 2     | OCCP2        | R/W    |                    | XXXXXXXXB     |  |  |  |

| 392Dн          | Output Compare Register 2     | OCCP2        | R/W    | Output Compore 2/2 | XXXXXXXXB     |  |  |  |

| 392Ен          | Output Compare Register 3     | OCCP3        | R/W    | Output Compare 2/3 | XXXXXXXXB     |  |  |  |

| 392Fн          | Output Compare Register 3     | OCCP3        | R/W    |                    | XXXXXXXXB     |  |  |  |

| 3930н to 39FFн | Reserved                      |              |        | ·                  |               |  |  |  |

| 3A00H to 3AFFH | Reserved for CAN 0 Interface. |              |        |                    |               |  |  |  |

| 3B00н to 3BFFн | Reserved for CAN 0 Interface. |              |        |                    |               |  |  |  |

| 3C00н to 3CFFн | Reserved for CAN 1 Interface. |              |        |                    |               |  |  |  |

| 3D00н to 3DFFн | Reserved for CAN 1 Interface. |              |        |                    |               |  |  |  |

| 3E00н to 3FFFн | Reserved                      |              |        |                    |               |  |  |  |

- Read/write notation

- R/W : Reading and writing permitted

- R : Read-only

- W : Write-only

#### Initial value notation

- 0 : Initial value is "0".

- 1 : Initial value is "1".

- X : Initial value is undefined.

- \_ : Initial value is unused.

Note: Any write access to reserved addresses in I/O map should not be performed. A read access to reserved addresses results in reading "X".

# 9. CAN Controller

The MB90540G series contains two CAN controllers (CAN0 and CAN1), the MB90545G series contains only one (CAN0). The Evaluation Chip MB90V540G also has two CAN controllers.

The CAN controller has the following features :

- Conforms to CAN Specification Version 2.0 Part A and B

- Supports transmission/reception in standard frame and extended frame formats

- Supports transmission of data frames by receiving remote frames

- 16 transmitting/receiving message buffers

- □ 29-bit ID and 8-byte data

- Multi-level message buffer configuration

- Provides full-bit comparison, full-bit mask, acceptance register 0/acceptance register 1 for each message buffer as ID acceptance mask

- Two acceptance mask registers in either standard frame format or extended frame formats

- Bit rate programmable from 10 Kbps to 1 Mbps (when input clock is at 16 MHz)

#### List of Control Registers

| Add     | lress           | Register                          | Abbreviation | Access | Initial Value                |  |

|---------|-----------------|-----------------------------------|--------------|--------|------------------------------|--|

| CAN0    | CAN1            | Kegiatei                          | Abbieviation | ALLESS | initial value                |  |

| 000070н | 000080н         | Message buffer valid register     | BVALR        | R/W    | 00000000 00000000в           |  |

| 000071н | <b>000081</b> н | Nessage builet valid register     | DVALK        | N/ W   | 0000000 000000B              |  |

| 000072н | 000082н         | Transmit request register         | TREOR        | R/W    | 0000000 0000000              |  |

| 000073н | 000083н         |                                   | IREQR        | r//v   |                              |  |

| 000074н | 000084н         | Transmit cancel register          | TCANR        | w      | 0000000 0000000 <sub>в</sub> |  |

| 000075н | 000085н         |                                   | ICANK        | vv     |                              |  |

| 000076н | 000086н         | Transmit complete register        | TCR          | R/W    | 0000000 0000000              |  |

| 000077н | 000087н         |                                   | ICK          | r/vv   |                              |  |

| 000078н | 000088н         | Receive complete register         | RCR          | R/W    | 00000000 00000000в           |  |

| 000079н | 000089н         | Receive complete register         | RCR          | r/vv   |                              |  |

| 00007Ан | 00008Ан         | Remote request receiving register | RRTRR        | R/W    | 0000000 0000000в             |  |

| 00007Bн | 00008Bн         | Remote request receiving register |              | N/ W   | 0000000 000000B              |  |

| 00007Cн | 00008Сн         |                                   | ROVRR        | R/W    | 00000000 00000000в           |  |

| 00007Dн | 00008Dн         | Receive overrun register          | ROVER        | r/vv   |                              |  |

| 00007Eн | 00008Eн         | Receive interrupt enable register | RIER         | R/W    | 0000000 0000000-             |  |

| 00007Fн | 00008Fн         | Receive interrupt enable register |              | IN/ VV | 00000000 0000000B            |  |

(Continued)

| Ado             | dress               | Register      | Abbreviation | Access   | Initial Value      |  |                   |

|-----------------|---------------------|---------------|--------------|----------|--------------------|--|-------------------|

| CAN0            | CAN1                | Keyistei      | Abbreviation | ALLESS   |                    |  |                   |

| 003А24н         | 003C24 <sub>H</sub> |               |              |          | XXXXXXXX XXXXXXXX  |  |                   |

| 003A25н         | 003C25н             | ID register 1 | IDR1         | R/W      | ~~~~~~~~~~         |  |                   |

| 003A26н         | 003C26н             |               |              | 1.1/ 1.1 | XXXXX XXXXXXXB     |  |                   |

| 003A27н         | 003C27н             |               |              |          |                    |  |                   |

| 003A28н         | 003C28н             |               |              |          | XXXXXXXX XXXXXXX8  |  |                   |

| 003A29н         | 003C29н             | ID register 2 | IDR2         | R/W      |                    |  |                   |

| 003А2Ан         | 003C2Ан             |               |              | 1.1/ 1.1 | XXXXX XXXXXXXB     |  |                   |

| 003A2Bн         | 003C2Bн             |               |              |          | ~~~~~ ~~~~~        |  |                   |

| 003А2Сн         | 003С2Сн             |               | IDR3         |          |                    |  | XXXXXXXX XXXXXXXB |

| 003A2Dн         | 003C2Dн             | ID register 3 |              | R/W      |                    |  |                   |

| 003А2Ен         | 003C2Eн             |               |              | 1.1/ 1.1 | XXXXX XXXXXXXB     |  |                   |

| 003A2Fн         | 003C2Fн             |               |              |          |                    |  |                   |

| 003А30н         | 003C30н             |               | IDR4         |          | XXXXXXXX XXXXXXXB  |  |                   |

| 003A31н         | 003C31н             | ID register 4 |              | R/W      |                    |  |                   |

| 003А32н         | 003С32н             |               |              |          | XXXXX XXXXXXXB     |  |                   |

| 003А33н         | 003С33н             |               |              |          |                    |  |                   |

| 003А34н         | 003C34н             |               |              |          | XXXXXXXX XXXXXXXxx |  |                   |

| <b>003А35</b> н | 003C35н             | ID register 5 | IDR5         | R/W      |                    |  |                   |

| 003А36н         | 003C36н             |               |              | 1.7, 4.4 | XXXXX XXXXXXXXB    |  |                   |

| 003А37н         | 003C37н             |               |              |          |                    |  |                   |

| 003А38н         | 003C38н             |               |              |          | XXXXXXXX XXXXXXXXB |  |                   |

| 003А39н         | 003С39н             | ID register 6 | IDR6         | R/W      |                    |  |                   |

| 003АЗАн         | 003С3Ан             |               |              | 11/11    | XXXXX XXXXXXXXB    |  |                   |

| 003А3Вн         | 003C3Bн             |               |              |          |                    |  |                   |

(Continued)

| Address             |                     | De sietes        | Abbreviation | A      |                                        |  |

|---------------------|---------------------|------------------|--------------|--------|----------------------------------------|--|

| CAN0                | CAN1                | Register         | Abbreviation | Access | Initial Value                          |  |

| 003А3Сн             | 003С3Сн             |                  |              |        | XXXXXXXX XXXXXXXxx                     |  |

| 003А3Dн             | 003C3DH             | ID register 7    | IDR7         | R/W    |                                        |  |

| 003А3Ен             | 003С3Ен             |                  |              | 10,00  | XXXXX XXXXXXXXB                        |  |

| 003A3Fн             | 003C3Fн             |                  |              |        | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |  |

| 003A40н             | 003C40 <sub>H</sub> |                  |              |        | XXXXXXXX XXXXXXX                       |  |

| 003A41н             | 003C41н             | ID register 8    | IDR8         | R/W    | ~~~~~                                  |  |

| 003A42н             | 003C42 <sub>H</sub> |                  | IDRO         | N/ V V | XXXXX XXXXXXXXB                        |  |

| 003A43н             | 003C43н             |                  |              |        |                                        |  |

| 003A44н             | 003C44 <sub>H</sub> |                  |              |        | XXXXXXXX XXXXXXXxx                     |  |

| 003A45н             | 003C45н             | ID register 9    | IDR9         | R/W    |                                        |  |

| 003А46н             | 003C46н             |                  | IDK9         | N/ V V | XXXXX XXXXXXXx                         |  |

| 003A47н             | 003C47н             |                  |              |        | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |  |

| 003A48н             | 003C48н             |                  |              |        | XXXXXXXX XXXXXXXxx                     |  |

| 003A49н             | 003C49н             | ID register 10   | IDR10        | R/W    |                                        |  |

| 003А4Ан             | 003C4Ан             |                  |              |        | XXXXX XXXXXXXxB                        |  |

| 003A4Bн             | 003C4Bн             |                  |              |        | ~~~~~                                  |  |

| 003А4Сн             | 003C4CH             |                  |              |        | XXXXXXXX XXXXXXXxx                     |  |

| 003A4Dн             | 003C4DH             | ID register 11   | IDR11        | R/W    |                                        |  |

| 003А4Ен             | 003C4Eн             |                  |              | 1.7.00 | XXXXX XXXXXXXx                         |  |

| 003A4Fн             | 003C4Fн             |                  |              |        |                                        |  |

| 003А50н             | 003С50н             |                  |              | R/W    | XXXXXXXX XXXXXXX                       |  |

| 003A51н             | 003C51н             | – ID register 12 | IDR12        |        |                                        |  |

| 003А52н             | 003С52н             |                  |              | N/ V V | XXXXX XXXXXXXx                         |  |

| 003А53н             | 003C53н             |                  |              |        |                                        |  |

| 003A54 <sub>H</sub> | 003C54н             |                  |              |        | XXXXXXXX XXXXXXX                       |  |

| 003А55н             | 003C55н             | – ID register 13 | IDR13        | R/W    | ~~~~~                                  |  |

| 003A56н             | 003С56н             |                  | IDICI3       | 1.7.00 | XXXXX XXXXXXXXB                        |  |

| 003А57н             | 003C57н             |                  |              |        |                                        |  |

| 003A58н             | 003C58н             |                  |              |        | XXXXXXXX XXXXXXXxx                     |  |

| 003А59н             | 003C59н             | ID register 14   |              | P/M    |                                        |  |

| 003А5Ан             | 003С5Ан             | – ID register 14 | IDR14        | R/W    | XXXXX XXXXXXXB                         |  |

| 003A5BH             | 003С5Вн             |                  |              |        |                                        |  |

| 003А5Сн             | 003С5Сн             |                  |              |        | XXXXXXXX XXXXXXXxx                     |  |

| 003A5Dн             | 003C5Dн             | ID register 15   | IDR15        | R/W    |                                        |  |

| 003A5Eн             | 003C5Eн             | ID register 15   |              |        | XXXXX XXXXXXXx                         |  |

| 003A5Fн             | 003C5Fн             |                  |              |        |                                        |  |

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept + B signal input.

- □ Sample recommended circuits :

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

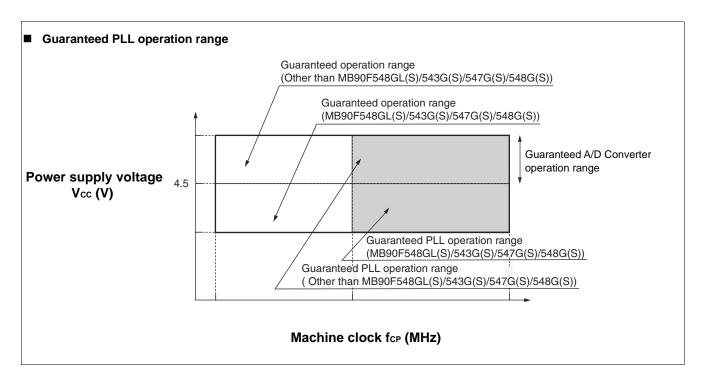

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 V \text{ to } 5.5 V, V_{SS} = AV_{SS} = 0.0 V, T_A = -40 \text{ °C to } +105 \text{ °C})$ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V\_{CC} = 5.0 V ± 10\%, V\_{SS} = AV\_{SS} = 0.0 V, T\_A = -40 \text{ °C to } +105 \text{ °C})

| Deveneter         | Sym-       | Pin name                                                   | Condition                                                           |     | Value |      | Units | Demente                             |

|-------------------|------------|------------------------------------------------------------|---------------------------------------------------------------------|-----|-------|------|-------|-------------------------------------|

| Parameter         | bol Finnar |                                                            | Condition                                                           | Min | Тур   | Max  | Units | Remarks                             |

|                   | lcc        |                                                            | Internal frequency : 16 MHz, At normal operating                    | _   | 40    | 55   | mA    |                                     |

|                   | ICC        |                                                            | Internal frequency : 16 MHz, At<br>Flash programming/erasing        | -   | 50    | 70   | mA    | Flash device                        |

|                   | Iccs       |                                                            | Internal frequency : 16 MHz, At sleep mode                          | _   | 12    | 20   | mA    |                                     |

|                   |            |                                                            | $V_{cc} = 5.0 \text{ V} \pm 10\%$                                   | -   | 300   | 600  | μΑ    |                                     |

|                   | Icts       |                                                            |                                                                     | —   | 600   | 1100 | μΑ    | MB90F548GL (S) only                 |

| Power             | 1013       |                                                            | Internal frequency : 2 MHz,<br>At pseudo timer mode                 | -   | 200   | 400  | μΑ    | MB90543G(S)/547G(S)/<br>548(S) only |

| supply            |            | Vcc                                                        | Internal frequency : 8 kHz,                                         | —   | 400   | 750  | μΑ    | MB90F548GL only                     |

| current*          | ICCL       |                                                            | At sub operation, $T_A = 25 \text{ °C}$                             | —   | 50    | 100  | μΑ    | MASK ROM                            |

|                   |            |                                                            | At sub operation, TA = 25°C                                         | —   | 150   | 300  | μΑ    | Flash device                        |

|                   | Iccls      |                                                            | Internal frequency : 8 kHz,<br>At sub sleep, $T_A = 25 \text{ °C}$  | -   | 15    | 40   | μΑ    |                                     |

|                   | Ісст       |                                                            | Internal frequency : 8 kHz,<br>At timer mode, $T_A = 25 \text{ °C}$ | -   | 7     | 25   | μΑ    |                                     |

|                   | Іссн1      |                                                            | At stop, $T_A = 25 \ ^\circ C$                                      | —   | 5     | 20   | μΑ    |                                     |

|                   | Іссн2      |                                                            | At hardware standby mode, $T_A = 25 \text{ °C}$                     | -   | 50    | 100  | μΑ    |                                     |

| Input<br>capacity | CIN        | Other than<br>AVcc, AVss,<br>AVRH,<br>AVRL, C,<br>Vcc, Vss | _                                                                   | _   | 5     | 15   | pF    |                                     |

\* : The power supply current testing conditions are when using the external clock.

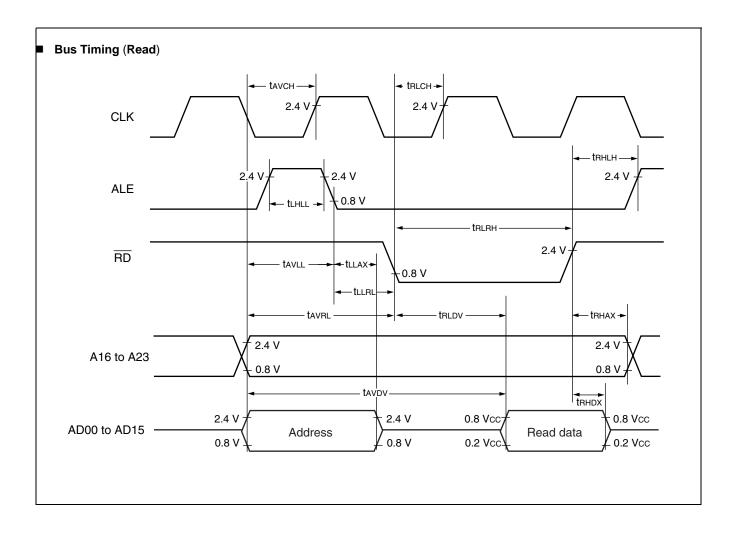

#### 11.4.5 Bus Timing (Read)

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 V \text{ to } 5.5 V, V_{SS} = AV_{SS} = 0.0 V, T_A = -40 \text{ °C to } + 105 \text{ °C})$ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V\_{CC} = 5.0 V ± 10%, V\_{SS} = AV\_{SS} = 0.0 V, T\_A = -40 \text{ °C to } + 105 \text{ °C})

| Parameter                                                   | Symbol        | Pin name                            | Condition | Va                        | alue         | Units | Remarks   |

|-------------------------------------------------------------|---------------|-------------------------------------|-----------|---------------------------|--------------|-------|-----------|

| Farameter                                                   | Symbol        | Finname                             | Condition | Min                       | Max          | Units | Reillarks |

| ALE pulse width                                             | <b>t</b> lhll | ALE                                 |           | tcp/2 — 20                | -            | ns    |           |

| Valid address $\rightarrow ALE \downarrow$ time             | tavll         | ALE,<br>A16 to A23,<br>AD00 to AD15 |           | tcp/2 — 20                | _            | ns    |           |

| $ALE\downarrow \rightarrow Address valid time$              | tllax         | ALE, AD00 to<br>AD15                |           | tср/2 — 15                | -            | ns    |           |

| Valid address $\rightarrow \overline{RD}\downarrow$ time    | <b>t</b> avrl | A16 toA23,<br>AD00 to AD15,<br>RD   |           | tcp — 15                  | _            | ns    |           |

| Valid address → Valid data<br>input                         | tavdv         | A16 to A23,<br>AD00 to AD15         |           | -                         | 5 tcp/2 - 60 | ns    |           |

| RD pulse width                                              | trlrh         | RD                                  | _         | 3 t <sub>CP</sub> /2 — 20 | -            | ns    |           |

| $\overline{RD} \downarrow \rightarrow Valid data input$     | <b>t</b> RLDV | RD, AD00 to<br>AD15                 |           | _                         | 3 tcp/2 — 60 | ns    |           |

| $\overline{RD} \uparrow \to Data$ hold time                 | <b>t</b> RHDX | RD, AD00 to<br>AD15                 |           | 0                         | -            | ns    |           |

| $\overline{RD}^{\uparrow} \rightarrow ALE^{\uparrow}$ time  | trhlh         | RD, ALE                             |           | tcp/2 — 15                | -            | ns    |           |

| $\overline{RD}$ $\uparrow$ $\rightarrow$ Address valid time | <b>t</b> RHAX | RD, A16 to A23                      |           | tcp/2 — 10                | _            | ns    |           |

| Valid address $\rightarrow \text{CLK}^{\uparrow}$ time      | tavch         | A16 to A23,<br>AD00 to AD15,<br>CLK |           | tcp/2 — 20                | _            | ns    |           |

| $\overline{RD} \downarrow \rightarrow CLK\uparrow$ time     | <b>t</b> RLCH | RD, CLK                             |           | tcp/2 — 20                | -            | ns    |           |

| $ALE \downarrow \rightarrow \overline{RD} \downarrow time$  | tllrl         | ALE, RD                             |           | tcp/2 — 15                | _            | ns    |           |

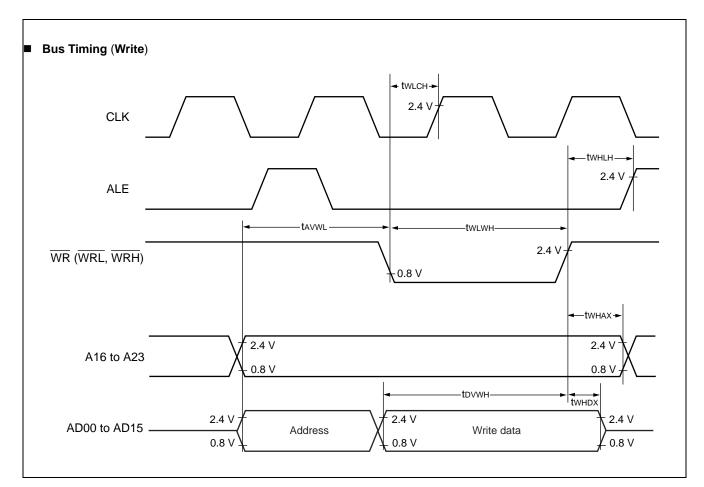

#### 11.4.6 Bus Timing (Write)

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 V to 5.5 V, V_{SS} = AV_{SS} = 0.0 V, T_A = -40 \text{ °C to} + 105 \text{ °C})$ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V\_{CC} = 5.0 V ± 10%, V\_{SS} = AV\_{SS} = 0.0 V, T\_A = -40 \text{ °C to} + 105 \text{ °C})

| Parameter                                                          | Symbol Pin name |                                | Condition | Value                   |     | Units | Remarks |

|--------------------------------------------------------------------|-----------------|--------------------------------|-----------|-------------------------|-----|-------|---------|

| Faranieter                                                         |                 |                                | Condition | Min                     | Max | Units | Remarks |

| Valid address $\rightarrow \overline{\mathrm{WR}} \downarrow$ time | tavwl           | A16 to A23 AD00<br>to AD15, WR |           | tcp — 15                | _   | ns    |         |

| WR pulse width                                                     | twlwh           | WR                             |           | 3 tcp/2 — 20            | —   | ns    |         |

| Valid data output $\rightarrow \overline{WR}^{\uparrow}$ time      | tovwн           | AD00 to AD15,<br>WR            |           | 3 tcp/2 — 20            | _   | ns    |         |

| $\overline{WR} \uparrow \to Data$ hold time                        | twhdx           | AD00 to AD15,<br>WR            | _         | 20                      | _   | ns    |         |

| $\overline{WR}^{\uparrow} \rightarrow Address$ valid time          | <b>t</b> WHAX   | A16 to A23, WR                 |           | tcp/2 — 10              | —   | ns    |         |

| $\overline{WR}^{\uparrow} \rightarrow ALE^{\uparrow}$ time         | twhlh           | WR, ALE                        |           | tcp/2 — 15              | —   | ns    |         |

| $\overline{WR}^{\uparrow} \rightarrow CLK^{\uparrow}$ time         | twlch           | WR, CLK                        |           | t <sub>CP</sub> /2 — 20 | —   | ns    |         |

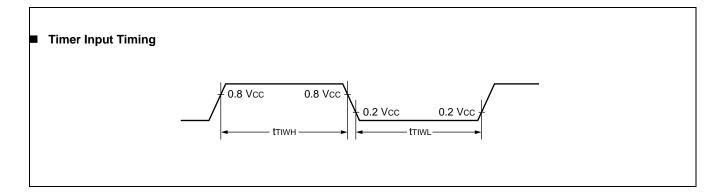

### 11.4.10 Timer Input Timing

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 V \text{ to } 5.5 V, V_{SS} = AV_{SS} = 0.0 V, T_A = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C})$ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V\_{CC} = 5.0 V ± 10\%, V\_{SS} = AV\_{SS} = 0.0 V, T\_A = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C})

| Parameter         | Symbol | Pin name   | Condition | Va    | ue  | Units | Remarks |

|-------------------|--------|------------|-----------|-------|-----|-------|---------|

| Falanetei         | Symbol | Finname    | Condition | Min   | Max | Units | Remarks |

| Input pulso width | tтіwн  | TIN0, TIN1 | _         | 4 +== | _   | 20    |         |

| Input pulse width | t⊤ıw∟  | IN0 to IN7 | _         | 4 tcp |     | ns    |         |

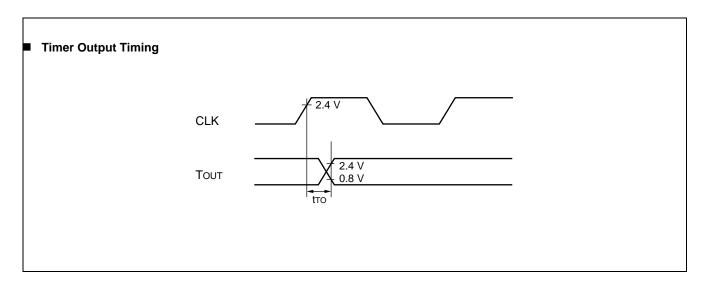

#### 11.4.11 Timer Output Timing

$(MB90543G(S)/547G(S)/548G(S)/F548GL(S): V_{CC} = 3.5 V \text{ to } 5.5 V, V_{SS} = AV_{SS} = 0.0 V, T_A = -40 \text{ °C to } + 105 \text{ °C})$ (Other than MB90543G(S)/547G(S)/548G(S)/F548GL(S): V\_{CC} = 5.0 V ± 10%, V\_{SS} = AV\_{SS} = 0.0 V, T\_A = -40 \text{ °C to } + 105 \text{ °C})

| Parameter                              | Symbol | Pin name                     | Pin name Condition |     | Value |       | Remarks |

|----------------------------------------|--------|------------------------------|--------------------|-----|-------|-------|---------|

| Farameter                              | Symbol | Fiii liaine                  | Condition          | Min | Max   | Units | Remarks |

| $CLK^\uparrow \to T_{OUT}$ change time | tтo    | TOT0 , TOT1,<br>PPG0 to PPG3 | _                  | 30  | _     | ns    |         |

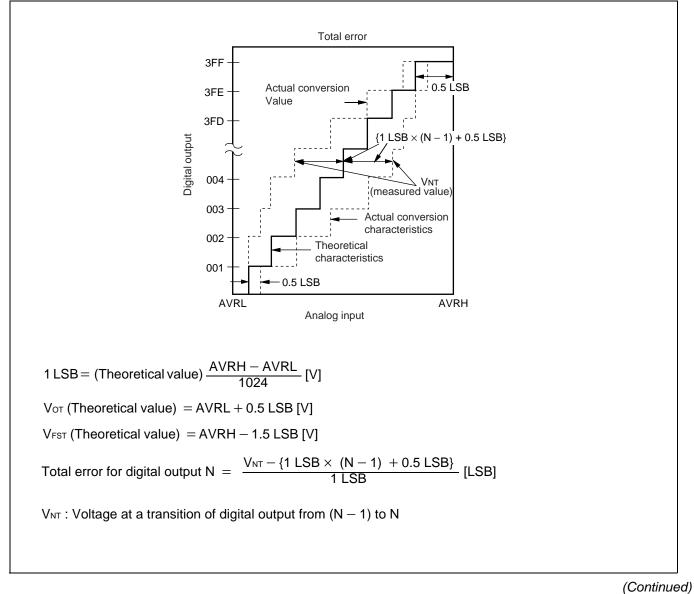

#### 11.5.2 A/D Converter Glossary

Resolution : Analog changes that are identifiable with the A/D converter

Linearity error : The deviation of the straight line connecting the zero transition point ("00 0000 0000"  $\leftrightarrow \rightarrow$  "00 0000 0001") with the full-scale transition point ("11 1111 1110"  $\leftrightarrow \rightarrow$  "11 1111 1111") from actual conversion characteristics

Differential linearity error : The deviation of input voltage needed to change the output code by 1 LSB from the theoretical value

Total error : The total error is defined as a difference between the actual value and the theoretical value, which includes zero-transition error/full-scale transition error and linearity error.

# **13. Ordering Information**

| Part number    | Package              | Remarks |

|----------------|----------------------|---------|

| MB90F543GPF    |                      |         |

| MB90F543GSPF   |                      |         |

| MB90F546GPF    |                      |         |

| MB90F546GSPF   |                      |         |

| MB90F548GPF    |                      |         |

| MB90F548GSPF   |                      |         |

| MB90F548GLPF   |                      |         |

| MB90F548GLSPF  |                      |         |

| MB90F549GPF    | 100-pin Plastic QFP  |         |

| MB90F549GSPF   | (FPT-100P-M06)       |         |

| MB90543GPF     |                      |         |

| MB90543GSPF    |                      |         |

| MB90547GPF     |                      |         |

| MB90547GSPF    |                      |         |

| MB90548GPF     |                      |         |

| MB90548GSPF    |                      |         |

| MB90549GPF     |                      |         |

| MB90549GSPF    |                      |         |

| MB90F543GPMC   |                      |         |

| MB90F543GSPMC  |                      |         |

| MB90F546GPMC   |                      |         |

| MB90F546GSPMC  |                      |         |

| MB90F548GPMC   |                      |         |

| MB90F548GSPMC  |                      |         |

| MB90F548GLPMC  |                      |         |

| MB90F548GLSPMC |                      |         |

| MB90F549GPMC   | 100-pin Plastic LQFP |         |

| MB90F549GSPMC  | (FPT-100P-M20)       |         |

| MB90543GPMC    |                      |         |

| MB90543GSPMC   |                      |         |

| MB90547GPMC    |                      |         |

| MB90547GSPMC   |                      |         |

| MB90548GPMC    |                      |         |

| MB90548GSPMC   |                      |         |

| MB90549GPMC    |                      |         |

| MB90549GSPMC   |                      |         |

# Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers cypress. | ooni, ann  |

|----------------------------------------------------------------|------------|

| Automotive cypress.com/au                                      | Itomotive  |

| Clocks & Buffers cypress.co                                    | m/clocks   |

| Interface cypress.com/                                         | /interface |

| Internet of Things cypres                                      | s.com/iot  |

| Lighting & Power Control cypress.com/pc                        | owerpsoc   |

| Memory cypress.com                                             | /memory    |

| PSoC cypress.c                                                 | com/psoc   |

| Touch Sensing cypress.co                                       | om/touch   |

| USB Controllers cypress.                                       | .com/usb   |

| Wireless/RF cypress.com                                        | /wireless  |

PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Forums | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuctitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

<sup>©</sup> Cypress Semiconductor Corporation, 2002-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.