# E·XFL

#### NXP USA Inc. - MKE16F256VLH16 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 168MHz                                                                 |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, SPI, UART/USART                      |

| Peripherals                | DMA, LVD, PWM, WDT                                                     |

| Number of I/O              | 58                                                                     |

| Program Memory Size        | 256КВ (256К х 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 68K x 8                                                                |

| RAM Size                   | 64K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mke16f256vlh16 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

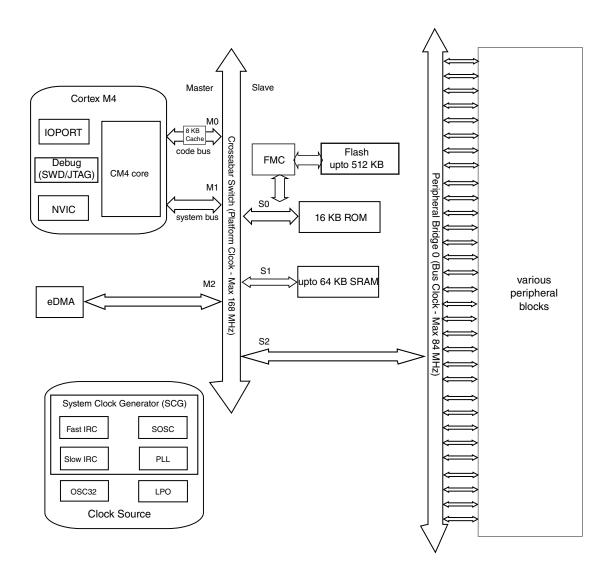

Figure 2. System diagram

The crossbar switch connects bus masters and slaves using a crossbar switch structure. This structure allows up to four bus masters to access different bus slaves simultaneously, while providing arbitration among the bus masters when they access the same slave.

### 2.1 System features

The following sections describe the high-level system features.

- Static operation in Normal Stop mode

- 16-word data buffer supported with multiple operation modes

- DMA support

### 2.2.5 CMP

There are three analog comparators on this device.

- Each CMP has its own independent 8-bit DAC.

- Each CMP supports up to 7 analog inputs from external pins.

- Each CMP is able to convert an internal reference from the bandgap.

- Each CMP supports internal reference from the on-chip 12-bit DAC out.

- Each CMP supports the round-robin sampling scheme. In summary, this allow the CMP to operate independently in VLPS and Stop modes, whilst being triggered periodically to sample up to 8 inputs. Only if an input changes state is a full wakeup generated.

The CMP has the following features:

- Inputs may range from rail to rail

- Programmable hysteresis control

- Selectable interrupt on rising-edge, falling-edge, or both rising and falling edges of the comparator output

- Selectable inversion on comparator output

- Capability to produce a wide range of outputs such as sampled, windowed, or digitally filtered

- External hysteresis can be used at the same time that the output filter is used for internal functions

- Two software selectable performance levels: Shorter propagation delay at the expense of higher power, and Low power with longer propagation delay

- DMA transfer support

- Functional in all power modes available on this MCU

- The window and filter functions are not available in STOP mode

- Integrated 8-bit DAC with selectable supply reference source and can be power down to conserve power

# 2.2.6 RTC

The RTC is an always powered-on block that remains active in all low power modes. The time counter within the RTC is clocked by a 32.768 kHz clock sourced from an external crystal using the oscillator, or clock directly from RTC\_CLKIN pin.

## 2.2.9 LPTMR

The low-power timer (LPTMR) can be configured to operate as a time counter with optional prescaler, or as a pulse counter with optional glitch filter, across all power modes, including the low-leakage modes. It can also continue operating through most system reset events, allowing it to be used as a time of day counter.

The LPTMR module has the following features:

- 16-bit time counter or pulse counter with compare

- Optional interrupt can generate asynchronous wakeup from any low-power mode

- Hardware trigger output

- Counter supports free-running mode or reset on compare

- Configurable clock source for prescaler/glitch filter

- Configurable input source for pulse counter

# 2.2.10 CRC

This device contains one cyclic redundancy check (CRC) module which can generate 16/32-bit CRC code for error detection.

The CRC module provides a programmable polynomial, WAS, and other parameters required to implement a 16-bit or 32-bit CRC standard.

The CRC module has the following features:

- Hardware CRC generator circuit using a 16-bit or 32-bit programmable shift register

- Programmable initial seed value and polynomial

- Option to transpose input data or output data (the CRC result) bitwise or bytewise.

- Option for inversion of final CRC result

- 32-bit CPU register programming interface

# 2.2.11 LPUART

This product contains three Low-Power UART modules, and can work in Stop and VLPS modes. The module also supports 4× to 32× data oversampling rate to meet different applications.

The LPUART module has the following features:

• Programmable baud rates (13-bit modulo divider) with configurable oversampling ratio from 4× to 32×

#### Overview

Each FlexCAN module contains 16 message buffers. Each message buffer is 16 bytes.

The FlexCAN module has the following features:

- Flexible mailboxes of zero to eight bytes data length

- Each mailbox configurable as receive or transmit, all supporting standard and extended messages

- Individual Rx Mask registers per mailbox

- Full-featured Rx FIFO with storage capacity for up to six frames and automatic internal pointer handling with DMA support

- Transmission abort capability

- Programmable clock source to the CAN Protocol Interface, either peripheral clock or oscillator clock

- RAM not used by reception or transmission structures can be used as general purpose RAM space

- Listen-Only mode capability

- Programmable Loop-Back mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independence from the transmission medium (an external transceiver is assumed)

- Short latency time due to an arbitration scheme for high-priority messages

- Low power modes, with programmable wake up on bus activity

- Remote request frames may be handled automatically or by software

- CAN bit time settings and configuration bits can only be written in Freeze mode

- Tx mailbox status (Lowest priority buffer or empty buffer)

- Identifier Acceptance Filter Hit Indicator (IDHIT) register for received frames

- SYNCH bit available in Error in Status 1 register to inform that the module is synchronous with CAN bus

- CRC status for transmitted message

- Rx FIFO Global Mask register

- Selectable priority between mailboxes and Rx FIFO during matching process

- Powerful Rx FIFO ID filtering, capable of matching incoming IDs against either 128 extended, 256 standard, or 512 partial (8 bit) IDs, with up to 32 individual masking capability

# 4 Pinouts

## 4.1 KE1xF Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

### NOTE

On this device, there are several special ADC channels which support hardware interleave between multiple ADCs. Taking ADC0\_SE4 and ADC1\_SE14 channels as an example, these two channels can work independently, but they can also be hardware interleaved. In the hardware interleaved mode, a signal on the pin PTB0 can be sampled by both ADC0 and ADC1. The interleaved mode is enabled by SIM\_CHIPCTL[ADC\_INTERLEAVE\_EN] bits. For more information, see "ADC Hardware Interleaved Channels" in the ADC chapter of Reference Manual.

| 100<br>LQFP | 64<br>LQFP | Pin Name      | Default       | ALTO          | ALT1  | ALT2     | ALT3            | ALT4      | ALT5    | ALT6    | ALT7            |

|-------------|------------|---------------|---------------|---------------|-------|----------|-----------------|-----------|---------|---------|-----------------|

| -           | 10         | VREFL/<br>VSS | VREFL/<br>VSS | VREFL/<br>VSS |       |          |                 |           |         |         |                 |

| 1           | -          | PTE16         | DISABLED      |               | PTE16 |          |                 | FTM2_CH7  |         | FXIO_D3 | TRGMUX_<br>OUT7 |

| 2           | -          | PTE15         | DISABLED      |               | PTE15 |          |                 | FTM2_CH6  |         | FXIO_D2 | TRGMUX_<br>OUT6 |

| 3           | 1          | PTD1          | ADC2_SE1      | ADC2_SE1      | PTD1  | FTM0_CH3 | LPSPI1_SIN      | FTM2_CH1  |         | FXIO_D1 | TRGMUX_<br>OUT2 |

| 4           | 2          | PTD0          | ADC2_SE0      | ADC2_SE0      | PTD0  | FTM0_CH2 | LPSPI1_SCK      | FTM2_CH0  |         | FXIO_D0 | TRGMUX_<br>OUT1 |

| 5           | 3          | PTE11         | ADC2_SE13     | ADC2_SE13     | PTE11 | PWT_IN1  | LPTMR0_<br>ALT1 | FTM2_CH5  |         | FXIO_D5 | TRGMUX_<br>OUT5 |

| 6           | 4          | PTE10         | ADC2_SE12     | ADC2_SE12     | PTE10 | CLKOUT   |                 | FTM2_CH4  |         | FXIO_D4 | TRGMUX_<br>OUT4 |

| 7           | _          | PTE13         | DISABLED      |               | PTE13 |          |                 | FTM2_FLT0 |         |         |                 |

| 8           | 5          | PTE5          | DISABLED      |               | PTE5  | TCLK2    | FTM2_QD_<br>PHA | FTM2_CH3  | CAN0_TX | FXIO_D7 | EWM_IN          |

| 9           | 6          | PTE4          | DISABLED      |               | PTE4  | BUSOUT   | FTM2_QD_<br>PHB | FTM2_CH2  | CAN0_RX | FXIO_D6 | EWM_OUT_b       |

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                             | ALT0                                | ALT1  | ALT2       | ALT3            | ALT4      | ALT5    | ALT6            | ALT7       |

|-------------|------------|----------|-------------------------------------|-------------------------------------|-------|------------|-----------------|-----------|---------|-----------------|------------|

| 10          | 7          | VDD      | VDD                                 | VDD                                 |       |            |                 |           |         |                 |            |

| 11          | 8          | VDDA     | VDDA                                | VDDA                                |       |            |                 |           |         |                 |            |

| 12          | 9          | VREFH    | VREFH                               | VREFH                               |       |            |                 |           |         |                 |            |

| 13          | _          | VREFL    | VREFL                               | VREFL                               |       |            |                 |           |         |                 |            |

| 14          | _          | VSS      | VSS                                 | VSS                                 |       |            |                 |           |         |                 |            |

| 15          | 11         | PTB7     | EXTAL                               | EXTAL                               | PTB7  | LPI2C0_SCL |                 |           |         |                 |            |

| 16          | 12         | PTB6     | XTAL                                | XTAL                                | PTB6  | LPI2C0_SDA |                 |           |         |                 |            |

| 17          | _          | PTE14    | ACMP2_IN3                           | ACMP2_IN3                           | PTE14 | FTM0_FLT1  |                 | FTM2_FLT1 |         |                 |            |

| 18          | 13         | PTE3     | DISABLED                            |                                     | PTE3  | FTM0_FLT0  | LPUART2_<br>RTS | FTM2_FLT0 |         | TRGMUX_IN6      | ACMP2_OUT  |

| 19          | _          | PTE12    | DISABLED                            |                                     | PTE12 | FTM0_FLT3  | LPUART2_TX      |           |         |                 |            |

| 20          | _          | PTD17    | DISABLED                            |                                     | PTD17 | FTM0_FLT2  | LPUART2_RX      |           |         |                 |            |

| 21          | 14         | PTD16    | ACMP2_IN0                           | ACMP2_IN0                           | PTD16 | FTM0_CH1   |                 |           |         |                 |            |

| 22          | 15         | PTD15    | ACMP2_IN1                           | ACMP2_IN1                           | PTD15 | FTM0_CH0   |                 |           |         |                 |            |

| 23          | 16         | PTE9     | ACMP2_IN2/<br>DAC0_OUT              | ACMP2_IN2/<br>DAC0_OUT              | PTE9  | FTM0_CH7   | LPUART2_<br>CTS |           |         |                 |            |

| 24          | _          | PTD14    | DISABLED                            |                                     | PTD14 | FTM2_CH5   |                 |           |         |                 | CLKOUT     |

| 25          | _          | PTD13    | DISABLED                            |                                     | PTD13 | FTM2_CH4   |                 |           |         |                 | RTC_CLKOUT |

| 26          | 17         | PTE8     | ACMP0_IN3                           | ACMP0_IN3                           | PTE8  | FTM0_CH6   |                 |           |         |                 |            |

| 27          | 18         | PTB5     | DISABLED                            |                                     | PTB5  | FTM0_CH5   | LPSPI0_PCS1     |           |         | TRGMUX_IN0      | ACMP1_OUT  |

| 28          | 19         | PTB4     | ACMP1_IN2                           | ACMP1_IN2                           | PTB4  | FTM0_CH4   | LPSPI0_SOUT     |           |         | TRGMUX_IN1      |            |

| 29          | 20         | PTC3     | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32 | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32 | PTC3  | FTM0_CH3   | CAN0_TX         |           |         |                 |            |

| 30          | 21         | PTC2     | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32  | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32  | PTC2  | FTM0_CH2   | CAN0_RX         |           |         |                 |            |

| 31          | 22         | PTD7     | DISABLED                            |                                     | PTD7  | LPUART2_TX |                 | FTM2_FLT3 |         |                 |            |

| 32          | 23         | PTD6     | DISABLED                            |                                     | PTD6  | LPUART2_RX |                 | FTM2_FLT2 |         |                 |            |

| 33          | 24         | PTD5     | DISABLED                            |                                     | PTD5  | FTM2_CH3   | LPTMR0_<br>ALT2 | FTM2_FLT1 | PWT_IN2 | TRGMUX_IN7      |            |

| 34          | _          | PTD12    | DISABLED                            |                                     | PTD12 | FTM2_CH2   | LPI2C1_HREQ     |           |         | LPUART2_<br>RTS |            |

| 35          | —          | PTD11    | DISABLED                            |                                     | PTD11 | FTM2_CH1   | FTM2_QD_<br>PHA |           |         | LPUART2_<br>CTS |            |

| 36          | —          | PTD10    | DISABLED                            |                                     | PTD10 | FTM2_CH0   | FTM2_QD_<br>PHB |           |         |                 |            |

| 37          | —          | VSS      | VSS                                 | VSS                                 |       |            |                 |           |         |                 |            |

| 38          | -          | VDD      | VDD                                 | VDD                                 |       |            |                 |           |         |                 |            |

| 39          | 25         | PTC1     | ADC0_SE9/<br>ACMP1_IN3              | ADC0_SE9/<br>ACMP1_IN3              | PTC1  | FTM0_CH1   |                 |           |         | FTM1_CH7        |            |

| 40          | 26         | PTC0     | ADC0_SE8/<br>ACMP1_IN4              | ADC0_SE8/<br>ACMP1_IN4              | PTC0  | FTM0_CH0   |                 |           |         | FTM1_CH6        |            |

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                          | ALT0                    | ALT1  | ALT2        | ALT3            | ALT4        | ALT5            | ALT6            | ALT7                             |

|-------------|------------|----------|----------------------------------|-------------------------|-------|-------------|-----------------|-------------|-----------------|-----------------|----------------------------------|

| 73          | 48         | PTA2     | ADC1_SE0                         | ADC1_SE0                | PTA2  | FTM3_CH0    | LPI2C0_SDA      | EWM_OUT_b   |                 | LPUART0_RX      |                                  |

| 74          | -          | PTB11    | ADC2_SE8                         | ADC2_SE8                | PTB11 | FTM3_CH3    | LPI2C0_HREQ     |             |                 |                 |                                  |

| 75          | _          | PTB10    | ADC2_SE9                         | ADC2_SE9                | PTB10 | FTM3_CH2    | LPI2C0_SDAS     |             |                 |                 |                                  |

| 76          | _          | PTB9     | ADC2_SE10                        | ADC2_SE10               | PTB9  | FTM3_CH1    | LPI2C0_SCLS     |             |                 |                 |                                  |

| 77          | _          | PTB8     | ADC2_SE11                        | ADC2_SE11               | PTB8  | FTM3_CH0    |                 |             |                 |                 |                                  |

| 78          | 49         | PTA1     | ADC0_SE1/<br>ACMP0_IN1           | ADC0_SE1/<br>ACMP0_IN1  | PTA1  | FTM1_CH1    | LPI2C0_SDAS     | FXIO_D3     | FTM1_QD_<br>PHA | LPUART0_<br>RTS | TRGMUX_<br>OUT0                  |

| 79          | 50         | PTA0     | ADC0_SE0/<br>ACMP0_IN0           | ADC0_SE0/<br>ACMP0_IN0  | PTA0  | FTM2_CH1    | LPI2C0_SCLS     | FXIO_D2     | FTM2_QD_<br>PHA | LPUART0_<br>CTS | TRGMUX_<br>OUT3                  |

| 80          | 51         | PTC7     | ADC1_SE5                         | ADC1_SE5                | PTC7  | LPUART1_TX  | CAN1_TX         | FTM3_CH3    |                 |                 |                                  |

| 81          | 52         | PTC6     | ADC1_SE4                         | ADC1_SE4                | PTC6  | LPUART1_RX  | CAN1_RX         | FTM3_CH2    |                 |                 |                                  |

| 82          | _          | PTA16    | ADC1_SE13                        | ADC1_SE13               | PTA16 | FTM1_CH3    | LPSPI1_PCS2     |             |                 |                 |                                  |

| 83          | _          | PTA15    | ADC1_SE12                        | ADC1_SE12               | PTA15 | FTM1_CH2    | LPSPI0_PCS3     |             |                 |                 |                                  |

| 84          | 53         | PTE6     | ADC1_SE11/<br>ACMP0_IN6          | ADC1_SE11/<br>ACMP0_IN6 | PTE6  | LPSPI0_PCS2 |                 | FTM3_CH7    |                 | LPUART1_<br>RTS |                                  |

| 85          | 54         | PTE2     | ADC1_SE10                        | ADC1_SE10               | PTE2  | LPSPI0_SOUT | LPTMR0_<br>ALT3 | FTM3_CH6    | PWT_IN3         | LPUART1_<br>CTS |                                  |

| 86          | _          | VSS      | VSS                              | VSS                     |       |             |                 |             |                 |                 |                                  |

| 87          | _          | VDD      | VDD                              | VDD                     |       |             |                 |             |                 |                 |                                  |

| 88          | _          | PTA14    | DISABLED                         |                         | PTA14 | FTM0_FLT0   | FTM3_FLT1       | EWM_IN      |                 | FTM1_FLT0       | BUSOUT                           |

| 89          | 55         | PTA13    | ADC2_SE4                         | ADC2_SE4                | PTA13 | FTM1_CH7    | CAN1_TX         | LPI2C1_SCLS |                 |                 |                                  |

| 90          | 56         | PTA12    | ADC2_SE5                         | ADC2_SE5                | PTA12 | FTM1_CH6    | CAN1_RX         | LPI2C1_SDAS |                 |                 |                                  |

| 91          | 57         | PTA11    | DISABLED                         |                         | PTA11 | FTM1_CH5    | LPUART0_RX      | FXIO_D1     |                 |                 |                                  |

| 92          | 58         | PTA10    | JTAG_TDO/<br>noetm_Trace_<br>SWO |                         | PTA10 | FTM1_CH4    | LPUART0_TX      | FXIO_D0     |                 |                 | JTAG_TDO/<br>noetm_Trace_<br>SWO |

| 93          | 59         | PTE1     | ADC2_SE6                         | ADC2_SE6                | PTE1  | LPSPI0_SIN  | LPI2C0_HREQ     | LPI2C1_SCL  |                 | FTM1_FLT1       |                                  |

| 94          | 60         | PTE0     | ADC2_SE7                         | ADC2_SE7                | PTE0  | LPSPI0_SCK  | TCLK1           | LPI2C1_SDA  |                 | FTM1_FLT2       |                                  |

| 95          | 61         | PTC5     | JTAG_TDI                         |                         | PTC5  | FTM2_CH0    | RTC_CLKOUT      | LPI2C1_HREQ |                 | FTM2_QD_<br>PHB | JTAG_TDI                         |

| 96          | 62         | PTC4     | JTAG_TCLK/<br>SWD_CLK            | ACMP0_IN2               | PTC4  | FTM1_CH0    | RTC_CLKOUT      |             | EWM_IN          | FTM1_QD_<br>PHB | JTAG_TCLK/<br>SWD_CLK            |

| 97          | 63         | PTA5     | RESET_b                          |                         | PTA5  |             | TCLK1           |             |                 | JTAG_TRST_b     | RESET_b                          |

| 98          | 64         | PTA4     | JTAG_TMS/<br>SWD_DIO             |                         | PTA4  |             |                 | ACMP0_OUT   | EWM_OUT_b       |                 | JTAG_TMS/<br>SWD_DIO             |

| 99          | _          | PTA9     | DISABLED                         |                         | PTA9  |             |                 | FXIO_D7     | FTM3_FLT2       | FTM1_FLT3       |                                  |

| 100         | -          | PTA8     | DISABLED                         |                         | PTA8  |             |                 | FXIO_D6     | FTM3_FLT3       |                 |                                  |

### 4.3.1 Core Modules

#### Table 7. JTAG Signal Descriptions

| Chip signal name | Module signal<br>name  | Description              | I/O |

|------------------|------------------------|--------------------------|-----|

| JTAG_TMS         | JTAG_TMS/<br>SWD_DIO   | JTAG Test Mode Selection | I/O |

| JTAG_TCLK        | JTAG_TCLK/<br>SWD_CLK  | JTAG Test Clock          | I   |

| JTAG_TDI         | JTAG_TDI               | JTAG Test Data Input     | I   |

| JTAG_TDO         | JTAG_TDO/<br>TRACE_SWO | JTAG Test Data Output    | 0   |

| JTAG_TRST_b      | JTAG_TRST_b            | JTAG Reset               | I   |

#### Table 8. SWD Signal Descriptions

| Chip signal name | Module signal<br>name | Description       | I/O |

|------------------|-----------------------|-------------------|-----|

| SWD_CLK          | JTAG_TCLK/<br>SWD_CLK | Serial Wire Clock | I   |

| SWD_DIO          | JTAG_TMS/<br>SWD_DIO  | Serial Wire Data  | I/O |

#### Table 9. TPIU Signal Descriptions

| Chip signal name | Module signal<br>name  | Description                                                            | I/O |

|------------------|------------------------|------------------------------------------------------------------------|-----|

| TRACE_SWO        | JTAG_TDO/<br>TRACE_SWO | Trace output data from the ARM CoreSight debug block over a single pin | 0   |

### 4.3.2 System Modules

#### Table 10. System Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                              | I/O |

|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| NMI_b            | _                     | Non-maskable interrupt NOTE: Driving the NMI signal low forces<br>a non-maskable interrupt, if the NMI function is selected on the<br>corresponding pin. | I   |

| RESET_b          |                       | Reset bidirectional signal                                                                                                                               | I/O |

| VDD              |                       | MCU power                                                                                                                                                | I   |

| VSS              | —                     | MCU ground                                                                                                                                               | I   |

| Chip signal name | Module signal<br>name | Description                                                                                                                                                        | I/O |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| EWM_IN           | EWM_in                | EWM input for safety status of external safety circuits. The polarity of EWM_IN is programmable using the EWM_CTRL[ASSIN] bit. The default polarity is active-low. | Ι   |

| EWM_OUT_b        | EWM_out               | EWM reset out signal                                                                                                                                               | 0   |

#### Table 11. EWM Signal Descriptions

## 4.3.3 Clock Modules

#### Table 12. OSC (in SCG) Signal Descriptions

| Chip<br>signal<br>name | Module signal name | Description                     | I/O |

|------------------------|--------------------|---------------------------------|-----|

| EXTAL                  | EXTAL              | External clock/Oscillator input | I   |

| XTAL                   | XTAL               | Oscillator output               | 0   |

#### Table 13. RTC Oscillator (OSC32) Signal Descriptions

| Chip signal name | Module signal<br>name | Description                  | I/O |

|------------------|-----------------------|------------------------------|-----|

| EXTAL32          | EXTAL32               | 32.768 kHz oscillator input  | I   |

| XTAL32           | XTAL32                | 32.768 kHz oscillator output | 0   |

### 4.3.4 Analog

#### Table 14. ADCn Signal Descriptions

| Chip signal name | Module signal<br>name | Description                        | I/O |

|------------------|-----------------------|------------------------------------|-----|

| ADCn_SE[15:0]    | AD[15:0]              | Single-Ended Analog Channel Inputs | I   |

| VREFH            | V <sub>REFSH</sub>    | Voltage Reference Select High      | I   |

| VREFL            | V <sub>REFSL</sub>    | Voltage Reference Select Low       | I   |

| VDDA             | V <sub>DDA</sub>      | Analog Power Supply                | I   |

#### Table 15. DAC0 Signal Descriptions

| Chip signal name | Module signal<br>name | Description | I/O |

|------------------|-----------------------|-------------|-----|

| DAC0_OUT         | _                     | DAC output  | 0   |

| Chip signal name | Module signal<br>name | Description                | I/O |

|------------------|-----------------------|----------------------------|-----|

| LPSPIn_SOUT      | SOUT                  | Serial Data Out            | 0   |

| LPSPIn_SIN       | SIN                   | Serial Data In             | I   |

| LPSPIn_SCK       | SCK                   | Serial Clock               | I/O |

| LPSPIn_PCS[3:0]  | PCS[3:0]              | Peripheral Chip Select 0-3 | I/O |

#### Table 21. LPSPIn Signal Descriptions

### Table 22. LPI2Cn Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                              | I/O |

|------------------|-----------------------|------------------------------------------------------------------------------------------|-----|

| LPI2Cn_SCL       | SCL                   | Bidirectional serial clock line of the I2C system.                                       | I/O |

| LPI2Cn_SDA       | SDA                   | Bidirectional serial data line of the I2C system.                                        | I/O |

| LPI2Cn_HREQ      | HREQ                  | Host request, can initiate an LPI2C master transfer if asserted and the I2C bus is idle. | I   |

| LPI2Cn_SCLS      | SCLS                  | Secondary I2C clock line.                                                                | I/O |

| LPI2Cn_SDAS      | SDAS                  | Secondary I2C data line.                                                                 | I/O |

#### Table 23. LPUARTn Signal Descriptions

| Chip signal name | Module signal<br>name | Description     | I/O |

|------------------|-----------------------|-----------------|-----|

| LPUARTn_TX       | LPUART_TX             | Transmit data   | 0   |

| LPUARTn_RX       | LPUART_RX             | Receive data    | I   |

| LPUARTn_CTS      | LPUART_CTS            | Clear to send   | I   |

| LPUARTn_RTS      | LPUART_RTS            | Request to send | 0   |

#### Table 24. FlexIO Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                               | I/O |

|------------------|-----------------------|-----------------------------------------------------------|-----|

| FXIO_D[7:0]      | FXIO_D[7:0]           | Bidirectional FlexIO Shifter and Timer pin inputs/outputs | I/O |

### 5.3.1 Nonswitching electrical specifications

#### 5.3.1.1 Voltage and current operating requirements Table 27. Voltage and current operating requirements

| Symbol                                | Description                                                                                                                                                            | Min.            | Max.            | Unit | Notes |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------|-------|

| $V_{DD}$                              | Supply voltage                                                                                                                                                         | 2.7             | 5.5             | V    |       |

| V <sub>DDA</sub>                      | Analog supply voltage                                                                                                                                                  | 2.7             | 5.5             | V    |       |

| V <sub>DD</sub> –<br>V <sub>DDA</sub> | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                              | - 0.1           | 0.1             | V    |       |

| V <sub>SS</sub> –<br>V <sub>SSA</sub> | $V_{SS}$ -to- $V_{SSA}$ differential voltage                                                                                                                           | - 0.1           | 0.1             | V    |       |

| I <sub>ICIO</sub>                     | Analog DC injection current — single pin                                                                                                                               |                 |                 |      | •     |

|                                       | $V_{IN} < V_{SS}$ - 0.3 V (Negative current injection)                                                                                                                 | - 5             | —               | mA   | 1, 2  |

|                                       | $V_{IN} > V_{DD} + 0.3 V$ (Positive current injection)                                                                                                                 |                 | + 5             | mA   |       |

| I <sub>ICcont</sub>                   | Contiguous pin DC injection current —<br>regional limit, includes sum of negative<br>injection currents or sum of positive injection<br>currents of 16 contiguous pins | - 25            | _               | mA   |       |

| V <sub>ODPU</sub>                     | Open drain pullup voltage level                                                                                                                                        | V <sub>DD</sub> | V <sub>DD</sub> | V    | 3     |

All analog pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is less than V<sub>AIO\_MIN</sub> or greater than V<sub>AIO\_MAX</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICIO</sub>I. Select the larger of these two calculated resistances if the pin is exposed to positive and negative injection currents.

- 2. Max voltage levels that I/O pins can withstand while keeping the injection current (maximum) at 5mA:

- Max supply V<sub>DD</sub> = 6.0 V for 60 s lifetime (with no switching restrictions) or for 10 hours (if device is in reset or no switching state)

- Max I/O pin voltage = 6.5 V (at injection current  $\leq$  5 mA) or 7.0 V (at injection current > 5 mA)

- 3. Open drain outputs must be pulled to  $V_{DD}$ .

#### 5.3.1.2 DC electrical specifications at 3.3 V Range and 5.0 V Range Table 28. DC electrical specifications

| Symbol          | Parameter                       | Value                |     |                       | Unit | Notes |

|-----------------|---------------------------------|----------------------|-----|-----------------------|------|-------|

|                 |                                 | Min                  | Тур | Max                   |      |       |

| V <sub>DD</sub> | I/O Supply Voltage <sup>1</sup> | 2.7                  | 3.3 | 4                     | V    |       |

|                 | @ V <sub>DD</sub> = 3.3 V       |                      |     |                       |      |       |

|                 | @ V <sub>DD</sub> = 5.0 V       | 4                    | —   | 5.5                   | V    |       |

| V <sub>ih</sub> | Input Buffer High Voltage       | $0.7 \times V_{DD}$  | _   | V <sub>DD</sub> + 0.3 | V    |       |

|                 | @ V <sub>DD</sub> = 3.3 V       |                      |     |                       |      |       |

|                 | @ V <sub>DD</sub> = 5.0 V       | $0.65 \times V_{DD}$ |     | V <sub>DD</sub> + 0.3 | V    |       |

Table continues on the next page...

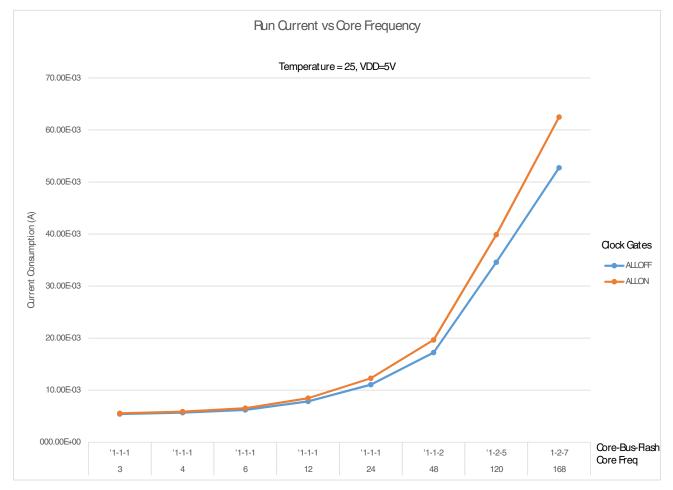

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFE

Figure 14. Run mode supply current vs. core frequency

- AN2764: Improving the Transient Immunity Performance of Microcontroller-Based Applications

- AN1259: System Design and Layout Techniques for Noise Reduction in MCU-Based Systems

#### 5.3.1.7.1 EMC radiated emissions operating behaviors

EMC measurements to IC-level IEC standards are available from NXP on request.

#### 5.3.1.7.2 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions.

- 1. Go to http://www.nxp.com.

- 2. Perform a keyword search for "EMC design".

- 3. Select the "Documents" category and find the application notes.

### 5.3.1.8 Capacitance attributes

#### Table 33. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | —    | 7    | pF   |

### NOTE

Please refer to External Oscillator electrical specifications for EXTAL/XTAL pins.

### 5.3.2 Switching specifications

### 5.3.2.1 Device clock specifications

| Symbol           | Description           | Min. | Max. | Unit | Notes |  |  |

|------------------|-----------------------|------|------|------|-------|--|--|

|                  | High Speed RUN mode   |      |      |      |       |  |  |

| f <sub>SYS</sub> | System and core clock | _    | 168  | MHz  |       |  |  |

| f <sub>BUS</sub> | _                     | 84   | MHz  |      |       |  |  |

#### Table 34. Device clock specifications

Table continues on the next page...

| Symbol               | Description                    | Min.            | Max. | Unit | Notes |

|----------------------|--------------------------------|-----------------|------|------|-------|

| f <sub>FLASH</sub>   | Flash clock                    | _               | 25   | MHz  |       |

|                      | Normal RUN mod                 | le              | •    |      | •     |

| f <sub>SYS</sub>     | System and core clock          | _               | 120  | MHz  |       |

| f <sub>BUS</sub>     | f <sub>BUS</sub> Bus clock     |                 | 60   | MHz  |       |

| f <sub>FLASH</sub>   | Flash clock                    | —               | 25   | MHz  |       |

| f <sub>LPTMR</sub>   | LPTMR clock                    | —               | 50   | MHz  |       |

|                      | VLPR / VLPW mod                | de <sup>1</sup> |      |      |       |

| f <sub>SYS</sub>     | System and core clock          | _               | 4    | MHz  |       |

| f <sub>BUS</sub>     | Bus clock                      | —               | 4    | MHz  |       |

| f <sub>FLASH</sub>   | Flash clock                    | _               | 1    | MHz  |       |

| f <sub>ERCLK</sub>   | External reference clock       | _               | 16   | MHz  |       |

| f <sub>LPTMR</sub>   | f <sub>LPTMR</sub> LPTMR clock |                 | 13   | MHz  |       |

| f <sub>FlexCAN</sub> | FlexCAN clock                  |                 | 4    | MHz  |       |

| Table 34. | <b>Device clock specifications</b> | (continued) |

|-----------|------------------------------------|-------------|

|-----------|------------------------------------|-------------|

1. The frequency limitations in VLPR / VLPW mode here override any frequency specification listed in the timing specification for any other module.

### 5.3.2.2 AC electrical characteristics

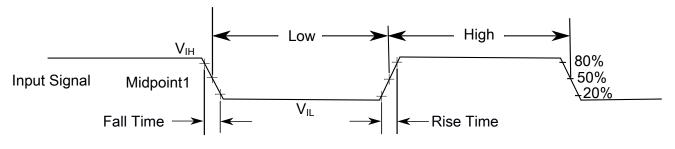

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is V<sub>IL</sub> + (V<sub>IH</sub> - V<sub>IL</sub>) / 2

### Figure 16. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume that the output pins have the following characteristics.

- $C_L=30 \text{ pF loads}$

- Normal drive strength

| Symbol              | Description                                           | Conditions <sup>1</sup>                                  | Min.  | Typ. <sup>2</sup>                 | Max. <sup>3</sup>                                                | Unit             | Notes                                                                                                       |

|---------------------|-------------------------------------------------------|----------------------------------------------------------|-------|-----------------------------------|------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|

|                     | Sample Time                                           |                                                          | 275   | _                                 | Refer to<br>the<br>device's<br><i>Reference</i><br><i>Manual</i> | ns               |                                                                                                             |

| TUE                 | Total unadjusted error at 2.7 to 5.5 V                |                                                          | —     | ±4.5                              | ±6.56                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| DNL                 | Differential non-<br>linearity at 2.7 to 5.5 V        |                                                          | _     | ±0.8                              | ±1.07                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| INL                 | Integral non-linearity at 2.7 to 5.5 V                |                                                          | -     | ±1.4                              | ±3.95                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| E <sub>FS</sub>     | Full-scale error at 2.7<br>to 5.5 V                   |                                                          | _     | -2                                | -3.40                                                            | LSB <sup>5</sup> | $V_{ADIN} = V_{DDA}^{6}$                                                                                    |

| E <sub>ZS</sub>     | Zero-scale error at 2.7<br>to 5.5 V                   |                                                          | _     | -2.7                              | -4.14                                                            | LSB <sup>5</sup> |                                                                                                             |

| EQ                  | Quantization error at 2.7 to 5.5 V                    |                                                          | _     | -                                 | ±0.5                                                             | LSB <sup>5</sup> |                                                                                                             |

| ENOB                | Effective number of bits at 2.7 to 5.5 V              |                                                          | _     | 11.3                              | —                                                                | bits             | 7                                                                                                           |

| SINAD               | Signal-to-noise plus<br>distortion at 2.7 to 5.5<br>V | See ENOB                                                 | _     | 70                                | —                                                                | dB               | SINAD = 6.02 ×<br>ENOB + 1.76                                                                               |

| EIL                 | Input leakage error at 2.7 to 5.5 V                   |                                                          |       | I <sub>In</sub> × R <sub>AS</sub> |                                                                  | mV               | I <sub>In</sub> = leakage<br>current (refer to<br>the MCU's<br>voltage and<br>current operating<br>ratings) |

| V <sub>TEMP_S</sub> | Temperature sensor slope at 2.7 to 5.5 V              | Across the full<br>temperature<br>range of the<br>device | 1.492 | 1.564                             | 1.636                                                            | mV/°C            | 8, 9                                                                                                        |

| V <sub>TEMP25</sub> | Temperatue sensor<br>voltage at 2.7 to 5.5 V          | 25 °C                                                    | 730   | 740.5                             | 751                                                              | mV               | 8, 9                                                                                                        |

Table 54. 12-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

1. All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$

- 2. Typical values assume  $V_{DDA}$  = 5.0 V, Temp = 25 °C,  $f_{ADCK}$  = 48 MHz unless otherwise stated.

- 3. These values are based on characterization but not covered by test limits in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 5. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 6. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 7. Input data is 100 Hz sine wave. ADC conversion clock < 40 MHz.

- 8. ADC conversion clock < 3 MHz

- 9. The sensor must be calibrated to gain good accuracy, so as to provide good linearity, see also AN3031 for more detailed application information of the temperature sensor.

### 5.4.5.2 CMP with 8-bit DAC electrical specifications Table 55. Comparator with 8-bit DAC electrical specifications

| Symbol             | Description                                             | Min.                                        | Typ. <sup>1</sup>    | Max.             | Unit |  |

|--------------------|---------------------------------------------------------|---------------------------------------------|----------------------|------------------|------|--|

| V <sub>DD</sub>    | Supply voltage                                          | 2.7                                         | —                    | 5.5              | V    |  |

| I <sub>DDHS</sub>  | Supply current, High-speed mode <sup>2</sup>            |                                             |                      |                  | μA   |  |

|                    | within ambient temperature range                        | _                                           | 145                  | 200              | -    |  |

| I <sub>DDLS</sub>  | Supply current, Low-speed mode <sup>2</sup>             | current, Low-speed mode <sup>2</sup>        |                      | μA               |      |  |

|                    | within ambient temperature range                        | —                                           | 5                    | 10               |      |  |

| V <sub>AIN</sub>   | Analog input voltage                                    | 0                                           | 0 - V <sub>DDX</sub> | V <sub>DDX</sub> | V    |  |

| V <sub>AIO</sub>   | Analog input offset voltage, High-speed mode            | input offset voltage, High-speed mode       |                      |                  |      |  |

|                    | within ambient temperature range                        | -25                                         | ±1                   | 25               | l    |  |

| V <sub>AIO</sub>   | Analog input offset voltage, Low-speed mode             |                                             |                      |                  |      |  |

|                    | within ambient temperature range                        | -40                                         | ±4                   | 40               | 1    |  |

| t <sub>DHSB</sub>  | Propagation delay, High-speed mode <sup>3</sup>         |                                             |                      |                  | ns   |  |

|                    | within ambient temperature range                        | _                                           | 30                   | 200              | 1    |  |

| t <sub>DLSB</sub>  | Propagation delay, Low-speed mode <sup>3</sup>          |                                             |                      |                  | μs   |  |

|                    | within ambient temperature range                        | —                                           | 0.5                  | 2                |      |  |

| t <sub>DHSS</sub>  | Propagation delay, High-speed mode <sup>4</sup>         | agation delay, High-speed mode <sup>4</sup> |                      |                  |      |  |

|                    | within ambient temperature range                        | _                                           | 70                   | 400              |      |  |

| t <sub>DLSS</sub>  | Propagation delay, Low-speed mode <sup>4</sup>          |                                             | μs                   |                  |      |  |

|                    | within ambient temperature range                        | _                                           | 1                    | 5                | 1    |  |

| t <sub>IDHS</sub>  | Initialization delay, High-speed mode <sup>3</sup>      |                                             |                      |                  | μs   |  |

|                    | within ambient temperature range                        | —                                           | 1.5                  | 3                |      |  |

| t <sub>IDLS</sub>  | Initialization delay, Low-speed mode <sup>3</sup>       |                                             |                      |                  | μs   |  |

|                    | within ambient temperature range                        | —                                           | 10                   | 30               |      |  |

| V <sub>HYST0</sub> | Analog comparator hysteresis, Hyst0 (V <sub>AIO</sub> ) | · · · · ·                                   |                      |                  | mV   |  |

|                    | within ambient temperature range                        | —                                           | 0                    | _                |      |  |

| V <sub>HYST1</sub> | Analog comparator hysteresis, Hyst1, High-speed mode    | eresis, Hyst1, High-speed                   |                      |                  |      |  |

|                    | within ambient temperature range                        | —                                           | 16                   | 53               |      |  |

|                    | Analog comparator hysteresis, Hyst1, Low-speed mode     |                                             |                      |                  |      |  |

|                    | within ambient temperature range                        | _                                           | 11                   | 30               | 1    |  |

| V <sub>HYST2</sub> | Analog comparator hysteresis, Hyst2, High-speed mode    |                                             |                      |                  |      |  |

|                    | within ambient temperature range                        | -                                           | 32                   | 90               |      |  |

|                    | Analog comparator hysteresis, Hyst2, Low-speed mode     |                                             |                      |                  |      |  |

|                    | within ambient temperature range                        | _                                           | 22                   | 53               |      |  |

| V <sub>HYST3</sub> | Analog comparator hysteresis, Hyst3, High-speed mode    |                                             |                      |                  | mV   |  |

Table continues on the next page...

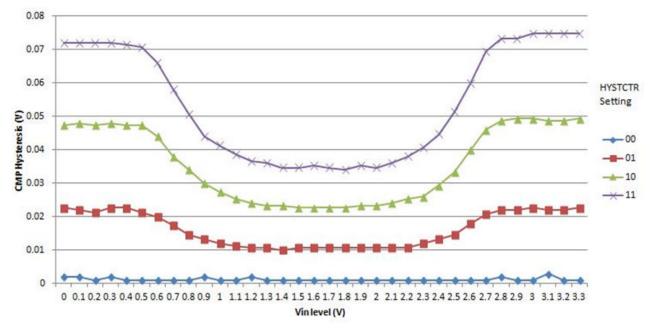

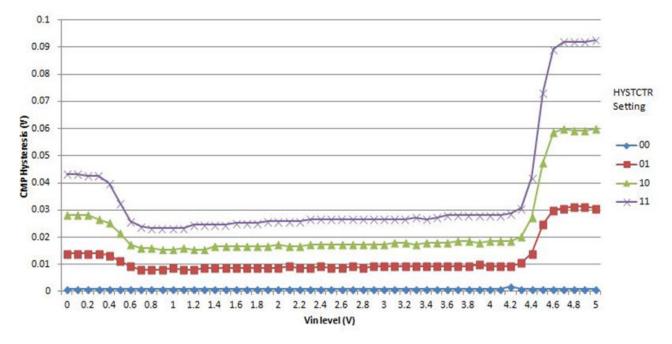

Figure 21. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

Figure 22. Typical hysteresis vs. Vin level (VDD = 5 V, PMODE = 0)

### 5.4.6.2 LPSPI electrical specifications

The Low Power Serial Peripheral Interface (LPSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic LPSPI timing modes.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all LPSPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                          | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                             | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | _                             | t <sub>SPSCK</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x<br>t <sub>periph</sub> | ns                 | -    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        | _                             | ns                 | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | _                             | ns                 | -    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                         | 15                            | ns                 | _    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         |                               | ns                 | _    |

| 10   | t <sub>RI</sub>     | Rise time input                | —                         | t <sub>periph</sub> - 25      | ns                 | -    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                               |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                         | 25                            | ns                 | -    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                               |                    |      |

Table 58. LPSPI master mode timing

1.  $f_{periph} = LPSPI peripheral clock$

2.  $t_{periph} = 1/f_{periph}$

### NOTE

High drive pin should be used for fast bit rate.

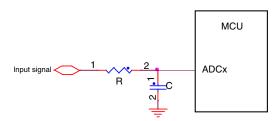

Figure 34. RC circuit for ADC input

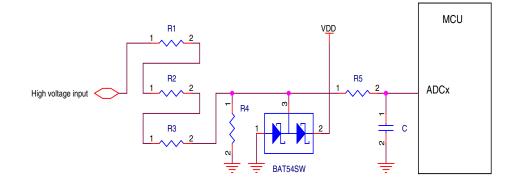

High voltage measurement circuits require voltage division, current limiting, and overvoltage protection as shown the following figure. The voltage divider formed by R1 – R4 must yield a voltage less than or equal to VREFH. The current must be limited to less than the injection current limit. Since the ADC pins do not have diodes to VDD, external clamp diodes must be included to protect against transient over-voltages.

#### Figure 35. High voltage measurement with an ADC input

#### NOTE

For more details of ADC related usage, refer to AN5250: How to Increase the Analog-to-Digital Converter Accuracy in an Application.

### 6.1.4 Digital design

Ensure that all I/O pins cannot get pulled above VDD (Max I/O is VDD+0.3V).

### CAUTION

Do not provide power to I/O pins prior to VDD, especially the RESET\_b pin.

• RESET\_b pin

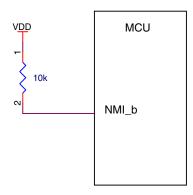

Do not add a pull-down resistor or capacitor on the NMI\_b pin, because a low level on this pin will trigger non-maskable interrupt. When this pin is enabled as the NMI function, an external pull-up resistor (10 k $\Omega$ ) as shown in the following figure is recommended for robustness.

If the NMI\_b pin is used as an I/O pin, the non-maskable interrupt handler is required to disable the NMI function by remapping to another function. The NMI function is disabled by programming the FOPT[NMI\_DIS] bit to zero.

Figure 38. NMI pin biasing

• Debug interface

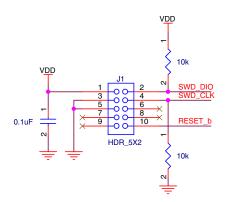

This MCU uses the standard ARM SWD interface protocol as shown in the following figure. While pull-up or pull-down resistors are not required (SWD\_DIO has an internal pull-up and SWD\_CLK has an internal pull-down), external 10 k $\Omega$  pull resistors are recommended for system robustness. The RESET\_b pin recommendations mentioned above must also be considered.

Figure 39. SWD debug interface

• Unused pin